JAJSFU7E December 2013 – March 2019 DLPC2607

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Typical Current and Power Dissipation

- 6.6 I/O Characteristics

- 6.7 Internal Pullup and Pulldown Characteristics

- 6.8 Parallel I/F Frame Timing Requirements

- 6.9 Parallel I/F General Timing Requirements

- 6.10 Parallel I/F Maximum Parallel Interface Horizontal Line Rate

- 6.11 BT.656 I/F General Timing Requirements

- 6.12 100- to 120-Hz Operational Limitations

- 6.13 Flash Interface Timing Requirements

- 6.14 DMD Interface Timing Requirements

- 6.15 mDDR Memory Interface Timing Requirements

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

-

10Layout

- 10.1

Layout Guidelines

- 10.1.1 Internal ASIC PLL Power

- 10.1.2 General Handling Guidelines for Unused CMOS-Type Pins

- 10.1.3 SPI Signal Routing

- 10.1.4 mDDR Memory and DMD Interface Considerations

- 10.1.5 PCB Design

- 10.1.6 General PCB Routing (Applies to All Corresponding PCB Signals)

- 10.1.7 Maximum, Pin-to-Pin, PCB Interconnects Etch Lengths

- 10.1.8 I/F Specific PCB Routing

- 10.1.9 Number of Layer Changes

- 10.1.10 Stubs

- 10.1.11 Termination Requirements:

- 10.2 Layout Example

- 10.1

Layout Guidelines

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- ZVB|176

サーマルパッド・メカニカル・データ

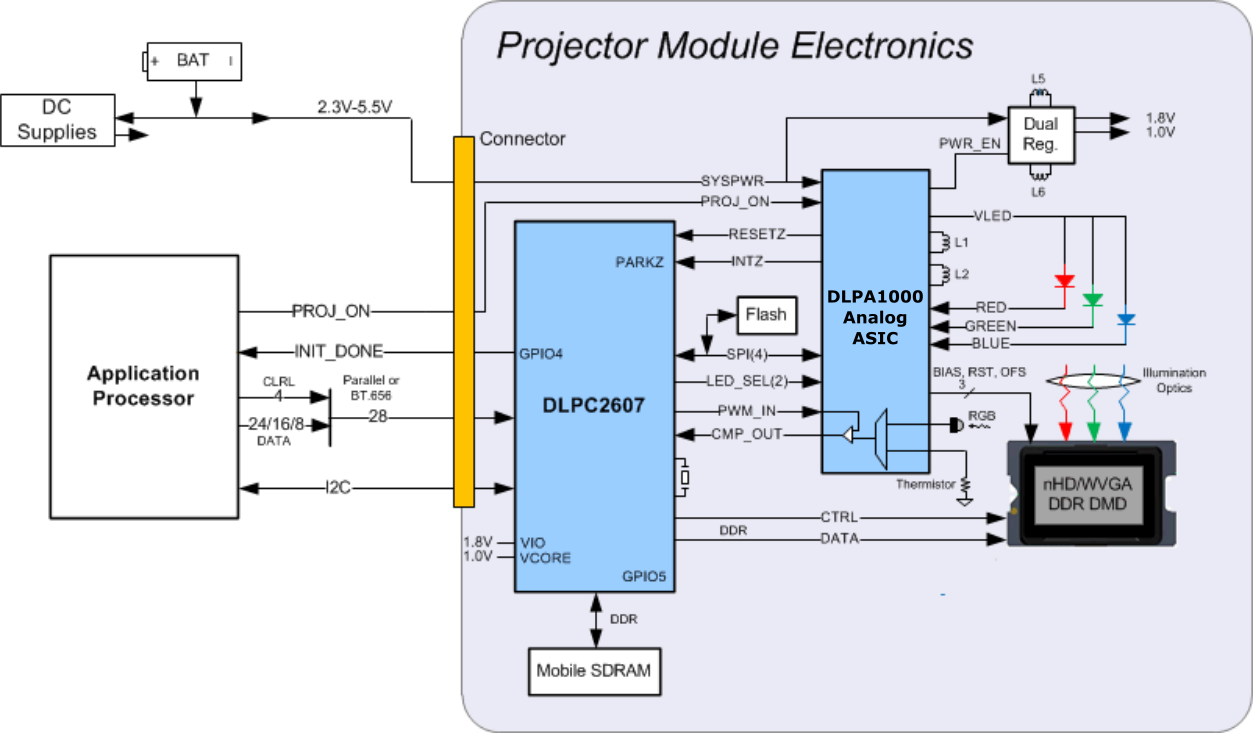

3 概要

DLPC2607はバッテリ駆動ディスプレイ機器向けの低消費電力 DLP™デジタル・コントローラであり、0.3WVGA、0.24VGA、0.2nHD DMDの信頼性の高い動作をサポートします。DLPC2607コントローラは、システム電子機器とDMDの間を接続する便利な多機能インターフェイスを提供し、小型で低消費電力のディスプレイを実現します。

製品情報(1)

| 型番 | パッケージ | 本体サイズ(公称) |

|---|---|---|

| DLPC2607 | VFBGA (176) | 7.00mm×7.00mm |

- 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。