JAJSEP0F April 2013 – May 2019 DLPC350

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 I/O Electrical Characteristics

- 7.6 I2C0 and I2C1 Interface Timing Requirements

- 7.7 Port 1 Input Pixel Interface Timing Requirements

- 7.8 Port 2 Input Pixel Interface (FPD-Link Compatible LVDS Input) Timing Requirements

- 7.9 System Oscillator Timing Requirements

- 7.10 Reset Timing Requirements

- 7.11 Video Timing Input Blanking Specification

- 7.12 Programmable Output Clocks Switching Characteristics

- 7.13 DMD Interface Switching Characteristics

- 7.14 JTAG Interface: I/O Boundary Scan Application Switching Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Application and Implementation

- 10.1 Application Information

- 10.2 Typical Applications

- 11Power Supply Recommendations

-

12Layout

- 12.1 Layout Guidelines

- 12.2 Layout Example

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

11.1.1.5 FPD-Link Input LVDS System Power

The controller supports an FPD-Link compatible LVDS input for an additional method of inputting video or graphics data for display. This interface has some special controller power considerations that are separate from the other controller 1.2- or 3.3-V power rails. An FPD-Link 1.2-V power pin configuration example is shown in Figure 20.

Figure 20. FPD-Link 1.2-V Power Pin Configuration

Figure 20. FPD-Link 1.2-V Power Pin Configuration In addition, TI recommends to place the 0.1-µF low equivalent series resistance (ESR) capacitors to ground as close to the FPD-Link power pins of the DLPC350 controller as possible. FPD-Link 3.3-V power pins should also use external capacitors in the same manner as the 1.2-V pins. When FPD-Link is not utilized, the filtering can be omitted. However, the corresponding voltages must still be provided in order to avoid potential long-term reliability issues.

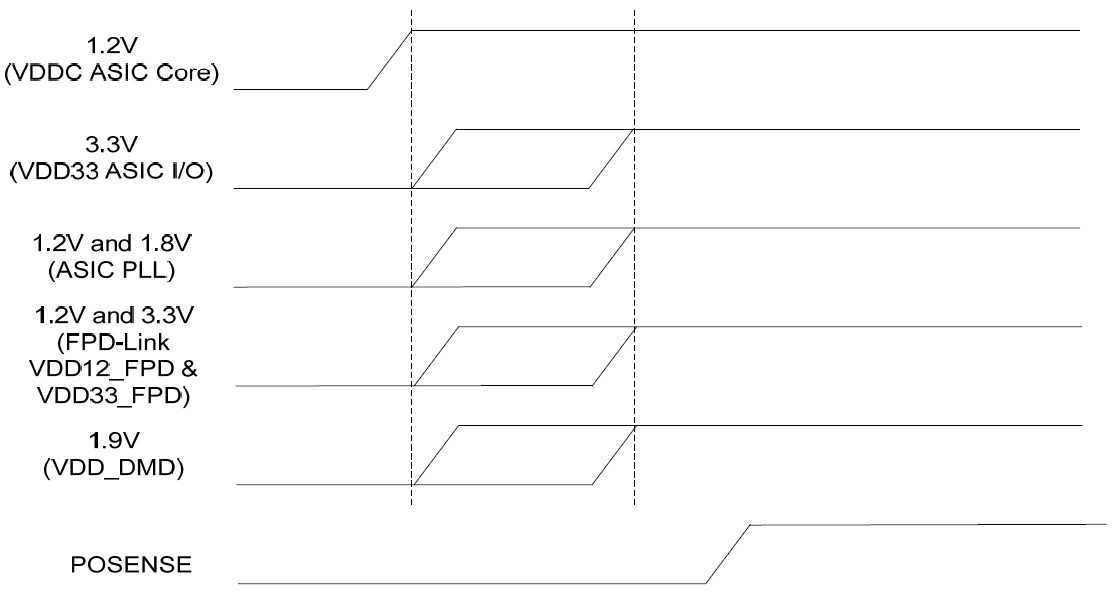

Figure 21. Initialization Timeline

Figure 21. Initialization Timeline