SLUSB69B May 2014 – July 2016 TPS544B20 , TPS544C20

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Turn-On and Turn-Off Delay and Sequencing

- 8.3.2 Pre-Biased Output Start-Up

- 8.3.3 Voltage Reference

- 8.3.4 Differential Remote Sense and Output Voltage Setting

- 8.3.5 PMBus Output Voltage Adjustment

- 8.3.6 Switching Frequency

- 8.3.7 Soft-Start

- 8.3.8 Linear Regulators BP3 and BP6

- 8.3.9 External Bypass (BPEXT)

- 8.3.10 Current Monitoring and Low-Side MOSFET Overcurrent Protection

- 8.3.11 High-Side MOSFET Short-Circuit Protection

- 8.3.12 Over-Temperature Protection

- 8.3.13 Input Undervoltage Lockout (UVLO)

- 8.3.14 Output Overvoltage and Undervoltage Protection

- 8.3.15 Fault Protection Responses

- 8.3.16 PMBus General Description

- 8.3.17 PMBus Address

- 8.3.18 PMBus Connections

- 8.3.19 Auto ARA (Alert Response Address) Response

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 OPERATION (01h)

- 8.6.2 ON_OFF_CONFIG (02h)

- 8.6.3 CLEAR_FAULTS (03h)

- 8.6.4 WRITE_PROTECT (10h)

- 8.6.5 STORE_USER_ALL (15h)

- 8.6.6 RESTORE_USER_ALL (16h)

- 8.6.7 CAPABILITY (19h)

- 8.6.8 VOUT_MODE (20h)

- 8.6.9 VIN_ON (35h)

- 8.6.10 VIN_OFF (36h)

- 8.6.11 IOUT_CAL_OFFSET (39h)

- 8.6.12 IOUT_OC_FAULT_LIMIT (46h)

- 8.6.13 IOUT_OC_FAULT_RESPONSE (47h)

- 8.6.14 IOUT_OC_WARN_LIMIT (4Ah)

- 8.6.15 OT_FAULT_LIMIT (4Fh)

- 8.6.16 OT_WARN_LIMIT (51h)

- 8.6.17 TON_RISE (61h)

- 8.6.18 STATUS_BYTE (78h)

- 8.6.19 STATUS_WORD (79h)

- 8.6.20 STATUS_VOUT (7Ah)

- 8.6.21 STATUS_IOUT (7Bh)

- 8.6.22 STATUS_TEMPERATURE (7Dh)

- 8.6.23 STATUS_CML (7Eh)

- 8.6.24 STATUS_MFR_SPECIFIC (80h)

- 8.6.25 READ_VOUT (8Bh)

- 8.6.26 READ_IOUT (8Ch)

- 8.6.27 READ_TEMPERATURE_2 (8Eh)

- 8.6.28 PMBUS_REVISION (98h)

- 8.6.29 MFR_SPECIFIC_00 (D0h)

- 8.6.30 VREF_TRIM (MFR_SPECIFIC_04) (D4h)

- 8.6.31 STEP_VREF_MARGIN_HIGH (MFR_SPECIFIC_05) (D5h)

- 8.6.32 STEP_VREF_MARGIN_LOW (MFR_SPECIFIC_06) (D6h)

- 8.6.33 PCT_VOUT_FAULT_PG_LIMIT (MFR_SPECIFIC_07) (D7h)

- 8.6.34 SEQUENCE_TON_TOFF_DELAY (MFR_SPECIFIC_08) (D8h)

- 8.6.35 OPTIONS (MFR_SPECIFIC_21) (E5h)

- 8.6.36 MASK_SMBALERT (MFR_SPECIFIC_23) (E7h)

- 8.6.37 DEVICE_CODE (MFR_SPECIFIC_44) (FCh)

-

9 Applications and Implementation

- 9.1 Application Information

- 9.2

Typical Application

- 9.2.1 Design Requirements

- 9.2.2

Detailed Design Procedure

- 9.2.2.1 Switching Frequency Selection

- 9.2.2.2 Inductor Selection

- 9.2.2.3 Output Capacitor Selection

- 9.2.2.4 D-CAP Mode and D-CAP2 Mode Stability

- 9.2.2.5 Input Capacitor Selection

- 9.2.2.6 Bootstrap Capacitor and Resistor Selection

- 9.2.2.7 BP6, BP3 and BPEXT

- 9.2.2.8 R-C Snubber and VIN Pin High-Frequency Bypass

- 9.2.2.9 Temperature Sensor

- 9.2.2.10 Key PMBus Parameter Selection

- 9.2.2.11 Output Voltage Setting and Frequency Compensation Selection

- 9.2.3 Application Curves

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- RVF|40

サーマルパッド・メカニカル・データ

- RVF|40

発注情報

1 Features

- PMBus-Enabled Converters: 20 A, 30 A

- 4.5-V to 18-V input, 0.6-V to 5.5-V Output

- 5 mm × 7 mm LQFN Package with 0.5-mm Pitch

- Single Thermal Pad

- Integrated 4.5-mΩ and 2.0-mΩ Stacked NexFET™ Power Stage

- 600-mV, 0.5% Reference

- Lossless, Low-Side MOSFET Current Sensing

- Selectable D-CAP™ and D-CAP2™ Mode Control

- Differential Remote Sensing

- Monotonic Start-Up into Pre-Biased Output

- Output Voltage Margin and Trim

- Output Voltage and Output Current Reporting

- External Temperature Monitoring with 2N3904

- Programmable via PMBus

- Overcurrent Protection

- UVLO, Soft-Start

- PGOOD, OV, UV, OT Levels

- Fault Responses

- Turn-On and Turn-Off Delays

- Thermal Shutdown

- Pin Compatible 20-A, 30-A Converters

2 Applications

- Test and Instrumentation

- Ethernet Switches, Optical Switches, Routers, Base Stations

- Servers

- Enterprise Storage SSD

- High-Density Power Solutions

3 Description

The TPS544B20 and TPS544C20 devices are PMBus compatible, non-isolated DC-DC Integrated FET converters, capable of high-frequency operation and delivering 20-A , or 30-A current output from a 5 mm × 7 mm package, enabling high-power density and fast transient performance with minimal PCB area. The PMBus interface provides for converter configuration as well as monitoring of key parameters including output voltage, current and an optional external temperature. High-frequency, low-loss switching, provided by an integrated NexFET power stage and optimized drivers, allows for very high-density power solutions and reduced inductor and filter capacitor sizes. Response to fault conditions can be set to either restart or latch off depending on system requirements.

Table 1. Device Information(1)

| PART NAME | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| TPS544B20 | LQFN (40) | 5.00 mm × 7.00 mm |

| TPS544C20 |

- For all available packages, see the orderable addendum at the end of the datasheet.

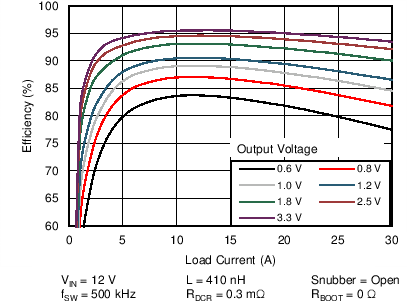

Efficiency vs Output Current

4 Revision History

Changes from A Revision (February 2016) to B Revision

- Changed From: PGND to GND in the Pin Functions table Description for pins BP6 and BPEXT.Go

- Changed Pin Functions table Description for VDD pin To: "Bypass with a 0.1-µF to 1.0-µF capacitor to GND (thermal pad or GND pins) or through a dedicated connection to AGNDSNS." Go

- Changed From: "PGND" To: "GND" in Linear Regulators BP3 and BP6 and External Bypass (BPEXT) Section text. Go

- Changed instances From: "PGND" To: "GND" in the Device Functional ModesGo

- Changed From: " a value of 4.7 μF" To: " a value of 0.1 μF to 1.0 μF" in the Input Capacitor SelectionGo

- Changed text string From: "...one 4.7-μF, 25-V ceramic capacitor..." To: "...one 1.0-μF, 25-V ceramic capacitor..." in the Input Capacitor Selection description.Go

- Changed From: "PGND" To: "GND" in the BP6, BP3 and BPEXT section Go

- Added text to Layout Guidelines section for emphasis on grounding schemes. Go

- Changed PCB Layout Recommendation figure. Go

- Added Receiving Notification of Documentation Updates section.Go

Changes from * Revision (May 2014) to A Revision

- Deleted package suffix and reel quantities from Device Comparison Table Go

- Changed "Handling" Ratings table to "ESD" Ratings and moved Tstg spec to the Absolute Maximum Ratings table.Go

- Added sentence in Switching Frequency description.Go

- Changed "Hiccup" to "Shutdown and latch-off" as the Default Behavior for CMD Command; and, changed Default Register Value from 3Fh to 07h in Table 5, CMD Code 47h Go

- Changed "address" to "frequency" in the PMBus Command Description for CMD Code 80h in Table 5. Go

- Changed Default Value for Bit Position 5, 4, and 3 from 1 1 1 to 0 0 0 respectively in the IOUT_OC_FAULT_RESPONSE (47h) table. Go

- Changed "IVADDR" to "IVFREQ" for Function at Bit Position 4 of the STATUS_MFR_SPECIFIC (80h); and also in the accompanying description. Go

- Added Community Resources section Go