JAJSIQ6C June 2020 – February 2021 UCC21540-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 デバイス比較表

- 6 ピン構成および機能

- 7 仕様

- 8 パラメータ測定情報

- 9 詳細説明

-

10アプリケーションと実装

- 10.1 アプリケーション情報

- 10.2 代表的なアプリケーション

- 11電源に関する推奨事項

- 12レイアウト

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

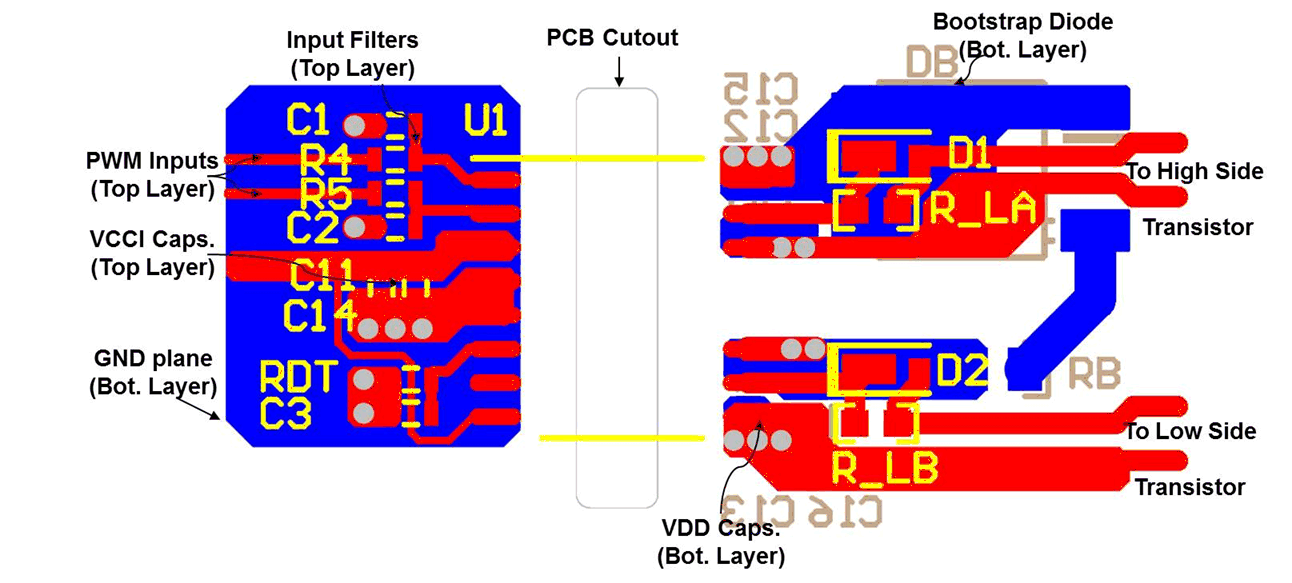

12.2 レイアウト例

図 12-1 に、SOIC-14 DW パッケージに合わせて信号と主要部品を表示した 2 層 PCB のレイアウト例を示します。このパッケージは、ピン 12 とピン 13 が除去されています。詳細については、UCC21540EVM 設計 - 『UCC21540EVM ユーザー・ガイド』を参照してください。

図 12-1 レイアウト例

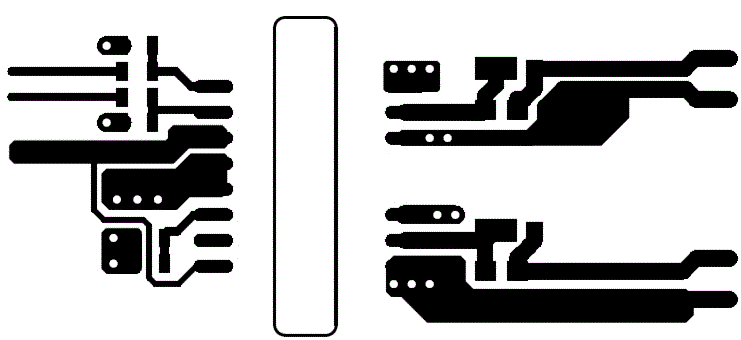

図 12-1 レイアウト例図 12-2 と図 12-3 に上層と下層のパターンと銅箔を示します。

注:

1 次側と 2 次側の間に PCB パターンも銅箔も存在しないため、絶縁性能を確保できます。

高電圧動作に備えて沿面距離を最大化するため、出力段のハイサイド・ゲート・ドライバとローサイド・ゲート・ドライバの PCB パターンの間隔が広げられています。これにより、高 dv/dt が発生する可能性があるスイッチング・ノード VSSA (SW) とローサイド・ゲート・ドライバの間の寄生容量結合によるクロストークも最小化されます。

図 12-4 と図 12-5 に、3D レイアウト画像 (上面図と底面図) を示します。

注:

1 次側と 2 次側の間の PCB カットアウトの場所に注意します。これにより、絶縁性能を確保しています。