# Application Note

# 半導体およびIC パッケージの熱評価基準

#### Darvin Edwards, Hiep Nguyen

#### 概要

半導体および集積回路 (IC) のパッケージには、 $R_{\theta JA}$ から  $\Psi_{JT}$ までの範囲に多くの熱評価基準があります。多くの場 合、これらの熱評価基準は、それぞれのシステムの接合部温度を推定するためにそれらを使用する人々によって、誤って 適用されています。本書は、旧来および新規のサーマルメトリックスを記述し、システムレベルの接合温度見積りに関し て、その適用を広い視野から説明します。

#### 目次

| 2 R <sub>BJC</sub> 接合部からケース                                                    | 6  |

|--------------------------------------------------------------------------------|----|

| 3 Ψ <sub>JT</sub> 、接合部からパッケージの上面まで                                             | 8  |

| 4 R <sub>θ(JB)</sub> 接合部-基板間                                                   | 10 |

| 5 接合部から基板への特性パラメータ Ψ <sub>JB</sub>                                             | 11 |

| 6 産業用および 商業用温度範囲                                                               |    |

| <b>7</b> その他の定義                                                                |    |

| 8 参考資料                                                                         |    |

| 9 改訂履歴                                                                         | 14 |

|                                                                                |    |

| 図の一覧                                                                           |    |

| 図 1-1. 各種パッケージの 1S と 2s2p の PCB                                                | 3  |

| 図 1-2. CSP におけるダイサイズの影響                                                        | 4  |

| 図 1-3. R <sub>0JA</sub> とピン-パッド間の距離                                            | 4  |

| 図 2-1. 銅 (Cu)コールドプレートの測定プロセス                                                   | 6  |

| 図 3-1. 熱電対付きヒートシンクの取り付け                                                        |    |

| 図 4-1.3 抵抗熱近似モデル                                                               | 10 |

| 図 4-2. R <sub>θ(JB)</sub> の測定方法                                                | 11 |

|                                                                                |    |

| 表の一覧                                                                           |    |

| 表 1-1. 特定のパッケージ外形の R <sub>OJA</sub> に影響を及ぼす要因                                  | 2  |

| 表 1-2. 乗算係数                                                                    | 5  |

| 表 3-1. 標準的な 128 ピン TQFP パッケージの (1) (2) (3) (4) (5) (6) (7) (8) Ψ <sub>JT</sub> | g  |

| <b>茄</b> 捶                                                                     |    |

蛍光® is a registered trademark of Luxtron Corporation.

すべての商標は、それぞれの所有者に帰属します。

# 1 R<sub>θJA</sub> 接合部から周囲、および R<sub>θ JMA</sub> 接合部から移動空気

接合部から周囲への熱抵抗  $R_{\theta JA}$  は、熱基準報告では最も一般的なものですが、誤用も最も多いものです。 $R_{\theta JA}$  は、特定のテストクーポンに実装されている IC パッケージの放熱性能の指標です。 $R_{\theta JA}$  の意図は、パッケージの相対的な放熱性能を比較できる基準を提供することです。したがって、TI の熱性能を他の会社のデバイスと比較することできます。これは、EIA/JESD51-x シリーズの資料で JEDEC が規定しているものなど、両社が  $R_{\theta JA}$  を測定するために標準化されたテストを使用する場合に当てはまります。しかし、時には JEDEC 条件に従わず、規格からの逸脱が文書化されていないこともあります。これらのテストのばらつきは、 $R_{\theta JA}$  の測定値に大きな影響を与える可能性があります。したがって、 $R_{\theta JA}$  値でテスト条件が報告されない限り、疑わしいとみなす必要があります。

R<sub>0,JA</sub> の測定は、以下の手順(EIA/JESD51-1、-2、-5、-6、-7、-9 から要約)を使用して実施します。

- 1. 通常、消費電力とチップ最大温度の両方を測定できる熱テストチップを搭載した集積回路(IC)パッケージがテスト基板に実装されます。

- 2. テストチップの温度センシングコンポーネントは較正されています。

- 3. パッケージおよびテスト基板システムは、静止空気中(R<sub>0,JA</sub>)または移動空気中(R<sub>0,JMA</sub>)環境に配置されます。

- 4. 既知の電力をテストチップで消費させます。

- 5. 定常状態に達した後、接合部温度を測定します。

- 6. 測定した周囲温度と接合部温度との差が計算され、消費電力で除算されるため、 $R_{\theta JA}$  の値は $^{\circ}$ C/W で与えられます。

#### 1.1 使用状況

残念ながら、システム設計者は多くの場合、デバイスをシステム内で使用したときの接合部温度を推定するために R<sub>0 JA</sub> を使用してきました。この式は通常、R<sub>0,JA</sub> から接合部温度を計算する際に有効であると考えられています。

$$T_{J} = T_{A} + \left(R_{\theta JA} \times Power\right)$$

(1)

$R_{\theta JA}$  は、パッケージだけでなく部品が実装されているプリント基板 (PCB) の設計やレイアウトなど、他の多くのシステムレベル特性によって変化する関数であるから、これは  $R_{\theta JA}$  熱パラメータを誤って適用していることになります。実際のところ、テストボードはデバイスのリードに半田付けされたヒートシンクです。テストボードの設計または構成を変更すると、ヒートシンクの効率が変化するため、測定値の  $R_{\theta JA}$  も変化します。実際、JEDEC の定義によれば、静止空気中の  $R_{\theta JA}$  測定値では、チップによって生成される電力の約  $70\%\sim95\%$  が、パッケージの表面からではなくテストボードで消費されます。システム基板が  $R_{\theta JA}$  を決定するために使用するテストクーポンと近似することはほとんどないため、式 1 を使った  $R_{\theta JA}$  は、結果として非常に誤った値になります。

すべての材料が一定に保たれているとき、表 1-1 は、特定のパッケージ外形の R<sub>0JA</sub> に影響を与える可能性のある要因を示しています。最初の列は要因を示し、2 番目の列は要因の影響に関する*経験則に*よる推定を示します。

表 1-1. 特定のパッケージ外形の R<sub>0JA</sub> に影響を及ぼす要因

| R <sub>OJA</sub> に影響を及ぼす要因 | 影響力の強さ(経験則) |

|----------------------------|-------------|

| PCB 設計                     | 強い(100%)    |

| チップまたはパッドサイズ               | 強い(50%)     |

| 内部パッケージの幾何学的構成             | 強い(35%)     |

| 高度                         | 強い(18%)     |

| 外部周囲温度                     | 弱い(7%)      |

| 消費電力                       | 弱い(3%)      |

$R_{\theta JA}$  は、パッケージ自体の特性ではなく、パッケージ、PCB、その他の環境要因の特性であることを踏まえて、異なる企業間のパッケージ放熱性能の比較として使用するのがベストです。たとえば、TI がパッケージについて  $40^{\circ}$ C/W の  $R_{\theta JA}$  を、競合他社の  $45^{\circ}$ C/W と比較した場合、TI の部品は、競合他社の部品よりもアプリケーションで 10% 低い温度で動作する可能性が高くなります。

#### 1.2 テストカードによる影響

JEDEC は、IC パッケージの熱性能の測定と報告に関する一連の規格を制定しています。これらの規格は、EIA/ JESD51 規格に準拠します。EIAJ/Semi には、JEDEC 版とは大幅に異なる一連の熱規格もあります。 $R_{\theta JA}$  は一定ではないため、比較を試みる前に、 $R_{\theta JA}$  の計算または測定を行うために使用する規格を決定することが重要です。

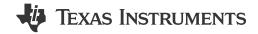

JEDEC の仕様では、2 つのタイプのテストボードが認められています。1s(単一信号層)構成は、適度に実装されたマルチプレーンシステムレベル PCB アプリケーションの*標準的な*使用値となります。2s2p(2 重信号層、2 層埋め込み電源プレーン)構成では、基板実装面積が少なく、配線密度が高い基板設計で埋め込み電源プレーンとグランドプレーンを使用すると仮定したベストケースのの性能推定値が得られます。図 1-1 に、17 の異なるパッケージタイプについて、これら 2 つのボードをモデル化して、R<sub>0JA</sub> の違いを示します。これらのモデルでは、すべての材料とパッケージの形状が一定に保たれていますので、注意してください。

図 1-1. 各種パッケージの 1S と 2s2p の PCB

この図に示すように、1s と 2s2p のテストカード構成における単独の関数として、最大 50%の  $R_{\theta JA}$  のばらつきが予想できます。

#### 1.3 ダイサイズの影響

パッケージ内のチップまたはダイパッドが十分に大きい場合、ヒートスプレッダと同じ機能を果たします。ヒートスプレッダーには、2 つの機能があります。第 1 は、チップのホットスポットからのエネルギーをパッケージ表面のより広い領域に拡散し、対流エネルギー損失を増加させます。第 2 に、パッドからリードフィンガーやパッケージボールへの熱伝導が増加し、PCB に熱を伝えます。図 1-2 は、テープベースのエリアアレイ・チップスケールパッケージ(CSP)に関するダイサイズのR<sub>0JA</sub>への影響を示します。ここに示すように、このパッケージのR<sub>0JA</sub>はダイサイズで約 8 倍に変わります。ダイシュリンクが計画されている場合は、パッケージのR<sub>0JA</sub>を再測定または再計算することが重要です。

図 1-2. CSP におけるダイサイズの影響

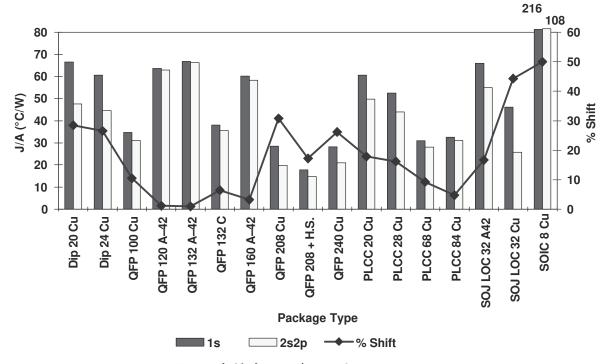

#### 1.4 内部パッケージの幾何学的構成

このトピックでは、従来型のリードフレームパッケージ、小型パッド(S-PAD)パッケージ、リードオンチップ(LOC)、ボールグリッドアレイ(BGA)パッケージなど、パッケージ内のレイアウトを指します。また、より単純な幾何学的構成も、パッケージの放熱性能に大きな影響を及ぼす可能性があります。これには、図 1-3 に示されているように、パッケージ内のリード端子とダイパッドとの間の距離や、パッドとリードフィンガーとの間の距離が含まれます。後者は、薄型パッケージでは特に重要な熱基準です。BGAでは、ダイからパッケージボールに熱を拡散し、そこから PCBに伝導させる上で、インターポーザトレース構成の設計が重要です。

図 1-3. R<sub>0.JA</sub> とピン-パッド間の距離

#### 1.5 高度

周囲環境の気圧が高度に応じて変化すると、空気の冷却効率も変化します。IBM [1]は、海水面で動作するものと同じデバイスを比較して、このデバイスが 8000 フィートでは 20% 高温でも動作すると予想されていることを示しました。他の研究者は、異なる高度で使用すると、ファンの性能とシャーシ内部の空気の流れが大きく変化することを示しています。 特にシステム設計が熱的観点から限界である場合には、これらの影響を検討する必要があります。 主要なシステム会社の多くは、さまざまな有効高度でシステムをテストすることができる圧力室を持っています。 通常、これらの企業は、異なる気圧で動作するときに内部コンポーネントの温度を測定するように設計しています。 表 1-2 に、海抜で決定される R<sub>θJA</sub> の値をディレーティングするために IBM の作業から得られた乗算係数を示します。

| 表 1-2. | 乗算係数 |

|--------|------|

|--------|------|

| 高度(ft) | 係数   |

|--------|------|

| 0      | 1    |

| 3000   | 1.1  |

| 5000   | 1.14 |

| 7000   | 1.17 |

| 8350   | 1.2  |

#### 1.6 周囲温度

周囲温度は対流および放射熱伝達に大きな影響を与えます。熱放射は温度の 4 乗 (T4)で変化するため、温度が上昇するにつれて放射熱の伝達が大幅に増進されます。反対に、対流熱伝達は、高温では空気の密度が低くなるため、温度が上昇すると低下します。一般的に、放射による影響は、自由対流の影響よりもはるかに大きくなります。 TI の熱ラボの実験では、 $0^{\circ}$ C  $\sim$ 100 $^{\circ}$ C の周囲温度で測定した場合、 $R_{\theta,IA}$  の値が約  $10^{\circ}$ C  $\sim$ 20%小さいことが示されています。 つまり、  $100^{\circ}$ C の周囲温度における  $R_{\theta,IA}$  が、 $0^{\circ}$ C の周囲温度  $R_{\theta,IA}$  が、 $0^{\circ}$ C の周囲温度  $R_{\theta,IA}$  が、 $0^{\circ}$ C の月  $R_{\theta,IA}$  が、

#### 1.7 電力散逸

デバイスの表面温度は、パッケージから対流と放射の両方でエネルギー損失を引き起こします。パッケージ表面の温度が高くなれば、周囲環境への対流と放射熱損失がより効率的になります。したがって、パッケージからの消費電力が大きくなると  $R_{\theta JA}$  は小さくなります。電力散逸が非常に小さく、表面温度の上昇を最小限に抑えるため、 $R_{\theta JA}$  は定格パッケージの電力レベルで  $2\sim3$  倍になることがあります。

#### 1.8 R<sub>AJA</sub> 実効値

$\theta$  JA( $R_{\theta JA}$ )は、前のセクションで説明したシステムパラメータに大きく依存するシステムレベルパラメータです。したがって、 $R_{\theta JA}$ (effective)の定義に役立つ場合がありますが、これは、単に対象システムで動作する  $R_{\theta JA}$  に過ぎません。システムの熱モデル化または測定から  $R_{\theta JA}$ (effective)を推定できる場合、システム上の周囲部品の電力が変化しないと仮定し、式 1を使用して接合部温度を計算することできます。式 1 次のようになります。

$$T_{J} = T_{A} + \left(R_{\theta JA(effective)} \times Power\right)$$

(2)

R<sub>0</sub>JA(effective)</sub>値を報告する際には、必ず R<sub>0</sub>JA(effective)</sub>値を決定する必要があります。

# 2 Raic 接合部からケース

当初、接合部からケースへの熱抵抗の指標は、ヒートシンクを取り付けたときのパッケージの熱性能を推定できるように考案されました。EIA/JESD51-1 には、 $R_{\theta JC}$  は「その表面での温度変動を最小限に抑えるために、同じ表面が適切に熱シンクされているときの、半導体デバイスの動作部分からパッケージの外部表面 (ケース) までの熱抵抗」と規定されています。 $R_{\theta JC}$  を定義する現在の JEDEC 仕様は利用できませんが、 $R_{\theta JC}$  を測定するためにかなり普遍的な業界手法が存在します。以下のセクションでこの方法について説明します。SEMI 規格 G43-87 は、 $R_{\theta JC}$  を測定するための液浸法について記述しています。TI は、過去にこの方法を使用してきましたが、歴史的な価値があるだけですので、ここでは詳しく説明しません。

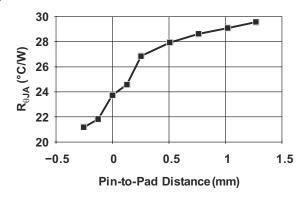

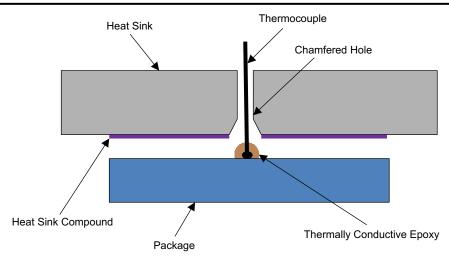

#### 2.1 銅(Cu)コールドプレートの R<sub>e,JC</sub> 測定

この方法では、パッケージの定義された表面をテストデバイスのほぼすべての電力が強制的に通過します。パッケージの上面となるか底面となるかは、ヒートシンクがデバイスにどのように適用されるかによって異なります。通常は、パッケージの上面であることがほとんどです。Rejc は、ダイとヒートシンクを取り付ける表面との間の熱抵抗を決定するのに有用です。

要約すると、手順は次のようになります。

- 1. 熱テストチップを含む IC パッケージは、通常、テスト PCB に取り付けられます。 普通は、JEDEC 定義の low-k 1s0p PCB なので、銅成分が少なく、PCB を介した熱損失を最小限に抑えることができます。

- 2. パッケージは、ケースの上部を測定する場合はケースをコールドプレートに当てた状態で、リード線を上向きにして、で銅コールドプレート (一定温度の流体が循環する銅ブロック)に圧入されます。それ以外の場合、パッケージの主な冷却パスが PCB にはんだ付けされたプレートを経由していれば、パッケージ底面への銅コールドプレートの接触は PCB を経由します。

- 3. シリコン熱伝導グリースまたは他のサーマルインターフェイス材料は、コールドプレートとパッケージの間に熱結合を 提供します。

- 4. 寄生熱損失を最小限に抑えるため、テストクーポンの周囲は絶縁が確保されています。

- 5. デバイスに電力を供給します。

- 6. テストチップの接合部温度を測定します。

- 7. コールドプレートと接触しているパッケージ表面の温度は、この表面に圧着した熱電対または他の温度センサによって測定されます。

- 8. Relic は、測定した温度差を消費電力で除算して算出します。

図 2-1. 銅 (Cu)コールドプレートの測定プロセス

#### 2.2 R<sub>RθJC</sub> アプリケーション

廃止された古い Raic の理解を式 3 に示します。

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \tag{3}$$

ここでは、パッケージの熱性能 R<sub>θJA</sub> は、次の 2 つの抵抗の合計になっています。 R<sub>θJC</sub> および R<sub>θCA</sub>。 R<sub>θCA</sub> は、この式で 定義されるケースから周囲までの熱抵抗を表します。これは、金属缶を持つパッケージは比較的一定の温度にあり、 PCB との熱的結合はなかった場合に有効な式となる場合があります。 ただし、このような条件は、 PCB に緊密に結合された現 在のプラスチックパッケージまたはセラミックパッケージには適用されません。 大きな熱勾配は、最新のパッケージ全体で 一般的であるため、式 3 の意味は疑問です。

従来の R<sub>0JC</sub> の用途は(無効ですが)、システムで動作するチップの接合部温度を計算することです。システムで動作しているデバイスのケース温度は、熱電対、IR カメラ、または蛍光®プローブを使用して測定します。誤って、式 4 を使用して接合部温度を計算してしまうことがあります。式 4:

$$T_{J} = T_{C} + \left(R_{\theta JC} \times Power\right) \tag{4}$$

ここで誤解するのは、標準的なプラスチックパッケージの熱エネルギーのごく一部のみがパッケージの上面から対流および放射されるということです。多くのモデルでは、チップに起因する熱エネルギーの  $60\% \sim 95\%$ が、パッケージを取り付けた PCB から実際に対流および放射が行われることが示されています。全電力が上面によって消費されると仮定すると、式 4 で算出される接合部温度は実際よりも高くなります。熱マージンを持つ設計では厄介ですが、熱マージンを持たない設計では誤った制限が課される可能性があります。この  $R_{\theta JC}$  の制限は、新しい熱評価基準  $\Psi_{JT}$ (以下に記載)によって克服できます。

式 5 には、 $R_{\theta JC}$  が  $R_{\theta JA}$  比べて小さいデバイスの上面に高効率のヒートシンクを適用した場合、それらのインスタンスに対して  $R_{\theta JC}$  を適切に適用したことが示されています。

$$T_{J} \cong T_{A} + \left( \left( R_{\theta JC} + R_{\theta(CS)} + R_{\theta(SA)} \right) \times Power \right)$$

(5)

ここで、 $R_{\theta(SA)}$ はヒートシンクのヒートシンク-周囲間性能、 $R_{\theta(CS)}$ は熱インターフェイス材料のケース-ヒートシンク間熱抵抗となります(式 7 を参照)。周囲温度は、 $R_{\theta(SA)}$ の特性評価に使用される場所で、通常はヒートシンクからある程度離れた位置の温度です。この式は、 $R_{\theta JC}$  が  $R_{\theta JA}$  に比べて小さいパッケージの場合に最も精度が高くなります。これは、十分に効率的なヒートシンクが取り付けられたときに、ほとんどの熱がパッケージの上面を通して放散できることを意味します。

式 6 に、システム構成で R  $_{\theta JA}$  が既知の場合、 $R_{\theta JA}$ 、 $R_{\theta JC}$ 、または  $R_{\theta (SA)}$  の任意の組み合わせの式 5 よりも精度の高い近似値を示します。

$$T_{J} \cong T_{A} + \left(\frac{R_{\theta JA} \times \left(R_{\theta JC} + R_{\theta (CS)} + R_{\theta (SA)}\right)}{R_{\theta JA} + R_{\theta JC} + R_{\theta (CS)} + R_{\theta (SA)}}\right) \times Power$$

(6)

#### $2.3 R_{\theta(CS)}$

$R_{\theta(CS)}$ を算出する最適な方法は、実際には  $R_{\theta(CS)}$ の値を測定することですが、これができない場合は、式 7 を使用して  $R_{\theta(CS)}$ を推定することできます。任意の 2 つの表面間に生じる可能性がある熱界面抵抗は無視されるため、これは単なる推定値であることに注意してください。

$$R_{\theta(CS)} = \frac{T}{k \times A} \tag{7}$$

ここで

T= パッケージとヒートシンク間のインターフェイス層の厚さ

k= 熱伝導材料のバルク熱伝導率 A= 熱伝導材料が適用される領域

#### 2.4 R<sub>0JC(top)</sub>および R<sub>0JC(bot)</sub>

一部のパッケージは、パッケージの上面、底面、または両方から熱を除去するためのヒートスラグや露出したパッドなどのメカニズムを持っています。熱除去のために一方の表面のみを使用する場合、これは EIA/JESD51-1 仕様に基づいて R<sub>θJC</sub> に使用される表面です。また、露出したパッドが PCB にはんだ付けされている場合でも、設計者がパッケージの上面にヒートシンクを取り付ける必要がある場合があります。このような場合、どの表面を指しているか混乱しないようにするために、R<sub>θJC(top)</sub>と R<sub>θJC(bot)</sub>を定義することが望ましいです。上面はパッケージの表面で PCB から離れた位置にあるのに対し、底面は PCB に面している表面です。R<sub>θJC(bot)</sub>を測定する場合、パッケージ底面と銅(Cu)コールドプレートとの間に接触できるような切り欠きを持つ特殊な PCB を構築します。銅(Cu)コールドプレートに接触すると、パッケージの底面で取得した温度が、ケースと接合部温度との間の温度差を計算するために使用されるケース温度になります。

テキサス・インスツルメンツでは、パッケージの接合部と露出パッドとの間の熱抵抗を表すために、時には R<sub>θ(JP)</sub>や接合部からパッドへの用語体系を使用することがありますので注意してください。パッドがパッケージの上面か底面かに露出していても、この用語体系は使用されています。

#### 3 Ψ<sub>ιτ</sub>、接合部からパッケージの上面まで

ケース温度の測定値から、使用時の接合部温度を推定するための熱評価基準をユーザーコミュニティに提供するために、業界では新しい熱評価基準  $\Psi_{JT}$  採用されています(JESD51-2)。この評価基準は、 $\theta(\theta)$ ではなくギリシャ文字 psi ( $\Psi$ )で定義されます。これは、 $\Psi_{JT}$  が真の熱抵抗ではないためです。

$\Psi_{JT}$ の測定手順は、JESD 51-2 で次のように要約されています。

- 通常、熱テストダイを搭載しているテストパッケージをテスト基板に実装します。

- 2. 微細ゲージ熱電対線(36 ゲージ以下)をパッケージの上部中央に接着します。

- 3. 熱電対の放熱特性を最小限に抑えるため、熱電対の配線をパッケージに沿って揃えます。

- 4. テストダイは電力を消費します。

- 5. テストダイの接合部温度と熱電対の温度を測定します。

- 6. 接合部温度と表面温度との間の熱勾配を消費電力で除算します。

$\Psi_{JT}$  が真の熱抵抗にならないのはなぜですか?上記の手順では、テストダイによって生成された熱エネルギーを、優先的な熱伝導経路に沿って正常に流すことができます。ダイからパッケージの上面に流れる熱量は測定値では実際は不明ですが、 $\Psi_{JT}$  計算ためにデバイスの全電力と仮定されています。この仮定が無効であることは明らかでが、この方法で計算すると、実験構成が IC パッケージのアプリケーション環境とよく似ているため、 $\Psi_{JT}$  が非常に便利な値になります。このため、テスト中にダイからパッケージの上面に流れるエネルギーの量は、アプリケーション環境でのエネルギーフローの区分と似ています。式 4 と比較して、実際の接合部温度は式 8 を使用して非常に厳密に推定できます。

$$T_{J} = T_{C} + (\Psi_{JT} \times Power)$$

(8)

プラスチックパッケージの場合、 $R_{\theta,JC}$  の値である  $4^{\circ}C$  /W  $0.5^{\circ}C$ – $15^{\circ}C$  /W に対して、 $\Psi_{JT}$  は通常、PF/W- $2^{\circ}C$  /W です。 薄型のパッケージでは、厚いパッケージよりも  $\Psi_{JT}$  の値が小さくなります。 熱スラグを組み込んだパッケージでは、 $\Psi_{JT}$  の値がゼロに近くなります。  $\Psi_{JT}$  は、基板の構造条件とエアフロー条件によって変化することに注意する必要があります(表 3-1 を参照)。 表 3-1 の値は、モデリングによって得られました。

#### 表 3-1. 標準的な 128 ピン TQFP パッケージの (1) (2) (3) (4) (5) (6) (7) (8) Ψ<sub>JT</sub>

| ダイパッド  | PCB のタイプ <sup>(9)</sup> | エア フロー (LFM) | $\Psi_{JT}$ |

|--------|-------------------------|--------------|-------------|

| 露出     | 1s0p                    | 0            | 0.22        |

| 露出(10) | 2s2p                    | 0            | 0.09        |

| 非露出    | 1s0p <sup>(11)</sup>    | 0            | 0.13        |

| 非露出    | 2s2p <sup>(11)</sup>    | 0            | 0.09        |

| 露出     | 1s0p                    | 250          | 0.47        |

| 露出     | 2s2p                    | 250          | 0.18        |

| 非露出    | 1s0p                    | 250          | 0.31        |

| 非露出    | 2s2p                    | 250          | 0.23        |

- (1) サイズ、タイプ、ピン:14mm×14mm×1.1mm、TQFP、128

- (2) ダイ サイズ 8.4mm × 8.3mm

- (3) ダイの厚さ:露出パッドで 0.31mm、非露出で 0.28mm

- (4) ダイパッドのサイズ: 10.5mm × 9.2mm × 0.15mm

- (5) ダイのインピーダンス:5.77°C mm²/W

- (6) モールドコンパウンドの熱伝導率:0.9W/m-K

- (7) 周囲温度:25°C

- (8) 消費電力:1W

- (9) サイズ: 114.3mm × 76.2mm × 1.6mm

- (10) サーマルビア:9×9 ダイパッドをグランドプレーンに接続(露出パッド付きの 2s2p PCB のみ)

- (11) 種類: JESD 51-7 および JESD 51-3 で定義されている JEDEC high-k(2s2p) および low-k(1s0p)

#### 3.1 ケース温度測定

ケース温度は、デバイス上面の最も高温の温度として定義されます。ほとんどの場合、これはデバイスの上部表面または蓋の中央にあります。ケース温度測定は、IR カメラ、フルオロ光学プローブ、熱電対、または直径 4mm の最大視野角を持つ IR ガンを使用して(精度の高い順に)行うことができます。測定手法として熱電対を選択する場合は、熱電対からの局所的な冷却を最小限に抑えるため、細かいゲージワイヤ(36 ~ 40 ゲージ、J または K ワイヤ)を使用します。ゲージ熱電対でケースの温度が 36 を超えると、熱電対は表面から熱を逃がすことになり、測定対象のスポットが冷却されるため、式 8 の計算が無効になることに注意する必要があります。太いゲージの熱電対を使用してパッケージの上面を測定すると、影響が非常に大きく、周囲温度と実際の表面温度との差が 50% 以上減少します。36 ゲージまたはより小さな熱電対を使用する場合でも、エラーが発生する可能性があります。

熱電対を使用する場合は、パッケージ表面の中心(±1mm)に熱伝導性エポキシのビーズを両側に取り付けます。これは、両側で 2×2mm 以内です。熱電対をパッケージ表面にテープ止めにすることは推奨しません。熱電対のヒートシンク性質を最小限に抑えるため、パッケージの対角線に沿って PCB 表面まで、また、PCB から持ち上げる前に少なくとも 25mm の距離を置いてください。テープを使用することで、熱電対線を PCB に接続し、この配線を行うことができます。 熱電対ワイヤゲージを不適切に使用すると、5% ~ 50%の測定誤差が発生する可能性があります。

IR カメラまたは IR ガンのいずれかを使用する場合は、調査対象の表面の放射率の読み取り値を修正してください。詳しくは、使用している機器のマニュアルを参照してください。

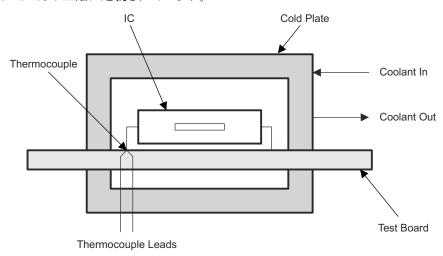

ヒートシンクを適用した状態でケース温度を測定することは、ヒートシンクによって測定対象表面がカバーされるため、特別な課題になっています。ヒートシンクを取り付けた状態でケース温度を測定する場合は、以下の手順を推奨します(図 3-1 を参照)。

- 1. ヒートシンクに直径 1mm 未満の穴をあけ、ヒートシンクが取り付けられたときはパッケージの中央に穴を開けるようにします。パッケージと篏合するヒートシンク表面の穴の端を面取りします。面取りは、熱電対をパッケージに取り付けるエポキシを収容できるようにサイズを調整する必要があります。

- 2. ヒートシンク上部の穴にファインゲージ(36 ゲージ未満)熱電対を通します。

- 3. 熱電対ワイヤは、パッケージの上面に垂直に向けたエポキシを使用して、熱電対ビーズをパッケージの上面に取り付けます。エポキシが硬化するのを待ちます。

- 4. ヒートシンクのベースにヒートシンクコンパウンドを塗布します。

- 5. 熱電対ワイヤはドリル穴に通したまま、ヒートシンクをパッケージの上部に注意深くスライドさせます。

図 3-1. 熱電対付きヒートシンクの取り付け

# 3.2 ヒートシンクを使用する場合の $\Psi_{JT}$ と $R_{\theta JC}$ との関係

$\Psi_{JT}$  は、ヒートシンクを検討するときには使用しないでください。代わりに、式 5 と式 6 を使用してください。

# 4 R<sub>θ(JB)</sub>接合部-基板間

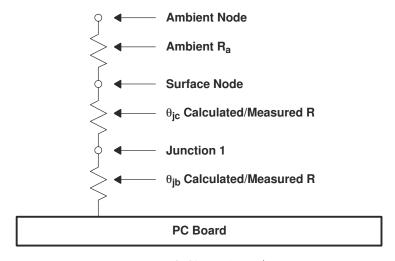

接合部から基板への熱抵抗、または接合部からピンへの熱抵抗は、パッケージと基板との間の熱抵抗を 1 つの数字で表す試みです。実際には、接合部と基板間の抵抗は、接合部-ピン-基板、接合部-プラスチック-空気-基板など、さまざまな抵抗経路に分散しています。さらに、 $R_{\theta JB}$ の概念は、デバイスの下の基板温度が均一温度 (単一ノード) であることを意味しており、これは誤りです。それにもかかわらず、 $R_{\theta JB}$ などの単一の熱評価基準は、図 4-1 に示すように、以下の単純な 3 抵抗の熱近似に基づいて、接合部温度の 1 回目のパス推定に有用です。このモデルでは、接合部から基板への抵抗は単純に  $R_{\theta JB}$ の値となります。接合部とケース表面との間の抵抗は、単純に  $R_{\theta JC}$ の値です。周囲抵抗  $R_{\theta (a)}$ 、パッケージの上面からの対流熱損失と放射損失から計算されます。

図 4-1.3 抵抗熱近似モデル

### 4.1 R<sub>θ(JB)</sub>の測定方法

R<sub>θ(JB)</sub>の主な測定方法は次のとおりです。

- 1. サーマルテストダイを含むテストパッケージをテスト基板に実装します。

- 2. 細線熱電対(36~40 ゲージ)は、ダイに最も近いデバイスピンに接着または半田付けします。BGA パッケージの場合、ダイに最も近いパッケージの端部の下から出るトレースに熱電対をはんだ付けまたは接着します。

- 3. 基板は、パッケージとコールドプレート表面の間に絶縁性の特殊な二重コールドプレート固定具でクランプされていますが、コールドプレートと基板の間には熱的接触があります。コールドプレートは PCB のヒートシンクに影響を与えます。

- 4. ダイは、電力を消費します。

- 5. ダイとピンの温度をモニターします。

- 6. 定常状態になると、接合部温度とピン温度との差を合計消費電力で除算します。

この手順は、JESD 51-8 でより正確に定義されています。

図 4-2. R<sub>θ(JB)</sub>の測定方法

# 5 接合部から基板への特性パラメータΨ μΒ

$\Psi_{JB}$ は、 $\Psi_{JT}$ と非常に似た概念です。これは、接合部温度とセンターパッケージピン温度との差を、デバイスの消費電力で除算したものです。このため、この熱抵抗を介して電力を実際に分割する方法は不明なので、真の熱抵抗ではありません。

#### 5.1 Ψ IR アプリケーション

$\Psi_{JB}$  により、極細熱電対を使用して基板の温度を測定し、式 9 を使用して接合部温度を算出することができます。 デバイスの熱の 75%~95% が PCB によって放散されるので、 $\Psi_{JB}$  は  $R_{\theta JB}$  に近い値になりますので注意してください。

$$T_{J} = T_{(PCB)} + (\Psi_{JB} \times Power)$$

(9)

$\Psi_{JB}$ の測定は JESD51-6 で定義されています。 $\Psi_{JT}$  測定用にケース温度を測定する目的で設計された熱電対と同様に、熱電対のタイプ、残量計、PCB 全体での熱電対の配置の選定、選択には注意が必要です。 $\Psi_{JT}$  の測定と同様に、IR カメラまたは光ファイバープローブを使用して PCB の温度を測定することができます。ただし、撮影するスポットサイズが小さいため、IR サーマルガンは不適です。

### 6 産業用および 商業用温度範囲

産業用温度範囲機能マークが付いているテキサスインスツルメンツのデバイスは、絶対最大動作温度範囲を超えないように適切な注意が払われていれば、-40°Cと85°Cの間で機能します。入力周囲気温が-40°C~85°Cの間であっても、デバイスの最大動作温度を超えないように、システムレベルの熱設計が必要です。産業用温度範囲が規定されている場合、最小動作温度は-40°Cです。産業用温度対応の意味を定義する業界標準は存在しないため、企業によってバリエーションが存在する可能性があります。

商業用温度範囲機能マークが付いているテキサスインスツルメンツのデバイスは、絶対最大動作温度範囲を超えないように適切な注意が払われていれば、 $0^{\circ}$ C ~  $70^{\circ}$ C の間の周囲温度で機能します。商業用温度範囲が規定されている場合、最低動作温度は $0^{\circ}$ C です。

#### 7その他の定義

**接合部絶対最大** その温度を上回るとデバイスが損傷する温度。この温度では、デバイスが機能しない、または期待す **温度** る性能を発揮しない可能性があります。

**絶対最大動** デバイスが電気的に機能する接合部の最大温度。デバイスがこの温度で継続的に動作している場合、デ**作温度** バイスの寿命が短くなります。時々「最大動作温度」という用語も使われます。

周 複数のソースには、周囲の空気温度を決定するためのさまざまな位置が記載されています。NEBS では、システム 囲 ボックスに入る気温を周囲温度として指定しています。AEC では、デバイスの下の気温を周囲温度として規定して います。JEDEC では、PCB の前の気流温度と規定しています。時には、周囲環境を理解するために、デバイス上 部の周囲気温を測定することがあります。これらの測定位置のそれぞれから得られる周囲の気温は、それぞれに異なります。いずれの場合でも、デバイスの信頼性と機能に影響を与える重要な要素は、周囲温度ではなく接合部温度であることを理解することが重要です。接合部温度と周囲温度は相互に関連しているため、システムレベルの解析を行う前に、周囲温度の仮定を明確にしておくことが重要です。

**接合部温度** パッケージ内部のシリコンチップの最高温度です。

最大ケ 場合によっては、「最大動作温度」を指定せずに、ケースの最大温度が与えられることがあります。デバイスを最 ース温 大ケース温度(ヒートシンクなし)で動作させると、ダイは推奨動作接合部温度で動作します。これは T<sub>C</sub> と表記 される場合もあります。 通常、T<sub>case</sub> は、パッケージ上面の中央で測定します。

**推奨動** デバイスが設計寿命全体を通じて指定された性能で連続的に動作する接合部温度。デバイスがこの温度を超**作温度** えると、デバイスの信頼性が低下する可能性があります。一部のデバイスは、この温度を超えると電気的に機能しなくなります。時には、「推奨連続動作接合部温度」という表現を使うこともあります。

www.ti.com/ja-jp 参考資料

### 8参考資料

- 1. Mansuria、1994 年国際エレクトロニクス パッケージング会議議事録、IEPS、カリフォルニア州サンディエゴ、1994 年 9 月、pp 122-130

- 2. Rosten, H., 1996,"Delphi—A Status Report on the European-funded Project for the Development of Libraries and Physical Models for an Integrated Design Environment,' Proc. of 46th Electronic Components & Technology Conference, pp. 172–185 . (英語)

- 3. EIA/JESD51-1、『IC の熱測定方法-電気的テスト方法』(シングル半導体デバイス)

- 4. JESD51-2、『IC の熱テスト手法の環境条件 自然対流 (静止空気)』.

- 5. JESD51-5、『直接熱付着機構を持つパッケージの熱テスト基板標準の拡張』

- 6. JESD51-6、『IC の熱テスト手法の環境条件 自然対流 (空気流)』

- 7. JESD51-7、『リード付き表面実装パッケージ用の有効熱伝導率の高いテスト基板』

- 8. JESD51-9、『エリア アレイ表面実装パッケージの熱測定用テスト基板』

# 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision C (April 2016) to Revision D (March 2024) | Page |

|-----------------------------------------------------------------|------|

| <ul><li>ドキュメント全体にわたって表、図、相互参照の採番方法を更新</li></ul>                 | 2    |

| Changes from Revision B (July 2012) to Revision C (April 2016)  | Page |

| - 関連する JEDEC 仕様を追加                                              | 2    |

| <ul><li>図 1-2 の Y 軸ラベルの変更</li></ul>                             | 3    |

| • 図 1-3 の Y 軸ラベルとキャプションの変更                                      | 4    |

| <ul><li>分圧を大気圧に変更しました</li></ul>                                 | 5    |

| <ul><li>セクション 1.6 のテストを変更</li></ul>                             | 5    |

| • セクション <b>1.7</b> のテキストを変更。                                    | 5    |

| • セクション 1.8 に更新しました。                                            | 5    |

| • セクション 2.2 に更新しました。                                            |      |

| • 仕様参考資料を JEDEC JC51.1 から EIA/JESD51-1 に訂正                      | 7    |

| <ul><li>ケース温度測定の手順を変更</li></ul>                                 | 9    |

#### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated