# 高密度 GaN 最適化 PFC コンバータにおける AC 電圧低下からの回復

#### **Brent McDonald**

System and Application Engineer Power Design Services

#### はじめに

データセンターのサーバー電源ユニットで電力損失が発生すると、エンターテインメントから金融取引、ホーム セキュリティシステムに至るまで、あらゆるサービスが中断される可能性があります。Open Compute Project (OCP) の V2 Power Shelf Specification [1] などの仕様では、堅牢な AC ドロップアウト制御アルゴリズムを用いてサーバーのダウンタイムを削減する必要性が指摘されています。また、データセンターでは、受動部品の小型化を図りながら力率補正 (PFC) の軽負荷とピーク効率を改善する費用対効果の優れた高ソリューションの実現が求められていますが、従来型の連続導通モード制御 [8 - 2] では難しくなっています。

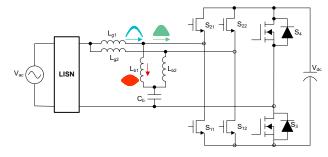

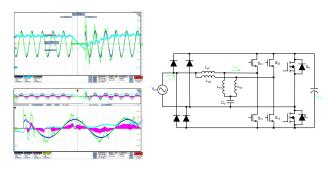

この問題に対処するために、テキサス・インスツルメンツは2 相統合型の三角波電流モード (iTCM) PFC (図 1) [9] を使用 して、窒化ガリウム (GaN) ベースの高密度設計を開発しまし た。値の低いインダクタを高周波で動作させることで、この設 計では高い効率 (>99%) と電力密度 (120 W/in3) を実現しい ます。このような小型インダクタの場合、わずか数マイクロ秒 のスイッチのオン時間で 70A を超えるスイッチ電流が発生す るという、AC 電圧低下からの回復に特有の問題が生じます。 また、タイミングが遅れると大きな逆電流が発生し、PFC の回 復がさらに悪化する可能性もあります。電流レベルを安全な 範囲に維持し、逆電流を防止するには、AC 電圧低下と回復 の問題を解決する新しいソリューションを開発する必要があり ました。この記事は、『可変周波数、ZVS (ゼロ電圧スイッチン グ)、5kW、GaN ベース、2 相トーテムポール PFC のリファレ ンス デザイン』 [表 1] に基づくラボ検証データをもとに、10 に 主要コンポーネントとシステム仕様を示すこのソリューション について説明します。

図1. インダクタと電流エンベロープを有する iTCM トポロジ

| パラメータ                                                                                             | 値                       |

|---------------------------------------------------------------------------------------------------|-------------------------|

| AC 入力                                                                                             | 90V~264V                |

| ライン周波数                                                                                            | 50Hz∼60Hz               |

| DC 出力                                                                                             | 400 V                   |

| 最大電力                                                                                              | 5 kW                    |

| 全負荷時のホールドアップ時間                                                                                    | 20 ms                   |

| Lg、低周波インダクタ                                                                                       | 140µH                   |

| L <sub>b</sub> 、高周波インダクタ                                                                          | 14µH                    |

| C <sub>b</sub> 、高周波ブロッキング コンデンサ                                                                   | 1.5µF                   |

| 全高調波歪み (THD)                                                                                      | OCP v3                  |

| 電磁干渉 (EMI)                                                                                        | 欧州規格 (EN) 55022 Class A |

| 動作周波数                                                                                             | 可変、75kHz ~ 1.2MHz       |

| マイクロコントローラ                                                                                        | TMS320F280049C [11]     |

| 高周波 GaN 電界効果トランジスタ<br>(FET) (S <sub>11</sub> 、S <sub>12</sub> 、S <sub>22</sub> 、S <sub>21</sub> ) | LMG3526R030 [12]        |

| 低周波シリコン FET (S3、S4)                                                                               | IPT60R022S7XTMA1        |

| 寸法                                                                                                | 38mm × 65mm × 263mm     |

| 電力密度                                                                                              | 120 W/インチ <sup>3</sup>  |

表 1. インダクタと電流エンベロープを有する iTCM トポロジ

## トポロジの概要

このトポロジでは、 $180^\circ$  の位相差で動作する 2 つの位相と、 1 つの DC ブロッキング コンデンサ  $C_b$  を使用し、2 相アーキテクチャによるリップル電流キャンセルを活用して、 $C_b$  の 2 乗平均平方根 (RMS) 電流ストレスを低減します。 $L_{b1}$  と  $L_{b2}$  は、TCM 動作に必要な高周波 AC リップル電流を処理する

大きさとなっているため、[5] で定義されているように、TCM で使用されるインダクタで必要な DC バイアス負荷を除去できます。 $L_{b1}$  と $L_{b2}$  にフェライトコアを使用すると、ゼロ電圧スイッチング (ZVS) に必要な高い磁東スイングが存在しても、損失を低く抑えることができます。 $L_{g1}$  と $L_{g2}$  は、 $L_{b1}$  と $L_{b2}$  に比べて値が大きいため (10 倍程度)、ほとんどの高周波電流が入力ソースに流れ込むのを防ぎ、EMI を改善できます。さらに、 $L_{g1}$  と $L_{g2}$  でリップル電流が低減されているため、低コストのコア材料の使用が可能となります。図 1 には、インダクタやスイッチ ノードのリップル電流エンベロープも示しています。

### AC 電圧低下に関する技術的な課題

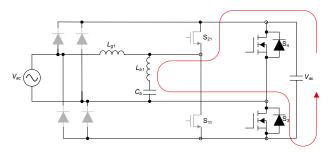

最初に注目したい課題は、AC 入力電圧がなくなると逆電流 が発生することです。トーテムポール PFC トポロジ内にある すべてのスイッチは双方向であるため、同期整流器として動 作する FET は、AC を取り除く際にできるだけ迅速に遮断す ることが重要です。これにより、出力電圧が放電し、利用可能 なホールドアップ時間が短縮される原因となる負電流の生成 が防止されます。図2は、正のハーフサイクル中の同期導通 区間に対してこの負電流を生成する経路を示します。さらに、 同期整流器のターンオフが大幅に遅延すると、過電流保護 (OCP) をアクティブにすることができる大きな電流スパイクが 発生する可能性もあります。たとえば、入力電圧がないときに 同期整流器がオンのままである場合、 $V_{dc} = L_{b1} \cdot rac{dI_1}{dt}$  を解け ば、70A の電流を生成するのにかかる時間、すなわち 2.5us を求めることができます。この短い時間は AC 電圧低下の検 出にとって重大な問題を提示しており、システムが OCP に達 したり損傷を引き起こしたりする前に問題を特定し、スイッチン グを停止する必要があります。

図2. 同期整流器 S<sub>21</sub> の遅延ターンオフ V<sub>DC</sub> 放電パス

2つ目の課題は、AC 回復後の PFC の動作再開です。この事象の中心的な問題は、PFC のバイパス ダイオードが出力電圧を入力正弦波のピークまで充電するという事実に起因します。これは、出力電圧がこのピーク値より大幅に低下したときに、高ラインで最も発生しやすくなります。このような事象が発生している間、コンバータには電流を止めるメカニズムがないため、サージ電流は非常に大きくなります。これらの事象の際にスイッチを不適切に制御すると、インダクタが飽和してOCP 事象が発生し、出力電圧がさらに放電されるため、事態をさらに悪化させる可能性があります。L<sub>b1</sub> と L<sub>b2</sub> に小さな値のインダクタを使用する iTCM トポロジの高周波動作ポイントにより、この間も高精度の制御アルゴリズムが必要となります。

#### AC 電圧低下に対するソリューション

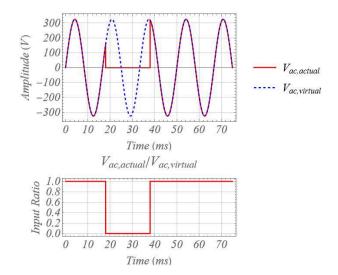

AC 入力の有無を正確に判定するために、このソリューションでは実際の AC 入力の整合性を監視する仮想 AC 入力信号を使用します。この仮想信号は、入力電圧の振幅、周波数、位相を測定することで生成され、通常動作時には、実際のAC 入力の 50Hz と 60Hz の成分をほぼ完全に追跡します。システムは、実際の入力と仮想入力を比較することで、AC 入力電圧の有無を簡単に認識できます。これら 2 つの信号の差に急激な変化があれば、それは入力過渡事象を示します。AC 入力電圧の損失と回復の両方を検出するために使用されるのが、この過渡事象です。図 3 は、電圧低下時の仮想AC 入力と実際の入力を示しています。

図3. 仮想 AC 信号による AC 入力電圧低下

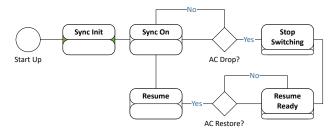

図 4 は、電圧低下と回復のプロセスを実行するステート マシンを示しています。起動時、システムは初期化サイクル (Sync Init) を通して RMS 入力電圧の大きさを決定します。 Vac, virtual の位相が Vac, actual と一致するように、ソフトウェア フェーズロック ループ (SPLL) を使用しています。 SPLL がロックされると (Sync On)、プロセッサは Vac, actual/Vac, virtual の比率を監視します (図 3 を参照)。この比率が目標スレッショルドよりも低い場合、電圧低下事象が宣言され、スイッチングはただちに停止します (Stop 状態)。ここから、システムは発生した故障をすべてクリアし、スタンバイ状態 (Ready) に移行し、

Vac,actual/Vac,virtual の比率を監視して、この比率が回復スレッショルドを超えるタイミングを判定します。ステートマシンは AC が回復したと判定すると、ただちにスイッチングを再開し、SPLL (Resume 状態) を再同期します。このアルゴリズムは、Vac,actual/Vac,virtual の比率と SPLL を組み合わせて使用することで、任意の入力電圧または周波数に対する AC の電圧低下時間と回復時間を決定することができます。さらに、このアルゴリズムは常に Vac,actual/Vac,virtual の比率を監視しているため、AC 入力電圧がゼロになった時点で検出する従来のレベルベースのソリューションよりも迅速に対応することができます。レベルベースの電圧低下監視は、大きな電流スパイクや激しい逆電流の原因となる遅延を発生させる可能性があります。

図4.AC の電圧低下と回復のステート マシン

# 結果

図 5 は、前述のアルゴリズムを使用した、2 相 iTCMトーテムポール PFC の AC の電圧低下と回復時のパフォーマンスを示しています。AC 入力電圧は 60Hz で 230V<sub>RMS</sub>、出力電圧は 400V です。負荷は 5kW (400V、12.5A) の定電流で、20ms の AC 電圧低下が発生します。システムにワーストケースのストレスを発生させるため、AC は、AC ラインサイクルのピーク時に戻るように除去しました。これは、AC ラインのピ

ークが V<sub>OUT</sub> を超えると、入力バイパス ダイオードが出力コン デンサに大きな突入電流を発生させるという意味で、突入電 流にとってワーストケースです。

図 5 の波形では、この事象の回復部分の拡大画像も示されています。PFC スイッチ電流が適切に制御されており、GaN FET の OCP 制限 [12] を下回っていることがよくわかります。逆電流が最小化されているため、V<sub>OUT</sub> の不要な放電が防止されます。また、入力電圧が出力電圧を上回っているか等しいかをアルゴリズムで容易に判定できるため、バイパス ダイオードの導通間隔に起因する異常動作はありません。

図5.5kW での AC の電圧低下と回復のパフォーマンス

このデザインは、AC 電圧低下の他にも、低 THD、高効率、 高電力密度、高速負荷過渡応答も実現しています。

このアルゴリズムやこのデザインのその他の詳細については、リファレンス [10] で 2 相トーテムポール PFC リファレンス デザインの回路図、レイアウト、部品表、テスト結果、コードを参照してください。

# 参考資料

- 『V2 Power Shelf Specification 6600W @ 12.6V DC (2+1) Redundant』(英語)。OPEN Compute Project。 Facebook:カリフォルニア州メンロパーク、2015 年 2 月。

- 2. Fernandes、Ryan、Olivier Trescases。『A Multimode 1-MHz PFC Front End With Digital Peak Current Modulation』(英語)。IEEE Transactions on Power Electronics 31、no. 8 (2016 年 8 月):pp. 5694 ~ 5708. doi:10.1109/TPEL.2015.2499194 で公開。

- Load』(英語)。2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC)、pp. 291~298. doi:10.1109/APEC.2012.6165833 で公開。

- 4. Huang、Long、Wenxi Yao、Zhengyu Lu。『Interleaved Totem-Pole Bridgeless PFC Rectifier with ZVS and Low Input Current Ripple』(英語)2015 IEEE Energy Conversion Congress and Exposition (ECCE)、pp. 166~171. doi:10.1109/ECCE.2015.7309684 で公開。

- 5. Zhengyang Liu。2017.『Characterization and Application of Wide-Band-Gap Devices for High Frequency Power Conversion』(英語)。博士論文、バージニアエ科大学。

- 6. Kim、J.W.、S.M.Choi、K.T.Kim。『Variable On-Time Control of the Critical Conduction Mode Boost Power Factor Correction Converter to Improve Zero-Crossing Distortion』(英語)。2005 International Conference on Power Electronics and Drives Systems、pp. 1542~1546、doi:10.1109/PEDS.2005.1619933 で公開。

- 7. Xu、Xiaojun、Alex Q. Huang。『A Novel Closed Loop Interleaving Strategy of Multiphase Critical Mode Boost PFC Converters』(英語)。 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition (APEC)、pp. 1033~1038、doi: 10.1109/APEC.2008.4522849 で公開。

- 8. Neumayr、D.、D. Bortis、E. Hatipoglu、J.W.Kolar、G. Deboy。『Novel Efficiency-Optimal Frequency Modulation for High Power Density DC/AC Converter Systems』(英語)。2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017-ECCE Asia)、pp. 834~839、doi:10.1109/IFEEC.2017.7992148 で公開。

- 9. Daniel Rothmund、Dominik Bortis、Jonas Huber、Davide Biadene、Johann W. Kolar。『10 kV SiC-Based Bidirectional Soft-Switching Single-Phase AC/DC Converter Concept for Medium-Voltage Solid-State Transformers』(英語)。2017 IEEE 8th International Symposium on Power Electronics for Distributed Generation Systems (PEDG)、pp. 1~8、doi:10.1109/PEDG.2017.7972488 で公開。

- 10. テキサス・インスツルメンツ (発行年記載なし)『**可変周波数、ZVS (ゼロ電圧スイッチング)、5kW、GaN ベース、2** 相トーテムポール PFC のリファレンス デザイン』テキサス・インスツルメンツのリファレンス デザイン No. PMP40988。2022 年 12 月 27 日アクセス。

- 11. テキサス・インスツルメンツ (発行年記載なし)『100MHz、FPU と TMU (三角関数算術演算ユニット) と 256KB フラッシュと CLA (制御補償器アクセラレータ) と InstaSPIN-FOC™ と CLB (構成可能論理ブロック) と PGA (プログラマブル ゲイン アンプ) と SDFM (デルタ シグマ フィルタモジュール) 搭載、C2000™ 32 ビット マイコン』2022 年12 月 27 日アクセス。

- 12. テキサス・インスツルメンツ (発行年記載なし)『**車載、ドライバと保護機能と温度レポート機能を内蔵、650V、30mΩの GaN FET**』2022 年 12 月 27 日アクセス。

**重要なお知らせ**:ここに記載されているテキサス・インスツルメンツ社および子会社の製品およびサービスの購入には、TI の販売に関する標準の使用許諾契約への同意が必要です。お客様には、ご注文の前に、TI 製品とサービスに関する完全な最新情報のご入手をお勧め致します。TI は、アプリケーションに対する援助、お客様のアプリケーションまたは製品の設計、ソフトウェアのパフォーマンス、または特許の侵害に対して一切責任を負いません。ここに記載されている他の会社の製品またはサービスに関する情報は、TI による同意、保証、または承認を意図するものではありません。

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated