# TIA/EIA-485(RS-485)のインターフェイス回路

## 概要

本デザイン・ノートでは、TIA/EIA-485方式のインターフェイス回路の設計に関する情報を提供します。本書では平衡型伝送路規格の必要性を説明し、プロセス制御設計の一例を示します。伝送路負荷について、信号減衰、フェイルセイフ、ガルバニック絶縁にも触れながら説明します。最後に、アイ・パターンを使った実験の装備と測定の方法について記述します。アイ・パターンを使用して、信号の歪み、ノイズ、信号の減衰、そしてそれらの結果データ伝送システム内で生じるシンボル間干渉(ISI)の影響を測定します。

#### 目次

| <b>概要</b>                               |              |

|-----------------------------------------|--------------|

| 1 平衡型伝送路規格の必要性                          | 2            |

| 2 システム設計の考慮事項                           | 4            |

| 2.1 伝送路負荷(Line Loading)                 | 2            |

| 2.2 信号の減衰と歪み                            | <del>.</del> |

| 2.3 障害保護とフェイルセーフ動作                      | 6            |

| 2.4 ガルバニック絶縁                            | 10           |

| 3 プロセス制御設計の例                            | 12           |

| 4アイ・パターン                                | 13           |

|                                         | 13           |

| 4.2 アイ・パターンから測定値を得る                     |              |

| 5 参考文献                                  |              |

| 6 要約                                    |              |

| V X+1                                   |              |

| 図目次                                     |              |

| 図 1 485仕様の主要点                           |              |

| 図 2 単位負荷の概念                             |              |

| 図 3 信号の減衰                               |              |

| 図 4 485の信号歪み vs 信号速度                    |              |

| 図 5 ノイズ環境での入力保護                         |              |

| 図 6 ノイズの多い環境用の、組み込み過渡電圧保護機能             |              |

| 図 7 外付け485 フェイルセーフ回路                    |              |

| 図 8 オープン/ショートのフェイルセーフ                   |              |

| 図 9 絶縁された3.3V或いは5V RS-485ノード            |              |

| 図 10 プロセス制御設計の例                         |              |

| 図 12 オシロスコープ上のアイ・パターンの光跡                |              |

| 図 13 NRZランダム・コード・ジェネレータ                 |              |

| 図 14 信号送信品質の測定                          |              |

|                                         |              |

| 表目次<br>表 1 絶縁された3 3V或いは5V RS-485ノードのBOM | 12           |

| 大                                       | 17           |

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

#### 1 平衡型伝送路規格の必要性

本書では、業界で最も広く使用されている平衡型伝送路規格であるANSI/TIA/EIA-485-A(参考文献[1], [2]) (以降「485」と表記)に重点をおいて説明します。

485の主要な要素のいくつかを説明した後で、ある工場のオートメーション化を例にして、差動伝送構成の実装を紹介します。 また最後に、TIの485製品ラインの新製品を紹介し、必要に応じてその応用例も見ていきます。

シングルエンド型のドライバとレシーバを使用している場合、コンピュータ・システムのコンポーネントとペリフェラル間の距離が長く、しかもノイズが多い状況下でデータ伝送を行うことは、不可能ではないとしても、たいていの場合非常に困難です。 平衡型デジタル電圧インターフェイシングの推奨規格では、長尺伝送システムの要件に合った一般的なソリューションを設計エンジニアに提供します。

485は、平衡(差動)型のデジタル伝送路インターフェイスであり、TIA/EIA-232 (以降「232」と表記)の性能の向上を目的として開発されました。その長所は次の通りです。

- 高い信号速度 最大50Mビット/秒

- 長い伝送路長 最大1200メートル

- 差動伝送方式 ノイズ放射が少ない

- 複数のドライバとレシーバを接続できる

485のドライバ、レシーバ、トランシーバを採用したデータ伝送回路は、2つ以上の機器を経済的かつ堅牢に相互接続する必要のあるアプリケーションでは必ずといってよいほど使用されています。POS端末と中央コンピュータ間で485信号処理を行うことで可能になる自動在庫管理などは、典型的な応用例といえるでしょう。ノイズ結合が低いツイストペア・ケーブルを使用する平衡型信号処理と同相電圧範囲が幅広い485では、最大50Mビット/秒の信号速度でのデータ交換が可能になります。また、それよりも信号速度は低くなりますが、数キロメートルもの距離を隔てたデータ通信も可能になります。

485規格はその用途の多様さのために、様々な規格団体が策定する通信規格の物理層仕様として採用されつつあります。そのような例としては、TIのアプリケーション・レポート "the Interface Circuits for SCSI"(文書番号SLLA035)で取り上げている ANSI (American National Standards Institute)の小型計算機システムインターフェイス(SCSI: Small Computer Systems Interface)、Profibus規格、DIN測定バスなどがあります。

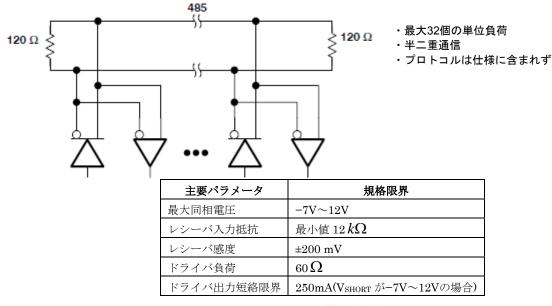

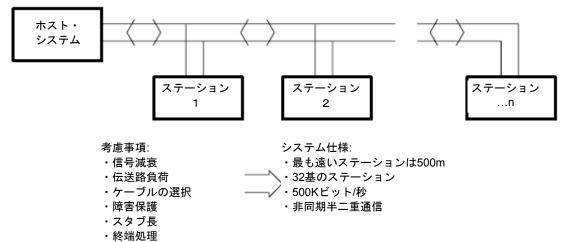

図1 485仕様の主要点

平衡型伝送路規格485は、ホスト・コンピュータ1台のデータ、タイミング、制御の各ラインと複数のペリフェラルを接続することを目的として、1983年に開発されました。この規格で仕様として定められているのは、(OSIモデルでいえば物理層の)電気的仕様のみです。プロトコル、タイミング、扱うデータの種類(シリアルかパラレルか)、およびコネクタは、すべて設計者が選択するか、上位規格に従って決定されます。

485規格はもともと、TIA/EIA-422規格(以後422と表記)をアップグレードして柔軟性を高めたバージョンとして定義されたものです。422では片方向通信(線路上の送信側と受信側が決まっていてデータの流れが一方通行)のみが可能であるのに対し、485では1本の線路上に複数のドライバとレシーバを配置して、半二重(双方向)通信を行うことが可能です(図1)。422同様、線路の最大長は仕様に定められていませんが、24AWGのケーブルをベースにしており、公称で約1.2kmとなっています。最大信号速度の制限はなく、232同様に、ビット時間に対する立ち上がり時間の比率によって設定されます。伝送線路の影響とノイズが原因で、信号速度はドライバよりもケーブル長によって制限される場合が多くなっています。

485方式と422方式の最も大きな違いは、ドライバの機能により、485では信頼性のあるマルチポイント通信が可能になっていることです。参考文献の[3]と[4]を参照して、数種類のバス規格を比較してみてください。

## 2 システム設計の考慮事項

## 2.1 伝送路負荷(Line Loading)

485規格では、伝送路終端処理(line termination)と、それに続く伝送路上の負荷の必要性が考慮されています。伝送路に終端処理を行う必要があるかどうかはシステムごとに異なり、また選択されている最大伝送路長と信号速度にも影響されます。

**伝送路の終端処理**: ある伝送線路を分布定数モデルと考えるべきか、集中定数モデルと考えるべきかを判断するには、ドライバ 出力側での信号の遷移時間  $t_t$  と、ケーブルを通過する信号の伝播時間  $t_p$  の関係を調べる必要があります。

$2t_{pd} \ge t_{r}/5$  であれば線路を分布定数モデルとして扱い、分布定数モデルに合わせて終端処理を行う必要があります。そうでない場合は集中定数モデルとして線路を扱うことができるため、終端処理の必要はありません。

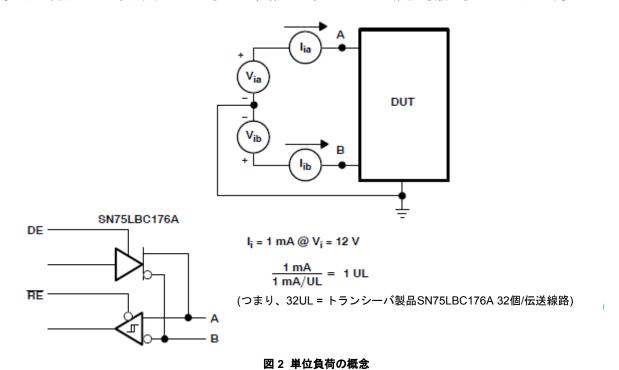

**単位負荷の概念:**1本の485通信バス上に配置できるドライバとレシーバの最大数は、単位負荷(UL)の定義に関連する、それらの負荷特性によって決まります。485規格の仕様では、線路1本あたりの最大UL数を32個と規定しています。

UL1個(ワーストケース)は、最大同相電圧ストレスが12Vの場合に1mA、あるいは-7Vの場合に0.8mAを流すことができる、安定した状態の負荷と定義されます。ULを構成する部品にはドライバやレシーバやフェイルセーフ抵抗などがありますが、AC終端抵抗がULの構成部品となることはありません。

図2は、SN75ALS176Bで使用するULの計算例です。このデバイスは内部でトランシーバとして接続されている(つまり、ドライバ側出力とレシーバ側入力が同じバスに接続されている)ため、ドライバ側の漏れ電流とレシーバ側の入力電流を別々に取得するのは困難です。この計算を行うために、レシーバ側の入力抵抗 $12\,k\Omega$ を基準として、トランシーバの電流を1mAとします。これを使用してUL1個を表すことができるため、最大で32個のデバイスを線路に接続できることになります。

ただし、すべてのレシーバの入力抵抗が $12\,k\Omega$  を超える値であり、したがって線路に負荷を追加できない場合にかぎっては、接続するレシーバの数を32個よりも多くすることができます。

## 2.2 信号の減衰と歪み

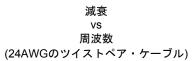

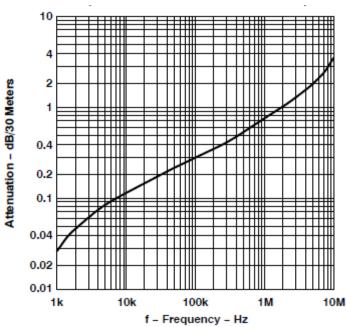

経験則から導き出された許容可能な減衰は、最大信号速度の単位がHzの場合は-6dBになります。たいていの場合、ケーブルのメーカーでは減衰の数値を公表しています。図3は、太さが24AWGのケーブルの「減衰の変化 vs 周波数」の曲線です。

- · DC抵抗+表皮効果

- ・近似と放射損失が原因の ノン・リニアリティ

- ・ケーブル・メーカーから 通常の方法で提供された詳細情報

経験則に導き出された減衰

-6dB (レシーバ側で測定) (ドライバ出力側の電圧の半分)

図3 信号の減衰

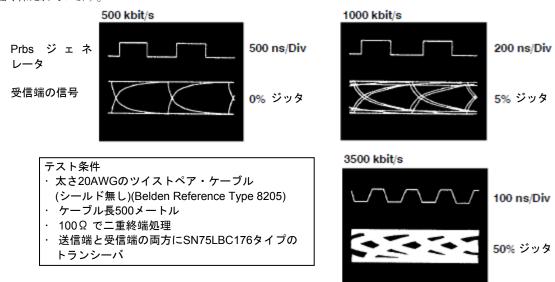

ランダム・ノイズ、ジッタ、減衰、ばらつきの影響がどの程度かを判断する最も簡単な方法は、アイ・パターンを調べることです。アイ・パターンを取得するための準備方法については、本書の「アイ・パターン」セクションを参照してください。図4は、信号速度を様々に変えて測定した、太さ20AWGのツイストペア・ケーブル500メートルの受信端の信号の歪みです。信号速度がこれ以上高くなるとジッタの影響が顕著になります。この場合は、1Mビット/秒でのジッタが5%になります。3.5Mビット/秒になると、信号が完全に消え始め、伝送の品質が大幅に劣化します。システムで許容可能なジッタの最大値は、通常では5%より低く保たれています。

図 4 485の信号歪み vs 信号速度

#### 2.3 障害保護とフェイルセーフ動作

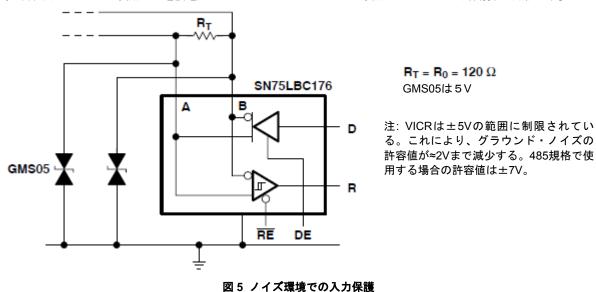

**障害保護**: どのシステム設計でもそうであるように、動作中に生じる自然の環境条件と人工的な環境条件の両方について考慮する必要があります。工場で制御されるアプリケーションは、通常は過剰なノイズ電圧から保護する必要があります。差動伝送方式自体にもノイズ耐性はあり、また485では幅広い同相電圧範囲をサポートしていますが、それだけでは不十分な可能性もあります。ノイズ電圧からの保護は色々な方法で実現可能です。最も効果的なのがガルバニック絶縁を利用する方法ですが、この方法については後述します。ガルバニック絶縁で可能になるシステムレベルの保護は優秀ですが、結果的にコストが高くなります。それより認知度が高く、費用も安く抑えられるソリューションが、保護ダイオードを使用する方法です。ただし、ダイオードを使用する場合は、ガルバニック絶縁ほど高い保護効果は望めません。外付けおよび組み込みの過渡電圧保護ダイオードの例を次の図に示します。

図5は、外付けダイオードを使用して過渡電圧スパイクから485トランシーバ製品SN75ALS176を保護する方法です。

RT は通常の終端抵抗であり、線路の特性インピーダンスRo の値に等しくなっています。

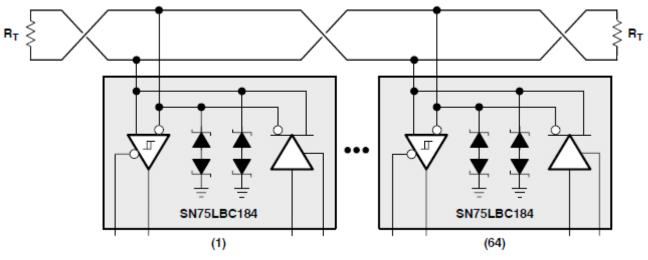

図6は組み込み過渡電圧抑制ダイオードです。これは、ボードのスペースにほとんど余裕がなく、しかも485のフルパフォーマンスが必要とされるアプリケーションで役立ちます。SN75LBC184(フットプリントは 'LBC176)には、高エネルギー過渡電圧

からの保護機能が組み込まれており、電気的にノイズの多い環境で役立ちます。

図 6 ノイズの多い環境用の、組み込み過渡電圧保護機能

- ・組み込み過渡電圧抑制機能付きトランシーバ

- ·ピークが400Wのパルスからの保護

- ・電気的にノイズの多い環境では250kbit/秒

- ・長めのスタブ向けに制御されたスルー・レート

フェイルセーフ動作:フェイルセーフ保護も、485アプリケーションの多くで必須とされる機能です。ただし、その有用性はアプリケーション・レベルで考慮され、理解される必要があります。

フェイルセーフ保護の必要性: 複数のドライバレシーバからなるパーティライン構成のインターフェイス・システムでは、駆動デバイスがアクティブでない期間が長くなります。この状態はライン・アイドル(line idle)と呼ばれ、ドライバの出力がハイ・インピーダンス状態になると発生します。ライン・アイドル中の線路の電圧はフローティング状態(つまり判定不可能 — 論理 Highでも論理Lowでもない状態)になります。その結果、ノイズの有無や、線路がフローティング状態になる直前にとっていた極性等が原因となってレシーバが誤起動され、論理Highか論理Lowになってしまう可能性があります。これは明らかに望ましくない事態です。レシーバにつながる回路で、この論理状態が有効な情報と解釈されるおそれがあるためです。このような状態を検知して、レシーバの出力を既知の定められたステートにすることが最良の解決策です。これを確実に行う方法をフェイルセーフと呼びます。フェイルセーフに求められるもうひとつの機能は、レシーバを線路の短絡から保護することです。短絡状態も、データ誤処理の原因となるおそれがあるためです。

ハード的にフェイルセーフを組み込む方法やプロトコルを使用する方法など、フェイルセーフ機能を実装する方法はいくつかあります。実装方法が複雑ですが、プロトコルの方が推奨できます。ただし多くのシステム設計者(この場合はハードウェア設計者)はハードウェアにフェイルセーフ機能を実装することを望むため、ハードワイヤード方式のフェイルセーフが採用される場合が最も多くなっています。

ハードワイヤード方式のフェイルセーフでは、信号のペアが互いに短絡されているか、それともオープン・サーキット状態かに 関係なく、レシーバの入力を横切る定義された電圧が必要になります。また伝送路終端器がある場合は、フェイルセーフ機能を 伝送路端の終端に組み込む必要があります。

内部フェイルセーフ: メーカーでは、ICに何らかの形態でオープン伝送路のフェイルセーフ回路を入れることで、フェイルセーフ機能の設計を可能にし始めています。多くの場合、追加する回路は、レシーバの非反転入力側の大きなプルアップ抵抗と、レシーバの反転入力側の大きなプルダウン抵抗のみです。この2種類の抵抗回路の値は通常 $100k\Omega$ 程度であり、伝送路終端抵抗(通常は $50\Omega\sim100\Omega$ )とつないで分圧器として使用すると、差動電圧がわずか数ミリボルトしか生成されなくなります。その結果、この電圧(レシーバ閾値電圧)では小さすぎて、レシーバのステートを切り替えられなくなります。つまり、これらの内部抵抗を効果的に使用しようと思うならば、伝送路終端抵抗を使用することはできません。伝送路終端抵抗を使用すると、許容範囲内の信頼性を持つ信号速度が大幅に低くなるためです。

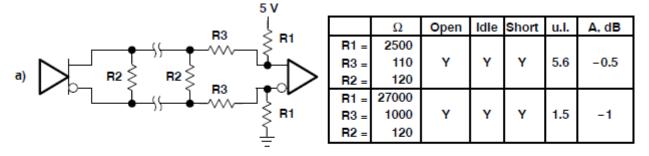

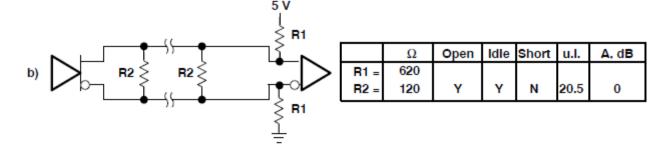

オープン伝送路状態と終端処理状態用の外付けフェイルセーフ機能:図7に、485の中継回路用の外付けハードワイヤード方式フェイルセーフ機能を提供するために使用される、一般的な回路をいくつか示します。各回路の目的は、レシーバ入力側での電圧を最小入力閾値よりも高い値に保ち、また3つの障害状態のうち1つ以上の状態下で既知の論理ステートを保つことです。どの図でも、R2は伝送線路のインピーダンス整合用の抵抗を表し、分圧器の一部となって安定した状態のバイアス電圧を生成します。各レシーバは、1ULを表すものとします。

回路図の右側の表に記載されている項目は、いくつかの標準的な抵抗値やコンデンサ値、提供されるフェイルセーフのタイプ、使用されるULの数、信号減衰です。次のセクションでは、伝送路短絡のフェイルセーフ回路用の抵抗値の計算について検討し、具体的な設計用に様々な値を変更する方法について考察します。

図7 外付け485 フェイルセーフ回路

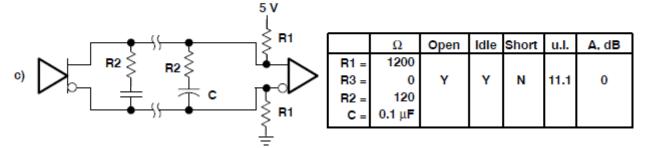

**伝送路短絡状態時の外付けフェイルセーフ回路**: 伝送路を短絡状態から保護するための回路を実装するには、抵抗を増やす必要があります。線路が短絡状態になると、伝送線路のインピーダンスがゼロになり、終端抵抗も短絡状態になります。レシーバに対する入力と直列に追加の抵抗を挿入することで、伝送路短絡状態フェイルセーフ保護回路を実装できます。

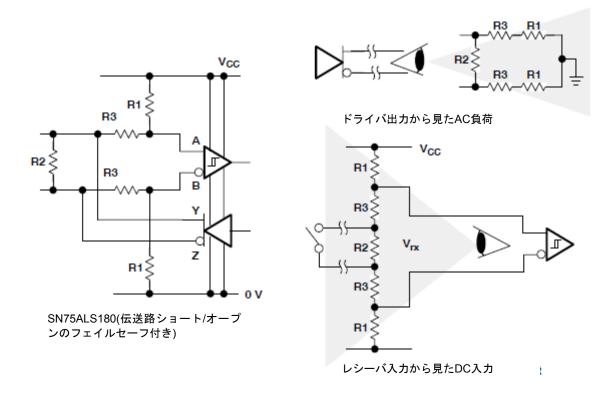

図8の抵抗R3を追加できるのは、ドライバ出力とレシーバ入力が分離しているデバイスを使用した場合のみです。トランシーバは内部で相互配線されており、伝送路短絡状態のフェイルセーフ回路を使用できません。この形態の保護回路をトランシーバで実装する必要がある場合は、ドライバ出力とレシーバ入力が分離しているSN75LBC180などのデバイスを使用する必要があります。トランシーバタイプのデバイスを使用している場合に抵抗R3を追加すると、出力信号の減衰が増加します。'ALS180のドライバ出力は伝送路に直接供給され、抵抗R3をバイパスします。

図8 オープン/ショートのフェイルセーフ

抵抗値の計算: 伝送路が短絡状態になった場合は、R2が回路から除去され、レシーバの両入力間の電圧が次の式で表される値になります。

$$V_{ID} = V_{CC} \times \frac{2R3}{2R1 + 2R3}$$

485アプリケーションでは、規格により、最大入力電圧閾値( $V_{IT}$ )を200mVより低い値と規定しています。したがって、既知のステートを仮定できるのは、 $V_{ID} > V_{IT}$  あるいは  $V_{ID} > 200$  mVである場合です。この条件が第一の設計制約になります。

$$V_{CC} \times \frac{2R3}{2R1 + 2R3} > 200 \text{ mV}$$

(1)

伝送路がハイ・インピーダンス・ステートに入った場合は、レシーバ側から見ると2つのR3が直列に接続され、R2プラス2つの R1が各R3の入力でプルアップとプルダウンを行っている状態です。この場合のレシーバ入力電圧は次の式で計算されます。

$$V_{ID} = V_{CC} \times \frac{R2 + 2R3}{2R1 + R2 + 2R3}$$

これにより、次のような第二の設計制約が生じます。

$$V_{CC} \times \frac{R2 + 2R3}{2R1 + R2 + 2R3} > 200 \text{ mV}$$

(2)

伝送路から見ると、有効な線路終端抵抗R2は2本のR1+R3と並列になっています。これは伝送路の特性インピーダンス $Z_0$ と一致する必要があります。したがって、次のような第三の制約が生じます。

$$Z_0 = 2R2 \times \frac{R1 + R3}{2R1 + R2 + 2R3}$$

(3)

その他の設計制約としては、フェイルセーフ回路に示された追加の伝送路負荷、R3とR1によって生じる減衰、レシーバの入力抵抗などがあります。

#### 注:

組み込み短絡/オープン回路フェイルセーフ機能については、485トランシーパ3.3Vファミリ製品SN75HVD10等の新製品を参照してください。

#### 2.4 ガルバニック絶縁

コンピュータと工業用シリアル・インターフェイシングは、ノイズが原因でデータ伝送の精度が深刻な影響を受けるおそれのある分野です。どのようなインターフェイス・システムのノイズ・パフォーマンスでも改善できることが証明された手段として、「ガルバニック絶縁」があります。

データ通信システムにおいては、ドライバ〜レシーバ間で直接ガルバニック接続を行わなくても、絶縁を行うことが可能です。トランスから生じる電磁結合によりシステム用の電力が供給され、TIの容量結合デジタル・アイソレータによりデータ接続が可能になります。ガルバニック絶縁はデータ線路からグラウンド・ループ電流を除去するため、データ通信を阻害するノイズ電圧も除去されます。この技術を使用すれば同相ノイズの影響や様々な形態の放射ノイズも無視できる程度にまで減らすことが可能です。

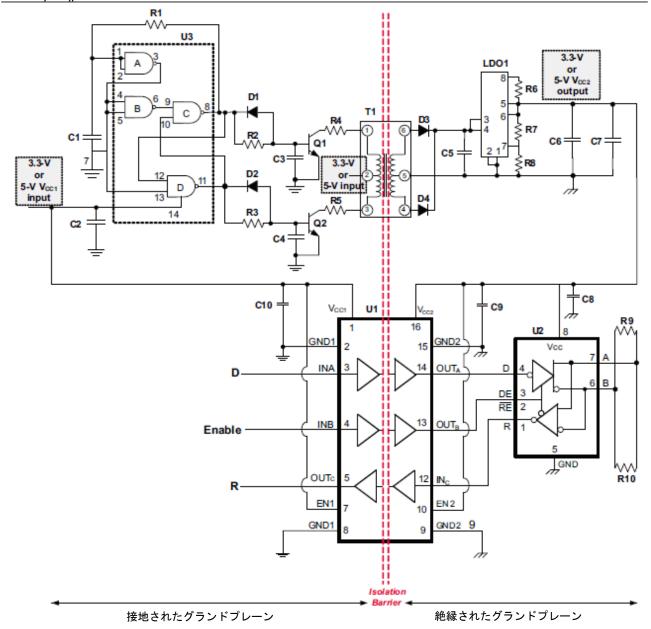

例として、あるプロセス制御システムの場合を考えてみます。この場合、図9に示すインターフェイス・モードにより、データ・ロガーとホスト・コンピュータが485リンク経由で接続されているものとします。

隣接する電気モーターが始動すると、サージ電流が原因で、データ・ロガーのグラウンド電位とコンピュータ間のグラウンド電位に瞬間的な差が生じる可能性があります。データ通信パスに何の絶縁対策もしていなければ、サージ・インターバルの間にデータが失われる可能性があり、最悪の場合はコンピュータに損傷が発生する可能性もあります。

回路の記述: 図9の回路図は、分散型制御調整(DSCRS)システムのインターフェイス 1 ノード分の構成です。この回路構成は、プロセス制御アプリケーションで使用できます。伝送は、ツイストペア・ケーブルとアース線をまとめてシールディングした2線式バスを介して行われます。このタイプのアプリケーションでは低消費電力が役に立ちます。多くのリモート・アウトステーションはバッテリで駆動されているか、バッテリによるバックアップ機能が必須だからです。さらに、低消費電力であれば、絶縁トランスが非常に小さくてすみます。図9のバス・ドライバにはSN65HVD10、或いはその他のTI製3.3V低消費電力トランシーバが使用できます。もちろん他の3.3や5VのRS-485、3.3VのTIA/EIA-644 (LVDS)、或いは3.3VのTIA/EIA-889 (M-LVDS) トランシーバを使用することもできます。

**動作理論**: 図9はデジタル・アイソレータと絶縁トランスを使用した3.3V或いは5Vのガルバニック絶縁の例です。485トランシーバでは絶縁電源から電力を取る必要があるため、出力調整可能LDO電源のTPS7101も絶縁する必要があります。これは、絶縁トランスを駆動しているNANDゲート発振回路によって実現されます。トランスの出力は整流とフィルタ処理を経て、レギュレータの入力として使用されます。EMI環境が厳しい場合はよくこの方法を使用して、ノイズが主電源に結合することを防ぎ、同じ電源に接続された他のサブシステムにノイズが回らないようにします。また、TPS7101は500mAの供給能力があるので、他の回路にも電源を供給することが可能です。バイアス抵抗を調整することにより3.3V或いは5V電源に構成可能です。

データ伝送路のガルバニック絶縁は、3回路入りデジタル・アイソレータISO7231Mで与えられます。このアイソレータは、その特性である最大150Mbps信号速度や、標準25nsと小さい伝播遅延、 $2.5 \mathrm{kV}$  (rms) の電圧絶縁能力、標準50kV/ $\mu$ sの電圧遷移耐性から選ばれました。ISO7231Mは入出力間で高い絶縁耐圧の必要な高速デジタル・インターフェィスで使用できるように設計されています。大きなグランド・ノイズや誘導ノイズの環境での使用を強くお勧めします。

図9に示した機能すべてを単体で提供する部品も入手可能です。しかし、このディスクリート構成では電源絶縁が大幅に向上しており、また費用もずっと少なく抑えられています。

図 9 絶縁された3.3V或いは5V RS-485ノード

この回路には、SN65HVD10のようなTI製3.3Vトランシーバ、或いはSN75LBC176Aのような5V製品が使えます。

| 照番号   | 記述                            |

|-------|-------------------------------|

| U1    | ISO7231M デジタル・アイソレータ          |

| U2    | 3.3V 又は 5V RS-485 全二重トランシーバ   |

| U3    | SN74HC132 クワッドNAND            |

| LDO_1 | TPS7101 出力可変LDO電源IC           |

| R1    | 抵抗, 2k $\Omega$ , 1/4 W, 1%   |

| R2,R3 | 抵抗, 1k $\Omega$ , 1/4 W, 1%   |

| R4,R5 | 抵抗, 10 $\Omega$ , 1/4 W, 1%   |

| R6    | 抵抗, 250k $\Omega$ , 1/4 W, 1% |

| R7        | 3.3V 出力抵抗, 309kΩ, 1/4 W, 1%           |

|-----------|---------------------------------------|

|           | 5V 出力抵抗, 549k Ω , 1/4 W, 1%           |

| R8        | 抵抗, 169k $\Omega$ , 1/4 W, 1%         |

| R9,R10    | 抵抗, 120 $\Omega$ , 1/4 W, 1%          |

| C1,C7     | コンデンサ, 0.01 $\mu$ F, 100 V, 10%       |

| C2        | コンデンサ, 0.001 $\mu$ F, 100 V, 10%      |

| C3,C4     | コンデンサ, 100pF, 100 V, 10%              |

| C5        | コンデンサ, 1 $\mu$ F, 100 V, 10%          |

| C6        | コンデンサ, 47 $\mu$ F, 100 V, 10%         |

| C8,C9,C10 | コンデンサ, 0.1 <i>μ</i> F, 100 V, 10%     |

| D1,D2     | ダイオード, 1N4148                         |

| D3.D4     | ダイオード, 1N5817                         |

| Q1,Q2     | トランジスタ, 2N2222                        |

| T1        | トランス, TGRTI340NA, haloelectronics.com |

表 1 絶縁された3.3V或いは5V RS-485ノードのBOM

# 3 プロセス制御設計の例

485システムの設計についてさらに深く知るには、具体例を調べることが効果的です。ホスト・コントローラ1つと、複数のアウトステーションからなる工場オートメーション・システムを考えてみましょう。各アウトステーションでは、データの送信と受信の両方が可能であるものとします。

システムの機能は次の通りです。また、システムの全体的な仕様を図10に示します。

- 最も遠いアウトステーションは、ホスト・コントローラから500mはなれています。

- 線路上には31基のアウトステーションが必要です。(ホスト・コントローラも含めて全部で32ステーション)

- システムの信号速度は500Kビット/秒です。

- 信号ペアを1組だけ使用して、半二重モードでデータ伝送を行います。

図 10 プロセス制御設計の例

485規格に従った方法で、設計目標である500Kビット/秒でデータを送信することは、ユニット・インターバル (UI)の0.3倍よりも短いドライバ出力遷移時間があれば可能です。これにより、次式で遷移時間の上限を求めることができます。

$t_t \le 0.3 \times UI$

$$t_t \le 0.3 \left( \frac{1}{500 \times 10^3} \right)$$

## t, ≤ 600 ns

位相速度が真空における光速に等しいケーブルが入手できたとすると、ケーブルの伝播遅延 tpd は、3.33 ns/mに500mを乗じたもの、つまり1667 nsになります。伝送路として扱うかどうかの判断基準をチェックすると、次のようになります。(セクション2.1を参照)

$$2t_{pd} \ge \frac{t_t}{5}$$

#### 3333 > 120

可能な範囲で最低速の信号遷移と最高の位相速度を考えると、伝送路として扱う必要があります。さらに、実世界の部品を使用して試しても、この場合に使用する半二重伝通信用伝送線路500mの両端には終端処理をする必要があるという事実を改めて確認するだけの結果になるでしょう。

減衰に関する限り、500Kビット/秒の信号速度の基本周波数は250kHzですが、500kHzでの減衰は信号の高周波数成分を含むように選択されます。500メートルのケーブルの場合、6dBルール(セクション2.2参照)を使用すると、許容可能な最大減衰は0.36dB/30メートルになります。図30グラフで示すように、減衰は0.5dB/30mより少し高い値であり、設計制約を0.14dB/30mだけ超過しています。これは、この例では問題になりません。控えめな経験則に基づいたものよりも少し少ないノイズ・マージンで動作することは容認できるためです。

## 4アイ・パターン

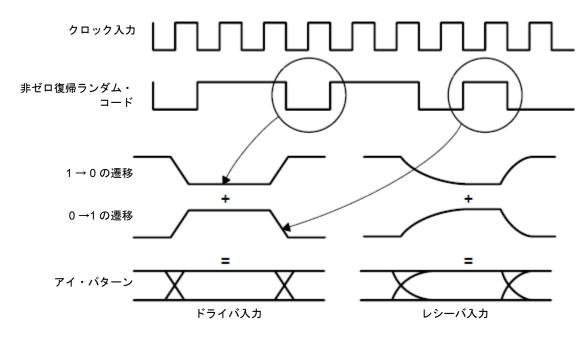

信号歪み、ノイズ、信号減衰と、その結果データ伝送システムで起こるシンボル間干渉 (ISI)の影響を測定するには、アイ・パターンを使用します。ISIは、連続したパルス列内で先行パルスが後続パルスに干渉することで生じる影響です。ISIが発生すると、隣接したパルス同士の区別を適切に保つために、任意の線路長の信号速度が強制的に下げられます。アイ・パターンはオシロスコープの画面上に表示されますが、その光跡が目(eye)のような形をしていることから「アイ」という用語で呼ばれます。

#### 4.1 アイ・パターンの取得準備

アイ・パターンは、疑似ランダムNRZコードをテスト対象の伝送路で送信することによって得られます。これは考えられるほとんどすべてのパルスの組み合わせを表します。伝送路の受信端の信号はオシロスコープの垂直アンプに接続され、別のトレース上にあるNRZコード・ジェネレータの同期クロックを使用してスコープにトリガーがかけられます(図11参照)。

アイ・パターンの形成

図 11 アイ・パターンによる信号の歪み

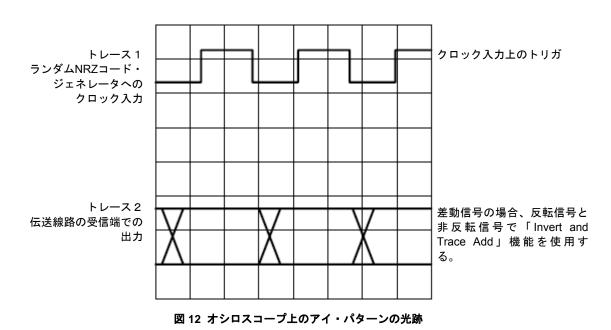

疑似ランダム・コード・ジェネレータでは、任意の1ユニット・インターバルにわたって信号の組み合わせを生成する必要があります。その後、結果の信号をオシロスコープに表示することが可能です。各ユニット・インターバルでのアイは、図12に示すアイと同じ形である必要があります。差動伝送の場合、伝送路の両端の信号をオシロスコープ上の別々のアンプに印加して、オシロスコープの加算機能を使用して合成します。

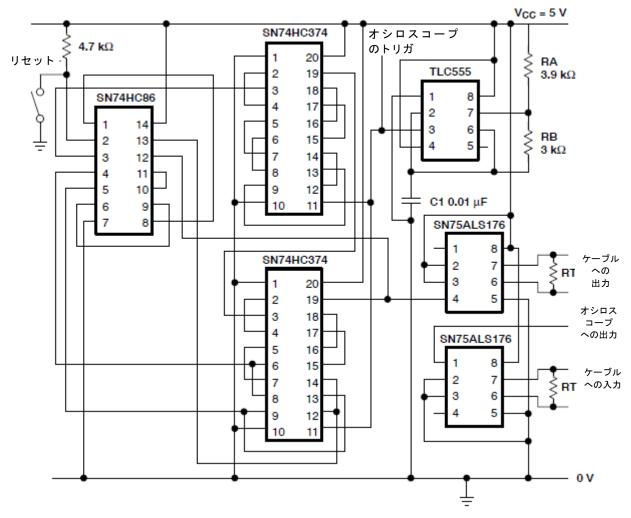

図13は、NRZコードを生成する回路です。この場合は、485のSN75176タイプのトランシーバをテストするために使用されました。

図 13 NRZランダム・コード・ジェネレータ

#### 4.2 アイ・パターンから測定値を得る

実際に測定値を得る前でも、伝送システムの大体のパフォーマンスはまずアイ・パターンを調べてみるだけで分かります。 アイの開口度は送信信号の品質を示しており、またノイズおよび歪みに対するシステムの許容範囲を示すものでもあります。

実際の測定では、トランシーバの判定点をアイ・パターンに重ね合わせる必要があります。判定点と信号軌跡間の垂直方向の距離は、システムのノイズ・マージンの近似標識です。アイの水平方向の外観は、システムの最大時間ジッタの判定に使用できます。最大許容可能ジッタは、受信回路のタイミングの確度に依存します。

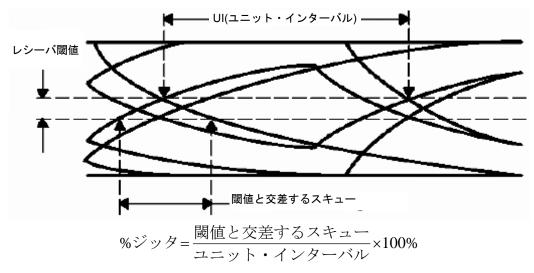

「信号速度対線路長」の曲線を判定するためにケーブル・メーカーが従来から使用している指針が、「5%ジッタ以下である」ということです。パーセント・ジッタとは、図14に示すように、閾値を横切るスキューの、ユニット・インターバルに対する比率と定義されます。信号の周波数、ノイズ、クロストークなど、ジッタが発生する要因は数多く存在します。50Hzのハムノイズや、他の低周波源からのノイズなどのノイズ周波数は、送信信号を変化させる可能性があります。また、閾値にずれがあると、検出されたパルス幅がその影響で大幅に減少するため、受信信号に深刻な問題が発生するおそれがあります。

図 14 信号送信品質の測定

## 5 参考文献

- 1) ANSI TIA/EIA-485-A Electrical Characteristics of Generators and Receivers for Use in Balanced Digital Multipoint Systems, Global Engineering Documents, www.global.ihs.com

- 2) TSB89 Application Guidelines for TIA/EIA-485, Global Engineering Documents, www.global.ihs.com

- 3) 422 and 485 Standards Overview and Systems Configurations, Texas Instruments Application Report (literature number SLLA070), <a href="https://www.ti.com">www.ti.com</a>

- 4) Comparing Bus Solutions, Texas Instruments Application Report, (literature number SLLA067), www.ti.com

## 6 要約

Texas Instruments製品の485ドライバ、レシーバ、トランシーバを使用したデータ伝送回路は、2つ以上のデバイス間で耐久性 のある(rugged)経済的なインターフェイスを必要とするあらゆるアプリケーションで使用できます。485での平衡差動信号と広 い同相電圧範囲があれば、信号速度が最大50Mビット/秒にもなる、低ノイズで信頼性のある通信チャネルを構築して、最大で 1200メートルも離れた地点間で通信を行うことができます。

伝送線路の終端処理や回路負荷といった設計詳細に配慮することにより、多様なアプリケーションでのパフォーマンスを最適な ものにできます。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

# 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上