# オペアンプのマクロモデル: 比較の一例

#### Bonnie Baker

オペアンプ市場の主な競合他社はすべて、Spiceベースのマクロモデルを顧客に提供しています。これらのモデルは、設計者が回路の初期特性評価と、ある程度のシステム・トラブルシューティングを行うためのツールを提供します。

シミュレーションの時間をより短くし、CPUのメモリ要件をより低くする目的で、大多数のオペアンプのパフォーマンス特性をシミュレートするためのマクロ・トポロジー(マクロ結線構成)が開発されてきました。従来から使用されてきたマクロモデル作成のためのアプローチはいくつかありますが、どのアプローチを使用して生成されたマクロにも、それぞれ長所と短所があります。

回路シミュレーションは、システム・レベル設計者にとっ てますます重要なものになっています。マクロを使用する ことで、設計者は自分の設計の全体的な限界を短時間で判 断し、回路で問題が発生する原因になりそうなことを、事 前にコンピュータの端末上で迅速に修正することができま す。試作基板を回路シミュレーションに置き換えることを 推奨するわけではありませんが、コストのかかる設計問題 の多くは、シミュレーション・サイクル中に迅速に特定す ることが可能です。マクロモデルをシミュレーション・ ツールとして使用することで、設計者が自分の回路の設計 サイクルを短くすることも可能になります。これはもちろ ん、設計の制約事項とトレードオフに対してモデルの精度 水準が適切であることが前提となります。シミュレーショ ンの段階で選択されたマクロの機能と限度についてシステ ム設計者が分かっていれば、設計サイクル全体を大幅に短 縮することが可能になります。

基礎的なマクロモデルの構成に対して容易に実装できる強化処置を施せばマクロの欠点も大部分は克服できます。ただしこれは、具体的なアプリケーションの要件に依存します。

適切な強化処置を施した正確なモデルを適切に選択することにより、設計者がオペアンプのマクロモデルを、システム・レベル回路設計での有効なツールとして使用することが可能になります。

歴史的に見ると、SPICE<sup>(1)</sup>等の回路シミュレーション・ツールは、集積回路の設計者用に開発されたものです。 SPICEでは詳細な数式を使用して、実際のデバイスの動作をエミュレートします。回路設計サイクル中に、IC設計者はSPICEのようなシミュレーション・ツールを縦横に使用します。

IC回路設計者が必要とする精密度水準は、どの部品も、実際のパフォーマンスに可能な限り近くなるようにシミュレートできるというものです。結果として、シミュレート対象回路の部品の大部分はバイポーラ・トランジスタやフィールド効果トランジスタ(field-effect transistors)等のノンリニア部品となります。Spiceシミュレーション環境にあるこれらのノンリニア部品の動作は複雑であるために、これらの部品についてはより多くのシミュレーション時間とコンピュータのメモリが必要になります。集積回路の複雑さ、パフォーマンス、サイズが増大するにつれて、シミュレーション時間とコンピュータ・メモリは、IC設計者の使用するソフトウェアとシステムのクリティカルなシミュレーション制約要因になってきました。

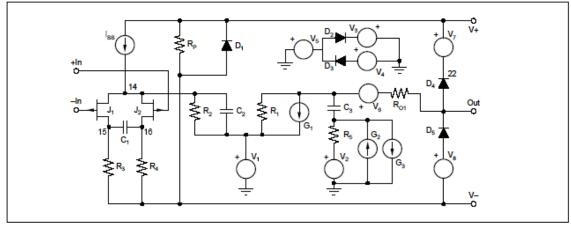

図1. オペアンプのシミュレーションに使用されるボイル・マクロモデル

SBOA027翻訳版

確認下さい

JAJA196 www.tij.co.jp

この制約のために、システム・レベル設計者がIC設計者と同じシミュレーション・ツールを十分に利用することができなくなりました。その結果、システム・レベルでの回路シミュレーション用の代替ツールとして、マクロが人気を獲得することになったのです。オペアンプのマクロは、各モデルに特化した、既定のアンプの特性として設計されます。Spiceが推奨ソフトウェアとして使用される場合は、オペアンプのマクロは通常、2つの基礎的な設計アプローチのうちどちらかを使用して開発されます。

## マクロモデル設計アプローチ

基礎的なマクロモデル設計アプローチの第一番目としては、回路の複雑さを減らすこと等があります。例えば、オペアンプの入力段は、電流源でバイアスをかけた負荷抵抗を持つ差動ペアに縮小することができます。アクティブな負荷を持つカスコード接続型差動入力を実際のオペアンプに付けることも可能です。また、入力段にバイアスをかける電流源の構築には、初期電圧とコレクタ抵抗等に関してノンリニアリティを持つトランジスタが使用されます。

マクロモデル回路全体では、それほど重要でないとみなされるトランジスタは、電流源や抵抗等の単純なリニア要素に置き換えられ、この単純化により回路中のノード数やノンリニアの部品も減らすことができます。この両方が減少すれば、シミュレーション時間が短縮されることになるためです。

さらにシミュレーション時間を短縮するために、トランジスタは可能な限り理想に近づけます。これは、トランジスタのモデル・パラメータ数を減らすことで可能になります。このマクロモデル設計アプローチの明白な長所が、シミュレーション時間の短縮です。ただし、オペアンプのミュレーション能力はある程度低下します。例えば、前述のモデルの入力段では、アンプの同相電圧入力範囲を正しく表したものにはなりません。

マクロモデリングに使用される第二の方法は、構築法です。この方法を使用する場合は、マクロの設計者はオペアンプのパフォーマンスを特性化して、抵抗、インダクタ、コンデンサ、従属電源、独立電源等の理想的なリニア部品からマクロを構築します。このトポロジーの良い例が、

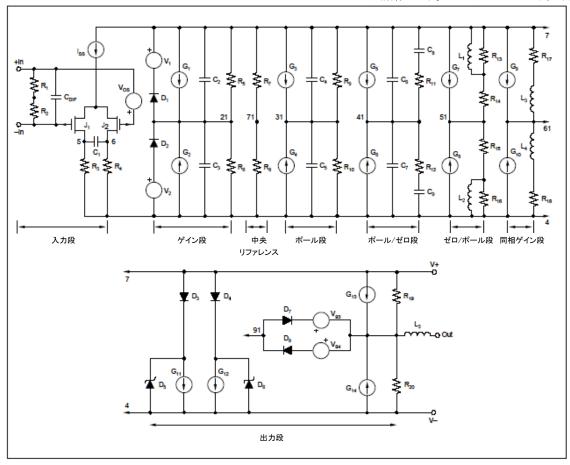

図2. MPZオペアンプのマクロモデル・ブロック図。マクロモデル設計では、重複したフェーズ・ブロックも可能です。

www.tij.co.jp JAJA196

アンプの入力段が抵抗になっている、オペアンプの複合型 piモデルです。

その抵抗を通る電圧は、ゲイン段等によりセンシングされます。このタイプのモデルのシミュレーション時間は、最初のマクロモデル設計方法よりも大幅に短縮されます。ただしこのアプローチでは、オペアンプのパフォーマンスの低下も大幅になります。

## ボイルのオペアンプ・マクロモデル

ボイルのオペアンプ・マクロモデル<sup>(2)</sup> は、入力段設計用の 簡素化法と、入力段設計以外のマクロ設計用の構築法を使 用して設計されたものです。

図1に示すように、ボイル・モデル中に一組だけあるトランジスタ群は、オペアンプの入力差動ペアに使用されます。その他の部品は、クランプとして使用される数個のダイオードを除いてすべてリニア・デバイスです。このモデル・トポロジーでシミュレートするACパラメータは、スルー・レート、ユニティ・ゲイン周波数、1極または2極アンプのゲイン/フェーズ、および簡素化されたAC出力抵抗です。

モデリングされるDC特性は、ゼロ入力電流、短絡出力電流、出力電圧振幅の最大値および最小値、入力バイアス電流、同相電圧除去比、およびDC出力抵抗です。これらのボイル・マクロモデル・パフォーマンス特性は、多くの一般的なアプリケーションにとって十分なものとなります。ただし、ボイルのマクロ・トポロジーではモデル化されていない温度特性、同相電圧入力範囲、オフセット電圧、オフセット電流、入力保護、電源除去比、ノイズ、THD、入力インピーダンス、良好なAC出力抵抗、および電源電流対電源電圧における変化などは、より重要なパラメータになることは少なくありません。

自社のマクロの設計にボイルのトポロジーをそのまま使わないことにしているオペアンプ・メーカーもあります。ボイル・モデルを使用しているメーカーを調査したところ、調査対象となったすべてのメーカーではボイル・モデルが強化され、オペアンプのパフォーマンス特性がいくつか追加されていました。

# 複数ポール/ゼロ・マクロモデル

両方のマクロモデリング手法を使用したもうひとつの一般的なトポロジーを図2に示します。図2のモデルとボイル・モデル (図1)の入力段は同一ですが、その他の段はすべて異なっています。このトポロジーはいくつかのソース<sup>(3,4)</sup>を発展させたものであり、モデルの中央部の形状にちなみ、複数ポール/ゼロ(MPZ)・マクロモデルという名前がついています。このモデルの中央部を拡張して、ポール段、ポールゼロ段(またはゼロポール段)を追加することもできます。

入力オフセット・バイアス電流、入力オフセット電圧、入力差動インピーダンスと同様に、MPZマクロのDCパフォーマンス特性も、ボイル・モデルと同じです。このモデルのトポロジーがシミュレートするACパラメータは、スルー・レート、ユニティ・ゲイン周波数、複数ポール/ゼロ・アンプのゲイン/フェーズ、CMRR対周波数、および簡素化されたAC出力抵抗です。

加えて、ゼロ入力電流でのMPZマクロモデルの変化対電源電圧の変化にはグランウンド・リファレンスがなく、電源間の出力電流をグラウンドから吸い込んだり吐き出したりするかわりに、分割します。MPZの限界としては、温度特性の欠如、同相電圧入力範囲のモデリングが弱いこと、入力保護回路の無いこと、電源除去比の無いこと、ノイズの無いこと、THDの無いこと、およびAC出力が単一のゼロ構成でモデリングされていることなどが挙げられます。

# ボイルのマクロモデル対 MPZ マクロモデル

オペアンプのマクロのパフォーマンスを比較する場合に、システム設計者にとって決定的に重要となるシミュレーション特性が2つあります。第一にマクロは、設計者の関心対象であるアプリケーションにおいて、オペアンプの電気的性能をモデリングする必要があること、第二にマクロは、妥当な量のコンピュータ・メモリを使用して、妥当な長さの時間でシミュレーションを行う必要があることです。

ボイル・モデルとMPZモデルの電気的性能を比較する場合、MPZモデルではボイル・モデルにはないいくつかの付加的なパフォーマンス特性を提供します。例えばMPZモデルでは、ボイル・モデルでモデリングされるのと同じDCパラメータをモデリングする上に、さらに入力オフセット電圧と入力オフセット・バイアス電流のモデリングも行います。MPZマクロには、レベルシフト回路で役に立つこともあるグラウンドへのリファレンスがありませんが、ボイル・モデルの回路中にはいくつかのグラウンド・リファレンスがあります。

加えてMPZマクロでは、グラウンド・ノードではなく電源のノードから出力電流を引き込みます。これは、電源の要件を評価する際に役立ちます。ただし、MPZマクロの真の能力は、ACの領域において発揮されます。オペアンプの伝達関数の中に極が2つ以上ある、および/または追加のポール/ゼロ・ペアがある場合は、ボイル・モデルではオペアンプをシミュレーションして適切な動作を行うことができません。

JAJA196 www.tij.co.jp

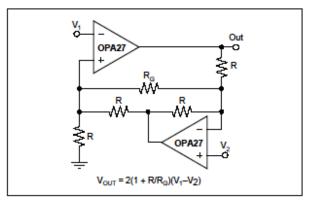

#### 図3. 業界標準製品OPA27を使用した計測アンプ

これを実際に示してみせるために選択されたのが、図3のアプリケーションです。オペアンプ・マクロモデルのAC 確度を判定するためのテストのうち、推奨されることの多いテストは、オペアンプのユニティ・ゲインの過渡応答をシミュレーションしたものと、実験用作業台でのデバイスの実際のパフォーマンスを比較するというものです。これは、マクロモデルのACパフォーマンスを検証する場合の良いスタートとなりますが、大多数のマクロは、伝達関数のゼロ交差点 (0dB) で正確なゲイン/フェーズを持つように最適化されています(図4、5参照)。

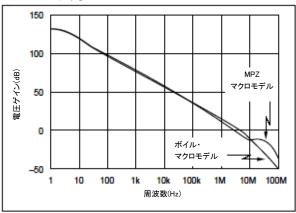

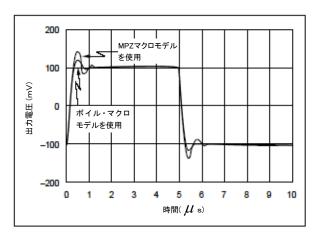

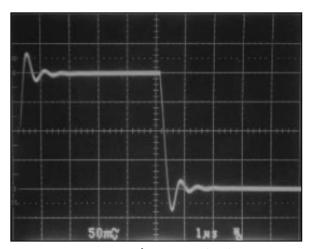

構成を様々に変えてオペアンプのマクロモデルを動作させ る必要のあるアプリケーションの場合は、MPZマクロモデ ル・トポロジーの真の能力を容易に示すことができます。 そのために、業界標準のオペアンプであるOPA27を使用し ます。図3に示すシミュレーションの結果を、図6に示しま す。図6では、2つのオペアンプによる計測アンプの位相余 裕をMPZマクロ(オーバーシュート19.2%)ではモデリング に成功していますが、ボイル・モデル(オーバーシュート 9.3%)でのモデリングは失敗しています。図7のオシロス コープ写真では、このアプリケーションではMPZマクロの 方がより正確な結果を出せることを実証しています。ただ しボイル・マクロを使用した場合は、シミュレーション時 間とコンピュータ・メモリの使用量の点でMPZマクロより も優れたパフォーマンスが示されます。オペアンプひとつ だけのシミュレーションであれば、これは重大な問題とは なりませんが、複数のアンプを使用するアプリケーション では、MPZマクロの場合は強力なCPUが必要になりま す。計算収束の問題(解の発散)がマクロに存在しないも のと仮定すると、動作点の計算は大まかに言って、ネッ ト・リストに指定された回路素子の数の関数になります。 オペアンプの複雑度が増すと、MPZマクロでのシミュレー ション時間もすぐに長くなります。同様に、素子がひとつ 増えるたびに、AC解析における計算時間も増加します。 過渡解析の定量化は、関わる要因が多いため、これよりも ずっと難しくなります。主な要因となるのは、過渡反復の 回数と、各計算に必要な結果の精度です。 多くの事例の MPZマクロでは、プログラマ側でSpiceの.OPTIONSス テートメントの変数2つのデフォルト値を変更して、反復

数を10から40(ITL4)に増やし、相対誤差許容範囲を0.001 から0.01 (RELTOL)に変更する必要があります。マクロモデルから得られるACパフォーマンスの精度を重視しない設計では、ボイル・モデルを選択したほうが良い結果が得られるでしょう。

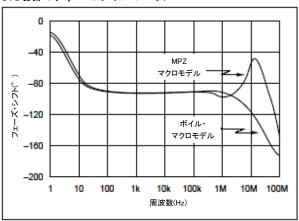

図4. OPA27のボイル・マクロモデルとMPZマクロモデルを使用 した場合の、Spiceのゲイン・プロット

図5. OPA27のボイル・マクロモデルとMPZマクロモデルを使用 した場合の、Spiceのフェーズ・プロット

図6. 図3に示した計測アンプの小信号過渡応答のSpiceシミュレーション

www.tij.co.jp JAJA196

図7. 図3に示した計測アンプの小信号過渡応答のオシロスコー プ写真

# 参考文献

- (1) Antognetti, Massobrio, Semiconductor Device Modeling with Spice, McGraw-Hill, 1988.

- (2) Boyle, Cohn, Pederson, et al, "Macromodeling of Integrated Circuit Operational Amplifiers," IEEE Journal of Solid State Circuits, Vol. SC-9, No. 6, December, 1974.

- (3) Tabor, Siegel, "Macromodels Aids in Use of Current-Mode Feedback Amps," Electronic Products, April, 1992

- (4) Alexander, Bowers, "Designer's Guide to Spice-Compatible Op-Amp Macromodels Part 1," Electronic Design News, Volume 35, No. 4, February 15, 1990.

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上