# Audio Serial Interface Configurations for Audio Codecs

Jorge Arbona, Uttam Agarwal

Audio Converter Products

### ABSTRACT

An audio serial interface (ASI) provides a means to transfer non-buffered audio data between processors and/or audio converters. These data are typically encoded in PCM twos complement format, although other format variations may be possible to achieve companding for lower data rate transfers. Audio converters based on the delta-sigma ( $\Delta\Sigma$ ) architecture require an internal master clock that operates at a much faster rate than the target sample rate. Although there are several means to obtain this master clock, care must be taken to ensure that this clock does not drift with respect to the ASI. This report discusses several configurations that prevent such situations.

#### Contents

| 1 | Introduction       | 1 |

|---|--------------------|---|

| 2 | ASI Configurations | 2 |

#### List of Figures

| Repeated Sample (Master Clock Slower than Ideal)   | 2                                                                                                                                                                                    |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASI Slave Mode                                     | 3                                                                                                                                                                                    |

| ASI Slave Mode (Independent Master Clock)          | 4                                                                                                                                                                                    |

| ASI Slave Mode (Generating Master Clock from BCLK) | 4                                                                                                                                                                                    |

| ASI Master Mode                                    | 5                                                                                                                                                                                    |

|                                                    | Repeated Sample (Master Clock Slower than Ideal)   ASI Slave Mode   ASI Slave Mode (Independent Master Clock)   ASI Slave Mode (Generating Master Clock from BCLK)   ASI Master Mode |

## 1 Introduction

Each system has different requirements when it comes to interfacing to an audio codec ASI. The most common configurations are the master and slave modes. When the audio codec ASI is configured in master mode, its bit clock (BCLK) and word clock (WCLK) pins are output. In slave mode, BCLK and WCLK are inputs to the codec ASI. This relationship might seem straightforward. However, care must be taken when the ASI is configured in slave mode to ensure that the oversampled data that are decimated always fall within the correct target rate time slot.

If a master clock is a free-running clock and it is fed to a converter, it will not be frequency-locked to the frame clock (WCLK) of an independent ASI. Any deviation from the ideal will eventually result in a skipped or repeated sample (assuming that the architecture repeats samples). For example, if a host processor provides an ideal 48-kHz WCLK with respect to absolute time, its respective ideal master clock could be exactly (128 • WCLK) = 6.144 MHz. If a master clock from a non-ideal crystal is provided directly to the converter modulator with a 0.001% error, this clock could result in 6.14393856 MHz. Eventually this slower clock will result in a repeated sample out of the ASI bus. Of course, there is no such thing as an ideal master or ASI clocks.

All trademarks are the property of their respective owners.

www.ti.com

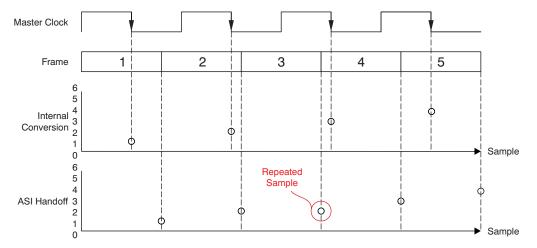

Figure 1 illustrates a simplified case in which a hypothetical analog-to-digital converter (ADC) operating at Nyquist frequency (for simplification purposes) results in a duplicated sample on the ASI bus. In this example, the hypothetical converter ideally hands over its data on the middle of a frame on the falling edge of the master clock. These data should then be ready to be transferred in the beginning of the next frame. As shown in Figure 1, the master clock is actually slower than the ideal. This configuration will eventually drift the clock enough (with respect to the ASI frame) such that there will be a frame that will not receive new data (as shown at the end of frame #3).

Figure 1. Repeated Sample (Master Clock Slower than Ideal)

If the master clock is faster than the ideal, then two ADC samples may be written within a single frame resulting in a skipped sample through the ASI bus. For DAC data received from the ASI bus, a faster modulator clock than the ideal will result in duplicate samples and a slower modulator clock will result in skipped samples at the modulator output.

# 2 ASI Configurations

As a general requirement, the internal master clock of a converter must be frequency-locked with the ASI frame clock (typically available through WCLK pin). This condition does not mean that the master clock and the ASI frame need to be phase-locked. What is important is that these clocks do not drift over time with respect to each other.

In TI's AIC family of devices, the ASI is composed of a bit clock, word clock, data in, and data out. The bit clock (typically the BCLK pin) clocks DOUT (ADC) data, and latches DIN (DAC) data for each word clock (WCLK) frame. The ASI bus has timing requirements itself (which can be found in the respective device data sheet). However, these are not related to the MCLK, only to the ASI itself.

www.ti.com

# 2.1 ASI Slave Mode

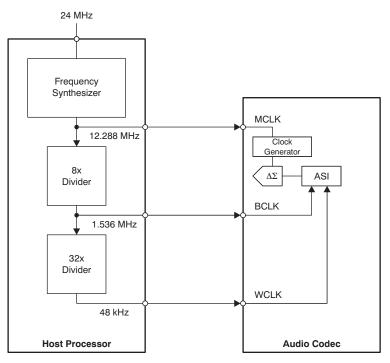

In slave mode, the host processor generates the bit clock and word clock from a system clock. To obtain an audio clock, the system clock is often synthesized to a number divisible by 44.1 kHz or 48 kHz. Figure 2 shows such example. This configuration ensures that the frame clock (accessible at the codec WCLK pin) will not drift with respect to the master clock generated by the frequency synthesizer.

Figure 2. ASI Slave Mode

For cases where a master clock output is not available, obtaining the audio codec MCLK directly from the frequency synthesizer source (for example, 24-MHz clock shown in Figure 2) may or may not be suitable in some applications. Some hosts may receive another clock, such as a USB start of frame (SOF) tick, as a reference which may continually change the phase of the ASI bus relative to the external clock.

ASI Configurations

www.ti.com

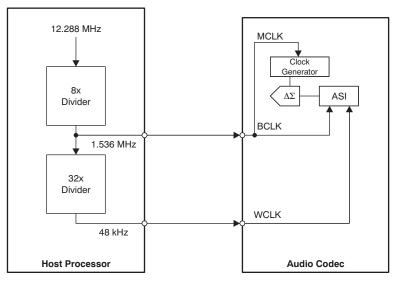

Figure 3 shows a configuration that should be avoided. Because the crystal and the frame clock are independent of each other, they will eventually drift and cause skipped and/or repeated samples.

Figure 3. ASI Slave Mode (Independent Master Clock)

Some audio codecs, such as the <u>TLV320AIC3254</u> and <u>TLV320AIC36</u>, are capable of deriving the internal master clock from an external BCLK, as shown in Figure 4. However, BCLK must be fast enough to be within the codec PLL input frequency specification. For low WCLK frequencies, this condition can be solved by increasing the number of BCLK cycles per WCLK frame enough to satisfy these requirements.

Figure 4. ASI Slave Mode (Generating Master Clock from BCLK)

www.ti.com

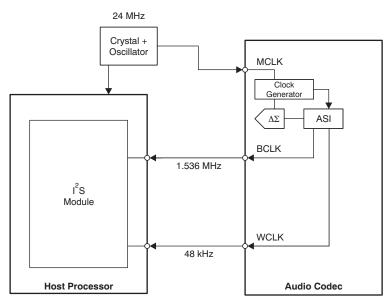

## 2.2 ASI Master Mode

In master mode, the BCLK and WCLK are outputs from the audio codec. These clocks are derived from an external master clock, such as an oscillator, as shown in Figure 5. The ASI bus is derived from the codec master clock input which prevents drift between both.

Figure 5. ASI Master Mode

# 2.3 ASI Hybrid Modes

Two additional modes are possible in most AIC family devices:

## • BCLK is output and WCLK is input.

In this case, BCLK is internally derived from MCLK and sent to the host processor, which in turn should generate a WCLK that conforms to the ASI specification of the codec. BCLK does not drift with respect to MCLK; thus, the generated WCLK will also not drift.

Additional information about this configuration can be found in Application Report <u>SLAA413</u>, Configuring  $\ell$ S to Generate BCLK from Codec Devices and WCLK from McBSP Port, available for download at <u>www.ti.com</u>.

## • BCLK is input and WCLK is output.

This mode has similar constraints to the ones mentioned in Section 2.1. In this mode, the audio codec monitors the BCLK pin to keep the WCLK output timing within the ASI bus specification. BCLK must not drift with respect to the master clock to ensure that the generated WCLK will not drift with respect to MCLK.

The internal master clock could also be generated from the BCLK (similar to Figure 4, but with WCLK as an output).

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                  |                                   |  |

|-----------------------------|------------------------|-------------------------------|-----------------------------------|--|

| Amplifiers                  | amplifier.ti.com       | Audio                         | www.ti.com/audio                  |  |

| Data Converters             | dataconverter.ti.com   | Automotive                    | www.ti.com/automotive             |  |

| DLP® Products               | www.dlp.com            | Communications and<br>Telecom | www.ti.com/communications         |  |

| DSP                         | dsp.ti.com             | Computers and<br>Peripherals  | www.ti.com/computers              |  |

| Clocks and Timers           | www.ti.com/clocks      | Consumer Electronics          | www.ti.com/consumer-apps          |  |

| Interface                   | interface.ti.com       | Energy                        | www.ti.com/energy                 |  |

| Logic                       | logic.ti.com           | Industrial                    | www.ti.com/industrial             |  |

| Power Mgmt                  | power.ti.com           | Medical                       | www.ti.com/medical                |  |

| Microcontrollers            | microcontroller.ti.com | Security                      | www.ti.com/security               |  |

| RFID                        | www.ti-rfid.com        | Space, Avionics & Defense     | www.ti.com/space-avionics-defense |  |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        | Video and Imaging             | www.ti.com/video                  |  |

|                             |                        | Wireless                      | www.ti.com/wireless-apps          |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2010, Texas Instruments Incorporated