# Grid-Connected Micro Solar Inverter Implement Using a C2000 MCU

Jason Tao/ Vieri Xue

MCU DMC&DPS SAE Team

#### ABSTRACT

The current boom in the development of renewable energy use will trigger a fourth industrial revolution. Photovoltaic power generation is a vital part of the overall renewable energy scheme. In all solar inverters, the micro solar inverters are critical components.

This paper describes how to use a TMS320F2802x to design a micro solar inverter with low cost and high performance. Also discussed is the use of the interleaved active-clamp flyback, plus an SCR full-bridge, to realize a micro solar inverter with a 220-W output, and also provide the entire system firmware architecture and control strategy. Finally, the waveforms in lab are provided.

#### Contents

| 1   | Overview |                                                                             |    |  |  |

|-----|----------|-----------------------------------------------------------------------------|----|--|--|

|     | 1.1      | 1.1 Introduction for Solar Inverter                                         |    |  |  |

|     | 1.2      | Classification of the Photovoltaic Power Generation System                  | 4  |  |  |

|     | 1.3      | PV Panel Electrical Characteristics                                         | 4  |  |  |

|     | 1.4      | Solar Inverter Topology Shifts                                              | 5  |  |  |

| 2   |          | dware Design                                                                |    |  |  |

|     | 2.1      | System Block Diagram                                                        | 6  |  |  |

|     | 2.2      | 2 Auxiliary Power Supply Design                                             |    |  |  |

|     | 2.3      | Active-Clamp Flyback as an Isolated Front-End Converter Design              | 8  |  |  |

|     |          | 2.3.1 Active-Clamp Flyback Converter Overview                               | 8  |  |  |

|     |          | 2.3.2 Zero-voltage switching for active-clamp Flyback Design Considerations | 9  |  |  |

|     |          | 2.3.3 Open-Loop Simulation of the Active-Clamp Flyback                      | 11 |  |  |

|     | 2.4      | Isolated MOSFET Bridge Drive Circuit Design                                 | 12 |  |  |

| 3 F | Firn     | nware Design                                                                | 13 |  |  |

|     | 3.1      | Firmware Specification                                                      |    |  |  |

|     |          | 3.1.1 Function Specification                                                | 13 |  |  |

|     |          | 3.1.2 Measurements                                                          | 14 |  |  |

|     |          | 3.1.3 Protection                                                            |    |  |  |

|     |          | 3.1.4 Grid-tie Converter Controller                                         |    |  |  |

|     | 3.2      | Firmware Structure                                                          |    |  |  |

|     |          | 3.2.1 Background and Task                                                   |    |  |  |

|     |          | 3.2.2 The Status Machine of the System                                      |    |  |  |

|     |          | 3.2.3 Interrupt Sevice Routine                                              |    |  |  |

|     | 3.3      | Grid-Tie Converter Controller                                               | 17 |  |  |

|     |          | 3.3.1 PLL Controller                                                        |    |  |  |

|     |          | 3.3.2 Current Controller                                                    | 18 |  |  |

| 4 | Test Waveforms in Lab              | .22 |

|---|------------------------------------|-----|

|   | Others                             |     |

| - | References                         | -   |

|   | endix A. Electrical Specifications |     |

|   | endix B. Schematics                |     |

|   |                                    |     |

### Figures

| Figure 1.<br>Figure 2.<br>Figure 3. | Development Trend of World Energy<br>Off-Grid Solar Inverter System<br>Grid-Tie Solar Inverter System | 4<br>4 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------|--------|

| Figure 4.<br>Figure 5.              | PV Panel Electrical Characteristics<br>Central and String Topology                                    |        |

| Figure 5.                           | Energy Harvest Influence by Shadow                                                                    |        |

| Figure 7.                           | Micro Inverters Topology                                                                              |        |

| Figure 8.<br>Figure 9.              | System Block Diagram of Micro Solar Inverter<br>Typical Application Schematic of LM34927              |        |

| Figure 10.                          | Simplified Schematic of the Active-Clamp Flyback Converter                                            | 9      |

| Figure 11.                          | Open-Loop Simulation Model of Active-Clamp Flyback                                                    |        |

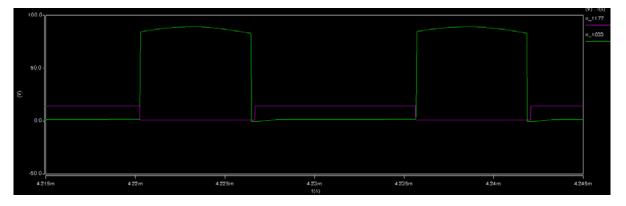

| Figure 12.                          | Simulated Waveform of $V_{DS}$ and $V_{GS}$ on Q1                                                     |        |

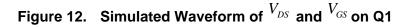

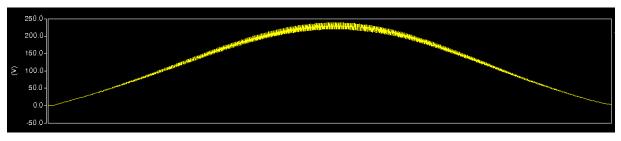

| Figure 13.<br>Figure 14.            | Simulated Output Voltage Waveform<br>Schematic Diagram of Isolated MOSFET High- and Low-Side Driver   | 12     |

| Figure 15.                          | Background Structure                                                                                  | 15     |

| Figure 16.<br>Figure 17.            | The Status Machine<br>The ISR Flow Chart                                                              |        |

| Figure 18.                          | The Controller Structure                                                                              |        |

| Figure 19.                          | The PLL Control System Diagram                                                                        |        |

| Figure 20.<br>Figure 21.            | The Flyback Circuit<br>The Continuous Mode Current of the Flyback                                     |        |

| Figure 22.                          | The Current Controller Loop                                                                           |        |

| Figure 23.                          | The Modified Current Loop                                                                             |        |

| Figure 24.<br>Figure 25.            | Close-Loop Output Current and Voltage<br>Grid-Tie Current and Grid-Tie Voltage                        |        |

| Figure 26.                          | Voltage and Current Waveform When System Turning On                                                   | 23     |

| Figure 27.                          | Voltage and Current Waveform When System Turning Off                                                  |        |

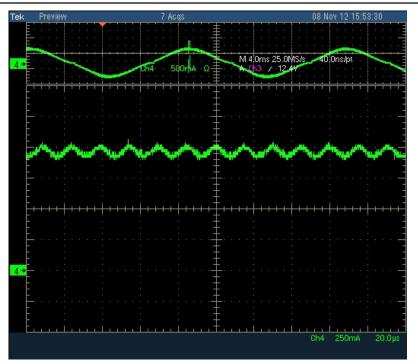

| Figure 28.<br>Figure 29.            | ZVS Waveform of Main Switch MOSFET and Resonance Current on $L_r$ Grid-Tie Current Ripple             |        |

### Tables

| Table 1. High-Speed [ | Digital Isolators Function Table | 13 |

|-----------------------|----------------------------------|----|

|-----------------------|----------------------------------|----|

### 1 Overview

### 1.1 Introduction for Solar Inverter

Material, energy, and information are the three important elements for human survival and development. Each new discovery for energy use transformed and greatly promoted the development of modern civilization:

- The invention of the steam engine brought us into the machine age.

- The invention and use of electricity brought us into the electrical age.

- The invention of the semiconductor transistor brought into the information age.

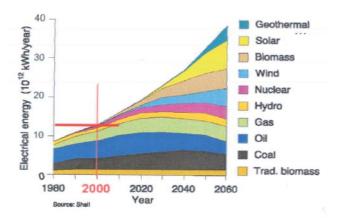

The present renewable energy development and use will trigger a fourth industrial revolution; of all the renewable energy use methods, photovoltaic power generation is a critical part of overall renewable energy development. According to the world energy organization predictions, as the traditional energy sources (such as coal, oil, and so forth) gradually dry up, renewable energy power generation will become a major energy method. Figure 1 shows the development trend of world energy.

Figure 1. Development Trend of World Energy

Governments are greatly concerned about the development of renewable energy. In 2007, the Chinese government issued a "renewable can meet the long-term development planning", and in 2008 issued a renewable energy development plan for the eleventh 5-year. According to the requirements of the plan, China photovoltaic power generation installed capacity in 2010 is 250 billion watts; it is estimated that by 2020 this capacity will reach 5000 billion watts, which, combined with the grid-tie photovoltaic power generation, accounts for 75 percent of the total.

The main advantages of solar photovoltaic power generation include:

- Solar energy is abundant and inexhaustible.

- The material to product PV panels is widely distributed and abundant reserves.

- Simple system structure, high conversion efficiency

- No pollution and can be recycle used

- Long life of photovoltaic battery, low maintenance costs

Shortcomings of solar photovoltaic power generation include:

• Low power density, larger cover area

- Generation limited by natural conditions, no sun and no power

- High unit generating cost

### 1.2 Classification of the Photovoltaic Power Generation System

According to the application of the scene, photovoltaic generation system can be divided into the off-grid solar inverter system and the grid-tied solar inverter system.

The off-grid solar inverter system is mainly used in composition-independent photovoltaic power generation system, applied in the family, the countryside, island, and remote areas of the power supply, and urban lighting, communications, testing and application of the system of power supply. Figure 2 is a system block diagram that shows the main components of the solar panels components, solar inverter units, energy storage unit, and electricity load and so on.

Figure 2. Off-Grid Solar Inverter System

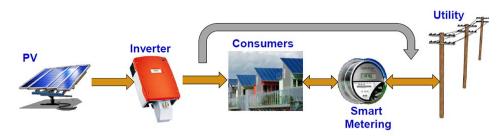

While the grid-tie solar inverter system is mainly used in parallel with the traditional utility grid, the solar inverter converts the energy from the PV panel to the traditional utility grid, the main components of the solar panels components, solar inverter units, smart bidirectional metering, the house's consumer load and traditional utility grid, and so forth (see Figure 3).

Figure 3. Grid-Tie Solar Inverter System

### **1.3 PV Panel Electrical Characteristics**

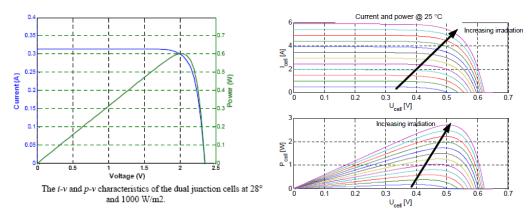

Solar inverter power output varies almost directly with sunlight, but current drops off much faster until you reach very low light levels. PV panels typically will generate 16V under very low light conditions, but at very little current.

In addition, as the PV panel temperature increases, voltage output decreases and vice versa. Curve moves with lighting condition, temperature, and so forth, just like Figure 4.

Solar inverters must operate at the MPP to capture maximum energy from the PV panel. This is accomplished by the maximum power point control loop known as the maximum power point tracker (MPPT).

Figure 4. PV Panel Electrical Characteristics

### 1.4 Solar Inverter Topology Shifts

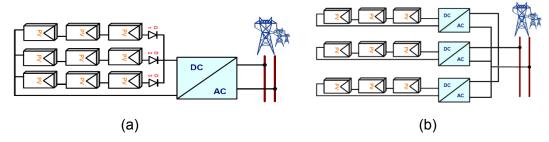

Because the output voltage of one PV cell is from 20 to 45 volts with the change of illumination, if a higher output voltage is needed to suit for grid-tied application, usually consider putting a PV cell in parallel and in series to obtain high input voltage, and use one inverter to realize electric energy conversion. This type of topology is called "central inverters" just like Figure 5(a); its main feature is:

- 10 to 250 kw, 3-phase and several strings in parallel

- High converter efficiency, low cost and low reliability

- Not optimal MPPT

- Usually used for power plants

Figure 5. Central and String Topology

Another application is putting a PV cell in series to make the energy conversion, in every series branch. There is one MPPT module to capture maximum energy from the PV panel. This type of topology is called "string inverters" just like Figure 5(b); its main feature is:

- 1 to 10 kw, typical residential application

- Each string branch has its own inverter enabling better MPPT.

- The strings can have different orientations.

- Three-phase inverters for output power above 5 kw

TEXAS INSTRUMENTS

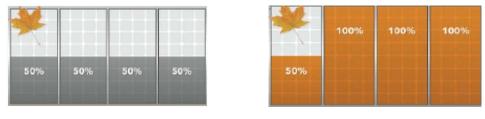

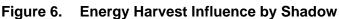

Although the string inverter can gain more efficiency in energy capture, when one of the series PV cell is kept out by shadow, this string branch for energy capture decreases with it just like Figure 6(a). If a MPPT module is placed to capture every PV panel, it will be solved. This type of topology is called "micro inverters" just like Figure 7.

(b)

Figure 7. Micro Inverters Topology

Obviously, for micro inverters, this is a "distributed MPPT" architecture that adds cost per PV panel; however, efficiency is increased by 5 to 25 percent by recovering the following efficiency losses:

- PV panel mismatch losses (3 to 5 percent)

- Partial shading losses (5 to 25 percent)

- Simpler system design and alleviated fault tolerance (0 to 15 percent)

- Suboptimal MPPT losses (3 to 10 percent)

- Also, increases safety and square footage (roof) use

So if we choose the micro inverters topology, it sacrifices the converter efficiency but make the energy capture more efficient.

## 2 Hardware Design

### 2.1 System Block Diagram

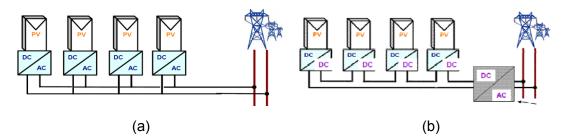

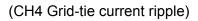

In our solution for solar inverter, we choose the topology that is interleaved flyback plus SCR fullbridge for industrial frequency inverting. All of the control is only one MCU (2802×) to realize, there is also an interface by RS485 or PLC for communication. Figure 8 shows a block diagram of the micro solar inverter. For detail specifications, see Appendix A.

This topology has the following features:

• Simple system structure

- High efficiency and low cost

- Complete isolation and high reliability

- Unable to realize the reactive power compensation

Figure 8. System Block Diagram of Micro Solar Inverter

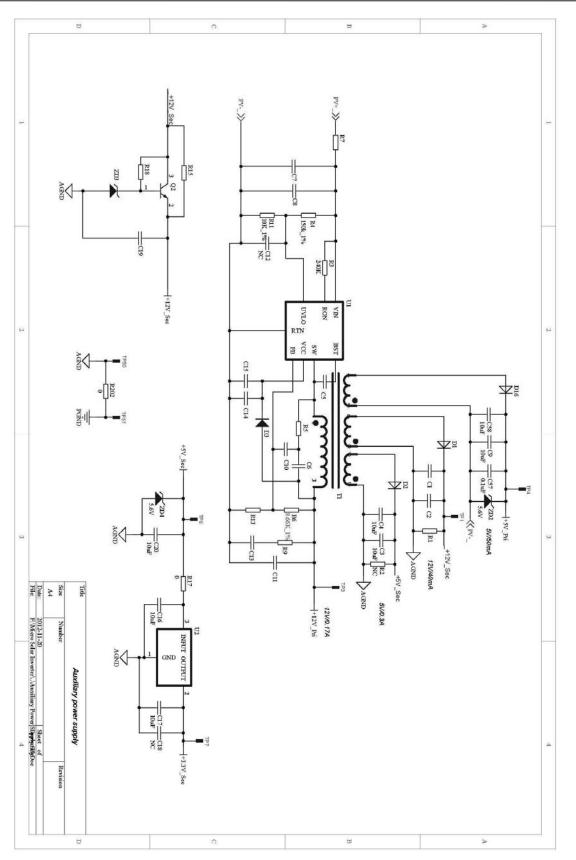

### 2.2 Auxiliary Power Supply Design

In a micro solar inverter, we need auxiliary power that can output multiple voltages to A/D sample circuits, drive circuits, MCU controller, and so forth. On the other hand, the auxiliary power must be completely isolated from primary side to secondary side.

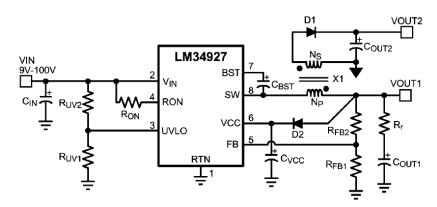

So the LM34927 chip is selected; this chip has many features as follows:

- Wide input range from 9 to 100V

- Low cost, integrated 100 V, high- and low-side switches

- The constant-on-time (COT) control scheme requires no loop compensation and provides excellent transient response.

- Full protected functions including adjustable UVLO.

Figure 9 shows the typical application schematic of LM34927. From the schematic, it is determined that the primary side of LM34927 is a buck circuit and the secondary side is a flyback topology to realize the isolation.

### 2.3 Active-Clamp Flyback as an Isolated Front-End Converter Design

### 2.3.1 Active-Clamp Flyback Converter Overview

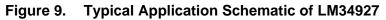

Figure 10 shows the incorporation of an active-clamp circuit into the basic flyback topology. In the figure, the flyback transformer is replaced with an equivalent circuit model showing the magnetizing and leakage inductances ( $L_r$  represents the total transformer leakage inductance reflected to the primary in addition to any external inductance).

Switches Q1 and Q2 are shown with their associated body diodes.  $C_r$  represents the parallel combination of the parasitic capacitance of the two switches. This device capacitance resonating with  $L_r$  enables zero-voltage switching (ZVS) for Q1.

With the active-clamp circuit, the transistor turn-off voltage spike is clamped, the transformer leakage energy is recycled, and ZVS for both primary (Q1) and auxiliary (Q2) switches becomes possible.

These advantages come at the expense of additional power stage components and increasing control circuit complexity (two switches as opposed to the usual one switch).

For this description of circuit operation, the following assumptions are made:

- Ideal switching components

- The magnetizing current is always nonzero and positive.

- $L_r$  (includes the transformer leakage inductance) is much less than the transformer

magnetizing inductance  $L_m$  (typically 5 to 10 percent of  $L_m$ ).

• Sufficient energy is stored in  $L_r$  to completely discharge  $C_r$  and turn on the body diode of Q1.

Figure 10. Simplified Schematic of the Active-Clamp Flyback Converter

### 2.3.2 Zero-voltage switching for active-clamp Flyback Design Considerations

To achieve ZVS for Q1, Q2 must be turned on during the decline interval of the resonant inductor current. If not, the resonant inductor current reverses (becoming positive again), recharging  $C_r$ , and ZVS is lost (or at least partially lost). Therefore, the delay time between Q2 turning off and Q1 turning on is critical to ZVS operation. The optimum value of this delay is one-quarter of the resonant period formed by  $L_r$  and  $C_r$ :

$$T_{delay} = \frac{\pi}{2} \times \sqrt{Lr \times Cr}$$

So it is best to put the dead time between the Q1 closed and Q2 open to less than  $T_{delay}$  to get partial condition of the ZVS.

Even if insufficient energy is stored in  $L_r$  to completely discharge the switch capacitance  $C_r$ , to minimize possible voltage stress on Q1 and Q2 (and get higher converter efficiency), we must cautiously design parameters of resonant inductor  $L_r$ , resonant capacitance  $C_r$ , and clamp capacitance  $C_r$ .

### **2.3.2.1** Design of Resonant Inductor $L_r$

After the value of  $L_m$  is fixed, the resonant inductor can be designed. As mentioned previously, it is assumed its value will be a small fraction of  $L_m$  (typically 5 to 10 percent of  $L_m$ ).

For a given converter operating point and the value of  $C_r$ , to achieve ZVS the size of  $L_r$  must be sufficient to completely discharge the switch capacitance.

Designing  $L_r$  is difficult because the resonant capacitor voltage ( $Vc_r$ ) is a function of the value of  $L_r$  as shown in the following equation:

UMENTS

$$I_{\mathcal{Q}_{1-}pk} = I_{Lm_pk} = I_{Lr_pk} \ge Vc_r \times \sqrt{\frac{C_r}{L_r}}$$

However, in a practical design situation, the resonant inductor voltage is relatively small (compared to  $V_{in} + NV_o$ ) and can be solved for an approximate minimum value of  $L_r$  necessary to achieve ZVS conditions:

$$L_r \ge \frac{C_r \times (V_{in} + NV_o)^2}{I_{Q1_pk}^2}$$

In this application requiring high-output voltage, it may be more desirable to specifically tailor the soft-switching characteristics of the output rectifier than to necessarily realize ZVS of the primary switch.

### **2.3.2.2** Design of Clamp Capacitor $C_c$

Choosing the value of clamp capacitance is done based on the design of  $L_r$ . The resonant frequency formed by the clamp capacitor and the resonant inductor should be sufficiently low so that excessive resonant ringing does not occur across the power switch when the switch is turned off. However, using a value of clamp capacitance that is too large yields no improvement in clamping performance at the expense of a larger (more costly) capacitor. A good compromise for design purposes is to select the capacitor value so that one-half of the resonant period formed by the clamp capacitor and resonant inductance exceeds the maximum off time of Q1. Therefore:

$$C_{clamp}\rangle\rangle\frac{\left(1-D^{HL}\right)^{2}}{\pi^{2}\times L_{r}\times f_{s}^{2}}$$

Where  $D^{HL}$  denotes operation at the maximum input voltage,  $f_s$  is the operation switch frequency of Q1 and Q2.

The capacitor voltage rating must exceed  $NV_{o}$  by the amount of voltage dropped across  $L_{r}$ :

$$V_{clamp_max} \approx NV_o + \frac{2 \times L_r \times f_s \times P_{o_max}}{\eta \times V_{in HL} \times (1 - D^{HL})}$$

The resonant period of the clamp capacitor and resonant inductance can be calculated by the following equation:

$$T_{resonant} = 2\pi \times \sqrt{L_r \times C_r}$$

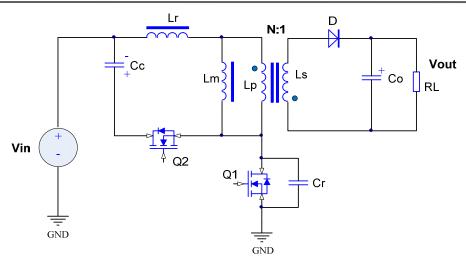

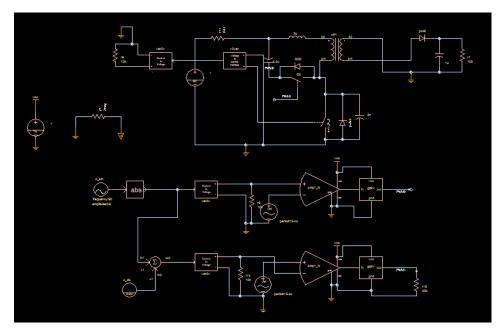

### 2.3.3 Open-Loop Simulation of the Active-Clamp Flyback

Figure 11 is the open-loop simulation model of the active-clamp flyback. The following values apply to this simulation: input voltage  $V_{in}$  = 36 volt, switch frequency of primary MOSFET  $f_s = 65kHz$ , resonant inductance  $L_r$  =0.5 µH, resonance capacitance  $C_r$  = 1 nF, clamping capacitance  $C_c$  =10 µF, the maximum duty cycle for primary main switch MOSFET D = 0.6, and load  $R_{Load}$  = 100  $\Omega$ .

Figure 11. Open-Loop Simulation Model of Active-Clamp Flyback

(Red waveform is  $V_{\scriptscriptstyle GS}$  , green waveform is  $V_{\scriptscriptstyle DS}$  )

Figure 12 indicates the voltage rise of gate drive after the voltage of drain to source drops to

zero, so it can be confirmed that Q1 realized ZVS. Also, the voltage spike of  $V_{DS}$  is clamped to  $V_{in} + NV_{out}$ , meaning that the primary side realized active-clamp.

Figure 13. Simulated Output Voltage Waveform

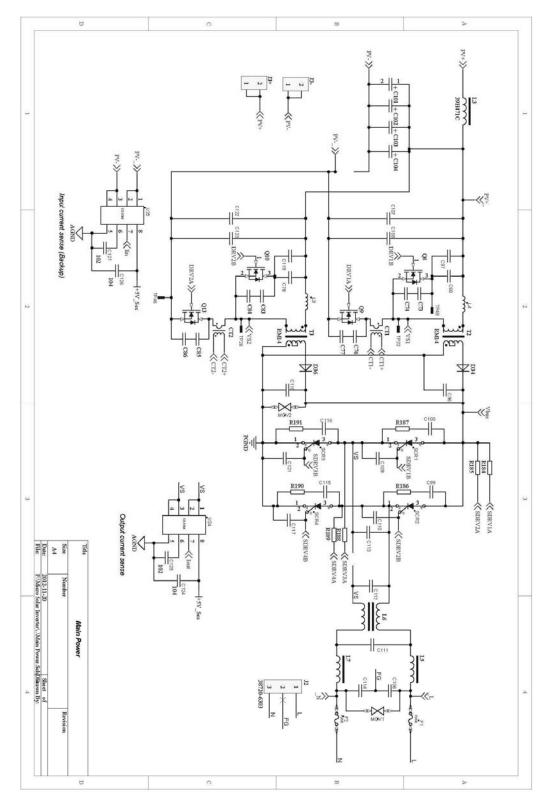

### 2.4 Isolated MOSFET Bridge Drive Circuit Design

To achieve complete isolation from primary side to secondary side, A/D sampling and drive circuit isolation is required, in addition to auxiliary power isolation.

Because the MCU is placed in the secondary side while the main switch MOSFET is at the primary side, we must turn the control signal of secondary side transfer to the primary side to control MOSFET.

To transfer the control signal from secondary side to primary side, select the chip of the highspeed digital isolators plus the high- and low-side driver. Figure 14 shows a schematic diagram of the isolated MOSFET high- and low-side driver.

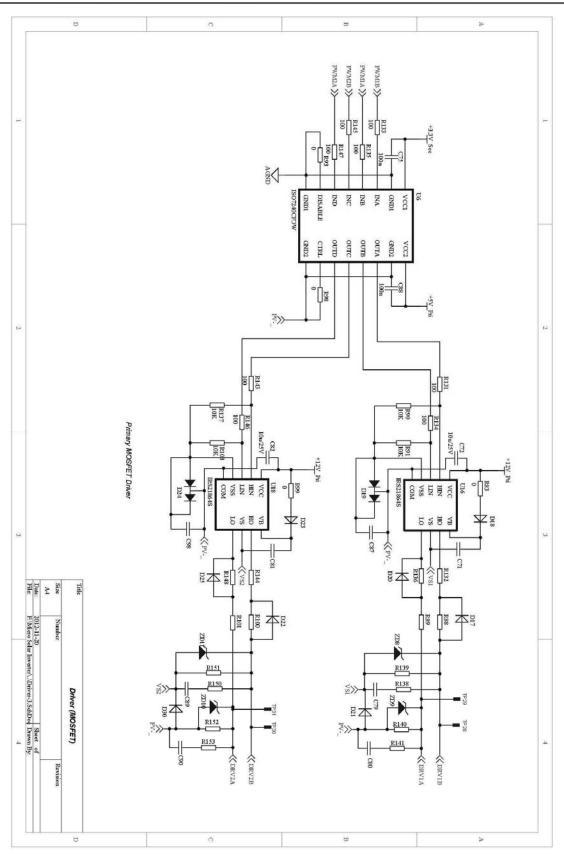

### Figure 14. Schematic Diagram of Isolated MOSFET High- and Low-Side Driver

In this application, the isolated MOSFET has many features, including:

- Simple structure, easy implementation

- Fully operational to +600 V

- 4-kV ESD protection

- Bootstrap operation

In addition, pay special attention to the initial state of the high-speed digital isolators; otherwise, it can damage the main switch MOSFET.

| Vcc1 | Vcc2 | Date Input<br>(IN) | Disable Input<br>(DISABLE) | Fail Safe Control Input<br>(CTRL) | Data Output<br>(OUTPUT) |

|------|------|--------------------|----------------------------|-----------------------------------|-------------------------|

| PU   | PU   | Н                  | L or Open                  | ×                                 | Н                       |

| PU   | PU   | L                  | L or Open                  | ×                                 | L                       |

| ×    | PU   | ×                  | Н                          | H or Open                         | Н                       |

| ×    | PU   | ×                  | Н                          | L                                 | L                       |

| PD   | PU   | ×                  | ×                          | H or Open                         | Н                       |

| PD   | PU   | ×                  | ×                          | L                                 | L                       |

Table 1.

High-Speed Digital Isolators Function Table

(PU = Powered Up; PD = Powered Down; X = Irrelevant; H = High Level; L = Low Level)

## 3 Firmware Design

### 3.1 Firmware Specification

### 3.1.1 Function Specification

The firmware of the system includes the following functions:

- 1. Turn On/Off. The user can turn on or turn off the system by pressing the turn on/off button. The software setting must enable this function.

- 2. Auto Turn On/Off. If the turn on condition is satisfied, the system can turn on itself automatically. When the condition is not fit to feed the energy to the grid, the system stays in the standby mode, and observes the condition changes. If the system is already turned on, the system turns off automatically when the condition is not fit to feed energy.

- 3. Soft start turning on. When the system must turn on, it starts from the zero current feeding, and the PWM turns on at the zero-crossing point to reduce the rush current to the grid.

- 4. LED Control. The system has one status LED. When the system is in standby mode, the corresponding LED flashes every 1.2 seconds. When the system is turned on, the LED flashes every 2.4 seconds. When there is a fault, the LED is lighted continuously.

- 5. User Key Control. The inverter has a user key. The user key can turn on or turn off the inverter, and it can also clear the fault. When the system stays in standby mode, if the key is pressed on for more than 1 second, the system turns on if the condition is satisfied. If the system is already turned on, when the key is pressed on for more than 1 second, the system stays in fault mode, the fault can be cleared and go into standby mode again by pressing the user key for more than 1 second.

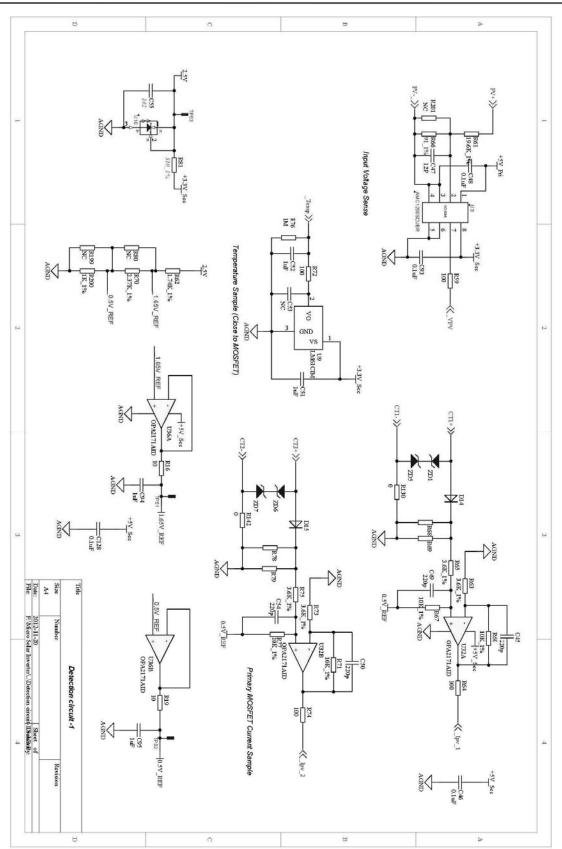

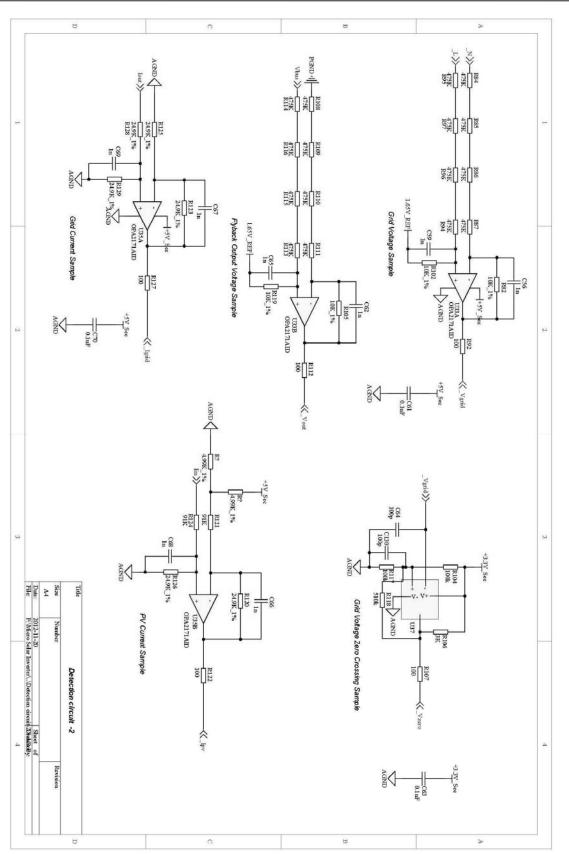

### 3.1.2 Measurements

To control and monitor the system status, the following measurements are calculated:

- Grid voltage RMS

- Grid frequency

- Output active power of the inverter

- Input power

- Input PV voltage

- Temperature

### 3.1.3 Protection

The system has some basic protection functions.

- 1. Primary side rush current protection. When a rush current caused by the short circuit or the saturation of the primary inductor occurs, the PWM works in CBC mode first; however, when the CBC is more than three times, the system turns off and goes into fault mode.

- 2. Secondary side overvoltage. When the SCR is not turn on normally, a very high voltage in the secondary side occurs. The system turns off and goes into the fault mode.

- 3. Output overcurrent. When the amplitude of the output current exceeds the threshold, an output overcurrent fault occurs. The system turns off and goes into fault mode.

- 4. Grid voltage/frequency over/under. If the system is already turned on, when the grid voltage/frequency is out of the normal range, the system turns off in five grid cycles.

- 5. Anti-islanding. If the islanding condition is satisfied, the system turns off in 4 seconds. If the condition is recovered to normal, the system can restart in 1 second.

- 6. Over temperature

### 3.1.4 Grid-tie Converter Controller

To feed the energy to the grid, the following controller algorithm must be realized in this system:

- 1. Phase-locked loop (PLL) controller. The PLL controller is used to synchronize with the grid voltage, which can provide a reference phase to the current controller.

- 2. Grid-tie current controller. The current controller can ensure the output current is a sine wave and trace the current reference to balance the input power and the output power.

- 3. Maximum power point tracking (MPPT). The MPPT is used to put the panel into a maximum power output stage.

### 3.2 Firmware Structure

### 3.2.1 Background and Task

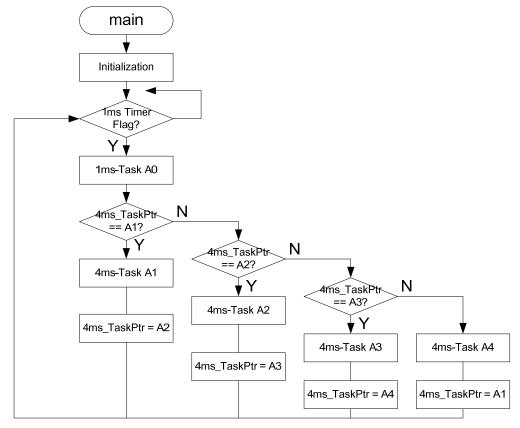

The whole firmware system is a forward-background system. Figure 15 shows the background structure.

Figure 15. Background Structure

There are one 1-ms task and four 4-ms tasks in this system.

- 1. 1ms-Task A0. The 1-ms periodical task. In this task, the LED control executes. Besides, the PLL controller is also located in this task.

- 2. 4ms-Task A1. The A1 4-ms periodical task. The status machine processor.

- 3. 4ms-Task A2. The A2 4-ms periodical task. All the measurements are calculated in this task.

- 4. 4ms-Task A3. The A3 4-ms periodical task. The user key detection is here, and the over/under range of the running conditions are detected here as well, and the fault command is sent out.

- 5. 4ms-Task A4. The A4 4-ms periodical task. MPPT controller and the debug support.

### 3.2.2 The Status Machine of the System

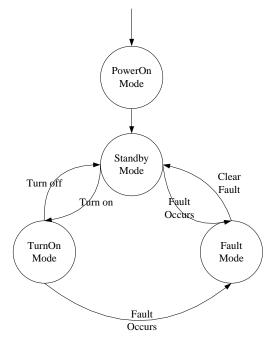

Figure 16. The Status Machine

Figure 16 shows the status machine processed in task A1. Different status represents different running mode.

There are four status modes in this system:

- Power on

- Standby

- Turn-on

- Fault

Power on mode is a transition mode when the system power is on. In this mode, the system does some initializations, after which the system gets into the standby mode automatically.

Standby mode is the mode in which the system waits for the command to turn on. All the PWM and the SCR control signal are off. In this mode, all the measurements are valid. The system detects the outside conditions and checks if the system can be turned on.

When the system is turn on successfully from standby mode, the system gets into turn-on mode. All the PWM and the SCR control signal are on in this mode. The system starts to feed the energy to the grid.

If a fault occurs, the system goes into fault mode, all the PWM and the SCR control signal is off. If the fault is cleared, the system can go back to standby mode automatically.

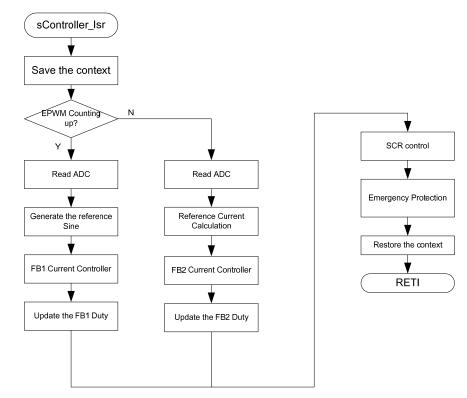

### 3.2.3 Interrupt Sevice Routine

The interrupt service routine (ISR) in this system has the following functions:

- Read the ADC result and a part of the measurement calculation.

- Grid-tie current controller

- SCR on/off control

- Emergency protection. The primary-side rush current, the secondary-side overvoltage and the output current amplitude over protection.

- Debug support. Record the debug data to the buffer.

Figure 17. The ISR Flow Chart

### 3.3 Grid-Tie Converter Controller

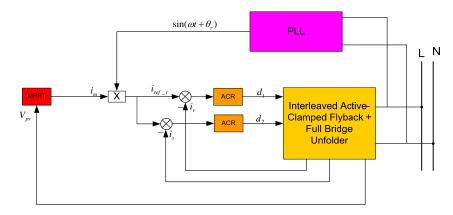

Figure 18 shows the whole grid-tie converter structure.

Figure 18. The Controller Structure

### 3.3.1 PLL Controller

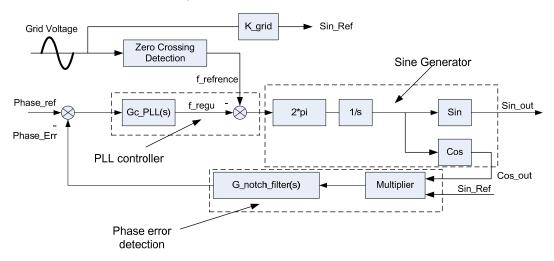

Figure 19 shows the PLL control system.

Figure 19. The PLL Control System Diagram

The PLL system is made up of the following parts:

- The phase error detection. Detect the phase error between the reference and the sine wave out. This detection is done in 1-ms task A0.

- The PLL controller. Close loop controller, the controller is executed in 1-ms task A0.

- The Sine generator. Generate the sine wave according to the frequency and sample time; this is done in the ISR.

### 3.3.2 Current Controller

To design the current loop, the object model must be built first. The small signal model can be used here.

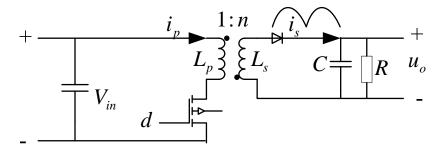

Figure 20. The Flyback Circuit

Assume a flyback circuit shown in Figure 6; also, assume it works in continuous mode.

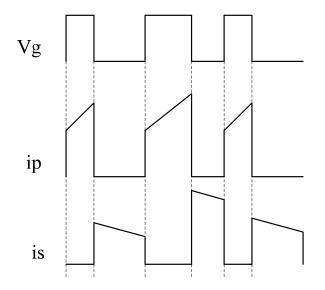

Figure 21. The Continuous Mode Current of the Flyback

If the MOS in the primary side is turned on, the current of the primary side increases, the  $L_p$  is charged, and the energy is stored in it. In the secondary side, the D1 turns off; the C is discharged to take the load. So the following equations can be obtained:

$$\begin{cases} L_p \frac{di_p}{dt} = V_{in} \\ C \frac{du_o}{dt} = -\frac{u_o}{R} \end{cases}$$

(1)

If the Q1 is turned off, the energy transfers to the secondary side immediately, the  $i_p$  degrades to zero soon. In the secondary side, the diode turns on, the secondary inductor takes the load and charges to the C. Equation (2) can be obtained.

$$\begin{cases} L_s \frac{di_s}{dt} = -u_o \\ i_s = C \frac{du_o}{dt} + \frac{u_o}{R} \end{cases}$$

(2)

The primary inductance  $L_p$  and the secondary inductance  $L_s$  have the following relationship:

XAS STRUMENTS

$$L_s = n^2 L_p \tag{3}$$

Put Equation (3) to Equation (2):

$$\begin{cases} n^{2}L_{p}\frac{d\frac{i_{p}}{n}}{dt} = -u_{o} \\ \frac{i_{p}}{n} = C\frac{du_{o}}{dt} + \frac{u_{o}}{R} \end{cases} \xrightarrow{} \begin{cases} L_{p}\frac{di_{p}}{dt} = -\frac{u_{o}}{n} \\ C\frac{du_{o}}{dt} = \frac{i_{p}}{n} - \frac{u_{o}}{R} \end{cases}$$

(4)

Use the average state space method, if the duty is d, then we can get the following equation:

$$\begin{cases} L_p \frac{di_p}{dt} = d \bullet V_{in} - (1-d) \frac{u_o}{n} \\ C \frac{du_o}{dt} = -\frac{u_o}{R} + (1-d) \frac{i_p}{n} \end{cases}$$

(5)

Add the small disturbance to Equation (5):

$$\begin{cases} L_{p} \frac{d(i_{p} + \hat{i}_{p})}{dt} = (d + \hat{d}) \bullet V_{in} - (1 - d - \hat{d}) \frac{(u_{o} + \hat{u}_{o})}{n} \\ C \frac{d(u_{o} + \hat{u}_{o})}{dt} = -\frac{u_{o} + \hat{u}_{o}}{R} + (1 - d - \hat{d}) \frac{i_{p} + \hat{i}_{p}}{n} \end{cases}$$

(6)

Remove the high-order infinitesimal element:

$$\begin{cases} L_{p} \frac{d\hat{i}_{p}}{dt} = \hat{d}(V_{in} + \frac{u_{o}}{n}) - \frac{1 - d}{n} \hat{u}_{o} \\ C \frac{d\hat{u}_{o}}{dt} = -\frac{\hat{u}_{o}}{R} + (1 - d) \frac{\hat{i}_{p}}{n} - \hat{d} \frac{i_{p}}{n} \end{cases}$$

(7)

So the relation between  $\hat{d}(s)$  and  $\hat{i}_p(s)$  is:

$$G_{id}(s) = \frac{\hat{i}_{p}(s)}{\hat{d}(s)} = \frac{V_{in} + \frac{u_{o}}{n}}{L_{p}}$$

(8)

The stable state of the d is:

$$D = \frac{u_o}{nV_{in} + u_o} \tag{9}$$

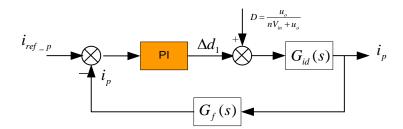

The controller loop is:

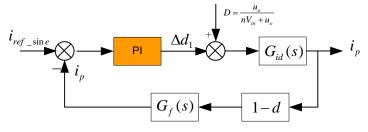

Figure 22. The Current Controller Loop

Using the PI controller, the controller calculation frequency is 22 kHz. The open loop bandwidth must be set to 1 to 2 kHz.

Figure 8 indicates that the feedback of the close loop must be the primary side current  $i_p$ , but in the real system it is the middle point current when Q1 is turned on in the real system. If the converter is working in continuous mode, the relationship between the primary feedback and the secondary average current is:

$$ni_s = (1-d)i_p$$

(10)

To get a sine wave output current, the secondary average current must be a sine wave; therefore, it is necessary to modify the feedback current to the following model:

Figure 23. The Modified Current Loop

## 4 Test Waveforms in Lab

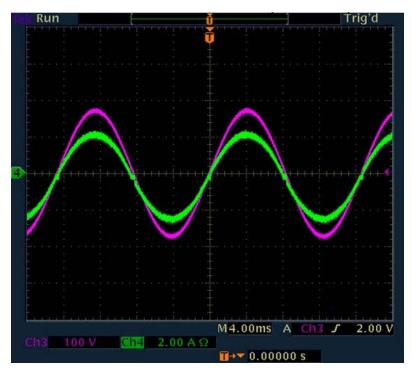

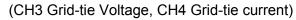

Figure 24. Close-Loop Output Current and Voltage

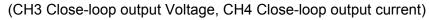

Figure 25. Grid-Tie Current and Grid-Tie Voltage

(CH2 Grid-tie Voltage, CH4 Grid-tie current)

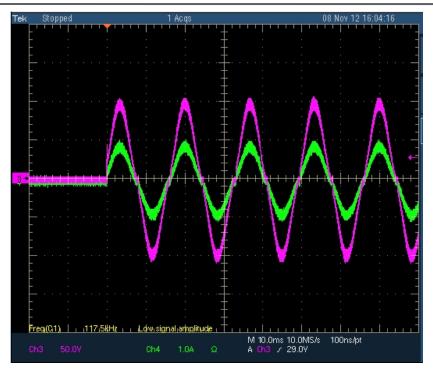

Figure 26. Voltage and Current Waveform When System Turning On

(CH2 Grid-tie Voltage, CH4 Grid-tie current)

Figure 27. Voltage and Current Waveform When System Turning Off

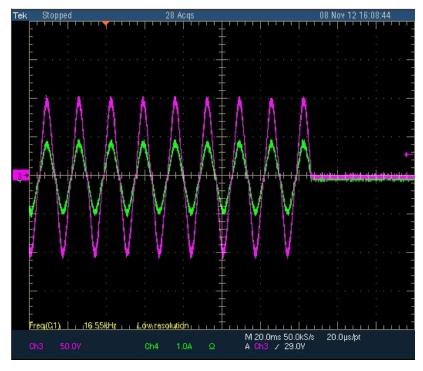

(CH1  $V_{GS}$  of main switch MOSFET,

CH3  $V_{DS}$  of main switch MOSFET,

CH4 resonance current on  $L_r$ )

Figure 28. ZVS Waveform of Main Switch MOSFET and Resonance Current on  $L_r$

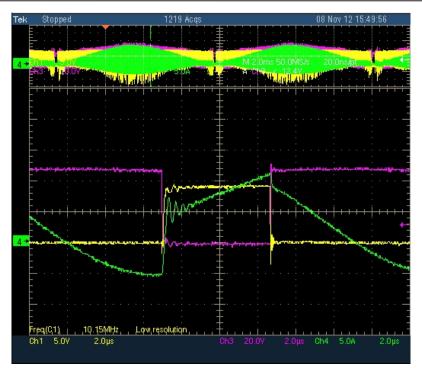

Figure 29. Grid-Tie Current Ripple

# 5 Others

For schematics, see Appendix B.

### **6** References

1. TMS320F2802x Datasheet, SPRS523G

# Appendix A. Electrical Specifications

| DC Parameters                          |                   |                        |      |      |     |  |  |

|----------------------------------------|-------------------|------------------------|------|------|-----|--|--|

| Items                                  |                   |                        | Min  | Тур. | Max |  |  |

| MPPT voltage range                     |                   |                        | 22   |      | 40  |  |  |

| Operating range                        |                   | V                      | 20   |      | 45  |  |  |

| Maximum DC input voltage               |                   | V                      |      |      | 50  |  |  |

| Minimum start voltage                  |                   | V                      | 18   |      |     |  |  |

| Maximum DC input short circuit current |                   | А                      |      |      | 15  |  |  |

| Maximum DC input current               |                   | А                      |      |      | 10  |  |  |

| AC Parameters                          |                   |                        |      |      |     |  |  |

| Items                                  |                   | Unit                   | Min  | Тур. | Max |  |  |

| Rated AC output power                  |                   | W                      |      | 220  |     |  |  |

| Output power factor (PF)               |                   |                        | 0.95 | 0.99 | 1   |  |  |

| Nominal AC output voltage range        |                   | Vrms                   | 90   | 110  | 135 |  |  |

| Nominal AC output current              |                   | А                      |      | 2.1  |     |  |  |

| Nominal AC output frequency range      |                   | Hz                     |      | 60   |     |  |  |

| Mis                                    | scellaneous Pa    | ramete                 | ers  |      |     |  |  |

| Items                                  |                   | Unit                   | Min  | Тур. | Max |  |  |

| Peak inverter efficiency               |                   |                        |      |      | 95  |  |  |

| Static MPPT efficiency                 |                   | %                      |      | 99   |     |  |  |

| Total harmonic distortion current      |                   | %                      | 3    | 5    |     |  |  |

| Ambient temperature range              |                   |                        | -25  |      | 50  |  |  |

| Night tare loss                        |                   | W                      |      | 1    |     |  |  |

| Software Functions                     |                   |                        |      |      |     |  |  |

| Communication PLC or RS485 (optional)  |                   |                        |      |      |     |  |  |

| Protection Islanding/Over Ra           |                   | ange/Short Circuit     |      |      |     |  |  |

| Status LED display Aux power LED, re   |                   | running LED, fault LED |      |      |     |  |  |

| Turn On/Off Manual start, so           |                   | oft start (optional)   |      |      |     |  |  |

| Debug support RS485 interface          |                   |                        |      |      |     |  |  |

| GUI                                    | RS485             |                        |      |      |     |  |  |

| Dimensions (W × H × D)                 |                   |                        |      |      |     |  |  |

| Cooling                                | Natural convectio | n                      |      |      |     |  |  |

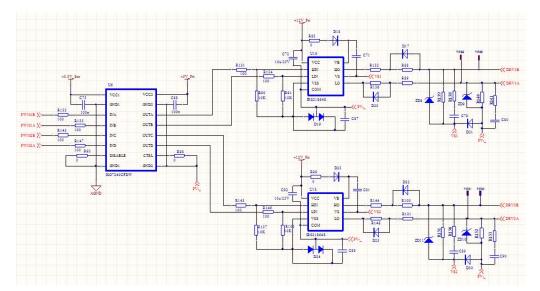

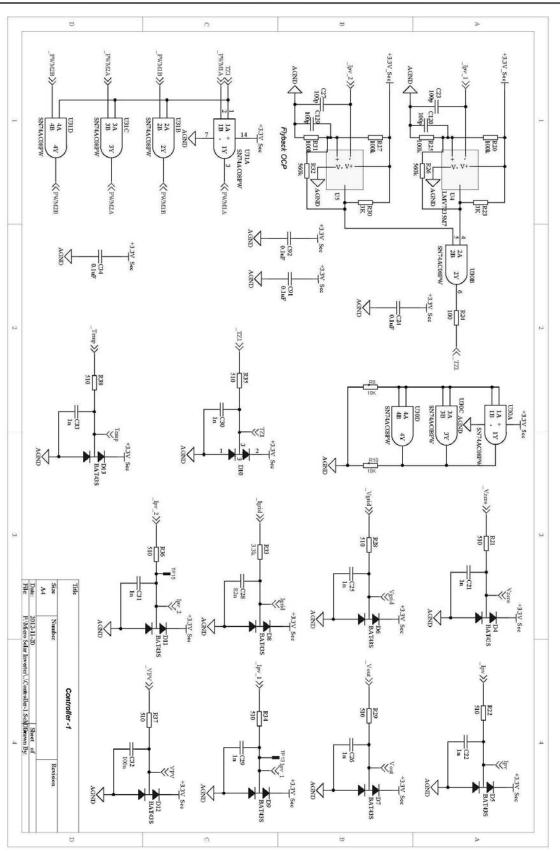

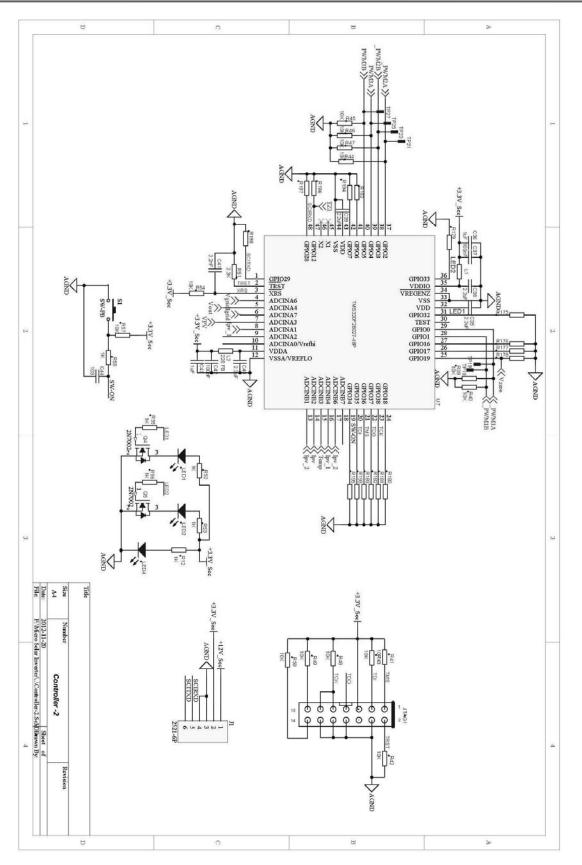

**Appendix B. Schematics**

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                                 | Applications                  |                                   |  |  |

|------------------------------|---------------------------------|-------------------------------|-----------------------------------|--|--|

| Audio                        | www.ti.com/audio                | Automotive and Transportation | www.ti.com/automotive             |  |  |

| Amplifiers                   | amplifier.ti.com                | Communications and Telecom    | www.ti.com/communications         |  |  |

| Data Converters              | dataconverter.ti.com            | Computers and Peripherals     | www.ti.com/computers              |  |  |

| DLP® Products                | www.dlp.com                     | Consumer Electronics          | www.ti.com/consumer-apps          |  |  |

| DSP                          | dsp.ti.com                      | Energy and Lighting           | www.ti.com/energy                 |  |  |

| Clocks and Timers            | www.ti.com/clocks               | Industrial                    | www.ti.com/industrial             |  |  |

| Interface                    | interface.ti.com                | Medical                       | www.ti.com/medical                |  |  |

| Logic                        | logic.ti.com                    | Security                      | www.ti.com/security               |  |  |

| Power Mgmt                   | power.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |  |  |

| Microcontrollers             | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |  |  |

| RFID                         | www.ti-rfid.com                 |                               |                                   |  |  |

| OMAP Applications Processors | www.ti.com/omap                 | TI E2E Community              | e2e.ti.com                        |  |  |

| Wireless Connectivity        | www.ti.com/wirelessconnectivity |                               |                                   |  |  |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated