🕳 Order

Now

Support & Community

#### ADS1282-SP

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

# ADS1282-SP 放射線耐性保証の高分解能デルタ-シグマADC

Technical

Documents

### 1 特長

- QMLV (QML Class V) MIL-PRF-38535認定済みで 放射線耐性保証(RHA)、SMD 5962-14231

- 5962L1423101VXC 軍事用温度範囲(-55℃~ 125℃)で認定済み

- 5962L1423102VXC 縮小温度範囲(-55℃~

115℃)で動的性能改善の認定済み

- 5962L14231

- 吸収線量(TID) 50kRAD (Si)までの放射線耐性保 証(RHA)

- シングル・イベント・ラッチアップ(SEL)耐性: LET = 50MeV-cm<sup>2</sup>/mg (125°C)

- シングル・イベント・ラッチアップ(SEL)耐性: LET = 60MeV-cm<sup>2</sup>/mg (85°C)

- 高分解能: 124dB SNR (1000SPS)

- 高精度: THD: -102dB INL: 0.5ppm

- 低ノイズのPGA

- 2チャネルの入力MUX

- 本質的に安定な変調器で、範囲外検出に迅速に応答

- 柔軟なデジタル・フィルタ:

- Sinc + FIR + IIR (選択可能)

- リニアまたは最小位相応答

- プログラム可能なハイパス・フィルタ

- FIRデータ・レートを選択可能:

250SPS~4kSPS

- フィルタ・バイパス・オプション

- 低消費電力: 25mW

- オフセットおよびゲイン較正エンジン

- SYNC入力

- アナログ電源:ユニポーラ(5V)またはバイポーラ (±2.5V)

- デジタル電源: 1.75~3.3V

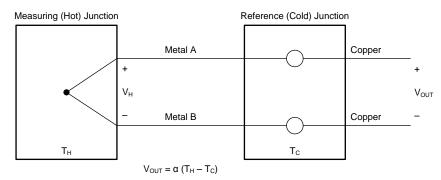

# 2 アプリケーション 人工衛星の温度および位置センシング

- 高精度の人工衛星および科学用アプリケーション

- 高精度の計測機器

🥭 Tools &

Software

22

- エンジニアリング評価(/EM)サンプルを利用可能<sup>(1)</sup>

- (1) これらのユニットは、技術的な評価のみを目的としています。標準とは異なるフロー(パーンインがないなど)に従って処理されており、 25℃の温度定格のみがテストされれています。これらのユニットは、 認定、量産、放射線テスト、航空での使用には適していません。これらの部品は、MILに規定されている温度範囲-55℃~125℃での 動作時間全体にわたるパフォーマンスを保証されていません。

# 3 概要

ADS1282-SPは、放射線耐性の高い超高性能シングル チップA/Dコンバータ(ADC)で、低ノイズのプログラマブ ル・ゲイン・アンプ(PGA)と2チャネルの入力マルチプレク サ(MUX)を内蔵しています。ADS1282-SPは、非常に高 い精度を実現しながら、放射線耐性を維持して、宇宙用 途の厳しい要求を満たし、各種の衛星、ペイロード、セン シング、その他過酷な環境のアプリケーションに適してい ます。

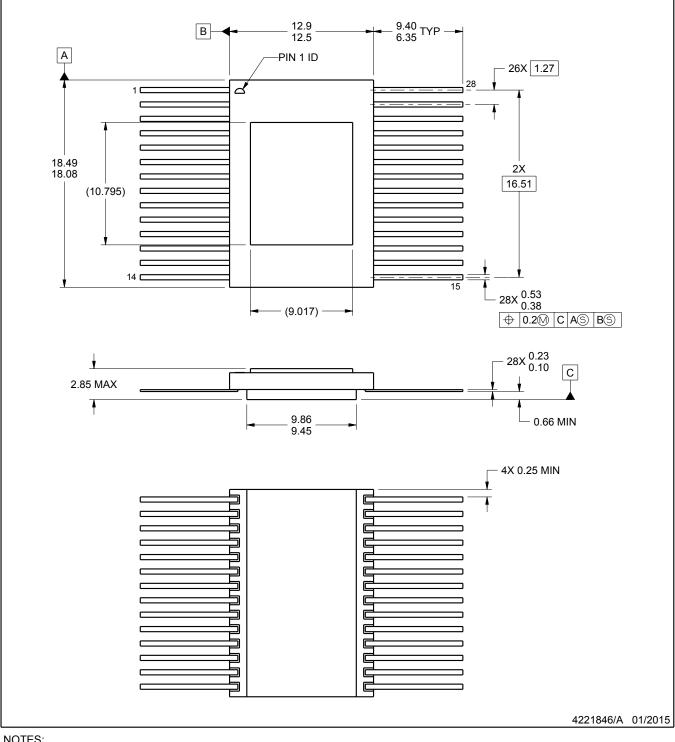

#### 製品情報<sup>(1)</sup>

| 型番         | パッケージ          | 本体サイズ(公称)       |

|------------|----------------|-----------------|

| ADS1282-SP | CFP (HKV) (28) | 18.23mm×12.70mm |

|            |                |                 |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内 容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。 English Data Sheet: SBAS691

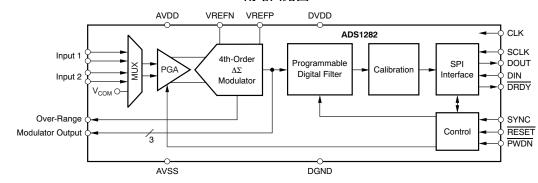

# 概略回路図

1

2 3

4

5

6

7

7.1

7.2

7.3

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

アプリケーション......1

概要......1

改訂履歴......2

概要(続き)......3

Pin Configuration and Functions ...... 4

7.4 Thermal Information ...... 6 7.8 Reset Timing Requirements ..... 10 7.9 Read Data Timing Requirements...... 10 7.10 Switching Characteristics ...... 10 7.11 Typical Characteristics ...... 11 Detailed Description ...... 15

8.1 Overview ...... 15

Revision A (December 2016) から Revision B に変更

Absolute Maximum Ratings ...... 5

ESD Ratings......5 Recommended Operating Conditions ...... 5

#### 4 改訂履歴

8

2

| 1   | <ul> <li>ドキュメントのタイトルを「ADS1282-SP 放射線耐性…」から「ADS1282-SP 放射線耐性保証…」に変更</li></ul>                                                                                                    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | • 「特長」の「シングル・イベント・ラッチアップ(SEL)耐性: LET = 40」を「シングル・イベント・ラッチアップ(SEL)耐性: LE                                                                                                         |

| 1   | 50」に変更                                                                                                                                                                          |

| 1   | • 「特長」に「シングル・イベント・ラッチアップ(SEL)耐性: LET = 60…」を追加                                                                                                                                  |

| 1   | • 「アプリケーション」一覧にエンジニアリング評価サンプルの箇条書き項目と脚注を追加                                                                                                                                      |

| 4   | Changed the HKV Package appearance                                                                                                                                              |

| ••• | <ul> <li>50」に変更</li> <li>「特長」に「シングル・イベント・ラッチアップ(SEL)耐性: LET = 60」を追加</li> <li>「アプリケーション」一覧にエンジニアリング評価サンプルの箇条書き項目と脚注を 追加</li> <li>Changed the HKV Package appearance.</li> </ul> |

#### 2016年3月発行のものから更新

| • | 「特長」セクションの箇条書き項目に5962L1423102VXCの縮小温度範囲を 追加                                               | . 1 |

|---|-------------------------------------------------------------------------------------------|-----|

| • | Added ESD Ratings table to Specifications section                                         | . 5 |

| • | Added T <sub>J</sub> values for 5962L1423102VXC to Recommended Operating Conditions table | . 5 |

| • | Added MIN, TYP and MAX values for 5962L1423102VXC to Electrical Characteristics table     | . 6 |

| • | 追加「ドキュメントの更新通知を受け取る方法」セクションを「デバイスおよびドキュメントのサポート」セクションに                                    | 57  |

|    |   | 目 | 5 |

|----|---|---|---|

| 特長 | 1 |   |   |

| 8.2  | Functional Block Diagram                                                                                                                          | 16                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.3  | Feature Description                                                                                                                               | 16                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.4  | Device Functional Modes                                                                                                                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.5  | Programming                                                                                                                                       | 35                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8.6  | Register Maps                                                                                                                                     | 40                                                                                                                                                                                                                                                                                                                                                                                                                                  |

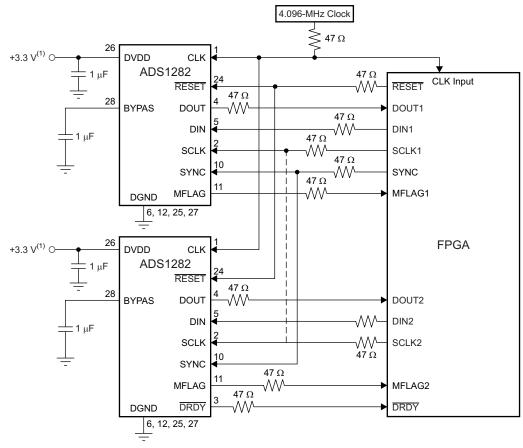

| Appl | ication and Implementation                                                                                                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.1  | Application Information                                                                                                                           | 45                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.2  | Typical Application                                                                                                                               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pow  | er Supply Recommendations                                                                                                                         | 51                                                                                                                                                                                                                                                                                                                                                                                                                                  |

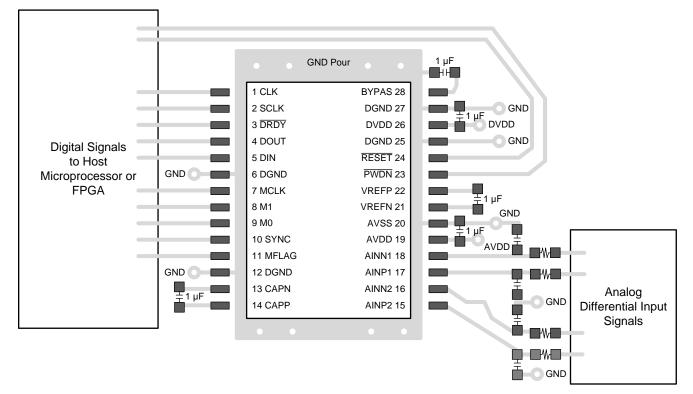

| Layo | out                                                                                                                                               | 52                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11.1 |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11.2 | Layout Example                                                                                                                                    | 53                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| デバ   | イスおよびドキュメントのサポート                                                                                                                                  | 54                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.1 | デバイス・サポート                                                                                                                                         | 54                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.2 | ドキュメントの更新通知を受け取る方法                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.3 | コミュニティ・リソース                                                                                                                                       | 57                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.4 | 商標                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.5 | 静電気放電に関する注意事項                                                                                                                                     | 57                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.6 | Glossary                                                                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                  |

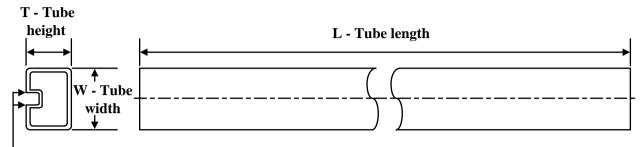

| メカニ  | ニカル、パッケージ、および注文情報                                                                                                                                 | 57                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      | 8.3<br>8.4<br>8.5<br>8.6<br><b>Appl</b><br>9.1<br>9.2<br><b>Pow</b><br>Layc<br>11.1<br>11.2<br>ブバ<br>12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6 | 8.3 Feature Description.<br>8.4 Device Functional Modes.<br>8.5 Programming.<br>8.6 Register Maps.<br>Application and Implementation<br>9.1 Application Information.<br>9.2 Typical Application<br>Power Supply Recommendations<br>Layout<br>11.1 Layout Guidelines<br>11.2 Layout Example<br>デバイスおよびドキュメントのサポート<br>12.1 デバイス・サポート<br>12.2 ドキュメントの更新通知を受け取る方法<br>12.3 コミュニティ・リソース<br>12.4 商標<br>12.5 静電気放電に関する注意事項<br>12.6 Glossary |

# 欠

www<u>.tij.co.jp</u>

### Page

Page

#### ADS1282-SP JAJSGE8B – MARCH 2016 – REVISED OCTOBER 2018

#### www.ti.com

#### 5 概要(続き)

このコンバータは、4次の本質的に安定なデルタ-シグマ(ΔΣ)変調器を使用しており、ノイズおよび線形性の性能が非常に 優れています。この変調器は、オンチップのデジタル・フィルタと組み合わせて使用することも、バイパスして後処理フィルタ とともに使用することもできます。

柔軟な入力マルチプレクサにより、測定用の追加の外部入力と、内部の自己テスト接続を使用できます。PGAは非常に低ノイズで(5nV/vHz)、入力インピーダンスが高いため、広い範囲のゲインで、トランスデューサと簡単に接続できます。

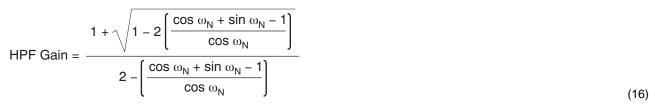

デジタル・フィルタは、毎秒250~4000サンプル(SPS)のデータ・レートを選択できます。ハイパス・フィルタ(HPF)はコーナー周波数を設定可能です。オンチップのゲインおよびオフセットのスケーリング・レジスタが、システム較正をサポートします。

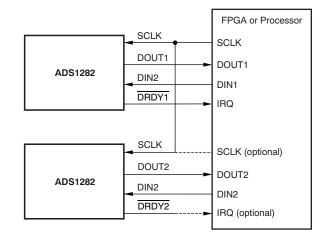

同期入力(SYNC)を使用して、複数のADS1282の変換を同期できます。SYNC入力はクロック入力も受け付け可能で、変換を外部のソースと継続的に同期できます。

アンプ、変調器、フィルタの合計消費電力は30mWです。ADS1282-SPは、-55℃~125℃で完全に動作が規定されています。

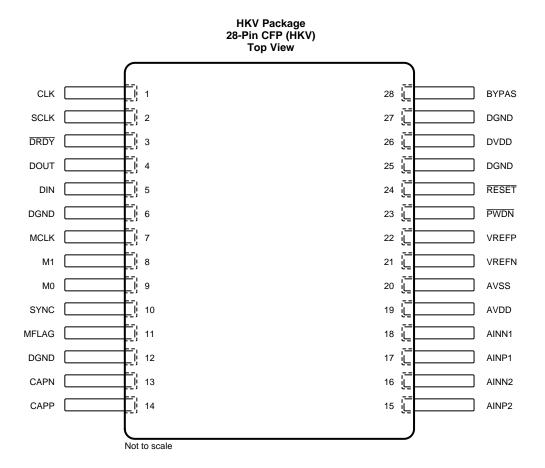

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN           |       | - I/O          | DESCRIPTION                                                                                                                              |  |  |  |

|---------------|-------|----------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO.           | NAME  | 1/0            | DESCRIPTION                                                                                                                              |  |  |  |

| 1             | CLK   | Digital input  | Master clock input                                                                                                                       |  |  |  |

| 2             | SCLK  | Digital input  | Serial clock input                                                                                                                       |  |  |  |

| 3             | DRDY  | Digital output | Data ready output: read data on falling edge                                                                                             |  |  |  |

| 4             | DOUT  | Digital output | Serial data output                                                                                                                       |  |  |  |

| 5             | DIN   | Digital input  | Serial data input                                                                                                                        |  |  |  |

| 6, 12, 27, 25 | DGND  | Digital ground | Digital ground, pin 12 is the key ground point                                                                                           |  |  |  |

| 7             | MCLK  | Digital I/O    | "Modulator clock output; if in modulator mode:<br>MCLK: Modulator clock output<br>Otherwise, the pin is an unused input (must be tied)." |  |  |  |

| 8             | M1    | Digital I/O    | "Modulator data output 1; if in modulator mode:<br>M1: Modulator data output 1<br>Otherwise, the pin is an unused input (must be tied)." |  |  |  |

| 9             | МО    | Digital I/O    | "Modulator data output 0; if in modulator mode:<br>M0: Modulator data output 0<br>Otherwise, the pin is an unused input (must be tied)." |  |  |  |

| 10            | SYNC  | Digital input  | Synchronize input                                                                                                                        |  |  |  |

| 11            | MFLAG | Digital output | Modulator Over-Range flag:<br>0 = Normal<br>1 = Modulator over-range                                                                     |  |  |  |

| 13            | CAPN  | Analog         | PGA outputs: Connect 10-nF capacitor from CAPP to CAPN                                                                                   |  |  |  |

| 14            | CAPP  | Analog         | PGA outputs: Connect 10-nF capacitor from CAPP to CAPN                                                                                   |  |  |  |

#### **Pin Functions (continued)**

| PIN |       | 1/0            | DESCRIPTION                                          |  |

|-----|-------|----------------|------------------------------------------------------|--|

| NO. | NAME  |                | DESCRIPTION                                          |  |

| 15  | AINP2 | Analog input   | Positive analog input 2                              |  |

| 16  | AINN2 | Analog input   | Negative analog input 2                              |  |

| 17  | AINP1 | Analog input   | Positive analog input 1                              |  |

| 18  | AINN1 | Analog input   | Negative analog input 1                              |  |

| 19  | AVDD  | Analog supply  | Positive analog power supply                         |  |

| 20  | AVSS  | Analog supply  | Negative analog power supply                         |  |

| 21  | VREFN | Analog input   | Negative reference input                             |  |

| 22  | VREFP | Analog input   | Positive reference input                             |  |

| 23  | PWDN  | Digital input  | Power-down input, active low                         |  |

| 24  | RESET | Digital input  | Reset input, active low                              |  |

| 26  | DVDD  | Digital supply | Digital power supply: 1.8 V to 3.3 V                 |  |

| 28  | BYPAS | Analog         | Sub-regulator output: Connect 1-µF capacitor to DGND |  |

#### **Specifications** 7

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted)<sup>(1)</sup>

|                                                                                                    | MIN        | MAX            | UNIT |

|----------------------------------------------------------------------------------------------------|------------|----------------|------|

| AVDD to AVSS                                                                                       | -0.3       | 5.5            | V    |

| AVSS to DGND                                                                                       | -2.8       | 0.3            | V    |

| DVDD to DGND                                                                                       | -0.3       | 3.9            | V    |

| Input current                                                                                      |            | 100, momentary | mA   |

| Input current                                                                                      |            | 10, continuous | mA   |

| Analog input voltage (AINP1, AINN1, AINP2, AINN2, VREFN, VREFP, CAPP, CAPN)                        | AVSS – 0.3 | AVDD + 0.3     | V    |

| Digital input voltage to DGND (CLK, SCLK, DRDY, DOUT, DIN, MCLK, M1, M0, MFLAG, SYNC, PWDN, RESET) | -0.3       | DVDD + 0.3     | V    |

| Storage temperature, T <sub>stg</sub>                                                              | -60        | 150            | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings (1) only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±1000 | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|    |                       |                 | MIN | NOM MAX | UNIT |

|----|-----------------------|-----------------|-----|---------|------|

| TJ |                       | 5962L1423101VXC | -55 | 125     | °C   |

|    | Operating temperature | 5962L1423102VXC | -55 | 115     |      |

#### ADS1282-SP

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

STRUMENTS

EXAS

www.ti.com

#### 7.4 Thermal Information

|                       |                                              | ADS1282-SP       |      |

|-----------------------|----------------------------------------------|------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | HKV [CFP (TBAR)] | UNIT |

|                       |                                              | 28 PINS          |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 64.4             | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 16               | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 58.6             | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 13.3             | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 50.5             | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 5.3              | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

AVDD = 2.5 V, AVSS = -2.5 V,  $f_{CLK}^{(1)}$  = 4.096 MHz, VREFP = 2.5 V, VREFN = -2.5 V, DVDD = 3.3 V, CAPN - CAPP = 10 nF, PGA = 1, and  $f_{DATA}$  = 1000 SPS, over operating temperature range, unless otherwise noted. Typical values are T<sub>J</sub> = 25°C. A total ionizing dose of 50 kRad (Si) exposure at a low dose rate of < 10 mRads (Si)/s, post tested at 25°C.

| PARAMETER       |                                              | TEST CONDITIONS          | 5962          | 5962L1423101VXC |                | 5962L1423102VXC |          |                | UNIT     |

|-----------------|----------------------------------------------|--------------------------|---------------|-----------------|----------------|-----------------|----------|----------------|----------|

|                 |                                              | TEST CONDITIONS          | MIN           | TYP             | MAX            | MIN             | TYP      | MAX            | UNIT     |

| ANALO           | G INPUTS                                     | -                        |               |                 |                |                 |          |                |          |

|                 | Full-scale input voltage                     | $V_{IN} = (AINP - AINN)$ | (VREFP        | – VREFN)        | / (PGA)        | (VREFP -        | - VREFN) | / (PGA)        | Vpp-diff |

| AINP or<br>AINN | Absolute input<br>range                      |                          | AVSS +<br>0.7 |                 | AVDD –<br>1.25 | AVSS +<br>0.7   |          | AVDD –<br>1.25 | V        |

|                 | PGA input voltage noise density              |                          |               | 5               |                |                 | 5        |                | nV/√Hz   |

|                 | Differential input impedance <sup>(2)</sup>  |                          |               | 1               |                |                 | 1        |                | GΩ       |

|                 | Common-mode<br>input impedance               |                          |               | 100             |                |                 | 100      |                | MΩ       |

|                 | Input bias current                           |                          |               | 1               |                |                 | 1        |                | nA       |

|                 | Crosstalk                                    | f = 31.25 Hz             |               | -128            |                |                 | -128     |                | dB       |

|                 | MUX on-<br>resistance                        |                          |               | 30              |                |                 | 30       |                | Ω        |

| PGA OL          | JTPUT (CAPP, CAP                             | ۷)                       |               |                 |                |                 |          |                |          |

|                 | Absolute output range                        |                          | AVSS + 0.4    |                 | AVDD - 0.4     | AVSS +<br>0.4   |          | AVDD -<br>0.4  | V        |

|                 | PGA differential<br>output impedance         |                          |               | 600             |                |                 | 600      |                | Ω        |

|                 | Output impedance tolerance                   |                          |               | ±10%            |                |                 | ±10%     |                |          |

|                 | External bypass capacitance                  |                          |               | 10              | 100            |                 | 10       | 100            | nF       |

|                 | Modulator<br>differential input<br>impedance |                          |               | 55              |                |                 | 55       |                | kΩ       |

| AC PER          | FORMANCE                                     |                          |               |                 |                |                 |          |                |          |

| SNR             | Signal-to-noise<br>ratio <sup>(3)</sup>      |                          | 112           | 124             |                | 112             | 124      |                | dB       |

(1)  $f_{CLK}$  = system clock.

Input impedance is improved by disabling input chopping (CHOP bit = 0).  $V_{IN} = 20 \text{ mV}_{DC} / \text{PGA}$ , see Table 1. (2)

(3)

#### **Electrical Characteristics (continued)**

AVDD = 2.5 V, AVSS = -2.5 V,  $f_{CLK}^{(1)}$  = 4.096 MHz, VREFP = 2.5 V, VREFN = -2.5 V, DVDD = 3.3 V, CAPN - CAPP = 10 nF, PGA = 1, and  $f_{DATA}$  = 1000 SPS, over operating temperature range, unless otherwise noted. Typical values are T<sub>J</sub> = 25°C. A total ionizing dose of 50 kRad (Si) exposure at a low dose rate of < 10 mRads (Si)/s, post tested at 25°C.

| -             |                                             | TEST CONDITIONS                     |                                                                 | 5962L1423101VXC |         |                        | 5962L1423102VXC |             |                           | UNIT              |

|---------------|---------------------------------------------|-------------------------------------|-----------------------------------------------------------------|-----------------|---------|------------------------|-----------------|-------------|---------------------------|-------------------|

| F             | PARAMETER                                   |                                     |                                                                 | MIN             | TYP     | MAX                    | MIN             | ТҮР         | MAX                       | UNIT              |

|               |                                             | PGA = 1                             | 16                                                              |                 | -122    | -99                    |                 | -122        | -101                      |                   |

| THD           | Total harmonic distortion <sup>(4)</sup>    | PGA = 32                            |                                                                 |                 | -117    | -90                    |                 | -117        | -92                       | dB                |

|               | 0.0101.011                                  | PGA = 64                            |                                                                 |                 | -115    |                        |                 | -115        |                           |                   |

| SFDR          | Spurious-free<br>dynamic range              |                                     |                                                                 |                 | 123     |                        |                 | 123         |                           | dB                |

| DC PER        | FORMANCE                                    |                                     |                                                                 |                 |         |                        |                 |             |                           |                   |

|               | Resolution                                  | No missing                          | g codes                                                         | 31              |         |                        | 31              |             |                           | bits              |

| <i>f</i> data | Data rate                                   | FIR filter n                        | node                                                            | 250             |         | 4000                   | 250             |             | 4000                      | SPS               |

| JDATA         | Data Tate                                   | SINC filter                         | mode                                                            | 8000            |         | 128000                 | 8000            |             | 128000                    | 010               |

|               | Integral                                    | Differenti                          |                                                                 |                 | 0.00005 | 0.0090                 |                 | 0.00005     | 0.0090                    | %                 |

|               | nonlinearity<br>(INL) <sup>(5)</sup>        | al input                            | Offset error                                                    |                 |         | 0.0170                 |                 |             | 0.0170                    | FSR <sup>(6</sup> |

|               | Offset error after                          |                                     |                                                                 |                 | 50      | 200                    |                 | 50          | 200                       |                   |

|               | calibration <sup>(7)</sup>                  | Observational                       | Offset drift                                                    |                 |         | 750                    |                 |             | 750                       | μV                |

|               | Gain error <sup>(8)</sup>                   | Shorted input                       |                                                                 |                 | 1       |                        |                 | 1           |                           | μV                |

|               | Gain error after calibration <sup>(7)</sup> |                                     |                                                                 |                 | 0.02    |                        |                 | 0.02        |                           | μV/°C             |

|               | Gain drift                                  |                                     |                                                                 | -1.5%           | -1.0%   | -0.5%                  | -1.5%           | -1.0%       | -0.5%                     |                   |

|               | Gain matching <sup>(9)</sup>                |                                     |                                                                 |                 | 0.0002% |                        |                 | 0.0002<br>% |                           |                   |

|               | Common-mode                                 | PGA = 1                             |                                                                 |                 | 2       |                        |                 | 2           |                           | ppm/°(            |

|               | rejection                                   | PGA = 16                            |                                                                 |                 | 9       |                        |                 | 9           |                           | ppm/ V            |

|               |                                             |                                     |                                                                 |                 | 0.3%    | 0.8%                   |                 | 0.3%        | 0.8%                      |                   |

|               |                                             | $f_{\rm CM} = 60$ H                 | Hz <sup>(10)</sup>                                              | 82              | 110     |                        | 82              | 110         |                           | dB                |

|               |                                             |                                     |                                                                 | 80              | 90      |                        | 80              | 90          |                           | dB                |

| AVDD,<br>AVSS | Power-supply rejection                      | $f_{PS} = 60$<br>Hz <sup>(10)</sup> | Post 50<br>kRads (Si), T <sub>J</sub><br>= 25°C <sup>(11)</sup> | 64              | 90      |                        | 64              | 90          |                           | dB                |

| DVDD          | _                                           |                                     |                                                                 | 90              | 115     |                        | 90              | 115         |                           | dB                |

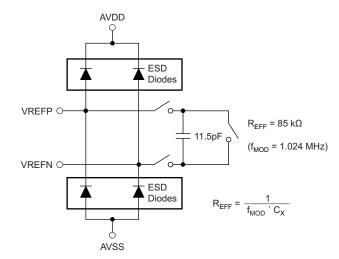

| VOLTA         | GE REFERENCE INF                            | PUTS                                |                                                                 |                 |         |                        |                 |             |                           |                   |

|               | Reference input voltage                     | (V <sub>REF</sub> = VI<br>VREFN)    | REFP –                                                          | 0.5             | 5       | (AVDD –<br>AVSS) + 0.2 | 0.5             | 5           | (AVDD -<br>AVSS) +<br>0.2 | V                 |

| VREFN         | Negative<br>reference input                 |                                     |                                                                 | AVSS –<br>0.1   |         | VREFP –<br>0.5         | AVSS -<br>0.1   |             | VREFP - 0.5               | V                 |

| VREFP         | Positive reference input                    |                                     |                                                                 | VREFN<br>+ 0.5  |         | AVDD + 0.1             | VREFN +<br>0.5  |             | AVDD +<br>0.1             | V                 |

|               | Reference input impedance                   |                                     |                                                                 |                 | 85      |                        |                 | 85          |                           | kΩ                |

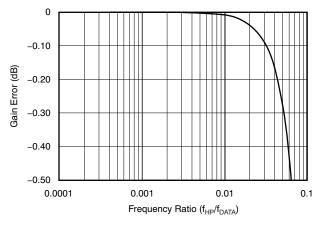

| DIGITAI       | FILTER RESPONS                              | E                                   |                                                                 |                 |         |                        |                 |             |                           |                   |

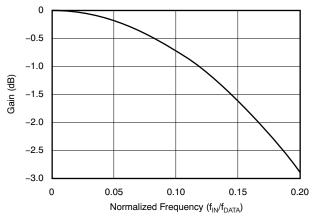

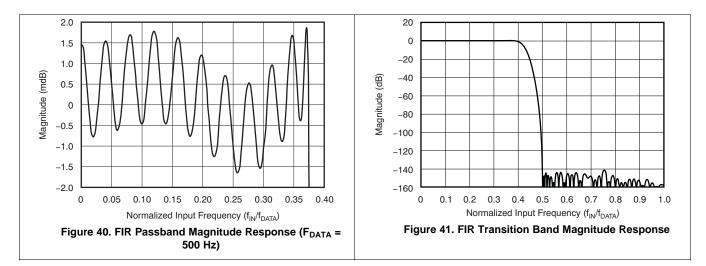

|               | Passband ripple                             |                                     |                                                                 |                 |         | ±0.003                 |                 |             | ±0.003                    | dB                |

(4)  $V_{IN} = 31.25 \text{ Hz}, -0.5 \text{ dBFS}.$

Best-fit method. (5)

(6) FSR: Full-scale range = ±V<sub>REF</sub> / (2 × PGA).

(7) Calibration accuracy is on the level of noise reduced by 4 (calibration averages 16 readings).

(8) The PGA output impedance and the modulator input impedance results in -1% systematic gain error.

Gain match relative to PGA = 1. (9)

(10)  $f_{CM}$  is the input common-mode frequency.  $f_{PS}$  is the power-supply frequency.

(11) The maximum limit applies to SMD 5962L14231 post 50 kRads (Si) test at 25°C.

Copyright © 2016–2018, Texas Instruments Incorporated

#### ADS1282-SP

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

www.ti.com

#### **Electrical Characteristics (continued)**

AVDD = 2.5 V, AVSS = -2.5 V,  $f_{CLK}^{(1)}$  = 4.096 MHz, VREFP = 2.5 V, VREFN = -2.5 V, DVDD = 3.3 V, CAPN - CAPP = 10 nF, PGA = 1, and  $f_{DATA}$  = 1000 SPS, over operating temperature range, unless otherwise noted. Typical values are T<sub>J</sub> = 25°C. A total ionizing dose of 50 kRad (Si) exposure at a low dose rate of < 10 mRads (Si)/s, post tested at 25°C.

|                  |                                       | TEST CONDITIONS         |                                                                 | 5962L1423101VXC |                                |                      | 5962L1423102VXC |                              |                   |      |

|------------------|---------------------------------------|-------------------------|-----------------------------------------------------------------|-----------------|--------------------------------|----------------------|-----------------|------------------------------|-------------------|------|

| I                | PARAMETER                             | TEST C                  | ONDITIONS                                                       | MIN             | TYP                            | MAX                  | MIN             | TYP                          | MAX               | UNIT |

|                  | Passband (–0.01<br>dB)                |                         |                                                                 | 0.              | 375 × $f_{DATA}$               |                      |                 | 0.375 ×<br>f <sub>DATA</sub> |                   | Hz   |

|                  | Bandwidth (–3<br>dB)                  |                         |                                                                 | 0.              | 413 × <i>f</i> <sub>DATA</sub> |                      |                 | 0.413 ×<br>f <sub>DATA</sub> |                   | Hz   |

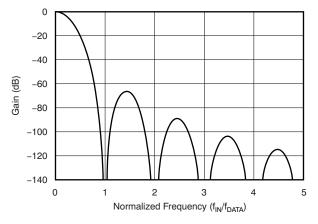

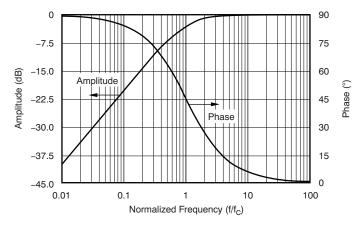

|                  | High-pass filter<br>corner            |                         |                                                                 | 0.1             |                                | 10                   | 0.1             |                              | 10                | Hz   |

|                  | Stop band attenuation <sup>(12)</sup> |                         |                                                                 | 135             |                                |                      | 135             |                              |                   | dB   |

|                  | Stop band                             |                         |                                                                 | 0.              | 500 × f <sub>DATA</sub>        |                      |                 | 0.500 ×<br>ƒ <sub>DATA</sub> |                   | Hz   |

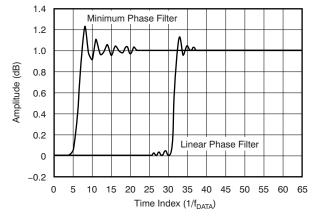

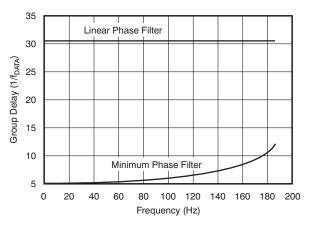

|                  | Group delay                           | Minimum p               | bhase filter <sup>(13)</sup>                                    |                 | 5 / f <sub>DATA</sub>          |                      |                 | 5 /<br>f <sub>DATA</sub>     |                   | S    |

|                  |                                       | Settling tim            | ne (latency)                                                    |                 | 31 / <i>f</i> <sub>DATA</sub>  |                      |                 | 31 /<br>f <sub>DATA</sub>    |                   | S    |

|                  |                                       | Minimum p               | hase filter                                                     |                 | 62 / f <sub>DATA</sub>         |                      |                 | 62 /<br>ƒ <sub>DATA</sub>    |                   | S    |

|                  |                                       | Linear phase filter     |                                                                 |                 | 62 / f <sub>DATA</sub>         |                      |                 | 62 /<br>ƒ <sub>DATA</sub>    |                   | S    |

| DIGITA           | L INPUT/OUTPUT                        | 1                       |                                                                 | 1               |                                |                      |                 |                              |                   |      |

| V <sub>IH</sub>  |                                       |                         |                                                                 | 0.8 ×<br>DVDD   |                                | DVDD                 | 0.8 ×<br>DVDD   |                              | DVDD              | V    |

| V <sub>IL</sub>  |                                       |                         |                                                                 | DGND            |                                | 0.2 × DVDD           | DGND            |                              | 0.2 ×<br>DVDD     | V    |

| V <sub>OH</sub>  |                                       | I <sub>OH</sub> = 1 mA  | <b>\</b>                                                        | 0.8 ×<br>DVDD   |                                |                      | 0.8 ×<br>DVDD   |                              |                   | V    |

| V <sub>OL</sub>  |                                       | $I_{OL} = 1 \text{ mA}$ |                                                                 |                 |                                | 0.2 × DVDD           |                 |                              | 0.2 ×<br>DVDD     | V    |

|                  | Input leakage                         | 0 < V <sub>DIGITA</sub> | <sub>IL IN</sub> < DVDD                                         |                 |                                | ±10                  |                 |                              | ±10               | μA   |

| f <sub>CLK</sub> | Clock input                           |                         |                                                                 | 1               |                                | 4.096                | 1               |                              | 4.096             | MHz  |

| $f_{SCLK}$       | Serial clock rate                     |                         |                                                                 |                 |                                | f <sub>CLK</sub> / 2 |                 |                              | $f_{\rm CLK}$ / 2 | MHz  |

| POWEF            | R SUPPLY                              | 1                       |                                                                 | 1               |                                |                      |                 |                              |                   |      |

| AVSS             |                                       |                         |                                                                 | -2.6            |                                | 0                    | -2.6            |                              | 0                 | V    |

| AVDD             |                                       |                         |                                                                 | AVSS +<br>4.75  |                                | AVSS +<br>5.25       | AVSS +<br>4.75  |                              | AVSS +<br>5.25    | V    |

| DVDD             |                                       |                         |                                                                 | 1.75            |                                | 3.6                  | 1.75            |                              | 3.6               | V    |

|                  |                                       | High-                   |                                                                 |                 | 4.5                            | 7.2                  |                 | 4.5                          | 6.5               | mA   |

|                  |                                       | resolution<br>mode      | Post 50<br>kRads (Si), T <sub>J</sub><br>= 25°C <sup>(11)</sup> |                 |                                | 11                   |                 |                              | 11                | mA   |

|                  | AVDD, AVSS<br>current                 | David                   |                                                                 |                 | -200                           | 200                  |                 | -200                         | 200               | μA   |

|                  |                                       | Power-<br>down<br>mode  | Post 50<br>kRads (Si), T <sub>J</sub><br>= 25°C <sup>(11)</sup> |                 |                                | 5                    |                 |                              | 5                 | mA   |

|                  |                                       |                         |                                                                 |                 | -200                           | 200                  |                 | -200                         | 200               | μA   |

|                  |                                       | Standby mode            | Post 50<br>kRads (Si), T <sub>J</sub><br>= 25°C <sup>(11)</sup> |                 |                                | 5                    |                 |                              | 5                 | mA   |

(12) Input frequencies in the range of Nf<sub>CLK</sub> / 512 ± f<sub>DATA</sub> / 2 (N = 1, 2, 3...) can mix with the modulator chopping clock. In these frequency ranges intermodulation = 120 dB, typ.

(13) At DC. See Figure 42.

#### **Electrical Characteristics (continued)**

AVDD = 2.5 V, AVSS = -2.5 V,  $f_{CLK}^{(1)}$  = 4.096 MHz, VREFP = 2.5 V, VREFN = -2.5 V, DVDD = 3.3 V, CAPN - CAPP = 10 nF, PGA = 1, and  $f_{DATA}$  = 1000 SPS, over operating temperature range, unless otherwise noted. Typical values are T<sub>J</sub> = 25°C. A total ionizing dose of 50 kRad (Si) exposure at a low dose rate of < 10 mRads (Si)/s, post tested at 25°C.

| PARAMETER         | TEST CONDITIONS             |                                                                 | 5962 | 5962L1423101VXC |      |     | 5962L1423102VXC |      |      |

|-------------------|-----------------------------|-----------------------------------------------------------------|------|-----------------|------|-----|-----------------|------|------|

| PARAMETER         |                             |                                                                 | MIN  | TYP             | MAX  | MIN | TYP             | MAX  | UNIT |

|                   | High-resol                  | ution mode                                                      |      | 0.6             | 1.5  |     | 0.6             | 1.2  | mA   |

| DVDD current      | Power-dov                   | vn mode <sup>(14)</sup>                                         |      | 32              | 120  |     | 32              | 120  | μA   |

|                   | Standby m                   | ode                                                             |      | 73              | 175  |     | 73              | 175  | μA   |

|                   | Lliab                       |                                                                 |      | 25              | 41   |     | 25              | 41   | mW   |

|                   | High-<br>resolution<br>mode | Post 50<br>kRads (Si), T <sub>J</sub><br>= 25°C <sup>(11)</sup> |      |                 | 60   |     |                 | 60   | mW   |

|                   | Dowor                       |                                                                 |      | 0.45            | 0.95 |     | 0.45            | 0.95 | mW   |

| Power dissipation | ation down<br>mode          | Post 50<br>kRads (Si), T <sub>J</sub><br>= 25°C <sup>(11)</sup> |      |                 | 25.4 |     |                 | 25.4 | mW   |

|                   |                             |                                                                 |      | 0.58            | 1.1  |     | 0.58            | 1.1  | mW   |

|                   | Standby<br>mode             | Post 50<br>kRads (Si), T <sub>J</sub><br>= 25°C <sup>(11)</sup> |      |                 | 25.4 |     |                 | 25.4 | mW   |

(14) CLK input stopped.

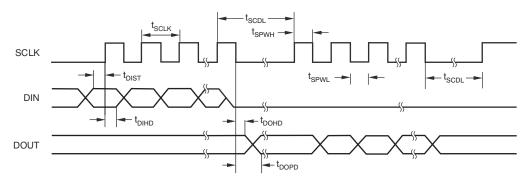

#### 7.6 Timing Requirements

At  $T_A = -55^{\circ}C$  to  $125^{\circ}C$  and DVDD = 1.65 to 3.6 V, unless otherwise noted.

|                      |                                                                                          | MIN | MAX | UNIT                 |

|----------------------|------------------------------------------------------------------------------------------|-----|-----|----------------------|

| t <sub>SCLK</sub>    | SCLK period                                                                              | 2   | 16  | 1 / f <sub>CLK</sub> |

| t <sub>SPWH, L</sub> | SCLK pulse width, high and low <sup>(1)</sup>                                            | 0.8 | 10  | 1 / f <sub>CLK</sub> |

| t <sub>DIST</sub>    | DIN valid to SCLK rising edge: setup time                                                | 50  |     | ns                   |

| t <sub>DIHD</sub>    | Valid DIN to SCLK rising edge: hold time                                                 | 50  |     | ns                   |

| t <sub>DOPD</sub>    | SCLK falling edge to valid new DOUT: propagation delay <sup>(2)</sup>                    |     | 100 | ns                   |

| t <sub>DOHD</sub>    | SCLK falling edge to DOUT invalid: hold time                                             | 0   |     | ns                   |

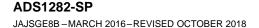

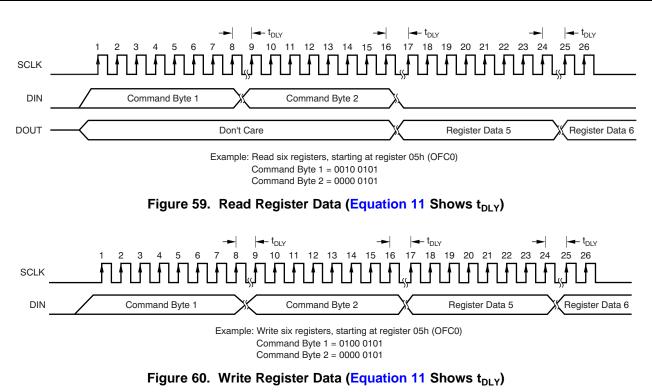

| t <sub>SCDL</sub>    | Final SCLK rising edge of command to first SCLK rising edge for register read/write data | 24  |     | 1 / f <sub>CLK</sub> |

(1) Holding SCLK low for 64 DRDY falling edges resets the serial interface.

(2) Load on DOUT = 20 pF || 100 k $\Omega$ .

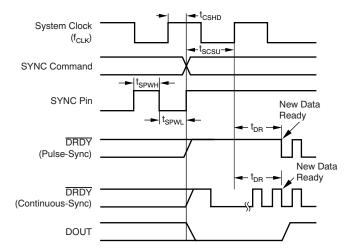

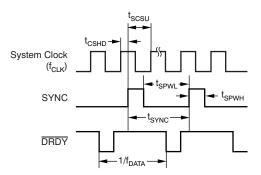

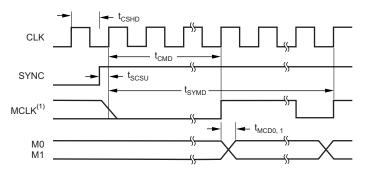

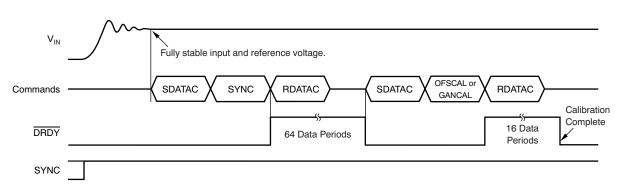

#### 7.7 Pulse-Sync Timing Requirements

See Figure 46 and Figure 47 for timing diagrams.

|                      |                                                | MIN                                   | MAX U             | INIT       |

|----------------------|------------------------------------------------|---------------------------------------|-------------------|------------|

| t <sub>SYNC</sub>    | SYNC period <sup>(1)</sup>                     | 1 Ir                                  | nfinite n /       | $f_{DATA}$ |

| t <sub>CSHD</sub>    | CLK to SYNC hold time to not latch on CLK edge | 10                                    |                   | ns         |

| t <sub>SCSU</sub>    | SYNC to CLK setup time to latch on CLK edge    | 10                                    |                   | ns         |

| t <sub>SPWH, L</sub> | SYNC pulse width, high or low                  | 2                                     | 1 /               | fclk       |

|                      | Time for data ready (SINC filter)              | See デバイス・サポート,                        | 表 21              |            |

| τ <sub>DR</sub>      | Time for data ready (FIR filter)               | 62.98046875 / f <sub>DATA</sub> + 466 | /f <sub>clk</sub> |            |

(1) Continuous-Sync mode; a free-running SYNC clock input without causing re-synchronization.

#### ADS1282-SP

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

www.ti.com

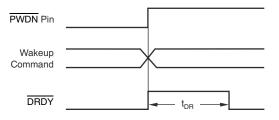

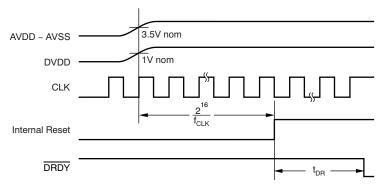

## 7.8 Reset Timing Requirements

See Figure 48 for timing diagram.

|                   |                         | MIN M.                                                   | X UNIT               |

|-------------------|-------------------------|----------------------------------------------------------|----------------------|

| t <sub>CRHD</sub> | CLK to RESET hold time  | 10                                                       | ns                   |

| t <sub>RCSU</sub> | RESET to CLK setup time | 10                                                       | ns                   |

| t <sub>RST</sub>  | RESET low               | 2                                                        | 1 / f <sub>CLK</sub> |

| t <sub>DR</sub>   | Time for data ready     | 62.98046875 / f <sub>DATA</sub> + 468 / f <sub>CLK</sub> | S                    |

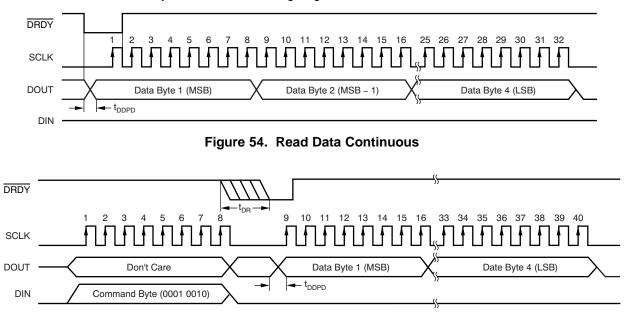

#### 7.9 Read Data Timing Requirements

|                   |                                                                            | MIN | MAX | UNIT       |

|-------------------|----------------------------------------------------------------------------|-----|-----|------------|

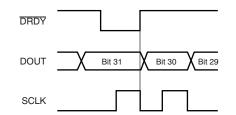

| t <sub>DDPD</sub> | DRDY to valid MSB on DOUT propagation delay (see Figure 54) <sup>(1)</sup> |     | 100 | ns         |

| t <sub>DR</sub>   | Time for new data after data read command (see Figure 55)                  | 0   | 1   | $f_{DATA}$ |

(1) Load on DOUT = 20 pF || 100 k $\Omega$ .

#### 7.10 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                  | TEST CONDITIONS      | MIN                          | TYP                    | MAX | UNIT |

|----------------------------|----------------------|------------------------------|------------------------|-----|------|

| Group delay <sup>(1)</sup> | Minimum phase filter | 5 / <i>f</i> <sub>DATA</sub> |                        |     | s    |

| Group delay                | Linear phase filter  | 31 / f <sub>DATA</sub>       |                        |     | s    |

| Settling time              | Minimum phase filter | 6                            | 62 / f <sub>DATA</sub> |     | s    |

| (latency)                  | Linear phase filter  | 6                            | 62 / f <sub>DATA</sub> |     | S    |

(1) At DC. See Figure 42.

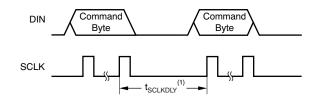

Figure 1. Timing Diagram

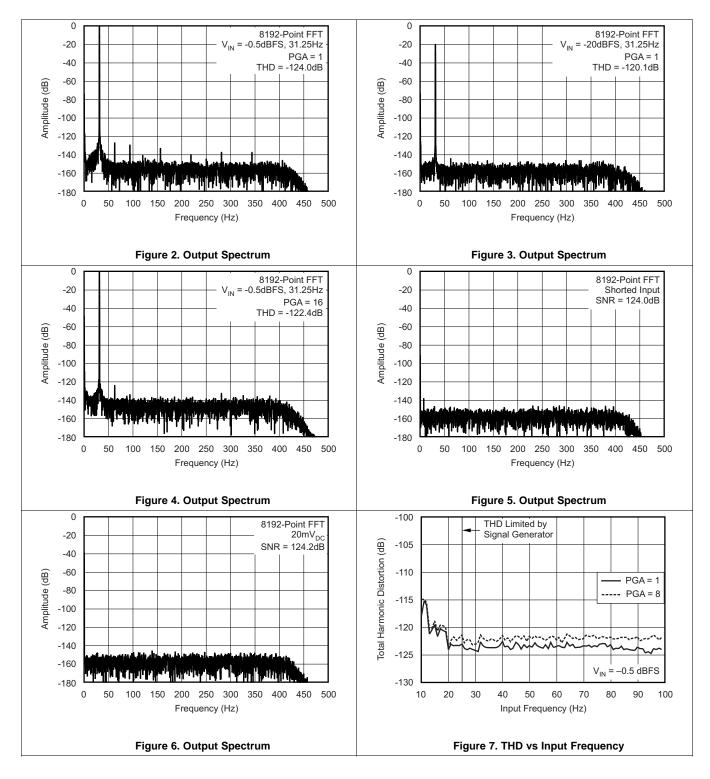

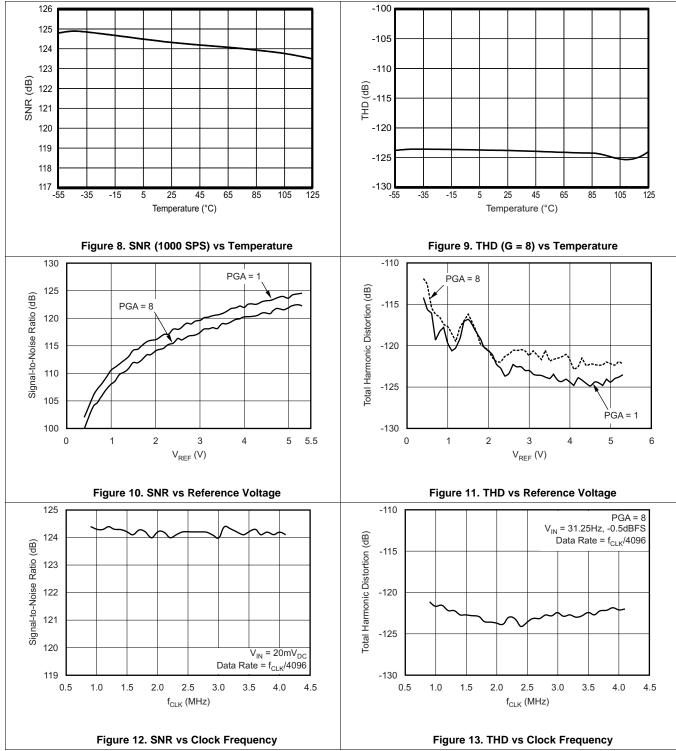

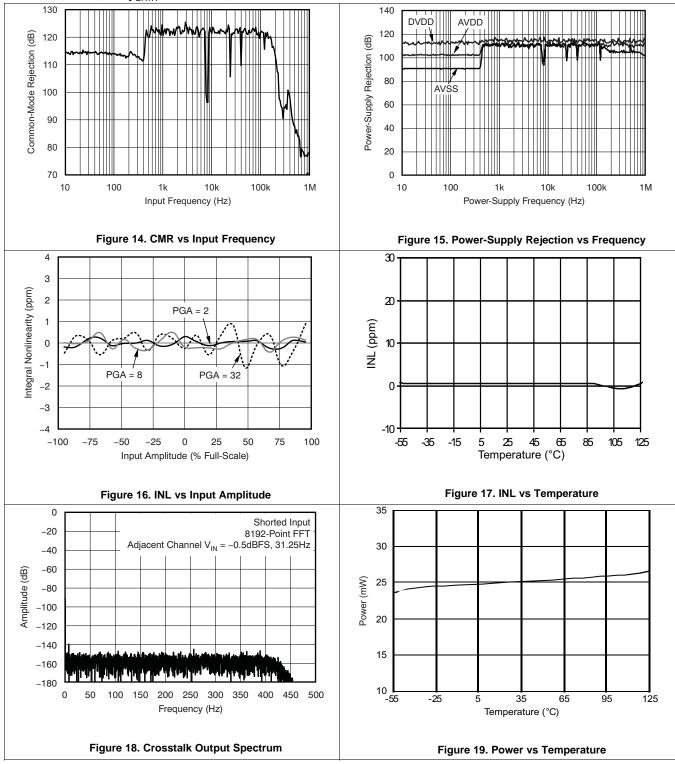

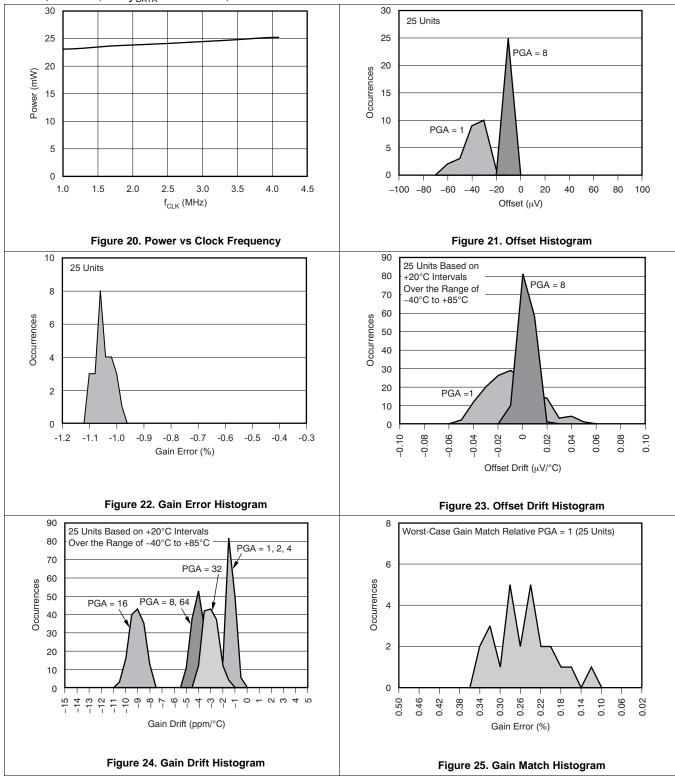

#### 7.11 Typical Characteristics

#### TEXAS INSTRUMENTS

#### ADS1282-SP

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

www.ti.com

#### **Typical Characteristics (continued)**

#### **Typical Characteristics (continued)**

#### TEXAS INSTRUMENTS

#### ADS1282-SP

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

www.ti.com

#### **Typical Characteristics (continued)**

#### 8 Detailed Description

#### 8.1 Overview

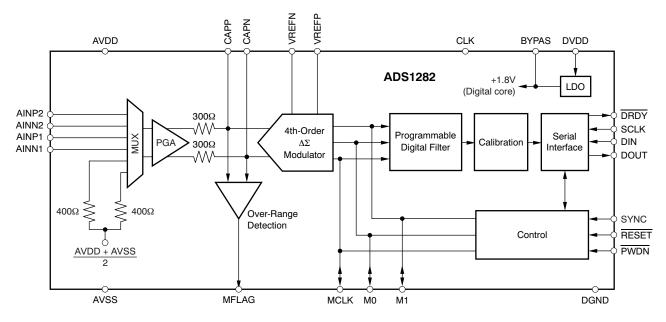

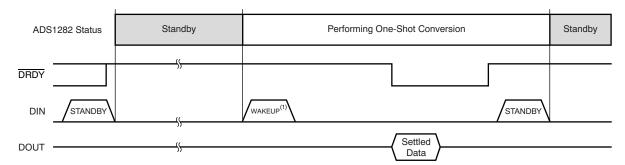

The ADS1282-SP is a high-performance analog-to-digital converter (ADC) intended for space satellite temperature sensing, precision scientific and high accuracy applications. The converter provides 24- or 32-bit output data in data rates from 250 SPS to 4000 SPS. The *Functional Block Diagram* shows the block diagram of the ADS1282-SP.

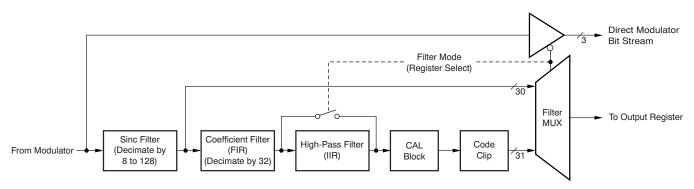

The two-channel input MUX allows five configurations: Input 1; Input 2; Input 1 and Input 2 shorted together; shorted with  $400-\Omega$  test; and common-mode test. The input MUX is followed by a continuous time PGA, featuring very low noise of 5 nV/ $\sqrt{\text{Hz}}$ . The PGA is controlled by register settings, allowing gains of 1 to 64, in powers of 2.

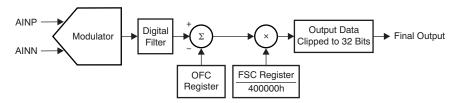

The inherently-stable, fourth-order, delta-sigma modulator measures the differential input signal  $V_{IN} = (AINP - AINN) \times PGA$  against the differential reference  $V_{REF} = (VREFP - VREFN)$ . A digital output (MFLAG) indicates that the modulator is in overload as a result of an overdrive condition. The modulator output is available directly on the MCLK, M0, and M1 output pins when in modulator mode. The modulator connects to an on-chip digital filter that provides the output code readings.

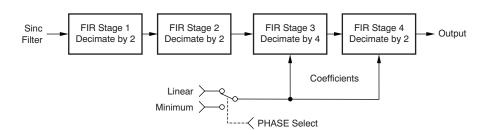

The digital filter consists of a variable decimation rate, fifth-order sinc filter followed by a variable phase, decimate-by-32, finite-impulse response (FIR) low-pass filter with programmable phase, and then by an adjustable high-pass filter for DC removal of the output reading. The output of the digital filter can be taken from the sinc, the FIR low-pass, or the infinite impulse response (IIR) high-pass sections as long as the maximum clock rate of the SPI (fclk/2) is respected.

Gain and offset registers scale the digital filter output to produce the final code value. The scaling feature can be used for calibration and sensor gain matching. The output data word is provided as either a 24-bit word or a full 32-bit word, allowing complete utilization of the inherently high resolution.

The SYNC input resets the operation of both the digital filter and the modulator, allowing synchronization conversions of multiple ADS1282-SP devices to an external event. The SYNC input supports a continuously-toggled input mode that accepts an external data frame clock locked to the conversion rate.

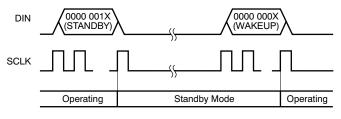

The RESET input resets the register settings and also restarts the conversion process. The PWDN input sets the device into a micro-power state. The register settings are not retained in PWDN mode. Use the STANDBY command in its place if it is desired to retain register settings (the quiescent current in the Standby mode is slightly higher).

Noise-immune Schmitt-trigger and clock-qualified inputs (RESET and SYNC) provide increased reliability in highnoise environments. The serial interface is used to read conversion data, in addition to reading from and writing to the configuration registers.

The device features unipolar and bipolar analog power supplies (AVDD and AVSS, respectively) for input range flexibility and a digital supply accepting 1.8 V to 3.3 V. The analog supplies may be set to 5 V to accept unipolar signals (with input offset) or set lower in the range of  $\pm 2.5$  V to accept true bipolar input signals (ground referenced).

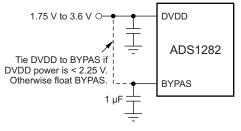

An internal sub-regulator is used to supply the digital core from DVDD. The BYPAS pin (pin 28) is the sub-regulator output and requires a  $1-\mu F$  capacitor for noise reduction. BYPAS should not be used to drive external circuitry.

ADS1282-SP JAJSGE8B – MARCH 2016 – REVISED OCTOBER 2018

www.ti.com

(1)

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Noise Performance

The ADS1282-SP device offers outstanding noise performance (SNR). SNR depends on the data rate, the PGA setting, and the mode. As the bandwidth is reduced by decreasing the data rate, the SNR improves correspondingly. Similarly, as the PGA gain is increased, the SNR decreases. Table 1 summarizes the noise performance versus data rate, PGA setting, and mode.

#### 8.3.2 Input-Referred Noise

The input-referred noise is related to SNR by Equation 1:

$\text{SNR} = 20 \text{log} \; \frac{\text{FSR}_{\text{RMS}}}{\text{N}_{\text{RMS}}}$

where:

- FSR<sub>RMS</sub> = Full-scale range RMS = (VREFP VREFN)/(2 ×  $\sqrt{2}$  × PGA)

- N<sub>RMS</sub> = Noise RMS (input-referred)

8.3.3 Idle Tones

The ADS1282-SP modulator incorporates an internal dither signal that randomizes the idle tone energy. Low-level idle tones may still be present, typically -137-dB less than full-scale. The low-level idle tones can be shifted out of the passband with an external offset = 20 mV/PGA. See the *Application Information* section for the recommended offset circuit.

#### Feature Description (continued)

#### 8.3.4 Operating Mode

The default mode is high-resolution.

|                 |     | PGA |     |     |     |     |     |  |  |

|-----------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| DATA RATE (SPS) | 1   | 2   | 4   | 8   | 16  | 32  | 64  |  |  |

| 250             | 130 | 130 | 129 | 128 | 125 | 119 | 114 |  |  |

| 500             | 127 | 127 | 126 | 125 | 122 | 116 | 111 |  |  |

| 1000            | 124 | 124 | 123 | 122 | 119 | 113 | 108 |  |  |

| 2000            | 121 | 121 | 120 | 119 | 116 | 111 | 106 |  |  |

| 4000            | 118 | 118 | 117 | 116 | 113 | 108 | 103 |  |  |

#### Table 1. Signal-to-Noise Ratio (dB)<sup>(1)</sup>

(1)  $V_{IN} = 20 \text{ mV}_{DC} / \text{PGA}.$

#### 8.3.5 Analog Inputs and Multiplexer

Figure 26 shows a diagram of the input multiplexer.

ESD diodes protect the multiplexer inputs. If either input is taken less than AVSS – 0.3 V or greater than AVDD + 0.3 V, the ESD protection diodes may turn on. If these conditions are possible, external Schottky clamp diodes and/or series resistors may be required to limit the input current to safe values (see the *Absolute Maximum Ratings*).

Also, overdriving one unused input may affect the conversions of the other input. If overdriven inputs are possible, TI recommends clamping the signal with external Schottky diodes.

Figure 26. Analog Inputs and Multiplexer

The specified input operating range of the PGA is shown in Equation 2:

AVSS + 0.7 V < (AINN or AINP) < AVDD - 1.25 V

Absolute input levels (input signal level and common-mode level) should be maintained within these limits for best operation.

(2)

The multiplexer connects one of the two external differential inputs to the preamplifier inputs, in addition to internal connections for various self-test modes. Table 2 summarizes the multiplexer configurations for Figure 26.

| MUX[2:0] | SWITCHES                                                          | DESCRIPTION                                                                 |

|----------|-------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 000      | S <sub>1</sub> , S <sub>5</sub>                                   | AINP1 and AINN1 connected to preamplifier                                   |

| 001      | S <sub>2</sub> , S <sub>6</sub>                                   | AINP2 and AINN2 connected to preamplifier                                   |

| 010      | S <sub>3</sub> , S <sub>4</sub>                                   | Preamplifier inputs shorted together through $400\Omega$ internal resistors |

| 011      | S <sub>1</sub> , S <sub>5</sub> , S <sub>2</sub> , S <sub>6</sub> | AINP1, AINN1 and AINP2, AINN2 connected together and to the preamplifier    |

| 100      | S <sub>6</sub> , S <sub>7</sub>                                   | External short, preamplifier inputs shorted to AINN2 (common-mode test)     |

| Table 2. Multiplexer Mode |

|---------------------------|

|---------------------------|

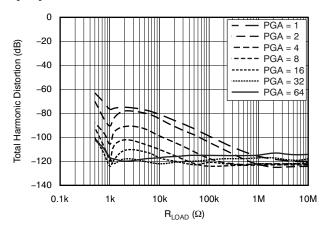

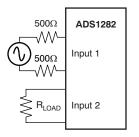

The typical on-resistance ( $R_{ON}$ ) of the multiplexer switch is 30  $\Omega$ . When the multiplexer is used to drive an external load on one input by a signal generator on the other input, on-resistance and on-resistance amplitude dependency can lead to measurement errors. Figure 27 shows THD versus load resistance and amplitude. THD improves with high-impedance loads and with lower amplitude drive signals. The data are measured with the circuit from Figure 28 with MUX[2:0] = 011.

Figure 27. THD vs External Load and Signal Magnitude (PGA) (See Figure 28)

Figure 28. Driving an External Load Through the MUX

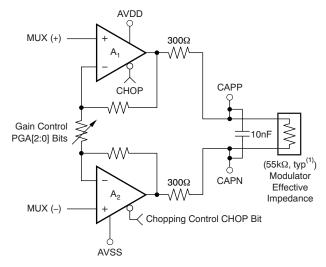

#### 8.3.6 PGA (Programmable Gain Amplifier)

The PGA of the ADS1282-SP is a low-noise, continuous-time, differential-in/differential-out CMOS amplifier. The gain is programmable from 1 to 64, set by register bits, PGA[2:0]. The PGA differentially drives the modulator through  $300-\Omega$  internal resistors. A COG capacitor (10 nF typical) must be connected to CAPP and CAPN to filter modulator sampling glitches. The external capacitor also serves as an anti-alias filter. The corner frequency is given in Equation 3:

$$f_{\rm P} = \frac{1}{6.3 \times 600 \times C}$$

(3)

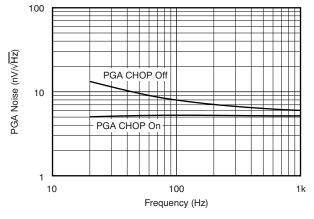

Referring to Figure 29, amplifiers A<sub>1</sub> and A<sub>2</sub> are chopped to remove the offset, offset drift, and the 1/f noise. Chopping moves the effects to  $f_{CLK}/128$  (8 kHz), which is safely out of the passband. Chopping can be disabled by setting the CHOP register bit = 0. With chopping disabled, the impedance of the PGA increases substantially (>> 1 G $\Omega$ ). As shown in Figure 30, chopping maintains flat noise density; if chopping is disabled, however, it results in a rising 1/f noise profile.

The PGA has programmable gains from 1 to 64. Table 3 shows the register bit setting for the PGA and resulting full-scale differential range.

The specified output operating range of the PGA is shown in Equation 4: AVSS + 0.4 V < (CAPN or CAPP) < AVDD - 0.4 V

(4)

PGA output levels (signal plus common-mode) should be maintained within these limits for best operation.

| PGA[2:0] | GAIN | DIFFERENTIAL INPUT RANGE (V) <sup>(1)</sup> |  |  |  |  |  |  |  |

|----------|------|---------------------------------------------|--|--|--|--|--|--|--|

| 000      | 1    | ±2.5                                        |  |  |  |  |  |  |  |

| 001      | 2    | ±1.25                                       |  |  |  |  |  |  |  |

| 010      | 4    | ±0.625                                      |  |  |  |  |  |  |  |

| 011      | 8    | ±0.312                                      |  |  |  |  |  |  |  |

| 100      | 16   | ±0.156                                      |  |  |  |  |  |  |  |

| 101      | 32   | ±0.078                                      |  |  |  |  |  |  |  |

| 110      | 64   | ±0.039                                      |  |  |  |  |  |  |  |

#### **Table 3. PGA Gain Settings**

(1)  $V_{REF} = VREFP - VREFN = 5 V$

Figure 29. PGA Block Diagram

Figure 30. PGA Noise

#### 8.3.7 ADC

The ADC block of the ADS1282-SP is composed of two sections: a high-accuracy modulator and a programmable digital filter.

#### 8.3.8 Modulator

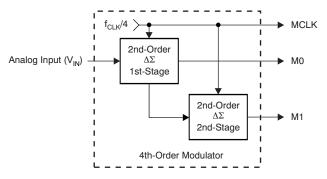

The high-performance modulator is an inherently-stable, fourth-order,  $\Delta\Sigma$ , 2 + 2 pipelined structure, as Figure 31 shows. It shifts the quantization noise to a higher frequency (out of the passband) where digital filtering can easily remove it. The modulator can be filtered either by the on-chip digital filter or by use of post-processing filters.

Figure 31. Fourth-Order Modulator

The modulator first stage converts the analog input voltage into a pulse-code modulated (PCM) stream. When the level of differential analog input (AINP – AINN) is near one-half the level of the reference voltage  $1/2 \times (VREFP - VREFN)$ , the '1' density of the PCM data stream is at its highest. When the level of the differential analog input is near zero, the PCM '0' and '1' densities are nearly equal. At the two extremes of the analog input levels (+FS and –FS), the '1' density of the PCM streams is approximately 90% and 10%, respectively.

The modulator second stage produces a '1' density data stream designed to cancel the quantization noise of the first stage. The data streams of the two stages are then combined before the digital filter stage, as shown in Equation 5.

$$Y[n] = 3M0[n-2] - 6M0[n-3] + 4M0[n-4] + 9(M1[n] - 2M1[n-1] + M1[n-2])$$

(5)

M0[n] represents the most recent first-stage output while M0[n - 1] is the previous first-stage output. When the modulator output is enabled, the digital filter shuts down to save power.

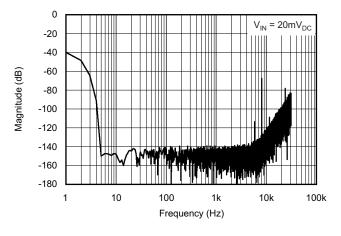

The modulator is optimized for input signals within a 4-kHz passband. As Figure 32 shows, the noise shaping of the modulator results in a sharp increase in noise greater than 6 kHz. The modulator has a chopped input structure that further reduces noise within the passband. The noise moves out of the passband and appears at the chopping frequency ( $f_{CLK}$  / 512 = 8 kHz). The component at 5.8 kHz is the tone frequency, shifted out of band by an external 20 mV/PGA offset. The frequency of the tone is proportional to the applied DC input and is given by PGA × V<sub>IN</sub>/0.003 (in kHz).

1-Hz resolution

Figure 32. Modulator Output Spectrum

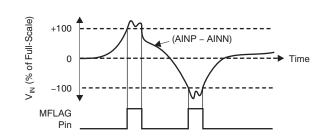

#### 8.3.9 Modulator Over-Range

The ADS1282-SP modulator is inherently stable, and therefore, has predictable recovery behavior resulting from an input overdrive condition. The modulator does not exhibit self-resetting behavior, which often results in an unstable output data stream.

The ADS1282-SP modulator outputs a 1s density data stream at 90% duty cycle with the positive full-scale input signal applied (10% duty cycle with the negative full-scale signal). If the input is overdriven past 90% modulation, but less than 100% modulation (10% and 0% for negative overdrive, respectively), the modulator remains stable and continues to output the 1s density data stream. The digital filter may or may not clip the output codes to +FS or -FS, depending on the duration of the overdrive. When the input returns to the normal range from a long duration overdrive (worst case), the modulator returns immediately to the normal range, but the group delay of the digital filter delays the return of the conversion result to within the linear range (31 readings for linear phase FIR). 31 additional readings (62 total) are required for completely settled data.

If the inputs are sufficiently overdriven to drive the modulator to full duty cycle, all 1s or all 0s, the modulator enters a stable saturated state. The digital output code may clip to +FS or -FS, again depending on the duration. A small duration overdrive may not always clip the output code. When the input returns to the normal range, the modulator requires up to 12 modulator clock cycles ( $f_{MOD}$ ) to exit saturation and return to the linear region. The digital filter requires an additional 62 conversions for fully settled data (linear phase FIR).

In the extreme case of over-range, either input is overdriven, exceeding the voltage of either analog supply voltage plus an internal ESD diode drop. The internal diodes begin to conduct and the signal on the input is clipped. When the input overdrive is removed, the diodes recover quickly. Keep in mind that the input current must be limited to 100-mA peak or 10-mA continuous if an overvoltage condition is possible.

#### ADS1282-SP

JAJSGE8B-MARCH 2016-REVISED OCTOBER 2018

#### 8.3.10 Modulator Input Impedance

The modulator samples the buffered input voltage with an internal capacitor to perform conversions. The charging of the input sampling capacitor draws a transient current from the PGA output. The average value of the current can be used to calculate an effective input impedance of:

$R_{EFF} = 1 / (f_{MOD} \times C_S)$

where

- $f_{MOD}$  = Modulator sample frequency, Mode = CLK / 4

- $C_{\rm S}$  = Input sampling capacitor (17 pF, typ)

AINP O

AINN C

The resulting modulator input impedance for CLK = 4.096 MHz is 55 k $\Omega$ . The modulator input impedance and the PGA output resistors result in a systematic gain error of -1%. C<sub>S</sub> can vary ±20% over production lots, affecting the gain error.

#### 8.3.11 Modulator Over-Range Detection (MFLAG)

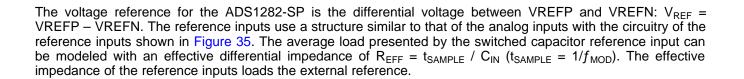

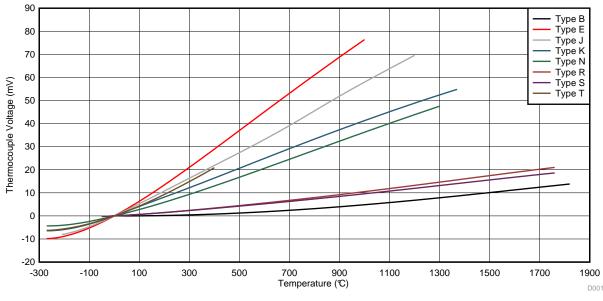

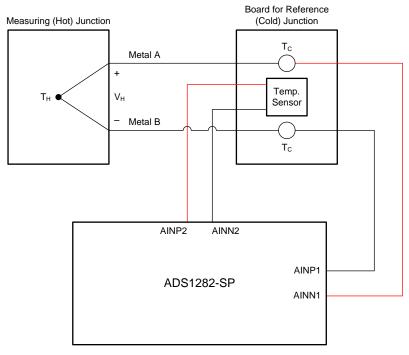

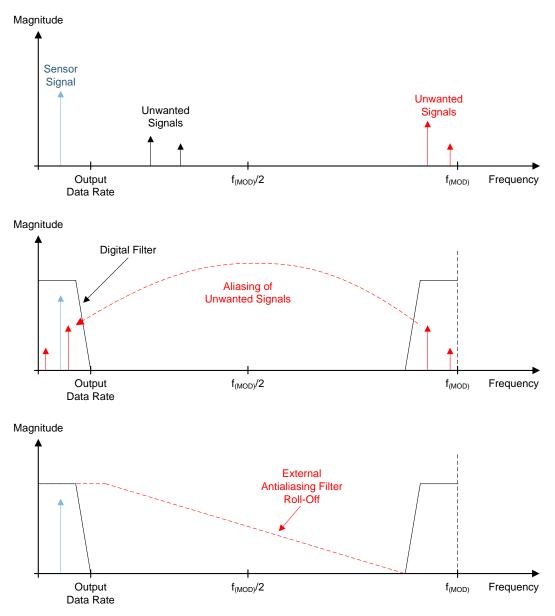

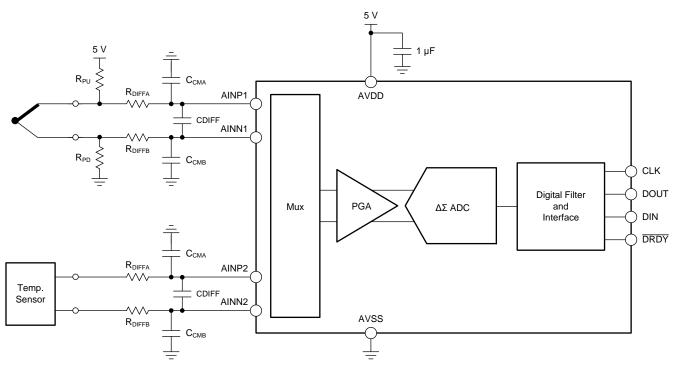

8.3.12 Voltage Reference Inputs (VREFP, VREFN)