Now

#### LMH5401

JAJSEU5D-OCTOBER 2014-REVISED FEBRUARY 2018

# LMH5401 8GHz、低ノイズ、低消費電力の完全差動アンプ

#### 特長 1

ゲイン帯域幅積(GBP): 8GHz

INSTRUMENTS

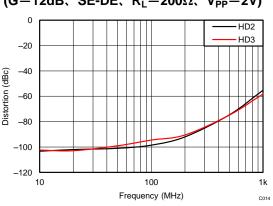

優れた直線性: DC~2GHz、G=12dB

Texas

- スルーレート: 17,500V/us

- HD2/HD3歪みが小さい

- $(1V_{PP}, 200\Omega, DE-DE, G=12dB)$ :

- 100MHz: HD2で-104dBc、HD3で-96dBc

- 200MHz: HD2で-95dBc、HD3で-92dBc

- 500MHz: HD2で-80dBc、HD3で-77dBc

- 1GHz: HD2で-64dBc、HD3で-58dBc

- IMD2/IMD3歪みが小さい

- $(2V_{PP}, 200\Omega, DE-DE, G=12dB)$ :

- 200MHz: IMD2で-96dBc、IMD3で-95dBc

- 500MHz: IMD2で-80dBc、IMD3で-83dBc

- 1GHz: IMD2で-70dBc、IMD3で-63dBc

- 入力電圧ノイズ: 1.25nV/√Hz

- 入力電流ノイズ: 3.5pA/√Hz

- シングルとデュアルの電源による動作をサポート

- 消費電力: 55mA

- パワーダウン機能

#### アプリケーション 2

- GSPS ADCドライバ

- 高速データ収集用ADCドライバ

- 1GBPS Ethernet over Microwave用ADCドライバ

- DACバッファ

- IF、RF、ベースバンド・ゲイン・ブロック

- SAWフィルタ・バッファおよびドライバ

- DCから2GHzまでのバランの代替

- レベル・シフタ

#### 歪みと周波数との関係 (G=12dB, SE-DE, $R_L$ =200 $\Omega$ , $V_{PP}$ =2V)

## 3 概要

LMH5401は、無線周波数(RF)や中間周波数(IF)のアプリ ケーション、または高速なDC結合の時間領域アプリケー ションに対して最適化された、極めて高性能な差動アンプ です。アナログ/デジタル・コンバータ(ADC)の駆動時に、 シングルエンドから差動への(SE-DE)変換を要するDC またはAC結合アプリケーションに最適であり、SE-DEまた は差動-差動(DE-DE)モードでの動作時に生じる2次/3 次歪みを非常に小さく抑えることができます。

LMH5401は、SE-DEシステムとDE-DEシステムのいずれ にも最適化されており、DC~2GHzというかつてない使用 可能帯域幅を実現しています。LMH5401を使用すれば、 試験/測定機器やブロードバンド通信、高速データ収集な どの幅広いアプリケーションにおいて、外部バランなしで 信号チェーンのSE-DE変換が可能になります。

同相基準入力ピンを使用して、アンプの出力同相をADC の入力要件に合わせることができるほか、3.3V~5Vの電 源を選択可能で、必要であればデュアル電源での動作に も対応します。またパワーダウン機能を利用して、消費電 力を削減することも可能です。

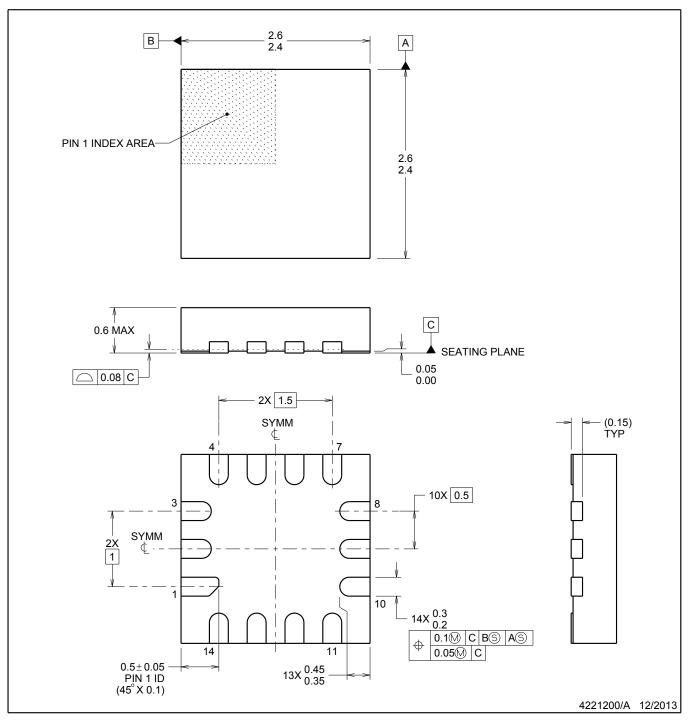

5V電源を使用した場合には、275mWという非常に低い消 費電力で優れた性能を提供します。高性能を実現する LMH5401は、テキサス・インスツルメンツの先進的な相補 型BiCMOSプロセスで製造され、省スペース型のUQFN-14パッケージで供給されます。

#### **製品情報**<sup>(1)</sup>

| 型番      | パッケージ     | 本体サイズ         |  |  |  |

|---------|-----------|---------------|--|--|--|

| LMH5401 | UQFN (14) | 2.50mm×2.50mm |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

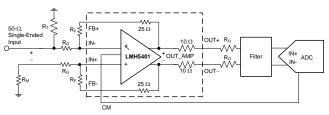

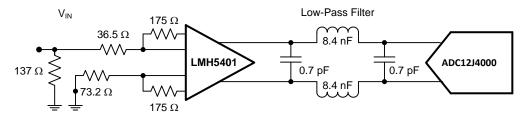

#### ADC12J4000を駆動するLMH5401

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内 容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。 English Data Sheet: SBOS710 JAJSEU5D-OCTOBER 2014-REVISED FEBRUARY 2018

## 目次

| 1 | 特長   |                                                     |

|---|------|-----------------------------------------------------|

| 2 | アプ   | リケーション 1                                            |

| 3 | 概要   |                                                     |

| 4 | 改訂   | 履歴2                                                 |

| 5 | Pin  | Configuration and Functions 4                       |

| 6 |      | cifications5                                        |

|   | 6.1  | Absolute Maximum Ratings 5                          |

|   | 6.2  | ESD Ratings                                         |

|   | 6.3  | Recommended Operating Conditions 5                  |

|   | 6.4  | Thermal Information                                 |

|   | 6.5  | Electrical Characteristics: $V_S = 5 V$             |

|   | 6.6  | Electrical Characteristics: V <sub>S</sub> = 3.3 V8 |

|   | 6.7  | Typical Characteristics: 5 V 10                     |

|   | 6.8  | Typical Characteristics: 3.3 V 15                   |

|   | 6.9  | Typical Characteristics: 3.3-V to 5-V Supply        |

| - | Dava | Range                                               |

| 7 |      | meter Measurement Information 20                    |

|   | 7.1  | Output Reference Points                             |

|   | 7.2  | ATE Testing and DC Measurements 20                  |

|   | 7.3  | Frequency Response                                  |

|   | 7.4  | S-Parameters 21                                     |

|   | 7.5  | Frequency Response with Capacitive Load             |

|   | 7.6  | Distortion 21                                       |

|   | 7.7  | Noise Figure                                        |

|   | 7.8  | Pulse Response, Slew Rate, and Overdrive Recovery   |

|   | 7.9  | Power Down                                          |

|   | 7.10 | V <sub>CM</sub> Frequency Response 22               |

|    | 7.11 | Test Schematics             | 22 |

|----|------|-----------------------------|----|

| 8  | Deta | iled Description            | 24 |

|    | 8.1  | Overview                    | 24 |

|    | 8.2  | Functional Block Diagram    | 24 |

|    | 8.3  | Feature Description         | 25 |

|    | 8.4  | Device Functional Modes     | 31 |

| 9  | App  | lication and Implementation | 32 |

|    | 9.1  | Application Information     | 32 |

|    | 9.2  | Typical Application         | 35 |

|    | 9.3  | Do's and Don'ts             | 43 |

| 10 | Pow  | ver Supply Recommendations  | 44 |

|    | 10.1 | Supply Voltage              | 44 |

|    | 10.2 | Single-Supply               | 44 |

|    | 10.3 | Split-Supply                | 44 |

|    | 10.4 | Supply Decoupling           | 44 |

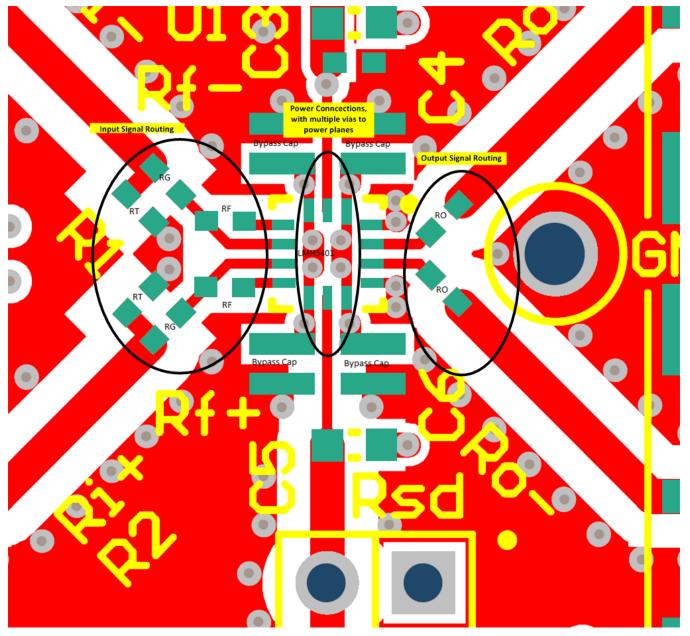

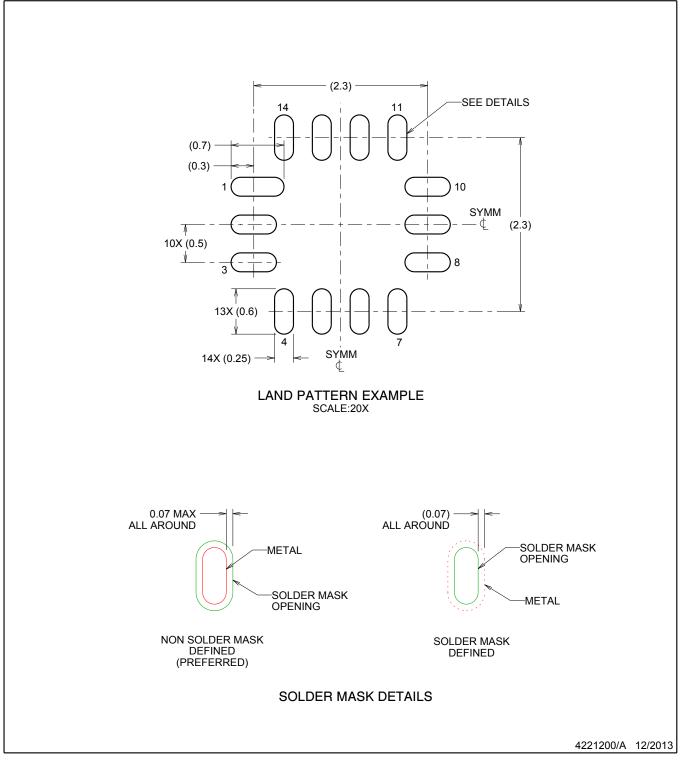

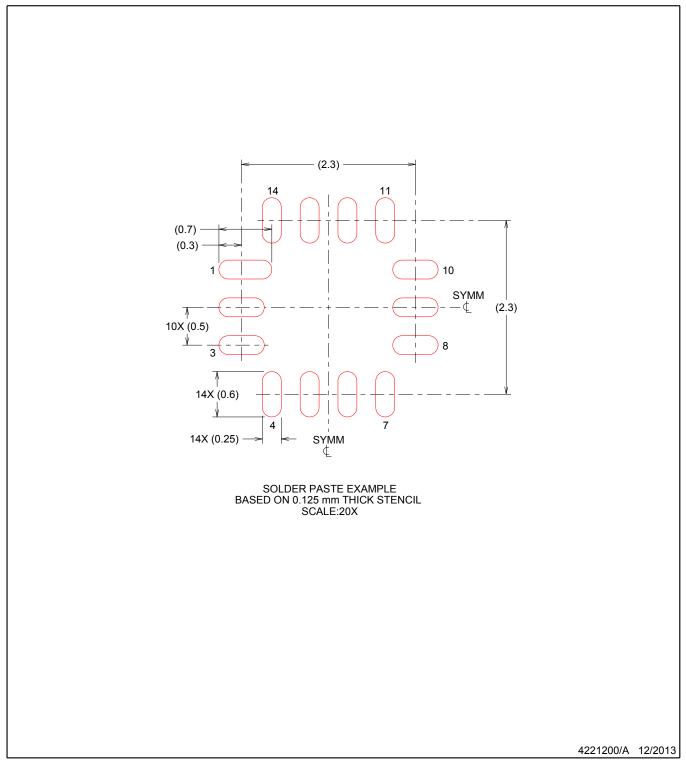

| 11 | Lay  | out                         | 45 |

|    | 11.1 | Layout Guidelines           | 45 |

|    | 11.2 | Layout Example              | 46 |

| 12 | デバ   | イスおよびドキュメントのサポート            | 48 |

|    | 12.1 | デバイス・サポート                   | 48 |

|    | 12.2 | ドキュメントのサポート                 | 48 |

|    | 12.3 | ドキュメントの更新通知を受け取る方法          | 48 |

|    | 12.4 | コミュニティ・リソース                 | 48 |

|    | 12.5 | 商標                          | 49 |

|    | 12.6 | 静電気放電に関する注意事項               | 49 |

|    | 12.7 | Glossary                    | 49 |

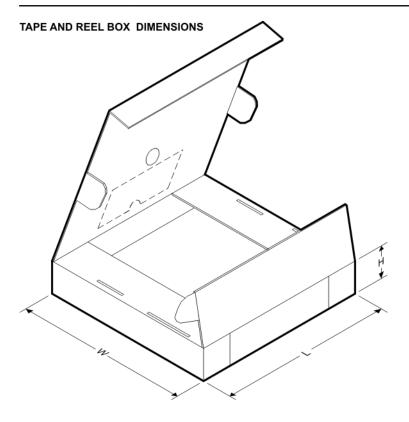

| 13 | メカニ  | ニカル、パッケージ、および注文情報           | 49 |

|    |      |                             |    |

## 4 改訂履歴

2

| • | Added table note to Pin Functions table to distinguish pin types                                                                                              | 4    |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed GND and PD pin descriptions in Pin Functions table                                                                                                    | 4    |

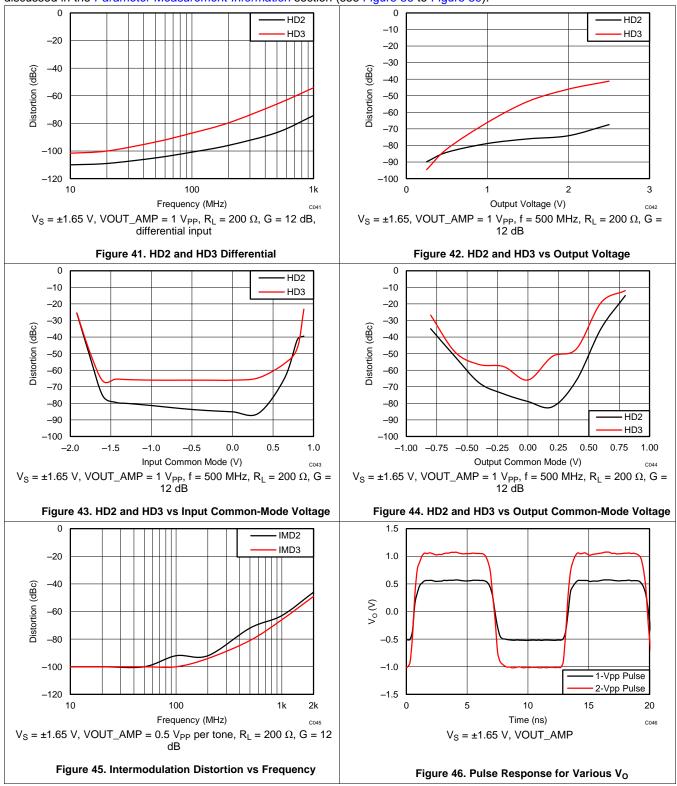

| • | Changed VOUT_AMP value from 2 V <sub>PP</sub> to 1 V <sub>PP</sub> in condition statement of HD2 and HD3 curve                                                | . 15 |

| • | Changed VOUT_AMP value from 2 V <sub>PP</sub> to 1 V <sub>PP</sub> in condition statement of HD2 and HD3 Differential curve                                   | . 16 |

| • | Changed VOUT_AMP value from 2 V <sub>PP</sub> to 1 V <sub>PP</sub> in condition statement of HD2 and HD3 vs Output Voltage curve                              | . 16 |

| • | Changed VOUT_AMP value from 2 V <sub>PP</sub> to 1 V <sub>PP</sub> in condition statement of <i>HD2 and HD3 vs Input Common-Mode Voltage</i> curve            | 16   |

| • | Changed VOUT_AMP value from 2 V <sub>PP</sub> to 1 V <sub>PP</sub> in condition statement of <i>HD2 and HD3 vs Output Common-Mode</i><br><i>Voltage</i> curve | . 16 |

| • | Corrected and deleted note from Functional Block Diagram                                                                                                      |      |

| • | Added Power Down and Ground Pins subsection to Feature Description section                                                                                    | 25   |

## Revision B (January 2015) から Revision C に変更

Revision C (October 2017) から Revision D に変更

| • | Added Input, V <sub>IO</sub> , I <sub>IB</sub> , and I <sub>IO</sub> parameters to 5-V Electrical Characteristics table | 6  |

|---|-------------------------------------------------------------------------------------------------------------------------|----|

| • | Changed $R_T$ and $R_{G2}$ values in first row of Table 2                                                               | 21 |

| • | Changed Functional Block Diagram graphic                                                                                | 24 |

| • | Changed Device Comparison Table to be a separate sub-section within Feature Description section                         | 30 |

| • | Added Driving Unmatched Loads For Lower Loss section                                                                    | 36 |

|   |                                                                                                                         |    |

# STRUMENTS

**EXAS**

www.tij.co.jp

Page

Page

JAJSEU5D-OCTOBER 2014-REVISED FEBRUARY 2018

####

#### Revision A (October 2014) から Revision B に変更

| • | 「概要」セクションの第1文にDC結合を追加                                                                                                                                         |      |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | 「概要」セクションの第2段落第2文を変更                                                                                                                                          | 1    |

| • | Updated ESD Ratings table to current standards                                                                                                                | 5    |

| • | Changed AC Performance, IMD3 and IMD2 parameter test conditions in 5-V Electrical Characteristics table                                                       | 6    |

| • | Changed Input, V <sub>ICL</sub> parameter maximum specification in 5-V Electrical Characteristics table                                                       | 6    |

| • | Changed Input, V <sub>ICL</sub> parameter maximum specification in 3.3-V Electrical Characteristics table                                                     | 8    |

| • | Changed Output, $V_{OCRH}$ parameter test condition from <i>Output voltage range low</i> to $T_A = -40$ °C to 85 °C in 3.3-V Electrical Characteristics table | 9    |

| • | Changed Typical Characteristics curves: updated color scheme, grammatical edits throughout curves                                                             | 10   |

| • | Added Large-Signal to title of Figure 2, Figure 4, and Figure 6                                                                                               | 10   |

| • | Added Large-Signal to title of Figure 8                                                                                                                       | . 10 |

| • | Changed Differential-Ended to Differential in title of Figure 11                                                                                              | 10   |

| • | Added Large-Signal to titles of Figure 30, Figure 32, and Figure 34                                                                                           | 15   |

| • | Added Large-Signal to title of Figure 36                                                                                                                      | 15   |

| • | Changed correction to reduction in second paragraph of Output Reference Points section                                                                        | 20   |

| • | Changed header for last column in Table 1                                                                                                                     | 21   |

| • | ChangedFigure 56 through Figure 59: modifications to figures, added $A_V = 4 V/V$ to titles                                                                   | 22   |

| • | Deleted last sentence from first paragraph of the Fully-Differential Amplifier section                                                                        | 25   |

| • | Changed 1.2 V to the specified minimum voltage in the third paragraph of the Fully-Differential Amplifier section                                             | 25   |

| • | Added sixth sentence stating the feedback path must always be DC-coupled to the AC-Coupled Signal Path<br>Considerations section                              | 25   |

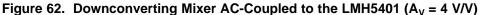

| • | Added $A_V = 4$ V/V to title of Figure 62                                                                                                                     | -    |

|   |                                                                                                                                                               |      |

| • | Deleted example from the Operation with a Single Supply section                                                                                               |      |

| • | Added Stability section                                                                                                                                       | 32   |

| • | Changed 15 dB to 19 dB in third paragraph of SFDR Considerations section                                                                                      | 38   |

| • | Added Figure 75 to the Active Balun section                                                                                                                   | 42   |

#### 2014年10月発行のものから更新

#### Page

Page

| • | Changed Output Common-Mode Control Pin, V <sub>CM</sub> voltage range low and high parameter typical specifications in 5-V Electrical Characteristics | . 7 |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Changed Output Common-Mode Control Pin, V <sub>CM</sub> voltage range low and high parameter specifications in 3.3-V Electrical Characteristics table | . 9 |

LMH5401 JAJSEU5D-OCTOBER 2014-REVISED FEBRUARY 2018 TEXAS INSTRUMENTS

www.ti.com

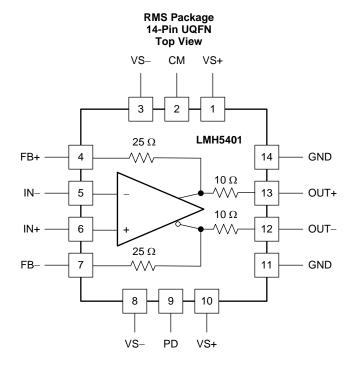

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN  |        | TYPE | DESCRIPTION                                                       |  |

|------|--------|------|-------------------------------------------------------------------|--|

| NAME | NO.    | TYPE | DESCRIPTION                                                       |  |

| СМ   | 2      | I    | Input pin to set amplifier output common-mode voltage             |  |

| FB–  | 7      | 0    | Negative output feedback component connection                     |  |

| FB+  | 4      | 0    | Positive output feedback component connection                     |  |

| GND  | 11, 14 | Р    | Power down ground. See Power Down and Ground Pins                 |  |

| IN-  | 5      | I    | legative input pin                                                |  |

| IN+  | 6      | I    | Positive input pin                                                |  |

| OUT- | 12     | 0    | Negative output pin                                               |  |

| OUT+ | 13     | 0    | Positive output pin                                               |  |

| PD   | 9      | I    | Power-down (logic 1 = power down). See Power Down and Ground Pins |  |

| VS-  | 3, 8   | Р    | Negative supply voltage                                           |  |

| VS+  | 1, 10  | Р    | Positive supply voltage                                           |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                           | MIN         | MAX             | UNIT             |

|---------------------------------------------------------------------------|-------------|-----------------|------------------|

| Power supply                                                              |             | 5.5             | V                |

| Input voltage range                                                       | (VS–) – 0.7 | (VS+) + 0.7     | V                |

| Input current                                                             |             | 10              | mA               |

| Output current (sourcing or sinking) OUT+, OUT-                           |             | 100             | mA               |

| Continuous power dissipation                                              | See T       | hermal Informat | <i>ion</i> table |

| Maximum junction temperature, T <sub>J</sub>                              |             | 150             | °C               |

| Maximum junction temperature, continuous operation, long-term reliability |             | 125             | °C               |

| Operating free-air temperature, T <sub>A</sub>                            | -40         | 85              | °C               |

| Storage temperature, T <sub>stg</sub>                                     | -40         | 150             | °C               |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±3500 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                          | MIN  | NOM | MAX  | UNIT |

|------------------------------------------|------|-----|------|------|

| Supply voltage ( $V_S = VS+ - VS-$ )     | 3.15 | 5   | 5.25 | V    |

| Operating junction temperature, $T_J$    | -40  |     | 125  | °C   |

| Ambient operating air temperature, $T_A$ | -40  | 25  | 85   | °C   |

#### 6.4 Thermal Information

|                       |                                              | LMH5401    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RMS (UQFN) | UNIT |

|                       |                                              | 14 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 101        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 51         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 61         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 4.2        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 61         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

JAJSEU5D-OCTOBER 2014-REVISED FEBRUARY 2018

LMH5401

#### XAS TRUMENTS

www.ti.com

## 6.5 Electrical Characteristics: V<sub>s</sub> = 5 V

at  $T_A = 25^{\circ}$ C, VS+ = 2.5 V, VS- = -2.5 V, V<sub>CM</sub> = 0 V, R<sub>L</sub> = 200- $\Omega$  differential, G = 12 dB (4 V/V), single-ended input, differential output, and R<sub>S</sub> = 50  $\Omega$ , (unless otherwise noted)<sup>(1)</sup>

|                  | PARAMETER                         | TEST CONDITIONS                                                       | MIN          | ТҮР         | МАХ          | UNIT   | TEST<br>LEVEL <sup>(2)</sup> |

|------------------|-----------------------------------|-----------------------------------------------------------------------|--------------|-------------|--------------|--------|------------------------------|

| AC PER           | FORMANCE                          |                                                                       |              |             |              |        |                              |

| GBP              | Gain bandwidth product            | G = 30 dB (32 V/V)                                                    |              | 8           |              | GHz    | С                            |

| SSBW             | Small-signal, -3-dB bandwidth     | $V_{O} = 200 \text{ mV}_{PP}$                                         |              | 6.2         |              | GHz    | С                            |

| LSBW             | Large-signal, –3-dB bandwidth     | V <sub>O</sub> = 2 V <sub>PP</sub>                                    |              | 4.8         |              | GHz    | С                            |

|                  | Bandwidth for 0.1-dB flatness     | $V_{O} = 2 V_{PP}$                                                    |              | 800         |              | MHz    | С                            |

| SR               | Slew rate                         | 2-V step                                                              |              | 17500       |              | V/µs   | С                            |

|                  | Rise and fall time                | 1-V step, 10% to 90%                                                  |              | 80          |              | ps     | С                            |

|                  | Overdrive recovery                | Overdrive = $\pm 0.5$ V                                               |              | 300         |              | ps     | С                            |

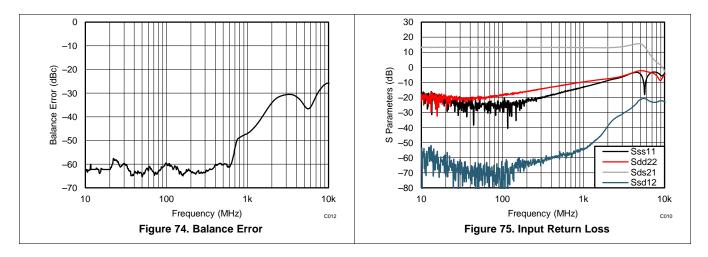

|                  | Output balance error              | f = 1 GHz                                                             |              | 47          |              | dBc    | С                            |

| z <sub>o</sub>   | Output impedance                  | At DC, differential                                                   | 16           | 20          | 24           | Ω      | А                            |

|                  | 0.1% settling time                | 2 V, R <sub>L</sub> = 200 Ω                                           |              | 1           |              | ns     | С                            |

|                  |                                   | $f = 100 \text{ MHz}, V_O = 2 V_{PP}$                                 |              | -99         |              | dBc    | С                            |

|                  | Second-order harmonic             | f = 200 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                       |              | -92         |              | dBc    | С                            |

| HD2              | distortion                        | $f = 500 \text{ MHz}, V_0 = 2 V_{PP}$                                 |              | -75         |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_0 = 2 V_{PP}$                                   |              | -56         |              | dBc    | С                            |

|                  |                                   | $f = 100 \text{ MHz}, V_0 = 2 V_{PP}$                                 |              | -94         |              | dBc    | С                            |

| HD3              |                                   | f = 200 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                       |              | -90         |              | dBc    | С                            |

|                  | Third-order harmonic distortion   | $f = 500 \text{ MHz}, \text{ V}_{\text{O}} = 2 \text{ V}_{\text{PP}}$ |              | -75         |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_O = 2 V_{PP}$                                   |              | -58         |              | dBc    | С                            |

|                  |                                   | f = 100 MHz, $V_0$ = 1 $V_{PP}$ per tone                              |              | -95         |              | dBc    | С                            |

| IMD3             | Third-order intermodulation       | f = 200 MHz, $V_0$ = 1 $V_{PP}$ per tone                              |              | -91         |              | dBc    | С                            |

|                  |                                   | f = 500 MHz, $V_0$ = 1 $V_{PP}$ per tone                              |              | -75         |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_0 = 1 V_{PP} \text{ per tone}$                  |              | -60         |              | dBc    | С                            |

|                  |                                   | f = 100 MHz, $V_0$ = 1 $V_{PP}$ per tone                              |              | -95         |              | dBc    | С                            |

| IMD2             | Second-order intermodulation      | f = 200 MHz, $V_0$ = 1 $V_{PP}$ per tone                              |              | -89         |              | dBc    | С                            |

| IIVIDZ           |                                   | f = 500 MHz, $V_0$ = 1 $V_{PP}$ per tone                              |              | -71         |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_O = 1 V_{PP} \text{ per tone}$                  |              | -52         |              | dBc    | С                            |

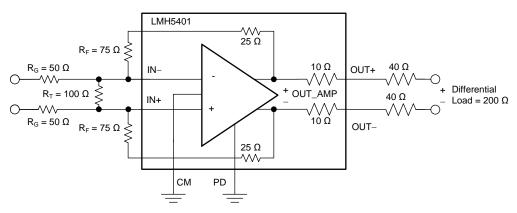

| NOISE F          | PERFORMANCE                       |                                                                       |              |             |              |        |                              |

| e <sub>n</sub>   | Input voltage noise density       |                                                                       |              | 1.25        |              | nV/√Hz | С                            |

| i <sub>n</sub>   | Input noise current               |                                                                       |              | 3.5         |              | pA/√Hz | С                            |

| NF               | Noise figure                      | $R_S = 50 \Omega$ , SE-DE, 200 MHz<br>(see Figure 59)                 |              | 9.6         |              | dB     | С                            |

| INPUT            |                                   |                                                                       |              |             |              |        |                              |

| V <sub>os</sub>  | Input offset voltage              |                                                                       |              | ±0.5        | ±5           | mV     | А                            |

| I <sub>B</sub>   | Input bias current                |                                                                       |              | 70          | 150          | μA     | А                            |

| l <sub>os</sub>  | Input offset current              |                                                                       |              | ±1          | ±10          | μA     | А                            |

|                  | Differential resistance           | Open-loop                                                             |              | 4600        |              | Ω      | С                            |

| V <sub>ICL</sub> | Input common-mode<br>low voltage  |                                                                       |              | VS-         | (VS–) + 0.41 | V      | А                            |

| V <sub>ICH</sub> | Input common-mode<br>high voltage |                                                                       | (VS+) - 1.41 | (VS+) – 1.2 |              | V      | А                            |

| CMRR             | Common-mode rejection ratio       | Differential, 1-V <sub>PP</sub> input shift, DC                       |              | 72          |              | dBc    | С                            |

(1)

The input resistance and corresponding gain are obtained with the external resistance added. Test levels: (A) 100% tested at 25°C. Overtemperature limits by characterization and simulation. (B) Limits set by characterization and (2) simulation. (C) Typical value only for information.

## Electrical Characteristics: V<sub>s</sub> = 5 V (continued)

at T<sub>A</sub> = 25°C, VS+ = 2.5 V, VS- = -2.5 V, V<sub>CM</sub> = 0 V, R<sub>L</sub> = 200- $\Omega$  differential, G = 12 dB (4 V/V), single-ended input, differential output, and R<sub>S</sub> = 50  $\Omega$ , (unless otherwise noted)<sup>(1)</sup>

| PARAMETER         |                                                                 | TEST C                               | CONDITIONS                         | MIN         | ТҮР         | МАХ       | UNIT            | TEST<br>LEVEL <sup>(2)</sup> |

|-------------------|-----------------------------------------------------------------|--------------------------------------|------------------------------------|-------------|-------------|-----------|-----------------|------------------------------|

| OUTPUT            | Г                                                               |                                      |                                    | ·           |             |           |                 |                              |

|                   |                                                                 | Measured                             | T <sub>A</sub> = 25°C              | (VS+) – 1.3 | (VS+) – 1.1 |           | V               | А                            |

| V <sub>OCRH</sub> | Output voltage range, high                                      | single-ended                         | T <sub>A</sub> = −40°C to<br>+85°C |             | (VS+) – 1.2 |           | V               | С                            |

|                   |                                                                 | Measured                             | $T_A = 25^{\circ}C$                | (VS–) + 1.3 | (VS–) + 1.1 |           | V               | А                            |

| V <sub>OCRL</sub> | Output voltage range, low                                       | single-ended                         | T <sub>A</sub> = −40°C to<br>+85°C |             | (VS–) + 1.2 |           | V               | С                            |

| V <sub>OD</sub>   | Differential output voltage swing                               | Differential                         |                                    |             | 5.8         |           | V <sub>PP</sub> | С                            |

| I <sub>OD</sub>   | Differential output current                                     | $V_{O} = 0 V^{(3)}$                  |                                    | 40          | 50          |           | mA              | А                            |

| POWER             | SUPPLY                                                          |                                      |                                    |             |             |           |                 |                              |

| Vs                | Supply voltage                                                  |                                      |                                    | 3.15        |             | 5.25      | V               | А                            |

| <b>DODD</b>       | Power-supply rejection ratio                                    | VS-                                  |                                    | -50         | -80         |           | dB              | А                            |

| PSRR              | Power-supply rejection ratio                                    | VS+                                  |                                    | -60         | -82         |           | dB              | А                            |

| IQ                | Quisseent surrent                                               | Power down = 0                       |                                    | 50          | 55          | 62        | mA              | А                            |

|                   | Quiescent current                                               | Power down = 1                       |                                    | 1           | 3           | 6         | mA              | А                            |

| OUTPUT            | COMMON-MODE CONTROL PIN                                         | (V <sub>CM</sub> )                   |                                    |             |             |           |                 |                              |

| SSBW              | Small-signal bandwidth                                          | $V_{OCM} = 100 \text{ mV}_{PP}$      | 2                                  |             | 1.2         |           | GHz             | С                            |

|                   | V <sub>CM</sub> slew rate                                       | $V_{OCM} = 500 \text{ mV}_{PP}$      | 2                                  |             | 2900        |           | V/µs            | С                            |

|                   | $V_{\text{CM}}$ voltage range low                               | Differential gain s                  | shift < 1 dB                       |             | (VS–) + 1.4 | (VS–) + 2 | V               | А                            |

|                   | $V_{CM}$ voltage range high                                     | Differential gain s                  | shift < 1 dB                       | (VS+) – 2   | (VS+) – 1.4 |           | V               | A                            |

|                   | V <sub>CM</sub> gain                                            | $V_{CM} = 0 V$                       |                                    | 0.98        | 1           | 1.01      | V/V             | А                            |

|                   | $V_{OCM}$ output common-mode offset from $V_{CM}$ input voltage | $V_{CM} = 0 V$                       |                                    |             | -27         |           | mV              | с                            |

| V <sub>OCM</sub>  | Common-mode offset voltage                                      | Output-referred                      |                                    |             | 0.4         |           | mV              | А                            |

| POWER             | DOWN (PD PIN)                                                   |                                      |                                    |             |             |           |                 |                              |

| V <sub>T</sub>    | Enable or disable voltage threshold                             | Device powers of<br>Device powers de |                                    | 0.9         | 1.1         | 1.2       | V               | A                            |

|                   | Power down quiescent current                                    |                                      |                                    | 1           | 3           | 6         | mA              | А                            |

|                   | Power down bias current                                         | Power down = 2.                      | 5 V                                |             | 10          | ±100      | μA              | С                            |

|                   | Turnon time delay                                               | Time to $V_0 = 90\%$                 | 6 of final value                   |             | 10          |           | ns              | С                            |

|                   | Turnoff time delay                                              | Time to V <sub>O</sub> = 10%         | 6 of original value                |             | 10          |           | ns              | С                            |

(3) This test shorts the outputs to ground (midsupply) then sources or sinks 60 mA and measures the deviation from the initial condition.

TEXAS INSTRUMENTS

JAJSEU5D-OCTOBER 2014-REVISED FEBRUARY 2018

www.ti.com

## 6.6 Electrical Characteristics: $V_s = 3.3 V$

at  $T_A = 25^{\circ}$ C, VS+ = 1.65 V, VS- = -1.65 V,  $V_{CM} = 0$  V,  $R_L = 200 \cdot \Omega$  differential, G = 12 dB (4 V/V), single-ended input and differential output, and input and output referenced to midsupply, (unless otherwise noted.) Measured using an EVM as discussed in the *Parameter Measurement Information* section.

|                  | PARAMETER                         | TEST CONDITIONS                                        | MIN          | ТҮР         | МАХ          | UNIT   | TEST<br>LEVEL <sup>(1)</sup> |

|------------------|-----------------------------------|--------------------------------------------------------|--------------|-------------|--------------|--------|------------------------------|

| AC PER           | FORMANCE                          |                                                        |              |             |              |        |                              |

| GBP              | Gain bandwidth product            | G = 30 dB (32 V/V)                                     |              | 8           |              | MHz    | С                            |

| SSBW             | Small-signal, -3-dB bandwidth     | $V_{O} = 200 \text{ mV}_{PP}$                          |              | 6           |              | GHz    | С                            |

| LSBW             | Large-signal, –3-dB bandwidth     | V <sub>O</sub> = 2 V <sub>PP</sub>                     |              | 4.4         |              | GHz    | С                            |

|                  | Bandwidth for 0.1-dB flatness     | V <sub>O</sub> = 2 V <sub>PP</sub>                     |              | 700         |              | MHz    | С                            |

| SR               | Slew rate                         | 2-V step                                               |              | 17500       |              | V/µs   | С                            |

|                  | Rise and fall time                | 1-V step, 10% to 90%                                   |              | 90          |              | ps     | С                            |

|                  | Overdrive recovery                | Overdrive = $\pm 0.5$ V                                |              | 400         |              | ps     | С                            |

|                  | Output balance error              | f = 1 GHz                                              |              | 47          |              | dBc    | С                            |

| zo               | Output impedance                  | At DC                                                  | 16           | 20          | 24           | Ω      | А                            |

|                  | 0.1% settling time                | 2 V, R <sub>L</sub> = 200 Ω                            |              | 1           |              | ns     | С                            |

|                  |                                   | f = 100 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>        |              | -100        |              | dBc    | С                            |

| HD2              | Second-order harmonic             | f = 200 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>        |              | -94         |              | dBc    | С                            |

|                  | distortion                        | f = 500 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>        |              | -78.5       |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_0 = 1 \text{ V}_{PP}$            |              | -58         |              | dBc    | С                            |

| HD3              | Third-order harmonic distortion   | f = 100 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>        |              | -86         |              | dBc    | С                            |

|                  |                                   | f = 200 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>        |              | -78         |              | dBc    | С                            |

|                  |                                   | f = 500 MHz, V <sub>O</sub> = 1 V <sub>PP</sub>        |              | -64         |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_0 = 1 \text{ V}_{PP}$            |              | -52         |              | dBc    | С                            |

|                  |                                   | f = 100 MHz, $V_0$ = 0.5 $V_{PP}$ per tone             |              | -95         |              | dBc    | С                            |

|                  | Second-order intermodulation      | f = 200 MHz, $V_0$ = 0.5 $V_{PP}$ per tone             |              | -95         |              | dBc    | С                            |

| IMD2             | distortion                        | f = 500 MHz, $V_0$ = 0.5 $V_{PP}$ per tone             |              | 81          |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_0 = 0.5 V_{PP} \text{ per tone}$ |              | -66         |              | dBc    | С                            |

|                  |                                   | f = 100 MHz, $V_O = 0.5 V_{PP}$ per tone               |              | -101        |              | dBc    | С                            |

| IMD3             | Third-order intermodulation       | f = 200 MHz, $V_O = 0.5 V_{PP}$ per tone               |              | -95         |              | dBc    | С                            |

| IMD3             | distortion                        | f = 500 MHz, $V_O$ = 0.5 $V_{PP}$ per tone             |              | -82         |              | dBc    | С                            |

|                  |                                   | $f = 1 \text{ GHz}, V_0 = 0.5 V_{PP} \text{ per tone}$ |              | -66         |              | dBc    | С                            |

| NOISE F          | PERFORMANCE                       |                                                        |              |             |              |        |                              |

| en               | Input voltage noise density       |                                                        |              | 1.25        |              | nV/√Hz | С                            |

| i <sub>n</sub>   | Input noise current               |                                                        |              | 3.5         |              | pA/√Hz | С                            |

| NF               | Noise figure                      | $R_S = 50 $ Ω, SE-DE, G = 12 dB, 200 MHz               |              | 9.6         |              | dB     | С                            |

| INPUT            |                                   | · · · · · · · · · · · · · · · · · · ·                  | ·            |             |              |        |                              |

| Z <sub>id</sub>  | Differential impedance            |                                                        |              | 4600        |              | Ω      | С                            |

| V <sub>ICL</sub> | Input common-mode<br>low voltage  |                                                        |              | (VS–)       | (VS–) + 0.41 | V      | A                            |

| VICH             | Input common-mode<br>high voltage |                                                        | (VS+) – 1.41 | (VS+) – 1.2 |              | V      | A                            |

| CMRR             | Common-mode rejection ratio       | Differential, 1-V <sub>PP</sub> input shift, DC        |              | -72         |              | dBc    | С                            |

(1) Test levels: (A) 100% tested at 25°C. Overtemperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

## Electrical Characteristics: V<sub>s</sub> = 3.3 V (continued)

at  $T_A = 25^{\circ}$ C, VS+ = 1.65 V, VS- = -1.65 V,  $V_{CM} = 0$  V,  $R_L = 200 \cdot \Omega$  differential, G = 12 dB (4 V/V), single-ended input and differential output, and input and output referenced to midsupply, (unless otherwise noted.) Measured using an EVM as discussed in the *Parameter Measurement Information* section.

|                   | PARAMETER                                                       | TEST C                               | ONDITIONS                          | MIN          | ТҮР          | МАХ          | UNIT            | TEST<br>LEVEL <sup>(1)</sup> |

|-------------------|-----------------------------------------------------------------|--------------------------------------|------------------------------------|--------------|--------------|--------------|-----------------|------------------------------|

| OUTPUT            | Г                                                               | •                                    |                                    |              |              |              |                 |                              |

|                   |                                                                 | Measured                             | $T_A = 25^{\circ}C$                | (VS+) – 1.3  | (VS+) – 1.1  |              | V               | А                            |

| V <sub>OCRH</sub> | Output voltage range, high                                      | single-ended                         | T <sub>A</sub> = −40°C to<br>+85°C |              | (VS+) – 1.2  |              | V               | С                            |

|                   |                                                                 | Measured                             | T <sub>A</sub> = 25°C              | (VS–) + 1.3  | (VS–) + 1.1  |              | V               | А                            |

| V <sub>OCRL</sub> | Output voltage range, low                                       | single-ended                         | T <sub>A</sub> = −40°C to<br>+85°C |              | (VS–) + 1.2  |              | V               | С                            |

| V <sub>OD</sub>   | Differential output voltage swing                               | Differential                         |                                    |              | 2.8          |              | V <sub>PP</sub> | С                            |

| I <sub>OD</sub>   | Differential output current                                     | $V_0 = 0 V^{(2)}$                    | $V_{O} = 0 V^{(2)}$                |              | 40           |              | mA              | А                            |

| POWER             | SUPPLY                                                          |                                      |                                    |              |              |              |                 |                              |

| Vs                | Supply voltage                                                  |                                      |                                    | 3.15         |              | 5.25         | V               | А                            |

| PSRR              | Dower oursely rejection ratio                                   | VS-                                  |                                    | -50          | -80          |              | dB              | А                            |

| PSKK              | Power-supply rejection ratio                                    | VS+                                  |                                    | -60          | -84          |              | dB              | А                            |

|                   | Quiescent current                                               | Power down = 0                       |                                    | 49           | 54           | 62           | mA              | А                            |

| Ι <sub>Q</sub>    | Quiescent current                                               | Power down = 1                       |                                    | 1            | 1.6          | 5            | mA              | А                            |

| OUTPUT            | COMMON-MODE CONTROL PIN                                         | (V <sub>см</sub> )                   |                                    |              |              |              |                 |                              |

| SSBW              | Small-signal bandwidth                                          | $V_{OCM} = 200 \text{ mV}_{PP}$      |                                    |              | 3            |              | GHz             | С                            |

|                   | $V_{\text{CM}}$ voltage range low                               | Differential gain sl                 | nift < 1 dB                        |              | (VS–) + 1.35 | (VS–) + 1.55 | V               | А                            |

|                   | V <sub>CM</sub> voltage range high                              | Differential gain sl                 | nift < 1 dB                        | (VS+) – 1.55 | (VS+) – 1.35 |              | V               | А                            |

|                   | V <sub>CM</sub> gain                                            | $V_{CM} = 0 V$                       |                                    | 0.98         | 1            | 1.01         | V/V             | А                            |

|                   | $V_{OCM}$ output common-mode offset from $V_{CM}$ input voltage | V <sub>CM</sub> = 0 V                |                                    |              | -27          |              | mV              | С                            |

| V <sub>OCM</sub>  | Common-mode offset voltage                                      | Output-referred                      |                                    |              | 0.4          |              | mV              | А                            |

| POWER             | DOWN (PD PIN)                                                   |                                      |                                    | ·            |              |              |                 |                              |

| V <sub>T</sub>    | Enable or disable voltage threshold                             | Device powers on<br>device powers do |                                    | 0.9          | 1.1          | 1.2          | V               | А                            |

|                   | Power down quiescent current                                    |                                      |                                    | 1            | 3            | 6            | mA              | А                            |

|                   | Power down bias current                                         | Power down = 2.5                     | V                                  |              | 10           | ±100         | μA              | С                            |

|                   | Turnon time delay                                               | Time to $V_0 = 90\%$                 | of final value                     |              | 10           |              | ns              | С                            |

|                   | Turnoff time delay                                              | Time to V <sub>O</sub> = 10%         | of original value                  |              | 10           |              | ns              | С                            |

(2) This test shorts the outputs to ground (midsupply) then sources or sinks 60 mA and measures the deviation from the initial condition.

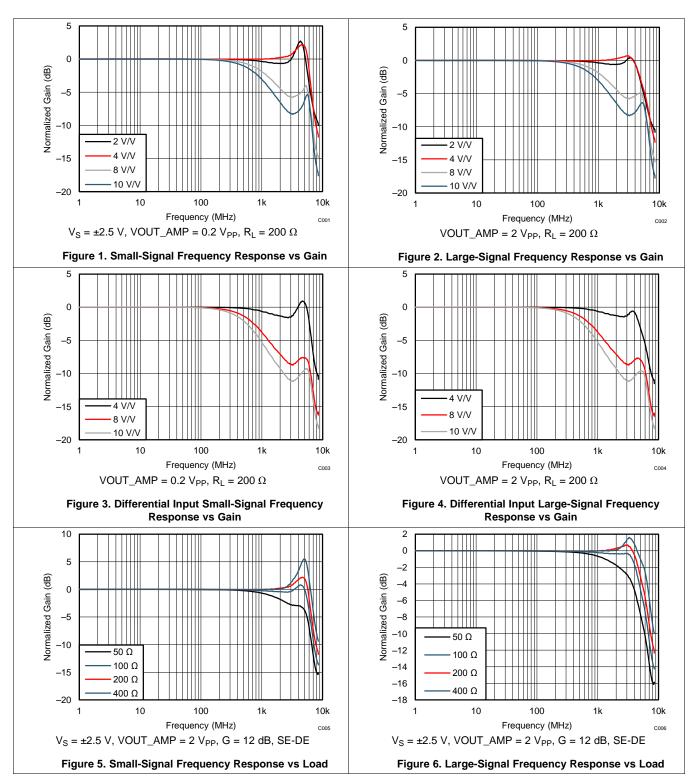

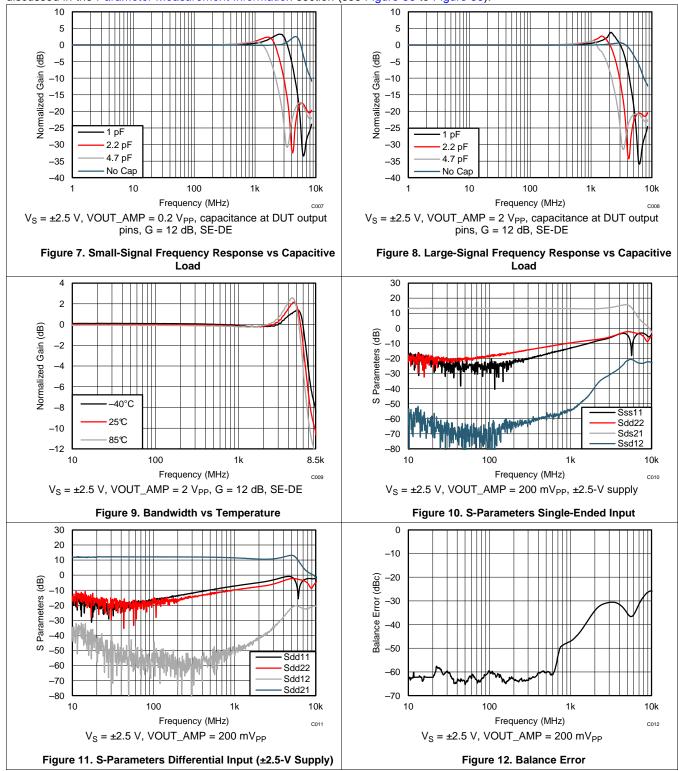

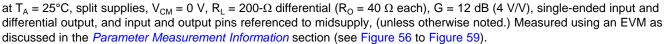

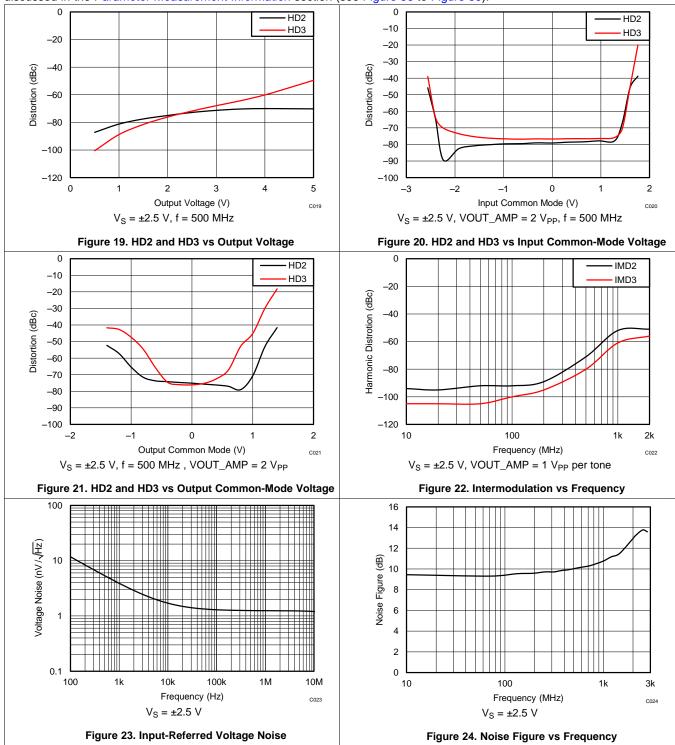

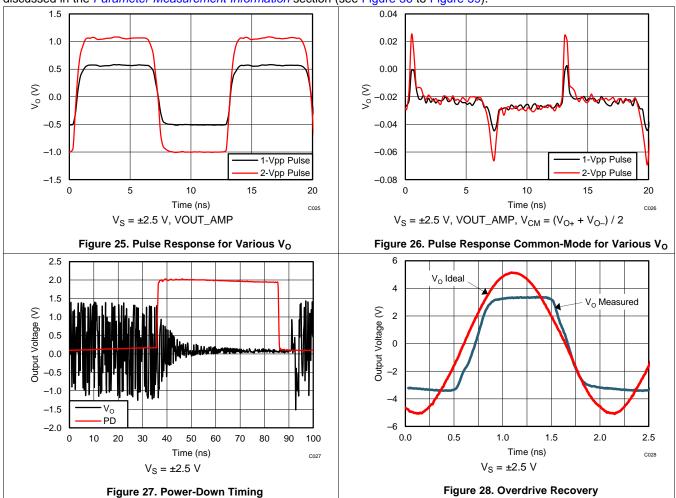

## 6.7 Typical Characteristics: 5 V

#### **Typical Characteristics: 5 V (continued)**

## Typical Characteristics: 5 V (continued)

#### Typical Characteristics: 5 V (continued)

## **Typical Characteristics: 5 V (continued)**

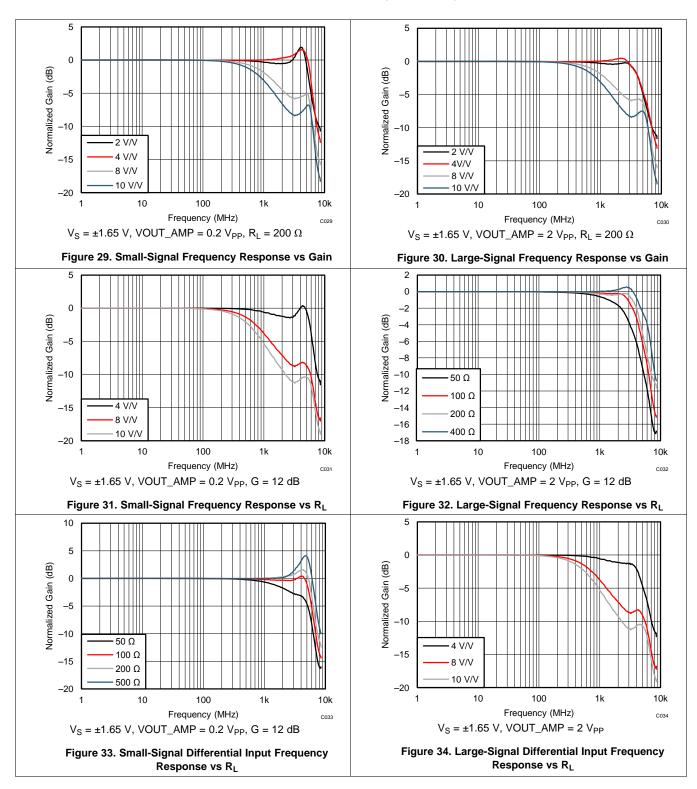

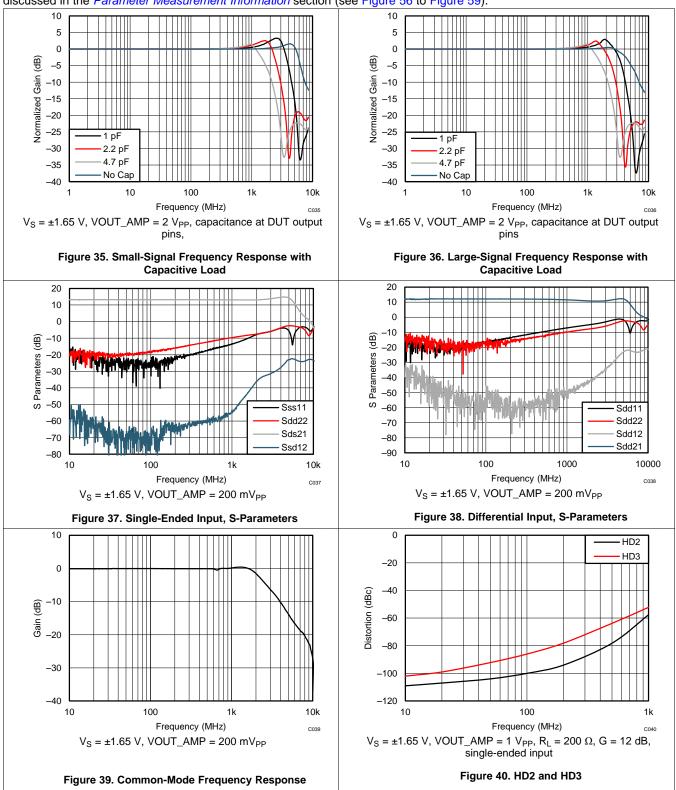

#### 6.8 Typical Characteristics: 3.3 V

## Typical Characteristics: 3.3 V (continued)

#### Typical Characteristics: 3.3 V (continued)

## Typical Characteristics: 3.3 V (continued)

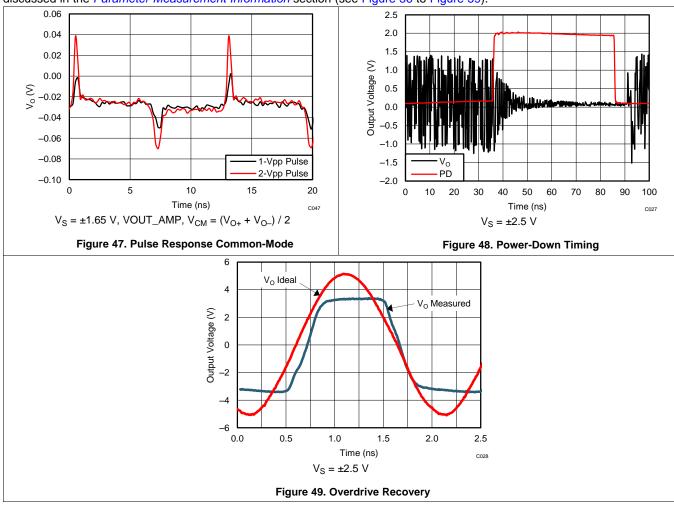

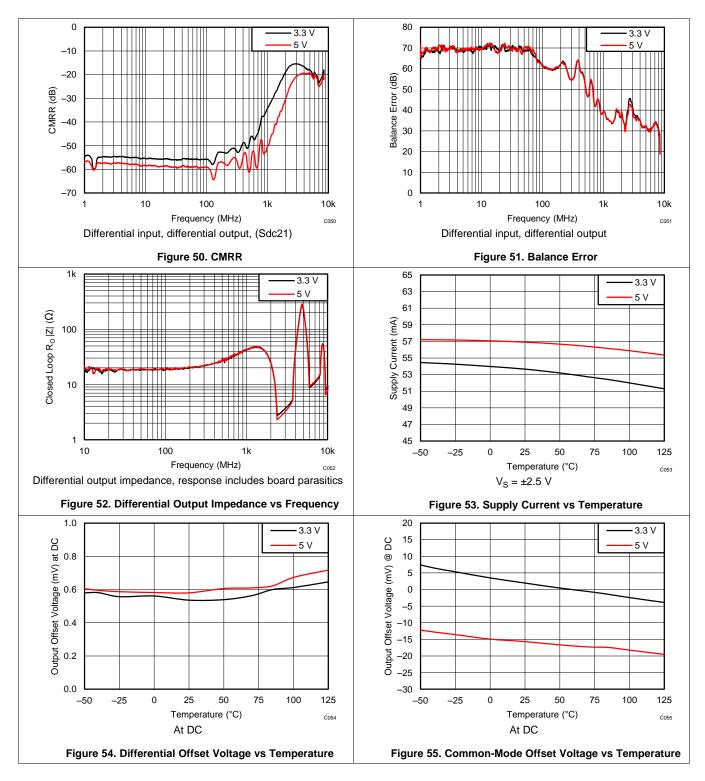

## 6.9 Typical Characteristics: 3.3-V to 5-V Supply Range

## 7 Parameter Measurement Information

## 7.1 Output Reference Points

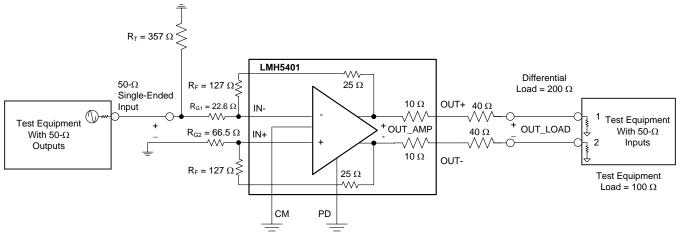

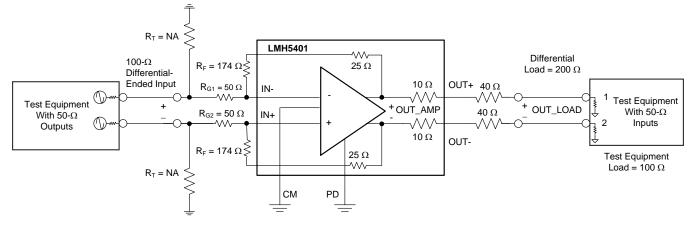

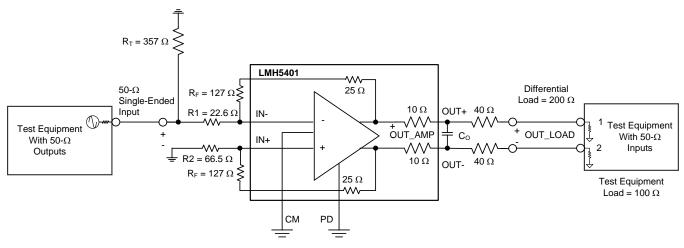

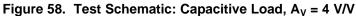

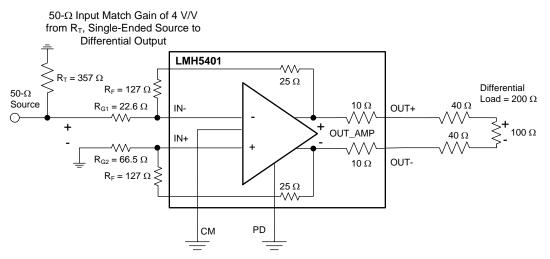

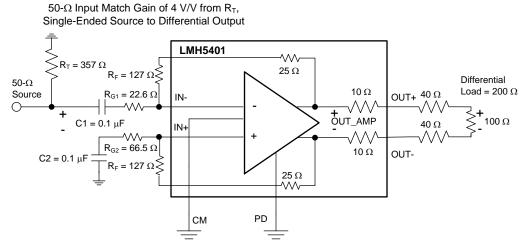

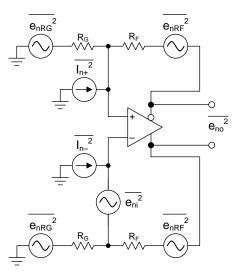

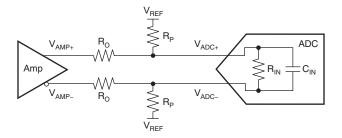

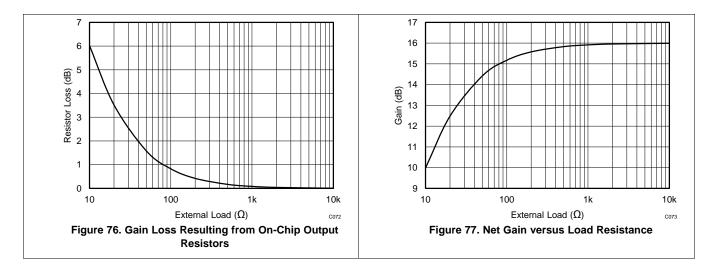

The LMH5401 is a fully-differential amplifier (FDA) configurable with external resistors for noise gain greater than 2 V/V or 6 dB (GBP = 8 GHz). For most of this document, data is collected for G = 12 dB for single-ended-todifferential (SE-DE) and differential-to-differential (DE-DE) conversions in the diagrams shown in the *Test Schematics* section. When matching the output to a 100- $\Omega$  load, the evaluation module (EVM) uses external 40- $\Omega$  resistors to complete the output matching. Having on-chip output resistors creates two potential reference points for measuring the output voltage. The amplifier output pins create one output reference point (OUT\_AMP). The other output reference point is the point at the matched 100- $\Omega$  load (OUT\_LOAD). These points are shown in Figure 56 to Figure 59; see the *Test Schematics* section.

Most measurements in the *Electrical Characteristics* tables and in the *Typical Characteristics* sections are measured with reference to the OUT\_AMP reference point. The conversion between reference points is a straightforward reduction of 3 dB for power and 6 dB for voltage, as shown in Equation 1. The measurements are referenced to OUT\_AMP when not specified.

VOUT\_LOAD = (VOUT\_AMP - 6 dB) and POUT\_LOAD = (POUT\_AMP - 3 dB) (1)

## 7.2 ATE Testing and DC Measurements

All production testing and ensured DC parameters are measured on automated test equipment capable of DC measurements only. Measurements such as output current sourcing and sinking are made in reference to the device output pins. Some measurements (such as voltage gain) reference the output of the internal amplifier and do not include losses attributed to the on-chip output resistors. The *Electrical Characteristics* table conditions specify these conditions. When the measurement refers to the amplifier output, then the output resistors are not included in the measurement. If the measurement refers to the device pins, then the output resistor loss is included in the measurement.

#### 7.3 Frequency Response

This test is run with single-ended inputs and differential inputs.

For tests with single-ended inputs, the standard EVM is used with no changes; see Figure 56. To provide a matched input, the unused input requires a broadband 50- $\Omega$  termination to connect. When using a four-port network analyzer, the unused input can be terminated with a broadband load, or can connect to the unused input on the four-port analyzer. The network analyzer provides proper termination. A network analyzer connects to the input and output of the EVM with 50- $\Omega$  coaxial cables and measures the forward transfer function (s21). The input signal frequency is swept with the signal level set for the required output amplitude.

The LMH5401 is fully symmetrical. Either input (IN+ or IN–) can be used for single-ended inputs. The unused input must be terminated.  $R_F$ ,  $R_{G1}$ , and  $R_{G2}$  determine the gain.  $R_T$  and  $R_M$  enable matching to the source resistance. See the *Test Schematics* section for more information on setting these resistors per gain and source impedance requirements. Bandwidth is dependant on gain settings because this device is a voltage feedback amplifier. With a GBP of 8 GHz, the approximate bandwidth is calculated for a specific application requirement, as shown in Equation 2. Figure 57 shows a test schematic for differential input and output.

GBP (Hz) = BW (Hz) × Noise Gain

(2)

www.ti.com

#### **Frequency Response (continued)**

For tests with differential inputs, the same setup for single-ended inputs is used except all four connectors are connected to a network analyzer port. Measurements are made in true differential mode on the Rohde & Schwarz<sup>®</sup> network analyzer or in calculated differential mode. In each case, the differential inputs are each driven with a 50- $\Omega$  source. Table 1 and Table 2 lists the resistor values used in frequency response sweeps.

| A <sub>V</sub> (V/V) | R <sub>G1</sub> , R <sub>G2</sub> (Ω) | $R_F$ (TOTAL / EXTERNAL, $\Omega$ ) | R <sub>T</sub> (Ω) |

|----------------------|---------------------------------------|-------------------------------------|--------------------|

| 2                    | 100                                   | 199 / 174                           | 100                |

| 4                    | 49.9                                  | 199 / 174                           | N/A                |

| 6                    | 49.9                                  | 300 / 274                           | N/A                |

| 8                    | 49.9                                  | 400 / 375                           | N/A                |

| 10                   | 49.9                                  | 500 / 475                           | N/A                |

#### Table 1. Differential Input/Output

#### Table 2. SE Input

| A <sub>V</sub> (V/V) | R <sub>G1</sub> (Ω) | R <sub>T</sub> (Ω) | R <sub>G2</sub> (Ω) | R <sub>F</sub> (TOTAL / EXTERNAL,<br>Ω) |

|----------------------|---------------------|--------------------|---------------------|-----------------------------------------|

| 2                    | 90.9                | 76.8               | 121                 | 200 / 175                               |

| 4                    | 22.6                | 357                | 66.5                | 152 / 127                               |

| 8                    | 12.1                | 1100               | 60.4                | 250 / 225                               |

| 10                   | 9.76                | 1580               | 57.6                | 300 / 275                               |

## 7.4 S-Parameters

The standard EVM is used for all s-parameter measurements. All four ports are used or are terminated with 50  $\Omega$ ; see the *Frequency Response* section.

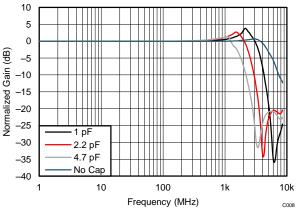

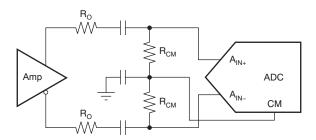

#### 7.5 Frequency Response with Capacitive Load

The standard EVM is used and the capacitive load is soldered to the inside pads of the 40- $\Omega$  matching resistors (on the DUT side). In this configuration, the on-chip, 10- $\Omega$  resistors isolate the capacitive load from the amplifier output pins. The test schematic for capacitive load measurements is shown in Figure 58.

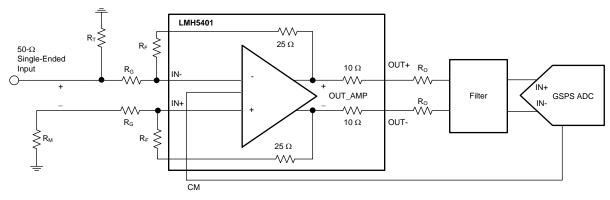

## 7.6 Distortion

The standard EVM is used for measuring single-tone harmonic distortion and two-tone intermodulation distortion. All distortion is measured with single-ended input signals; see Figure 59. To interface with single-ended test equipment, external baluns are required between the EVM output ports and the test equipment. The *Typical Characteristics* plots are created with Marki<sup>™</sup> baluns, model number BAL-0010. These baluns combine two tones in the two-tone test plots. For distortion measurements, the same termination must be used on both input pins. When a filter is used on the driven input port, the same filter and a broadband load terminate the other input. When the signal source is a broadband controlled impedance, only a broadband-controlled impedance is required to terminate the unused input.

#### 7.7 Noise Figure

The standard EVM is used with a single-ended input matched to  $50-\Omega$  and the Marki balun on the output similar to the harmonic distortion test setup.

#### 7.8 Pulse Response, Slew Rate, and Overdrive Recovery

The standard EVM is used for time-domain measurements. The input is single-ended with the differential outputs routed directly to the oscilloscope inputs. The differential signal response is calculated from the two separate oscilloscope inputs (Figure 25 to Figure 46). In addition, the common-mode response is captured in this configuration.

LMH5401 JAJSEU5D-OCTOBER 2014-REVISED FEBRUARY 2018

## 7.9 Power Down

The standard EVM is used with the shorting block on jumper JPD removed completely. A high-speed,  $50-\Omega$  pulse generator drives the PD pin when the output signal is measured by viewing the output signal (such as a 250-MHz sine-wave input).

## 7.10 V<sub>CM</sub> Frequency Response

The standard EVM is used with  $R_{CM+}$  and  $R_{CM-}$  removed and a new resistor installed at  $R_{TCM}$  = 49.9  $\Omega$ . The 49.9- $\Omega$  resistor is placed at C17 on the EVM schematic. A network analyzer is connected to the V<sub>CM</sub> input of the EVM and the EVM outputs are connected to the network analyzer with 50- $\Omega$  coaxial cables. Set the network analyzer analysis settings to single-ended input and differential output. Measure the output common-mode with respect to the single-ended input (Scs21). The input signal frequency is swept with the signal level set for 100 mV (–16 dBm). Note that the common-mode control circuit gain is one.

## 7.11 Test Schematics

Figure 56. Test Schematic: Single-Ended Input, Differential Output, A<sub>V</sub> = 4 V/V

Figure 57. Test Schematic: Differential Input, Differential Output,  $A_V = 4 V/V$

## **Test Schematics (continued)**

Figure 59. Test Schematic for Noise Figure and Single-Ended Harmonic Distortion, A<sub>V</sub> = 4 V/V

## 8 Detailed Description

#### 8.1 Overview

The LMH5401 is a very high-performance, differential amplifier optimized for radio frequency (RF) and intermediate frequency (IF) or high-speed, time-domain applications for wide bandwidth applications as the GBP is 8 GHz. The device is designed for DC- or AC-coupled applications that may require a single-ended-to-differential (SE-DE) conversion when driving an analog-to-digital converter (ADC). The required external feedback (R<sub>F</sub>) and gain set (R<sub>G</sub>) resistors configure the gain of the device. For the EVM the standard gain is set to G = 12 dB (for DE and SE conversions) with R<sub>F</sub> = 127  $\Omega$  and R<sub>G</sub> = 22.6  $\Omega$ .

A common-mode reference input pin aligns the amplifier output common-mode with the ADC input requirements. Power supplies between 3.3 V and 5 V are selected and dual-supply operation is supported when required by the application. A power-down feature is available for power savings.

The LMH5401 offers two on-chip termination resistors, one for each output with values of 10  $\Omega$  each. For most load conditions the 10- $\Omega$  resistors are a partial termination. Consequently, external termination resistors are required in most applications. See Table 4 for some common load values and the matching resistors.

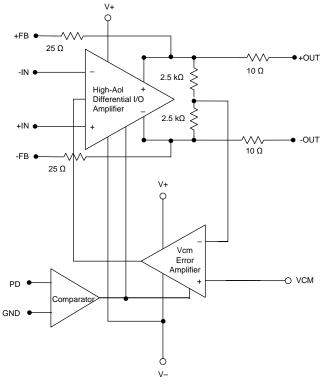

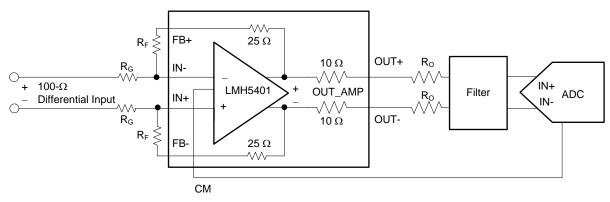

#### 8.2 Functional Block Diagram

V- and GND are isolated.

#### 8.3 Feature Description

The LMH5401 includes the following features:

- Fully-differential amplifier

- Flexible gain configurations using external resistors

- Output common-mode control

- · Single- or split-supply operation

- Gain bandwidth product (GBP) of 8 GHz

- Linear bandwidth of 2 GHz (G = 12 dB)

- Power down

#### 8.3.1 Fully-Differential Amplifier

The LMH5401 is a voltage feedback (VFA)-based fully-differential amplifier (FDA) offering a GBP of 8 GHz with flexible gain options using external resistors. The core differential amplifier is a slightly decompensated voltage feedback design with a high slew rate and best-in-class linearity up to 2 GHz for G = 12 dB (SE-DE, DE-DE).

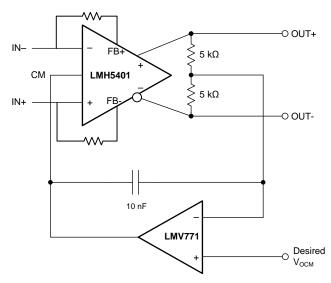

As with all FDA devices, the output average voltage (common-mode) is controlled by a separate common-mode loop. The target for this output average is set by the  $V_{CM}$  input pin. The  $V_{OCM}$  range extends from 1.1 V below the midsupply voltage to 1.1 V above the midsupply voltage when using a 5-V supply. Note that on a 3.3-V supply the output common-mode range is quite small. For applications using a 3.3-V supply voltage, the output common-mode must remain very close to the midsupply voltage.

The input common-mode voltage offers more flexibility than the output common-mode voltage. The input common-mode range extends from the negative rail to approximately 1 V above the midsupply voltage when powered with a 5-V supply.

#### 8.3.1.1 Power Down and Ground Pins

A power-down pin is included. This pin is referenced to the GND pins with a threshold voltage of approximately 1 V. Setting the PD pin voltage to more than the specified minimum voltage turns the device off, which places the LMH5401 into a very low quiescent current state. Note that when disabled, the signal path is still present through the passive external resistors. Input signals applied to a disabled LMH5401 device still appear at the outputs at some level through this passive resistor path, as with any disabled FDA device. The power-down pin is biased to the logic-low state with a 50-k $\Omega$  internal resistor.

#### 8.3.2 Operations for Single-Ended to Differential Signals

One of the most useful features supported by the FDA device is a simple conversion from a single-ended input to a differential output centered on a user-controlled, common-mode level. Although the output side is relatively straightforward, the device input pins move in a common-mode sense with the input signal. This feature increases the apparent input impedance to be greater than the  $R_G$  value. However, this feature can cause input clipping if this common-mode signal moves beyond the input range. This input active impedance issue applies to AC- and DC-coupled designs, and requires somewhat more complex solutions for the resistors to account for this active impedance, as shown in this section.

#### 8.3.2.1 AC-Coupled Signal Path Considerations for Single-Ended Input to Differential Output Conversion

When the signal path is AC coupled, the DC biasing for the LMH5401 becomes a relatively simple task. In all designs, start by defining the output common-mode voltage. The AC-coupling issue can be separated for the input and output sides of an FDA design. The input can be AC-coupled and the output DC coupled, or the output can be AC-coupled and the input DC-coupled, or they can both be AC-coupled. One situation where the output can be DC-coupled (for an AC-coupled input), is when driving directly into an ADC where the V<sub>OCM</sub> control voltage uses the ADC common-mode reference to directly bias the FDA output common-mode to the required ADC input common-mode. The feedback path must always be DC-coupled. In any case, the design starts by setting the desired V<sub>OCM</sub>. When an AC-coupled path follows the output pins, the best linearity is achieved by operating V<sub>OCM</sub> at midsupply. The V<sub>OCM</sub> voltage must be within the linear range for the common-mode loop, as specified in the headroom specifications. If the output path is AC-coupled, letting the V<sub>OCM</sub> control pin float is usually preferred to obtain a midsupply default V<sub>OCM</sub> bias with no external elements. To limit noise, place a 0.1- $\mu$ F decoupling capacitor on the V<sub>OCM</sub> pin to ground. After V<sub>OCM</sub> is defined, check the target output voltage swing to ensure that the V<sub>OCM</sub> positive or negative output swing on each side does not clip into the supplies. If the

#### Feature Description (continued)

desired output differential swing is defined as  $V_{OPP}$ , divide by 4 to obtain the  $\pm V_P$  swing around  $V_{OCM}$  at each of the two output pins (each pin operates 180° out of phase with the other). Check that  $V_{OCM} \pm V_P$  does not exceed the output swing of this device. Going to the device input pins side, because both the source and balancing resistor on the non-signal input side are DC blocked (see Figure 61), no common-mode current flows from the output common-mode voltage, thus setting the input common-mode equal to the output common-mode voltage. This input headroom sets a limit for higher  $V_{OCM}$  voltages. The minimum headroom for the input pins to the positive supply overrides the headroom limit for the output  $V_{OCM}$  because the input  $V_{ICM}$  is the output  $V_{OCM}$  for AC-coupled sources. The input signal moves this input  $V_{ICM}$  around the DC bias point, as shown in the *Resistor Design Equations for Single-to-Differential Applications* subsection of the *Fully-Differential Amplifier* section.

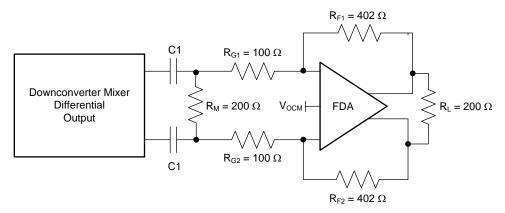

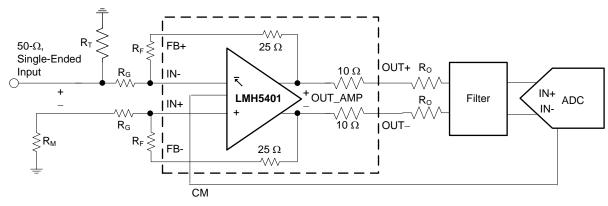

## 8.3.2.2 DC-Coupled Input Signal Path Considerations for SE-DE Conversions

The output considerations remain the same as for the AC-coupled design. The input can be DC-coupled when the output is AC-coupled. A DC-coupled input with an AC-coupled output can have some advantages to move the input V<sub>ICM</sub> down if the source is ground referenced. When the source is DC-coupled into the LMH5401 (as shown in Figure 60), both sides of the input circuit must be DC coupled to retain differential balance. Normally, the non-signal input side has an R<sub>G</sub> element biased to an expected source midrange value. Providing this midscale reference provides a balanced differential swing around V<sub>OCM</sub> at the outputs. Often, R<sub>G2</sub> is grounded for DC-coupled, bipolar-input applications. This configuration provides a balanced differential output if the source swings around ground. If the source swings from ground to some positive voltage, grounding R<sub>G2</sub> results in a unipolar output differential swing from both outputs at V<sub>OCM</sub> (when the input is at ground) to one polarity of swing. Biasing R<sub>G2</sub> to an expected midpoint for the input signal creates a differential output swing around V<sub>OCM</sub>. One significant consideration for a DC-coupled input is that V<sub>OCM</sub> sets up a common-mode bias current from the output back through R<sub>F</sub> and R<sub>G</sub> to the source on both sides of the feedback. Without input-balancing networks, the source must sink or source this DC current. After the input signal range and biasing on the other R<sub>G</sub> element is set, check that the voltage divider from V<sub>OCM</sub> to V<sub>I</sub> through R<sub>F</sub> and R<sub>G</sub> (and possibly R<sub>S</sub>) establishes an input V<sub>ICM</sub> at the device input pins that is in range.

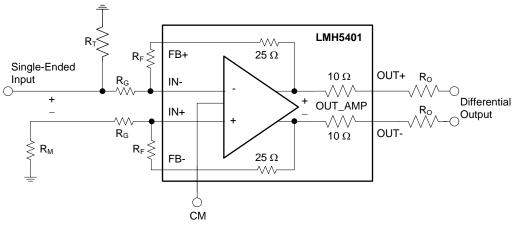

Figure 60. DC-Coupled, Single-Ended-to-Differential, Gain of 4 V/V

## 8.3.2.3 Resistor Design Equations for Single-to-Differential Applications

Being familiar with the FDA resistor selection criteria is still important because the LMH5401 gain is configured through external resistors. The design equations for setting the resistors around an FDA to convert from a singleended input signal to a differential output can be approached in several ways. In this section, several critical assumptions are made to simplify the results:

- The feedback resistors are selected first and are set to be equal on the two sides of the device.

- The DC and AC impedances from the summing junctions back to the signal source and ground (or a bias voltage on the non-signal input side) are set equal to retain the feedback divider balance on each side of the FDA.

#### Feature Description (continued)

Both of these assumptions are typical and are aimed to deliver the best dynamic range through the FDA signal path.

After the feedback resistor values are selected, the aim is to solve for  $R_T$  (a termination resistor to ground on the signal input side),  $R_{G1}$  (the input gain resistor for the signal path), and  $R_{G2}$  (the matching gain resistor on the non-signal input side); see Figure 61. This example uses the LMH5401, which is an external resistor FDA. The same resistor solutions can be applied to AC- or DC-coupled paths. Adding blocking capacitors in the input-signal chain is a simple option. Adding these blocking capacitors after the  $R_T$  element (see Figure 61) has the advantage of removing any DC currents in the feedback path from the output  $V_{OCM}$  to ground.

Figure 61. AC-Coupled, Single-Ended Source to a Differential Gain of a 4-V/V

Most FDA amplifiers use external resistors and have complete flexibility in the selected R<sub>F</sub>. However, the LMH5401 has small on-chip feedback resistors that are fixed at 25  $\Omega$ . The equations used in this section apply with an additional 25  $\Omega$  to add to the external R<sub>F</sub> resistors.

After the feedback resistor values are selected, solve for  $R_T$  (a termination resistor to ground on the signal input side),  $R_{G1}$  (the input gain resistor for the signal path), and  $R_{G2}$  (the matching gain resistor on the non-signal input side). The same resistor solutions are applied to AC- or DC-coupled paths. Adding blocking capacitors in the input-signal chain is a simple option. Adding these blocking capacitors after the  $R_T$  element has the advantage of removing any DC currents in the feedback path from the output V<sub>OCM</sub> to ground.

Earlier approaches to the solutions for  $R_T$  and  $R_{G1}$  (when the input must be matched to a source impedance,  $R_S$ ) follow an iterative approach. This complexity arises from the active input impedance at the  $R_{G1}$  input. When the FDA converts a single-ended signal to a differential signal, the common-mode input voltage at the FDA inputs must move with the input signal to generate the inverted output signal as a current in the  $R_{G2}$  element. A more recent solution is shown as Equation 3, where a quadratic in  $R_T$  is solved for an exact required value. This quadratic emerges from the simultaneous solution for a matched input impedance and target gain. The only required inputs are:

- 1. The selected  $R_F$  value.

- 2. The target voltage gain  $(A_v)$  from the input of  $R_T$  to the differential output voltage.

- 3. The desired input impedance at the junction of  $R_T$  and  $R_{G1}$  to match  $R_S$ .

Solving this quadratic for R<sub>T</sub> starts the solution sequence, as shown in Equation 3:

$$R_{T}^{2} - R_{T} \frac{2R_{S} \left(2R_{F} + \frac{R_{S}}{2}A_{V}^{2}\right)}{2R_{F} \left(2 + A_{V}\right) - R_{S}A_{V}(4 + A_{V})} - \frac{2R_{F}R_{S}^{2}A_{V}}{2R_{F} \left(2 + A_{V}\right) - R_{S}A_{V}(4 + A_{V})} = 0$$

(3)

## Feature Description (continued)

Because this equation is a quadratic, there are limits to the range of solutions. Specifically, after  $R_F$  and  $R_S$  are selected, there is physically a maximum gain beyond which Equation 3 starts to solve for negative  $R_T$  values (if input matching is a requirement). With  $R_F$  selected, use Equation 4 to verify that the maximum gain is greater than the desired gain.

$$Av_{max} = \left(\frac{R_{F}}{R_{S}} - 2\right) \cdot \left[1 + \sqrt{1 + \frac{4\frac{R_{F}}{R_{S}}}{\left(\frac{R_{F}}{R_{S}} - 2\right)^{2}}}\right]$$

(4)

#### LMH5401 JAJSEU5D – OCTOBER 2014 – REVISED FEBRUARY 2018

#### Feature Description (continued)

If the achievable  $A_{Vmax}$  is less than desired, increase the  $R_F$  value. After  $R_T$  is derived from Equation 3, the  $R_{G1}$  element is shown in Equation 5:

$$R_{G1} = \frac{2\frac{R_F}{A_V} - R_S}{1 + \frac{R_S}{R_T}}$$

(5)

Then, the simplest approach is to use a single  $R_{G2} = R_T || R_S + R_{G1}$  on the non-signal input side. Often, this approach is shown as the separate  $R_{G1}$  and  $R_S$  elements. This approach can provide a better divider match on the two feedback paths, but a single  $R_{G2}$  is often acceptable. A direct solution for  $R_{G2}$  is shown as Equation 6:

$$R_{G2} = \frac{2\frac{R_F}{A_V}}{1 + \frac{R_S}{R_T}}$$

(6)

This design proceeds from a target input impedance matched to  $R_S$ , signal gain  $A_V$ , and a selected  $R_F$  value. The nominal  $R_F$  value selected for the LMH5401 characterization is 152  $\Omega$  ( $R_{FExternal} + R_{FInternal}$ , where  $R_{FInternal}$  is always 25  $\Omega$ ). As discussed previously, this resistance is on-chip and cannot be changed. See Table 1 and Table 2 in the *Frequency Response* section, which lists the value of resistors used for characterization in this document.

#### 8.3.2.4 Input Impedance Calculations

The designs so far have included a source impedance ( $R_S$ ) that must be matched by  $R_T$  and  $R_{G1}$ . The total impedance with respect to the input at  $R_{G1}$  for the circuit of Figure 60 is the parallel combination of  $R_T$  to ground and ZA (active impedance) presented by the amplifier input at  $R_{G1}$ . That expression (assuming  $R_{G2}$  is set to obtain a differential divider balance) is shown in Equation 7:

$$ZA = R_{G1} \frac{\left(1 + \frac{R_{G1}}{R_{G2}}\right) \left(1 + \frac{R_{F}}{R_{G1}}\right)}{2 + \frac{R_{F}}{R_{G2}}}$$

(7)