**TPS25980** JAJSJ14 - AUGUST 2020

# TPS25980:2.7~24V、8A、3mΩスマート eFuse - 調整可能な過渡障害管理を備 えたホットスワップ保護機能搭載

# 1 特長

- 広い入力電圧範囲:2.7V~24V - 絶対最大定格:30V

- 低オン抵抗:R<sub>ON</sub> = 3mΩ (標準値)

- サーキット・ブレーカ応答

- 調整可能な電流制限スレッショルド

- 範囲:2A~8A

- 精度:±8% (I<sub>I M</sub> > 5A での標準値)

- 調整可能な過電流ブランキング・タイマ

- トリップなしに負荷過渡を処理

- 正確な電流モニタ出力

- ±3% (25℃、IOUT > 3A での標準値)

- フォルト応答をユーザーが設定可能

- ラッチ・オフまたは自動再試行

- 再試行回数(有限または無限)

- 再試行間隔

- 堅牢な短絡保護機能

- 高速トリップ応答時間:400ns 未満 (標準値)

- 100 万回の電源短絡イベントでテスト済み

- ライン過渡への耐性 不要なトリップなし

- 可変出力スルー・レート (dVdt) 制御

- 可変の低電圧誤動作防止

- 過電圧誤動作防止(固定 3.7V、7.6V、16.9V、および) OVLO なしのオプション)

- 過熱保護機能を内蔵

- パワー・グッド表示

- 可変の負荷検出およびハンドシェイク・タイマ

- UL 2367 認定

- ファイル番号 E339631

- R<sub>ILIM</sub> ≥ 182Ω

- IEC 62368 CB 認証

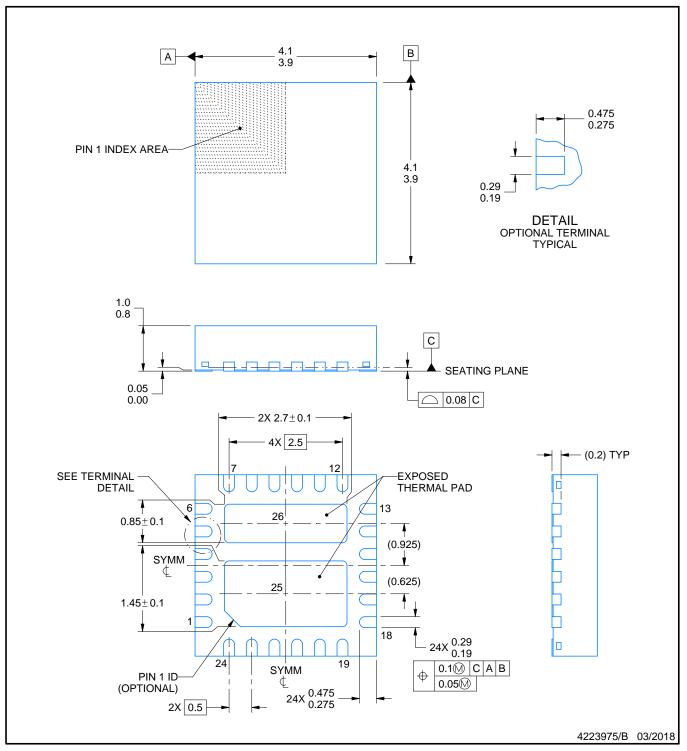

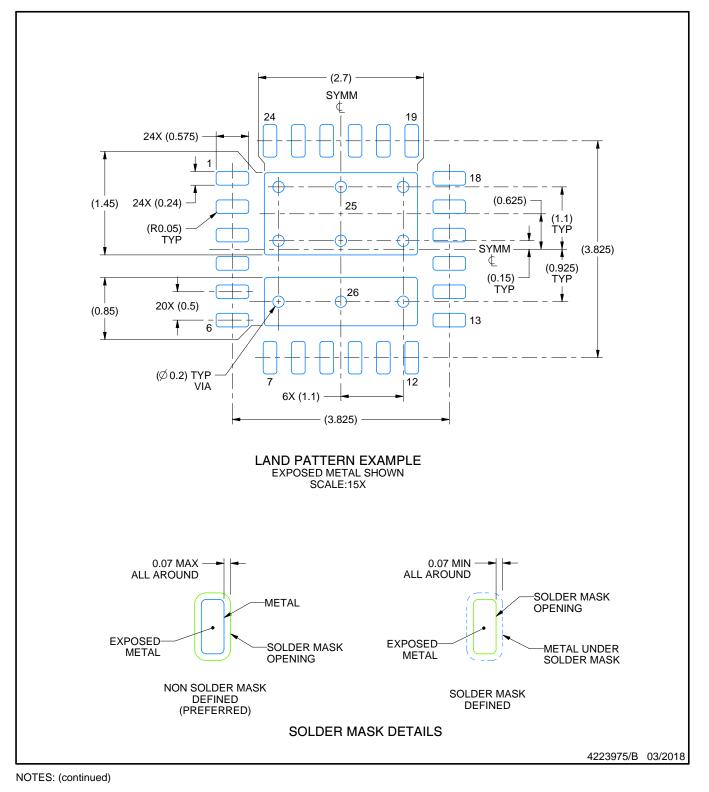

- 小さなフットプリント:4mm×4mmのQFN パッケージ

# 2 アプリケーション

- ホットスワップ、ホットプラグ

- サーバーのスタンバイ・レール、PCle ライザー、アドオ ン・カード、ファン・モジュールの保護

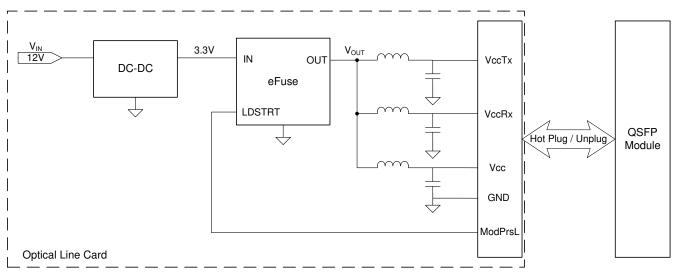

- ・ ルータおよびスイッチの光モジュール保護

- 産業用 PC

- デジタル TV

# 3 概要

TPS25980x ファミリの eFuse は、小さなパッケージに搭 載され、高度に統合された回路保護および電力管理ソリュ ーションです。これらのデバイスは、広い入力電圧範囲で 動作します。 I\*R 電圧降下を最小限に抑える必要がある 低電圧システムから、低消費電力を必要とする、より高電 圧の大電流システムまで、1 つの部品で対応できます。こ れらのデバイスは、過負荷、短絡、電圧サージ、過剰な突 入電流に対する堅牢な保護素子です。

過電圧事象は内部のカットオフ回路により制限されます。 過電圧スレッショルドを選択できるように、複数のデバイス・ オプションが用意されています。

このデバイスは、過電流状態に対してサーキット・ブレーカ 応答を提供します。過電流制限 (サーキット・ブレーカ・ス レッショルド)および高速トリップ (短絡)スレッショルドは、1 つの外付け抵抗で設定できます。これらのデバイスは、過 渡事象と実際のフォルトとを識別して、過電流応答をイン テリジェントに管理するので、フォルトに対する保護の堅牢 性を損なわずに、システムはライン過渡や負荷過渡の間も 中断なく動作できます。デバイスは、フォルト・シャットダウ ン後、ラッチ・オフに維持されるか、または自動的に再試行 を行うかを設定可能です。自動再試行の回数や再試行の 間隔は、コンデンサで設定できます。これによって、リモー ト・システムは一時的なフォルトから自動的に復元できると ともに、持続的なフォルトが原因で電源にいつまでもストレ スがかかることがないようになります。

TPS25980x デバイスは、小型の 4mm × 4mm QFN パッ ケージで供給されます。これらのデバイスは、-40℃~ 125℃の接合部温度範囲で動作が規定されています。

**制品情報(1)**

| 部品番号      | パッケージ    | 本体サイズ (公称)    |  |

|-----------|----------|---------------|--|

| TPS25980x | QFN (24) | 4.0mm × 4.0mm |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 | 特長                                   | 1   |

|---|--------------------------------------|-----|

|   | アプリケーション                             |     |

|   | 概要                                   |     |

| 4 | Revision History                     | . 2 |

|   | Device Comparison Table              |     |

| 6 | Pin Configuration and Functions      | .4  |

| 7 | Specifications                       | . 6 |

|   | 7.1 Absolute Maximum Ratings         | . 6 |

|   | 7.2 ESD Ratings                      | 6   |

|   | 7.3 Recommended Operating Conditions |     |

|   | 7.4 Thermal Information              | .7  |

|   | 7.5 Electrical Characteristics       |     |

|   | 7.6 Timing Requirements              | .9  |

|   | 7.7 Switching Characteristics        |     |

|   | 7.8 Typical Characteristics          |     |

| 8 | Detailed Description                 | 16  |

|   | 8.1 Overview                         | 16  |

|   | 8.2 Functional Block Diagram         |     |

|   | 8.3 Feature Description              | 16  |

|   | 8.4 Fault Response                   | 25  |

|   | 8.5 Device Functional Modes          | 27  |

| 9 Application and Implementation                      | . 28 |

|-------------------------------------------------------|------|

| 9.1 Application Information                           |      |

| 9.2 Typical Application: Patient Monitoring System in |      |

| Medical Applications                                  | 28   |

| 9.3 System Examples                                   |      |

| 10 Power Supply Recommendations                       |      |

| 10.1 Transient Protection                             | 39   |

| 10.2 Output Short-Circuit Measurements                | . 40 |

| 11 Layout.                                            |      |

| 11.1 Layout Guidelines                                | . 41 |

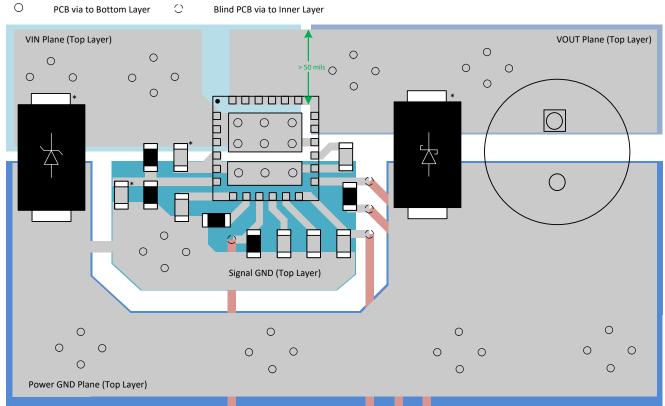

| 11.2 Layout Example                                   | . 42 |

| 12 Device and Documentation Support                   |      |

| 12.1 Documentation Support                            | .43  |

| 12.2 Receiving Notification of Documentation Updates. | 43   |

| 12.3 Support Resources                                | . 43 |

| 12.4 Trademarks                                       |      |

| 12.5 静電気放電に関する注意事項                                    | .43  |

| 12.6 Glossary                                         |      |

| 13 Mechanical, Packaging, and Orderable               |      |

| Information                                           | .44  |

|                                                       |      |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE        | REVISION | NOTES            |

|-------------|----------|------------------|

| August 2020 | *        | Initial release. |

# **5** Device Comparison Table

| PART NUMBER    | OVERVOLTAGE LOCKOUT<br>THRESHOLD<br>TYPICAL (V) | OVERCURRENT RESPONSE |

|----------------|-------------------------------------------------|----------------------|

| TPS259802ONRGE | 3.7                                             | Circuit Breaker      |

| TPS259803ONRGE | 7.6                                             | Circuit Breaker      |

| TPS259804ONRGE | 16.9                                            | Circuit Breaker      |

| TPS259807ONRGE | No OVLO                                         | Circuit Breaker      |

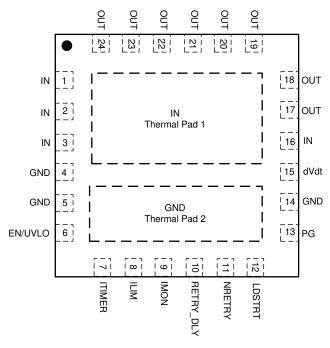

# 6 Pin Configuration and Functions

# 図 6-1. RGE 24-Pin QFN Top View

#### **Pin Functions**

| PIN                                                                   |                                      | TYPE               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----------------------------------------------------------------------|--------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                  | NO.                                  |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| OUT                                                                   | 17, 18, 19,<br>20, 21, 22,<br>23, 24 | Power              | Power Output.                                                                                                                                                                                                                                                                                                                                                               |  |  |

| IN                                                                    | 1, 2, 3, 16,<br>Pad 1                | Thermal /<br>Power | Power Input. The exposed pad must be soldered to input power plane uniformly to ensure proper heat dissipation and to maintain optimal current distribution through the device.                                                                                                                                                                                             |  |  |

| GND                                                                   | 4, 5, 14,<br>Pad 2                   | Ground             | Connect to System Ground.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| EN/UVLO                                                               | 6                                    | Analog Input       | Active High Enable for the device. A resistor divider on this pin from input supply to GND can be used to adjust the Undervoltage Lockout threshold. <b>Do not leave floating.</b>                                                                                                                                                                                          |  |  |

| ITIMER 7 Analog<br>Output                                             |                                      | 0                  | A capacitor from this pin to GND sets the overcurrent blanking interval during which the output current can temporarily exceed set current limit (but lower than fast-trip threshold) before the device overcurrent response takes action. Leave this pin open for fastest response to overcurrent events. Refer to <i>ITIMER Functional Mode Summary</i> for more details. |  |  |

| ILIM8Analog<br>OutputIMON9Analog<br>OutputRETRY_DLY10Analog<br>Output |                                      |                    | An external resistor from this pin to GND sets the output current limit threshold and fast trip threshold. <b>Do not leave floating.</b>                                                                                                                                                                                                                                    |  |  |

|                                                                       |                                      |                    | Analog output load current monitor. This pin sources a current proportional to the load current. This can be converted to a voltage signal by connecting an appropriate resistor from this pin to GND.                                                                                                                                                                      |  |  |

|                                                                       |                                      |                    | A capacitor from this pin to GND sets the time period that has to elapse after a fault shutdown before the device attempts to restart automatically. Connect this pin to GND for latch-off operation (no auto-retries) after a fault. Refer to <i>Fault Response</i> section for more details.                                                                              |  |  |

| NRETRY                                                                | 11                                   | Analog<br>Output   | A capacitor from this pin to GND sets the number of times the part attempts to restart automatically after shutdown due to fault. Connect this pin to GND if the part should retry indefinitely. Refer to <i>Fault Response</i> section for more details.                                                                                                                   |  |  |

## **Pin Functions (continued)**

| PI                                                                                                                                        | N   | TYPE                                                                                                                                                                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                      | NO. |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                  |

| LDSTRT 12 Analog Input PG assertion within which the pin has to be pulled low for to GND if the load detect/handshake feature is not used |     | Load Detect/Handshake Signal. A capacitor from this pin to GND sets the time period after PG assertion within which the pin has to be pulled low for the device to remain ON. Connect to GND if the load detect/handshake feature is not used. Refer to <i>Load Detect/Handshake</i> ( <i>LDSTRT</i> ) section for more details. <b>Do not leave floating.</b> |                                                                                                                                                                                                                                                                                  |

| PG                                                                                                                                        | 13  | Digital Output                                                                                                                                                                                                                                                                                                                                                 | Active High Power Good Indication. This pin is asserted when the FET is fully enhanced and output has reached maximum voltage. It is an open drain output that requires an external pull-up resistor to an external supply. This pin remains logic low when $V_{IN} < V_{UVP}$ . |

|                                                                                                                                           |     | Ũ                                                                                                                                                                                                                                                                                                                                                              | A capacitor from this pin to GND sets the output turn on slew rate. Leave this pin floating for the fastest slew rate during start up.                                                                                                                                           |

# **7** Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                        | Parameter                           | Pin       | MIN MAX                               | UNIT |

|------------------------|-------------------------------------|-----------|---------------------------------------|------|

| V <sub>IN</sub>        | Maximum Input Voltage Range         | IN        | -0.3 30                               | V    |

| V <sub>OUT</sub>       | Maximum Output Voltage Range        | OUT       | –0.8 min (30V, V <sub>IN</sub> + 0.3) | V    |

| V <sub>EN/UVLO</sub>   | Maximum Enable Pin Voltage Range    | EN/UVLO   | -0.3 7                                | V    |

| V <sub>LDSTRT</sub>    | Maximum LDSTRT Pin Voltage Range    | LDSTRT    | 7                                     | V    |

| V <sub>dVdt</sub>      | Maximum dVdt Pin Voltage Range      | dVdt      | Internally Limited                    | V    |

| V <sub>PG</sub>        | Maximum PG Pin Voltage Range        | PG        | -0.3 7                                | V    |

| VITIMER                | Maximum ITIMER Pin Voltage Range    | ITIMER    | Internally Limited                    | V    |

| V <sub>NRETRY</sub>    | Maximum NRETRY Pin Voltage Range    | NRETRY    | Internally Limited                    | V    |

| V <sub>RETRY_DLY</sub> | Maximum RETRY_DLY Pin Voltage Range | RETRY_DLY | Internally Limited                    | V    |

| I <sub>MAX</sub>       | Maximum Continuous Switch Current   | IN to OUT | Internally Limited                    | Α    |

| TJ                     | Junction temperature                |           | Internally Limited                    | °C   |

| T <sub>LEAD</sub>      | Maximum Soldering Temperature       |           | 300                                   | °C   |

| T <sub>stg</sub>       | Storage temperature                 |           | -65 150                               | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                    |                         |                                                                                         | VALUE  | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|--------|------|

| M                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>         | ± 2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ± 1000 | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                        | Parameter                              | Pin       | MIN                 | MAX                   | UNIT |

|------------------------|----------------------------------------|-----------|---------------------|-----------------------|------|

| V <sub>IN</sub>        | Input Voltage Range                    | IN        | 2.7                 | 24                    | V    |

| V <sub>OUT</sub>       | Output Voltage Range                   | OUT       |                     | V <sub>IN</sub> + 0.3 | V    |

| V <sub>EN/UVLO</sub>   | Enable Pin Voltage Range               | EN/UVLO   |                     | 6 <sup>(1)</sup>      | V    |

| V <sub>LDSTRT</sub>    | LDSTRT Pin Capacitor Voltage Rating    | LDSTRT    | 4                   |                       | V    |

| V <sub>dVdT</sub>      | dVdT Pin Capacitor Voltage Rating      | dVdt      | V <sub>IN</sub> + 4 |                       | V    |

| V <sub>PG</sub>        | PG Pin Voltage Range                   | PG        |                     | 6 <sup>(2)</sup>      | V    |

| VITIMER                | ITIMER Pin Capacitor Voltage Rating    | ITIMER    | 4                   |                       | V    |

| V <sub>NRETRY</sub>    | NRETRY Pin Capacitor Voltage Rating    | NRETRY    | 4                   |                       | V    |

| V <sub>RETRY_DLY</sub> | RETRY_DLY Pin Capacitor Voltage Rating | RETRY_DLY | 4                   |                       | V    |

| R <sub>ILIM</sub>      | ILIM Pin Resistor                      | ILIM      | 182                 | 1650                  | Ω    |

| I <sub>MAX</sub>       | Continuous Switch Current              | IN to OUT |                     | 8                     | А    |

| TJ                     | Junction temperature                   |           | -40                 | 125                   | °C   |

For supply voltages below 6V, it is okay to pull up the EN pin to IN directly. For supply voltages greater than 6V, it is recommended to use an appropriate resistor divider between IN, EN and GND to ensure the voltage at the EN pin is within the specified limits.

(2) For supply voltages below 6V, it is okay to pull up the PG pin to IN/OUT through a resistor. For supply voltages greater than 6V, it is recommended to use a stepped down power supply to ensure the voltage at the PG pin is within the specified limits.

## 7.4 Thermal Information

|                       | TPS25980X                                    |           |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup> <sup>(2)</sup> | RGE (QFN) | UNIT |

|                       |                                              | 24 PINS   |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 34.6      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 36.7      | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 11.2      | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 3         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 11.2      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.6       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

(2) Based on simulations conducted with the device mounted on a JEDEC 4-layer PCB (2s2p) with minimum recommended pad size (2 oz Cu) and 3x2 via array.

# 7.5 Electrical Characteristics

(Test conditions unless otherwise noted) –40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, V<sub>IN</sub> = 12 V for TPS259804x/7x, 5 V for TPS259803x, 3.3 V for TPS259802x, V<sub>EN/UVLO</sub> = 2 V, R<sub>ILIM</sub> = 1650  $\Omega$ , C<sub>dVdT</sub> = Open, OUT = Open. All voltages referenced to GND.

|                      | PARAMETER                                                                                                      | TEST CONDITIONS                                                    | MIN    | TYP  | MAX    | UNIT               |

|----------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------|------|--------|--------------------|

|                      | PLY (IN)                                                                                                       |                                                                    |        |      |        |                    |

| V <sub>IN</sub>      | Input Voltage Range                                                                                            |                                                                    | 2.7    |      | 24     | V                  |

| lq                   | IN Quiescent Current                                                                                           | $V_{EN} \ge V_{UVLO(R)}$                                           |        | 800  | 1200   | μA                 |

|                      | IN Shutdown Current                                                                                            | V <sub>SD</sub> < V <sub>EN</sub> < V <sub>UVLO</sub>              |        | 204  | 300    | μA                 |

| SD                   | IN Shutdown Current                                                                                            | V <sub>EN</sub> < V <sub>SD</sub>                                  |        | 3.67 | 20     | μA                 |

|                      | IN Undervoltage Protection                                                                                     | V <sub>IN</sub> Rising                                             | 2.46   | 2.53 | 2.6    | V                  |

| V <sub>UVP</sub>     | Threshold                                                                                                      | V <sub>IN</sub> Falling                                            | 2.35   | 2.42 | 2.49   | V                  |

| OVERVOLT             | AGE PROTECTION (IN)                                                                                            |                                                                    |        |      |        |                    |

|                      |                                                                                                                | TPS259802x, V <sub>IN</sub> Rising                                 | 3.62   | 3.7  | 3.76   | V                  |

| V <sub>OVP(R)</sub>  |                                                                                                                | TPS259803x, V <sub>IN</sub> Rising                                 | 7.39   | 7.6  | 7.76   | V                  |

|                      | Overveltage Protection Threshold                                                                               | TPS259804x, V <sub>IN</sub> Rising                                 | 16.32  | 16.9 | 17.31  | V                  |

|                      | Overvoltage Protection Threshold                                                                               | TPS259802x, V <sub>IN</sub> Falling                                | 3.52   | 3.6  | 3.66   | V                  |

| V <sub>OVP(F)</sub>  |                                                                                                                | TPS259803x, V <sub>IN</sub> Falling                                | 7.22   | 7.4  | 7.55   | V                  |

|                      |                                                                                                                | TPS259804x, V <sub>IN</sub> Falling                                | 15.80  | 16.4 | 16.81  | V                  |

| Ουτρυτ Cι            | JRRENT MONITOR (IMON)                                                                                          |                                                                    |        |      |        |                    |

| G <sub>IMON</sub>    | Current Monitor Gain (I <sub>IMON</sub> :I <sub>OUT</sub> )                                                    | $3 \text{ A} \leq I_{OUT} \leq \min(8 \text{ A}, I_{LIM})$         | 228.78 | 246  | 263.22 | µA/A               |

| Ουτρυτ Cι            | JRRENT LIMIT (ILIM)                                                                                            |                                                                    |        |      |        |                    |

|                      | I <sub>OUT</sub> Current Limit Threshold                                                                       | R <sub>ILIM</sub> = 773 Ω, T <sub>J</sub> = 25 °C                  | 1.76   | 2    | 2.17   | А                  |

|                      |                                                                                                                | $R_{ILIM}$ = 773 $\Omega$ , $T_J$ = -40 to 125 °C                  | 1.53   | 2    | 2.43   | А                  |

|                      |                                                                                                                | R <sub>ILIM</sub> = 300 Ω, T <sub>J</sub> = 25 °C                  | 4.75   | 4.98 | 5.23   | Α                  |

| I <sub>LIM</sub>     |                                                                                                                | $R_{ILIM}$ = 300 $\Omega$ , $T_J$ = -40 to 125 °C                  | 4.36   | 4.98 | 5.66   | А                  |

|                      |                                                                                                                | R <sub>ILIM</sub> = 182 Ω, T <sub>J</sub> = 25 °C                  | 7.77   | 8.13 | 8.54   | А                  |

|                      |                                                                                                                | $R_{ILIM}$ = 182 $\Omega$ , $T_J$ = -40 to 125 °C                  | 7.23   | 8.13 | 9.07   | А                  |

|                      |                                                                                                                | R <sub>ILIM</sub> = Open                                           |        | 0    |        | А                  |

| СВ                   | I <sub>OUT</sub> Circuit Breaker Threshold<br>During ILIM pin Short to GND<br>Condition (Single point failure) | R <sub>ILIM</sub> = Short to GND, T <sub>J</sub> = 25 °C           |        |      | 20     | A                  |

| I <sub>sc</sub>      | Short-circuit Fast Trip Threshold                                                                              |                                                                    |        | 210  |        | % I <sub>LIM</sub> |

| ON-RESIST            | ANCE (IN - OUT)                                                                                                | 1                                                                  |        |      |        |                    |

| D                    | ON State Registrate                                                                                            | T <sub>J</sub> = 25 °C, I <sub>OUT</sub> = 2 A                     |        | 3    |        | mΩ                 |

| R <sub>ON</sub>      | ON State Resistance                                                                                            | $T_{J}$ = -40 to 125 °C, $I_{OUT}$ = 2 A                           |        |      | 5      | mΩ                 |

| ENABLE / U           | INDERVOLTAGE LOCKOUT (EN/UVLO)                                                                                 | )                                                                  |        |      |        |                    |

| V <sub>UVLO(R)</sub> |                                                                                                                | V <sub>EN</sub> Rising                                             | 1.18   | 1.2  | 1.23   | V                  |

| V <sub>UVLO(F)</sub> | EN/UVLO Pin Voltage Threshold                                                                                  | V <sub>EN</sub> Falling                                            | 1.08   | 1.1  | 1.13   | V                  |

| V <sub>SD</sub>      | EN/UVLO Pin Voltage Threshold for<br>Lowest Shutdown Current                                                   | V <sub>EN</sub> Falling                                            | 0.59   | 0.8  |        | V                  |

| I <sub>ENLKG</sub>   | EN/UVLO Pin Leakage Current                                                                                    |                                                                    |        |      | 0.1    | μA                 |

| POWER GO             | OD INDICATION (PG)                                                                                             |                                                                    |        |      |        |                    |

|                      |                                                                                                                | $V_{IN}$ < $V_{UVP}$ , $V_{EN}$ < $V_{SD}$ , $I_{PG}$ = 26 $\mu$ A |        | 651  | 786    | mV                 |

| V <sub>PGD</sub>     | PG Pin Low Voltage (PG de-<br>asserted)                                                                        | V <sub>IN</sub> = 3.3V, I <sub>PG</sub> ≤ 5 mA                     |        | 320  |        | mV                 |

|                      |                                                                                                                | V <sub>IN</sub> ≥ 5V, I <sub>PG</sub> ≤ 5 mA                       |        | 100  |        | mV                 |

| I <sub>PGLKG</sub>   | PG Pin Leakage Current (PG asserted)                                                                           | PG pulled up to 5 V through 10 k $\Omega$                          |        | ·    | 1.7    | μA                 |

| R <sub>ON(PGA)</sub> | R <sub>ON</sub> When PG is asserted                                                                            |                                                                    |        | 4.2  |        | mΩ                 |

## 7.5 Electrical Characteristics (continued)

(Test conditions unless otherwise noted) –40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C, V<sub>IN</sub> = 12 V for TPS259804x/7x, 5 V for TPS259803x, 3.3 V for TPS259802x, V<sub>EN/UVLO</sub> = 2 V, R<sub>ILIM</sub> = 1650  $\Omega$ , C<sub>dVdT</sub> = Open, OUT = Open. All voltages referenced to GND.

| PARAMETER                  |                                                                    | TEST CONDITIONS                                                               | MIN   | TYP   | MAX   | UNIT |

|----------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------|-------|-------|-------|------|

| V <sub>PGTHD</sub>         | $V_{\text{IN}}$ - $V_{\text{OUT}}$ Threshold when PG is deasserted |                                                                               | 0.224 | 0.326 | 0.450 | V    |

| AUTO-RETRY I               | DELAY INTERVAL (RETRY_DLY)                                         | · · · · ·                                                                     |       |       |       |      |

| V <sub>RETRY_DLY(R)</sub>  | RETRY_DLY Oscillator Comparator                                    |                                                                               |       | 1.1   |       | V    |

| V <sub>RETRY_DLY(F)</sub>  | Threshold                                                          |                                                                               |       | 0.35  |       | V    |

| V <sub>RETRY_DLY_HYS</sub> | RETRY_DLY Oscillator Hysteresis                                    |                                                                               | 0.65  | 0.75  | 0.85  | V    |

| I <sub>RETRY_DLY</sub>     | RETRY_DLY Pin Bias Current                                         |                                                                               | 1.7   | 2.05  | 2.5   | μA   |

| NUMBER OF A                | UTO-RETRIES (NRETRY)                                               |                                                                               |       |       |       |      |

| V <sub>NRETRY(R)</sub>     | NRETRY Oscillator Comparator                                       |                                                                               |       | 1.1   |       | V    |

| V <sub>NRETRY(F)</sub>     | Threshold                                                          |                                                                               |       | 0.35  |       | V    |

| V <sub>NRETRY_HYS</sub>    | NRETRY Oscillator Hysteresis                                       |                                                                               | 0.65  | 0.75  | 0.85  | V    |

| INRETRY                    | NRETRY Pin Bias Current                                            |                                                                               | 1.7   | 2.05  | 2.5   | μA   |

| CURRENT FAU                | LT TIMER (ITIMER)                                                  |                                                                               |       |       |       |      |

| IITIMER                    | ITIMER Discharge Current                                           | $I_{SC} > I_{OUT} > I_{LIM}$                                                  | 1.4   | 2.1   | 2.8   | μA   |

| R <sub>ITIMER</sub>        | ITIMER Internal Pull-up Resistance                                 | I <sub>OUT</sub> < I <sub>LIM</sub>                                           |       | 23    |       | kΩ   |

| V <sub>INT</sub>           | ITIMER Pin Default Voltage                                         | I <sub>OUT</sub> < I <sub>LIM</sub>                                           |       | 2.5   |       | V    |

| VITIMER                    | ITIMER Comparator Falling<br>Threshold                             | I <sub>SC</sub> > I <sub>OUT</sub> > I <sub>LIM,</sub> ITIMER Voltage Rising  |       | 1.53  |       | V    |

| ΔV <sub>ITIMER</sub>       | ITIMER Comparator Voltage<br>Threshold Delta                       | I <sub>SC</sub> > I <sub>OUT</sub> > I <sub>LIM,</sub> ITIMER Voltage Falling | 0.7   | 0.98  | 1.3   | V    |

| LDSTRT                     |                                                                    |                                                                               |       |       | •     |      |

| V <sub>LDSTRT</sub>        | LDSTRT Rising Threshold                                            | LDSTRT voltage rising                                                         | 1.1   | 1.21  | 1.3   | V    |

| ILDSTRT                    | LDSTRT Charging Current                                            | PG asserted                                                                   | 1.7   | 2.05  | 2.4   | μA   |

| R <sub>LDSTRT</sub>        | LDSTRT Internal Pull-down<br>Resistance                            |                                                                               |       | 31    |       | Ω    |

| RQOD                       | QOD effective resistance                                           | IN connected to EN, OUT connected to QOD, EN! to 1V                           |       | 73.2  |       | mA   |

| OVERTEMPER                 | ATURE PROTECTION                                                   | ·                                                                             |       |       |       |      |

| TSD                        | Thermal Shutdown Threshold                                         | T <sub>J</sub> Rising                                                         |       | 150   |       | °C   |

| TSDHys                     | Thermal Shutdown Hysteresis                                        | T <sub>J</sub> Falling                                                        |       | 10    |       | °C   |

| dVdt                       |                                                                    | · /                                                                           |       |       | I     |      |

| I <sub>dVdt</sub>          | dVdt Pin Charging Current                                          |                                                                               | 2     | 4.6   | 6.33  | μA   |

## 7.6 Timing Requirements

|                  | PARAMETER                                                            | TEST CONDITIONS                                                                                    | MIN TYP | MAX | UNIT |

|------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------|-----|------|

|                  |                                                                      | $V_{\text{IN}}$ > $V_{\text{OVLO}(\text{R})}$ to $V_{\text{OUT}}\downarrow$ , TPS259802x           | 1.5     |     | μs   |

| t <sub>OVP</sub> | t <sub>OVP</sub> Overvoltage Protection Response Time <sup>(1)</sup> | $V_{IN} > V_{OVLO(R)}$ to $V_{OUT} \downarrow$ , TPS259803x                                        | 5       |     | μs   |

|                  |                                                                      | $V_{IN} > V_{OVLO(R)}$ to $V_{OUT} \downarrow$ , TPS259804x                                        | 5       |     | μs   |

| t <sub>SC</sub>  | Short Circuit Response Time                                          | $I_{OUT}$ > 3 x $I_{LIM}$ to $V_{OUT}$ turned OFF                                                  | 400     |     | ns   |

| t <sub>PGD</sub> | PG Assertion/De-assertion De-glitch (2)                              | $V_{G}$ > (V_{IN} + 3.6V) to PG $\uparrow~$ or (V_{IN} - V_{OUT})> $V_{PGTHD}$ to PG $\downarrow~$ | 120     |     | μs   |

Please refer to Fig. 8-2

Please refer to Fig. 8-5

# 7.7 Switching Characteristics

The output rising slew rate is internally controlled and constant across the entire operating voltage range to ensure the turn on timing is not affected by the load conditions. The rising slew rate can be adjusted by adding capacitance from the dVdt pin to ground. As  $C_{dVdt}$  is increased it will slow the rising slew rate (SR). See Slew Rate and Inrush Current Control (dVdt) section for more details. The Turn-Off Delay and Fall Time, however, are dependent on the RC time constant of the load capacitance ( $C_{OUT}$ ) and Load Resistance ( $R_L$ ). The Switching Characteristics are only valid for the power-up sequence where the supply is available in steady state condition and the load voltage is completely discharged before the device is enabled.Typical Values are taken at  $T_J = 25^{\circ}$ C unless specifically noted otherwise.  $R_L = 3.6 \Omega$ ,  $C_{OUT} = 1 \text{ mF}$

|                    | PARAMETER               | V <sub>IN</sub> | C <sub>dVdt</sub> = Open | C <sub>dVdt</sub> = 3300pF | C <sub>dVdt</sub> =<br>6800pF | UNIT |

|--------------------|-------------------------|-----------------|--------------------------|----------------------------|-------------------------------|------|

|                    |                         | 2.7 V           | 6.26                     | 1.39                       | 0.68                          |      |

| SR <sub>ON</sub>   | Output Rising slew rate | 12 V            | 7.35                     | 1.4                        | 0.68                          | V/ms |

|                    |                         | 24 V            | 7.4                      | 1.4                        | 0.68                          |      |

|                    |                         | 2.7 V           | 1.3                      | 1.49                       | 1.7                           |      |

| t <sub>D,ON</sub>  | Turn on delay           | 12 V            | 1.24                     | 2.1                        | 3.01                          | ms   |

|                    |                         | 24 V            | 1.2                      | 2.91                       | 4.74                          |      |

|                    |                         | 2.7 V           | 0.67                     | 1.63                       | 3.35                          |      |

| t <sub>R</sub>     | Rise time               | 12 V            | 1.35                     | 6.99                       | 14.41                         | ms   |

|                    |                         | 24 V            | 2.66                     | 13.77                      | 28.41                         |      |

|                    |                         | 2.7 V           | 1.97                     | 3.12                       | 5.05                          | ms   |

| t <sub>ON</sub>    | Turn on time            | 12 V            | 2.59                     | 9.09                       | 17.42                         |      |

|                    |                         | 24 V            | 3.86                     | 16.68                      | 33.15                         |      |

|                    |                         | 2.7 V           | 151                      | 152                        | 152                           |      |

| t <sub>D,OFF</sub> | Turn off delay          | 12 V            | 212                      | 212                        | 212                           | μs   |

|                    |                         | 24 V            | 262                      | 262                        | 262                           |      |

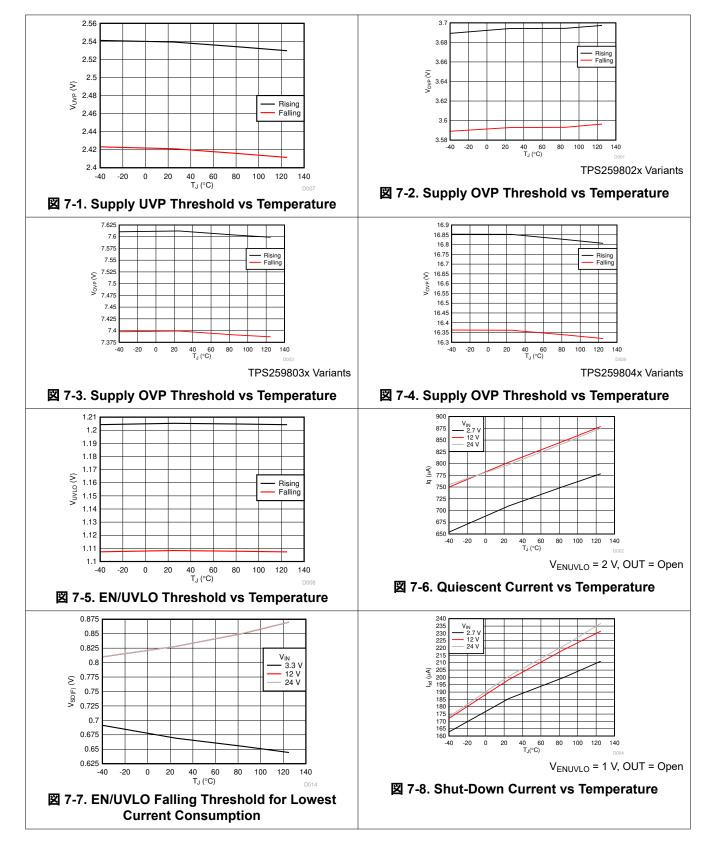

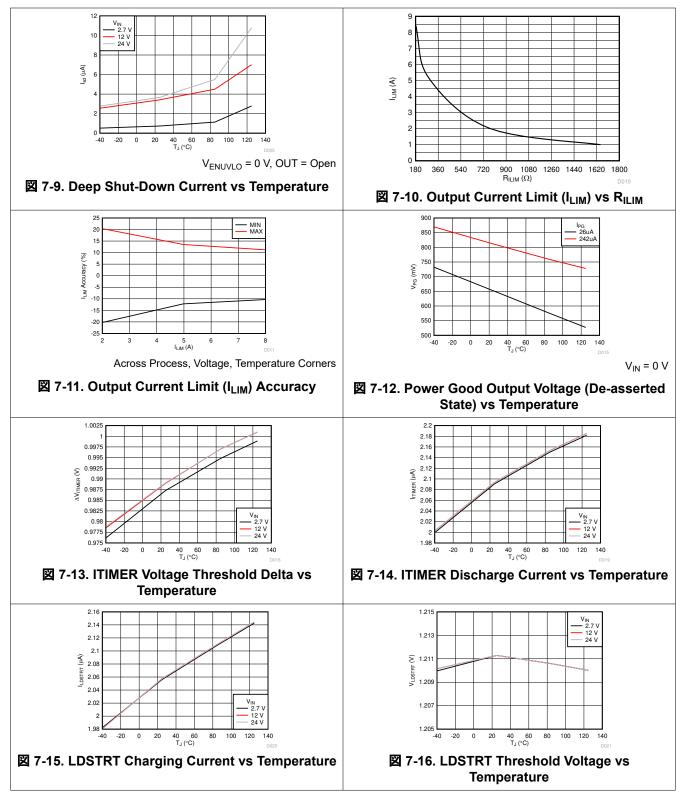

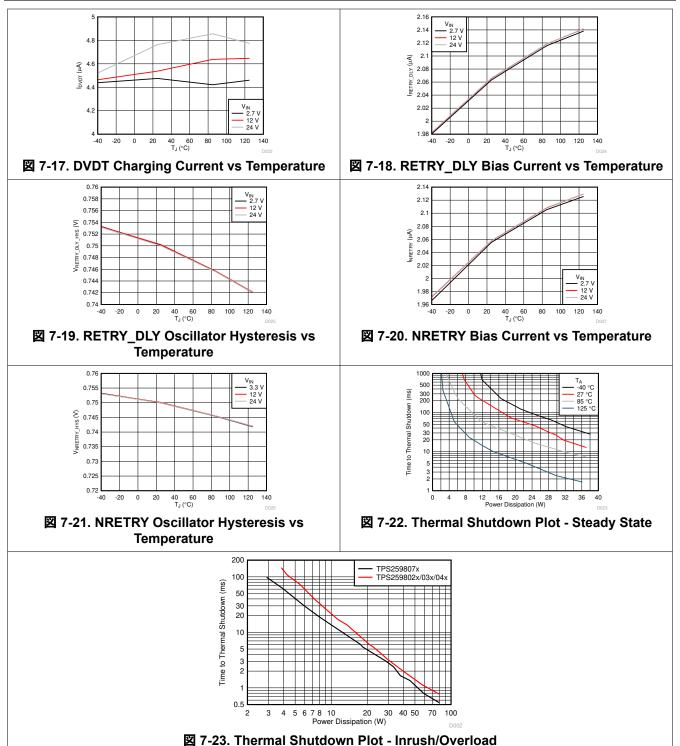

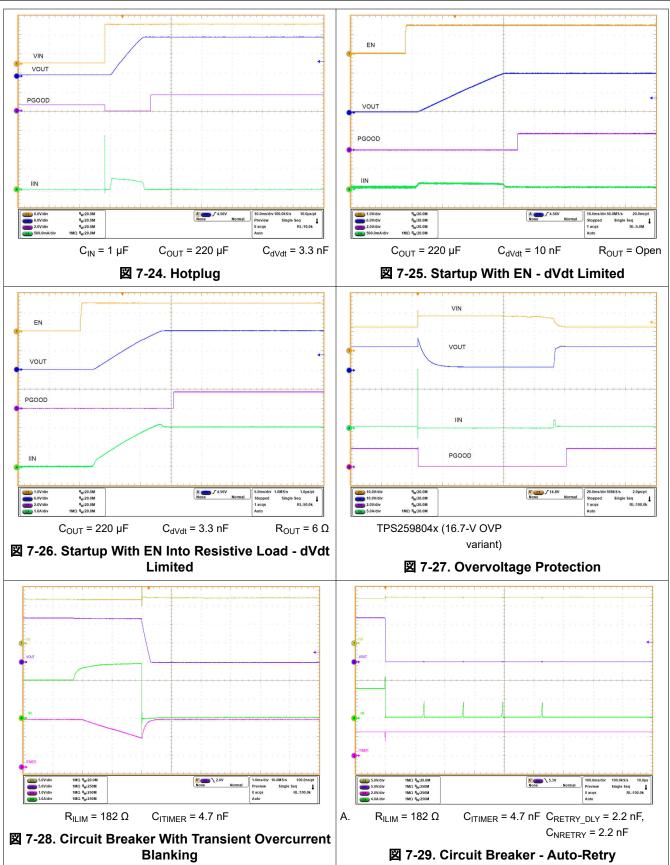

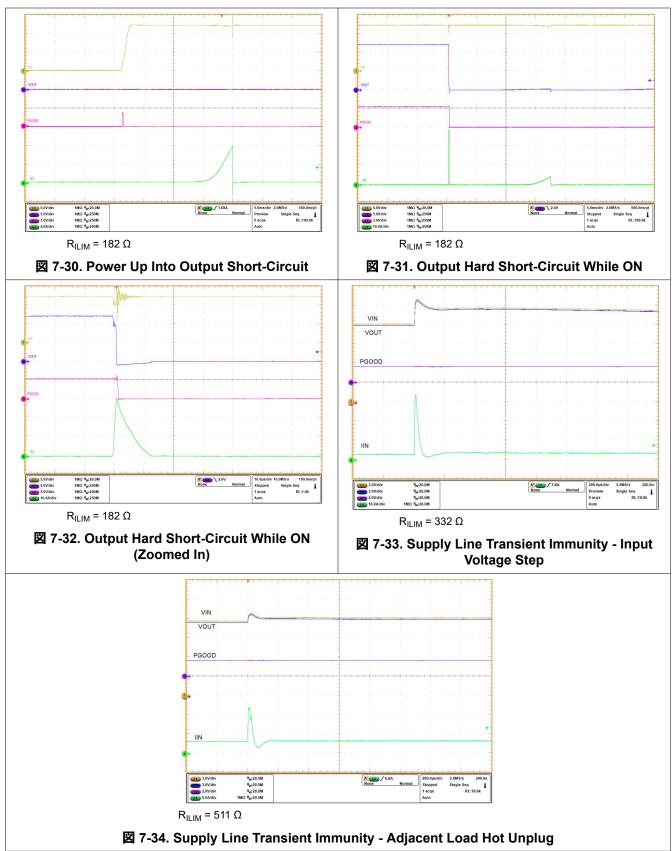

# 7.8 Typical Characteristics

**TPS25980** JAJSJ14 – AUGUST 2020

# 8 Detailed Description

# 8.1 Overview

The TPS25980x device is a smart eFuse with integrated power switch that is used to manage load voltage and load current. The device starts its operation by monitoring the IN bus. When  $V_{IN}$  is above the Undervoltage Protection threshold ( $V_{UVP}$ ) and below the Overvoltage Protection threshold ( $V_{OVP}$ ), the device samples the EN/UVLO pin. A high level on this pin enables the internal MOSFET to start conducting and allow current to flow from IN to OUT. When EN/UVLO is held low, the internal MOSFET is turned off. After a successful start-up sequence, the device now actively monitors its load current, input voltage and protects the load from harmful overcurrent and overvoltage conditions. The device also relies on a built-in thermal sense circuit to shut down and protect itself in case the device internal temperature ( $T_{J}$ ) exceeds the safe operating conditions.

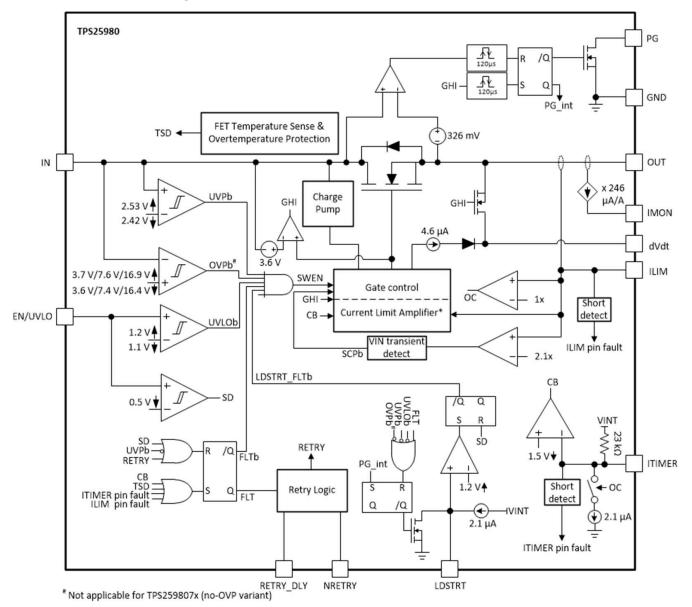

# 8.2 Functional Block Diagram

# 8.3 Feature Description

The TPS25980x eFuse is a compact, feature rich power management device that provides detection, protection and indication in the event of system faults.

#### 8.3.1 Undervoltage Protection (UVLO and UVP)

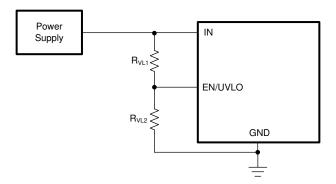

The TPS25980x implements Undervoltage Protection on IN to turn off the output in case the applied voltage becomes too low for the downstream load or the device to operate correctly. The Undervoltage Protection has a default internal threshold of  $V_{UVP}$ . If needed, it is also possible to set a user defined Undervoltage Protection threshold higher than  $V_{UVP}$  using the UVLO comparator on the EN/UVLO pin. 🛛 8-1 and  $\overrightarrow{1}$  1 show how a resistor divider from supply to GND can be used to set the UVLO set point for a given voltage supply level.

図 8-1. Adjustable Supply UVLO Threshold

$VINUVLO = \frac{VUVLO(R) \ x \ (RVL1 + RVL2)}{RVL2}$

(1)

The resistors must be sized large enough to minimize the constant leakage from supply to ground through the resistor divider network. At the same time, keep the current through the resistor network sufficiently larger (20x) than the leakage current on the EN/UVLO pin to minimize the error in the resistor divider ratio.

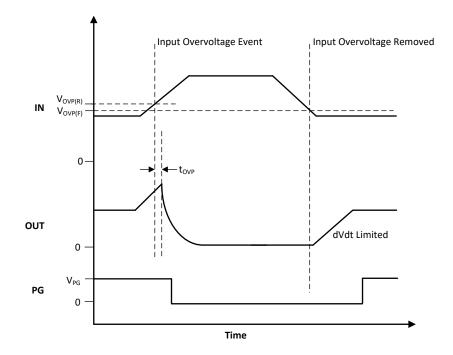

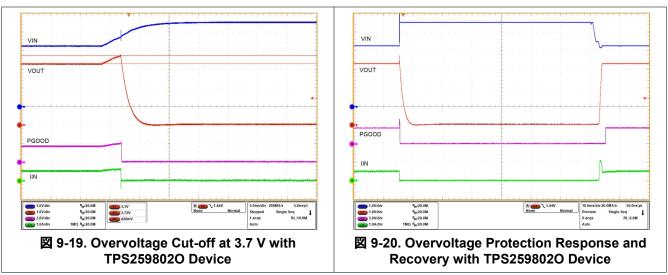

#### 8.3.2 Overvoltage Protection (OVP)

The TPS25980x implements Overvoltage Lock-Out (OVLO) on IN to protect the output load in the event of input overvoltage. When the input exceeds the Overvoltage Protection threshold ( $V_{OVP(R)}$ ) the device turns off the output within  $t_{OVP}$ . As long as an overvoltage condition is present on the input, the device stays disabled and the output will be turned off. Once the input voltage returns to the normal operating range, the device attempts to start up normally.

図 8-2. Overvoltage Response

There are multiple device options with different fixed overvoltage thresholds to choose from, including one without internal overvoltage protection. See the *Device Comparison Table* for a list of available options.

#### 8.3.3 Inrush Current, Overcurrent, and Short-Circuit Protection

TPS25980x devices incorporate three levels of protection against overcurrent:

- Adjustable slew rate (dVdt) for inrush current control

- Adjustable overcurrent protection (with adjustable blanking timer) Circuit Breaker to protect against soft overload conditions

- · Adjustable fast-trip response to quickly protect against severe overcurrent (short-circuit) faults

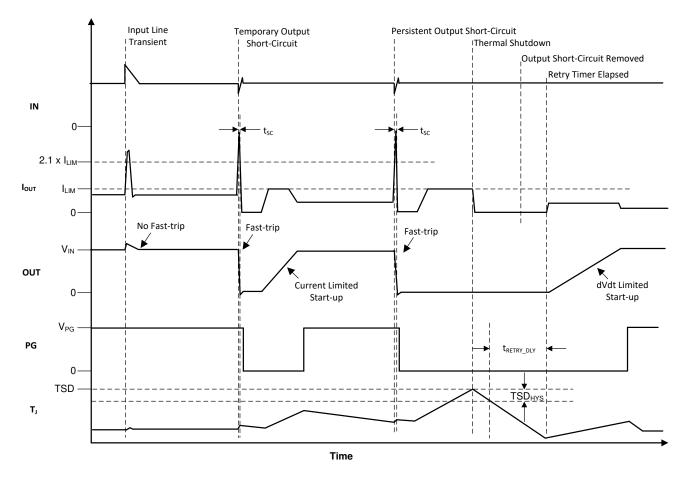

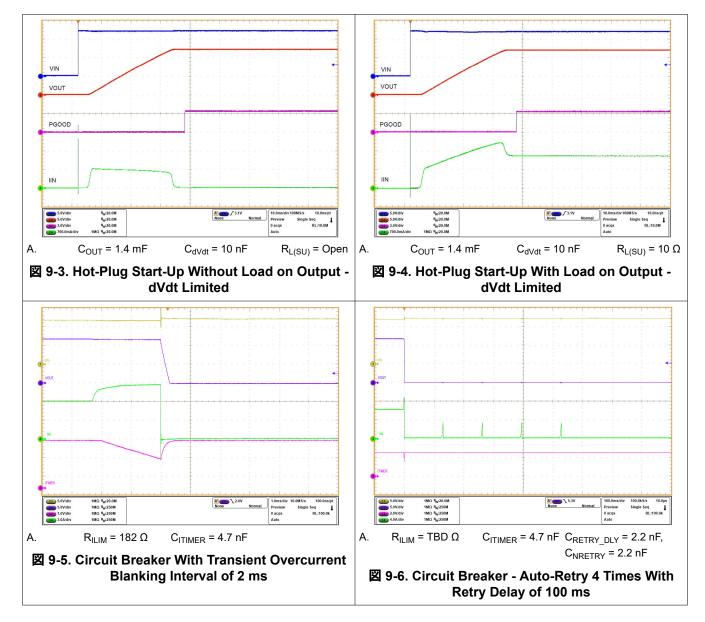

## 8.3.3.1 Slew Rate and Inrush Current Control (dVdt)

During hot-plug events or while trying to charge a large output capacitance, there can be a large inrush current. If the inrush current is not controlled, it can damage the input connectors and/or cause the system power supply to droop leading to unexpected restarts elsewhere in the system. The TPS25980x provides integrated output slew rate (dVdt) control to manage the inrush current during start-up. The inrush current is directly proportional to the load capacitance and rising slew rate. The following equation can be used to calculate the slew rate (SR) required to limit the inrush current ( $I_{INRUSH}$ ) for a given load capacitance ( $C_{OUT}$ ):

$$SR(V/ms) = \frac{IINRUSH(mA)}{COUT(\mu F)}$$

(2)

An external capacitance can be connected to the dVdt pin to control the rising slew rate and lower the inrush current during turn on. The required  $C_{dVdt}$  capacitance to produce a given slew rate can be calculated using the following formula:

$$CdVdt(pF) = \frac{4600}{SR(V/ms)}$$

The fastest output slew rate is achieved by leaving the dVdt pin open.

(3)

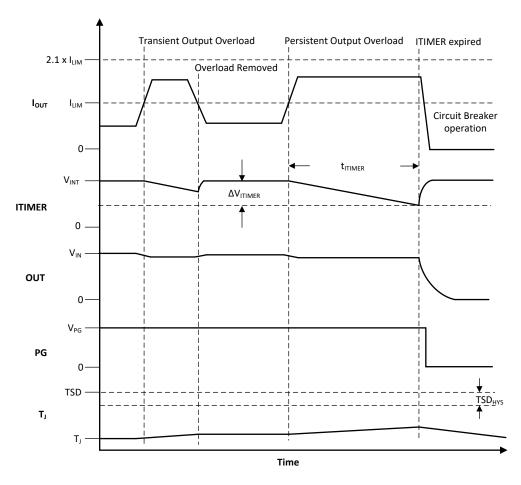

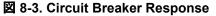

#### 8.3.3.2 Circuit Breaker

The TPS25980x responds to output overcurrent conditions by turning off the output after a user adjustable transient fault blanking interval. When the load current exceeds the programmed current limit threshold (I<sub>LIM</sub> set by the ILIM pin resistor R<sub>ILIM</sub>), but lower than the fast-trip threshold (2.1 x I<sub>LIM</sub>), the device starts discharging the ITIMER pin capacitor using an internal pull-down current (I<sub>ITIMER</sub>). If the load current drops below the current limit threshold before the ITIMER capacitor drops by  $\Delta V_{\text{ITIMER}}$ , the circuit breaker action is not engaged and the ITIMER is reset by pulling it up to V<sub>INT</sub> internally. This allows short transient overcurrent pulses to pass through the device without tripping the circuit. If the overcurrent condition persists, the ITIMER capacitor continues to discharge and once it falls by  $\Delta V_{\text{ITIMER}}$ , the circuit breaker action turns off the FET immediately. The following equation can be used to calculate the R<sub>ILIM</sub> value for a desired current limit threshold.

$\text{RiLIM}(\Omega) = \frac{1460}{\text{ILIM}(A) - 0.11}$

(4)

#### Note

Leaving the ILIM pin Open sets the current limit to zero and causes the FET to shut off as soon as any load current is detected. Shorting the ILIM pin to ground at any point during normal operation is detected as a fault and the part shuts down. The ILIM pin Short to GND fault detection circuit requires a minimum amount of load current ( $I_{CB}$ ) to flow through the device. This ensures robust eFuse behavior even under single point failure conditions. Refer to the *Fault Response* section for details on the device behavior after a fault.

The duration for which load transients are allowed can be adjusted using an appropriate capacitor value from ITIMER pin to ground. The transient overcurrent blanking interval can be calculated using  $\pm 5$ .

$$\text{titimer}(\text{ms}) = \frac{\text{Citimer}(\text{nF}) \times \Delta \text{Vitimer}(\text{V})}{\text{Iitimer}(\mu A)}$$

(5)

Leave the ITIMER pin open to allow the part to break the circuit with the minimum possible delay.

| 表 8-1.          | Device | ITIMER | Functional | Mode  | Summary |

|-----------------|--------|--------|------------|-------|---------|

| <b>3</b> X 0⁻Ⅰ. | Device |        | гипсиона   | woue, | Summary |

| ITIMER Pin Connection | Timer Delay before Overcurrent response |

|-----------------------|-----------------------------------------|

| OPEN                  | 0 s                                     |

| Capacitor to ground   | As per Equation 5                       |

| Short to GND          | ITIMER Pin Fault - Part Shuts Off       |

#### Note

1. Shorting the ITIMER pin to ground is detected as a fault and the part shuts down. This ensures robust eFuse behavior even in case of single point failure conditions. Refer to the *Fault Response* section for details on the device behavior after a fault.

2. Larger ITIMER capacitors take longer to charge during start-up and may lead to incorrect fault assertion if the ITIMER voltage is still below the pin short detection threshold after the device has reached steady state. To avoid this, it is recommended to limit the maximum ITIMER capacitor to the value suggested by the equation below.

CITIMER <

$$\frac{\text{tGHI}}{53000}$$

tGHI = tD,ON + Cdvdt ×  $\left(\frac{\text{VIN} + 3.6\text{V}}{\text{Idvdt}}\right)$

Where

- t<sub>GHI</sub> is the time taken by the device to reach steady state

- t<sub>D.ON</sub> is the device turn-on delay

- C<sub>dvdt</sub> is the dVdt capacitance

- I<sub>dvdt</sub> is the dVdt charging current

It is possible to avoid incorrect ITIMER pin fault assertion and achieve higher ITIMER intervals if needed by increasing the dVdt capacitor value accordingly, but at the expense of higher start-up time.

Once the part shuts down due to a Circuit Breaker fault, it can be configured to either stay latched off or restart automatically. Refer to the *Fault Response* section for details.

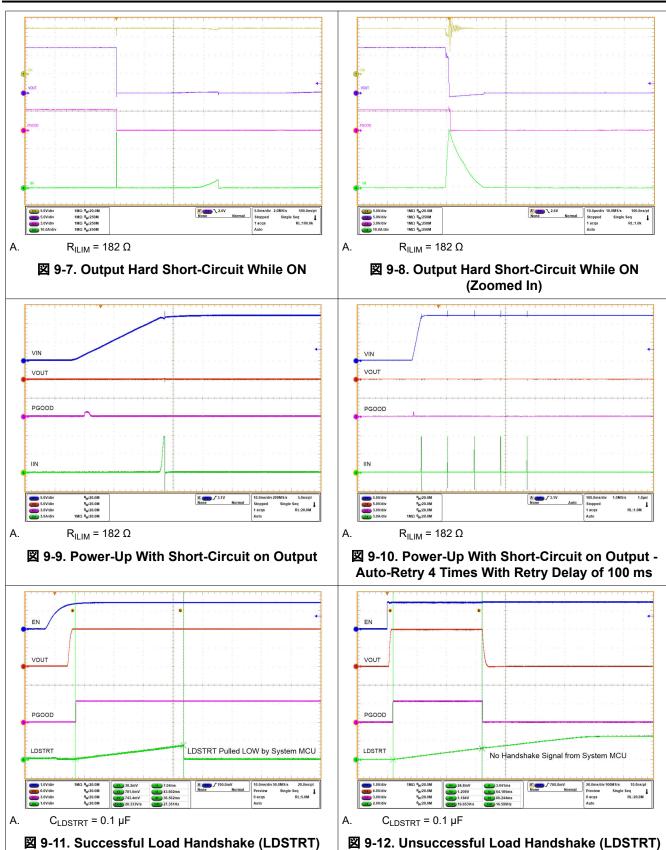

## 8.3.3.3 Short-Circuit Protection

During an output short-circuit event, the current through the device increases very rapidly. When an output shortcircuit is detected, the internal fast-trip comparator turns off the output within the  $t_{SC}$ . The comparator employs a scalable threshold which is equal to  $2.1 \times I_{LIM}$ . This enables the user to adjust the fast-trip threshold as per system needs rather than using a fixed threshold which may not be suitable for all systems. After a fast trip event, the device restarts in a current limited mode to try and restore power to the load quickly in case the fast trip was triggered by a transient event. However, if the fault is persistent, the device will stay in current limit causing the junction temperature to rise and eventually enter thermal shutdown. See *Overtemperature Protection (OTP)* section for details on the device response to overtemperature.

In some of the systems, for example servers or telecom equipment which house multiple hot-pluggable cards connected to a common supply backplane, there can be transients on the supply due to switching of large currents through the inductive backplane. This can result in current spikes on adjacent cards which could be

potentially large enough to inadvertently trigger the fast-trip comparator of the eFuse. The TPS25980x uses a proprietary algorithm to avoid nuisance tripping in such cases thereby facilitating un-interrupted system operation.

図 8-4. Input Line Transient and Output Short-Circuit Response

Note

To prevent the circuit breaker loop from interfering with the input line transient detection logic, TI recommends to set the ITIMER interval higher than 100  $\mu$ s. Refer to  $\cancel{x}$  8-1 for more details on ITIMER.

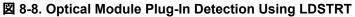

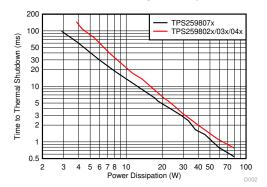

## 8.3.4 Overtemperature Protection (OTP)

The device monitors the internal die temperature  $(T_J)$  at all times and shuts down the part as soon as the temperature exceeds a safe operating level (TSD) thereby protecting the device from damage. The device will not turn back on until the die cools down sufficiently, that is the die temperature falls below (TSD - TSDHys). Thereafter, the part can be configured to either remain latched off or restart automatically. Refer to the *Fault Response* section for details.

## 8.3.5 Analog Load Current Monitor (IMON)

The device allows the system to monitor the output load current accurately by providing an analog current on the IMON pin which is proportional to the current through the FET. The user can connect a resistor from IMON to ground to convert this signal to a voltage which can be fed to the input of an Analog-to-Digital Converter. The internal amplifier on the IMON employs chopper based offset cancellation techniques to provide accurate measurement even at lower currents over time and temperature.

(6)

$$\mathsf{V}_{\mathsf{IMON}}\left(\mathsf{V}\right) = \mathsf{G}_{\mathsf{IMON}}\left(\mu\mathsf{A} \,/\,\mathsf{A}\right) \times \mathsf{I}_{\mathsf{OUT}}\left(\mathsf{A}\right) \times \mathsf{R}_{\mathsf{IMON}}\left(\Omega\right)$$

It is recommended to limit the maximum IMON voltage to the values mentioned in *VIMON(Max) Recommended Values*. This is to ensure the IMON pin internal amplifier has sufficient headroom to operate linearly.

| V <sub>IN</sub> | Recommended V <sub>IMON(MAX)</sub> |

|-----------------|------------------------------------|

| 2.7 V           | 1 V                                |

| 3.3 V           | 1.8 V                              |

| > 5 V           | 3.3 V                              |

表 8-2. VIMON(MAX) Recommended Values

It is recommended to add a RC low pass filter on the IMON output to filter out any glitches and get a smooth average current measurement. TI recommends a series resistance of 10 k $\Omega$  or higher.

## 8.3.6 Power Good (PG)

PG is an active high open drain output which indicates whether the FET is fully turned ON and the output voltage has reached the maximum value. After power-up, PG is pulled low initially. The gate driver circuit starts charging the gate capacitance from the internal charge pump. When the FET gate voltage reaches ( $V_{IN} + 3.6V$ ), PG is asserted after a de-glitch time ( $t_{PGD}$ ). During normal operation, if at any time  $V_{OUT}$  falls below ( $V_{IN} - V_{PGTHD}$ ), PG is de-asserted after a de-glitch time ( $t_{PGD}$ ).

8-5. Power Good Assertion and De-assertion

#### Note

1. When there is no supply to the device, the PG pin is expected to stay low. However, there is no active pull-down in this condition to drive this pin all the way down to 0 V. If the PG pin is pulled up to an independent supply which is present even if the TPS25980x is unpowered, there can be a small voltage seen on this pin depending on the pin sink current, which in turn is a function of the pull-up supply voltage and resistor. Minimize the sink current to keep this pin voltage low enough not to be detected as a logic HIGH by associated external circuits in this condition.

2. The PG pin provides a mechanism to detect a possible failed MOSFET condition during start-up. If the PG does not get asserted for an extended period of time after the device is powered up and enabled, it might be an indication of internal MOSFET failure.

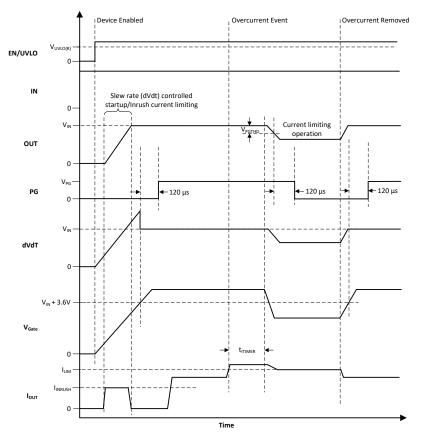

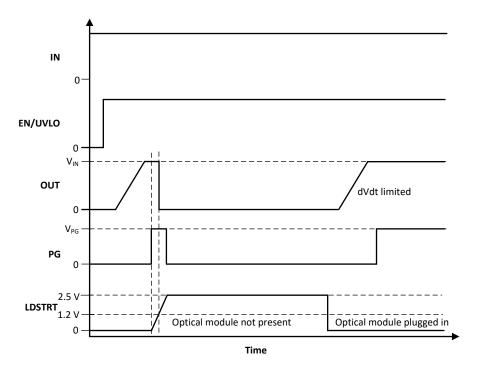

#### 8.3.7 Load Detect/Handshake (LDSTRT)

The LDSTRT pin provides a mechanism for the downstream load circuit to indicate to the TPS25980x that the load is present and has powered up successfully. This allows the system to have additional control over the conditions in which power is presented to the load and disconnect the power when the load is not present or unable to provide a valid handshake signal after an expected boot-up time.

Once the TPS25980x completes the startup sequence and the output reaches the full voltage, it asserts the PG signal. At the same time, it also starts charging the capacitor on the LDSTRT pin ( $C_{LDSTRT}$ ) with an internal current source ( $I_{LDSTRT}$ ). If the LDSTRT pin voltage rises above  $V_{LDSTRT}$  before the load circuit pulls it low, the TPS25980x detects the condition as a LDSTRT fault and turns off the FET to power down the load. The time to trigger the LDSTRT fault can be calculated from the following equation:

$$tLDSTRT (ms) = \frac{CLDSTRT (nF) \times VLDSTRT (V)}{ILDSTRT (\mu A)}$$

(7)

During normal operation, if at any time the load circuit releases the active pull-down on the LDSTRT pin, the capacitor  $C_{LDSTRT}$  would start charging up again and eventually trigger a shutdown due to LDSTRT fault once the capacitor charges up to  $V_{LDSTRT}$ .

Once the TPS25980x turns off due to LDSTRT fault, it can be turned ON again in 3 ways:

- LDSTRT pin is driven low

- Input supply voltage is driven low (< V<sub>UVP(F)</sub>) and then driven high (> V<sub>UVP(R)</sub>)

- EN/UVLO voltage is driven low (< V<sub>SD</sub>) and then driven high (> V<sub>UVLO(R)</sub>)

Tie the LDSTRT pin to ground if this functionality is not needed.

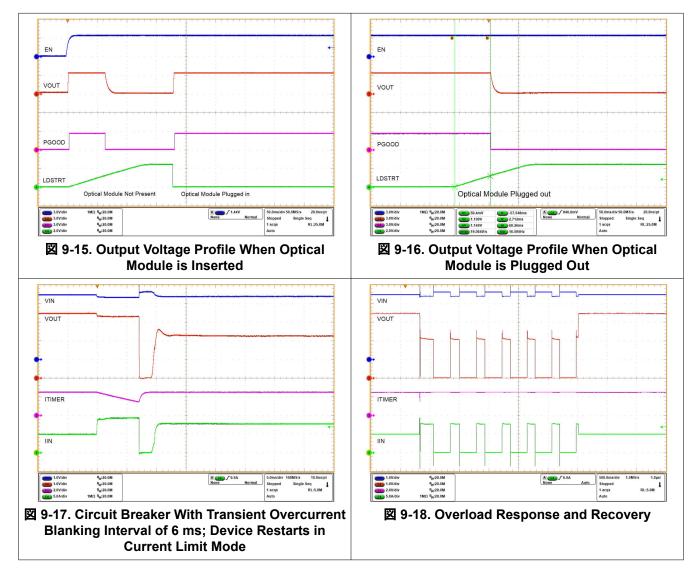

The LDSTRT pin can also be used to implement a load or module detect function wherein the output power is presented only when the load or module is plugged in. A typical use case for this function is on optical module power supply rails in Switches/Routers or similar networking end equipment. The LDSTRT pin should be tied to a corresponding pin on the module connector which gets pulled low by the module when it is plugged in. An example of such a signal is ModPrsL on QSFP-DD modules.

In this scheme, initially when the TPS25980x is powered up or enabled, the output charges up and PG is asserted. If the module is not plugged in, there is no external pull-down on the LDSTRT pin and the pin voltage starts rising due to internal pull-up. Once the LDSTRT pin voltage exceeds  $V_{LDSTRT}$ , the TPS25980x turns off the output power. If the module is plugged in later, the LDSTRT pin is pulled low by the module and the TPS25980x turns on the output power.

## 8.4 Fault Response

The following events trigger an internal fault which causes the device to shut down:

- Overtemperature Protection

- Circuit Breaker Operation

- ITIMER pin Short to GND

- ILIM pin Short to GND

Once the device shuts down due to a fault, even if the associated external fault is subsequently cleared, the fault stays latched internally and the output cannot turn on again until the latch is reset. The fault latch can be externally reset by one of the following methods:

- Input supply voltage is driven low (< V<sub>UVP(F)</sub>)

- EN/UVLO voltage is driven low (< V<sub>SD</sub>)

The fault latch can also be reset by an internal auto-retry logic. The user can either disable the auto-retry behavior completely (latch-off behavior) or configure the device to auto-retry indefinitely or for a limited number of times before latching off. The auto-retry behavior is controlled by the connections on the RETRY\_DLY and NRETRY pins.

| EN/UVLO | RETRY_DLY        | NRETRY           | DEVICE STATE                                                                                 |

|---------|------------------|------------------|----------------------------------------------------------------------------------------------|

| L       | X                | X                | Disabled                                                                                     |

| Н       | Short to GND     | Х                | No auto-retry (Latch-off)                                                                    |

| н       | Open             | Open             | Auto-retry 4 times with minimum delay between retries and then latch-off                     |

| Н       | Open             | Short to GND     | Auto-retry indefinitely with minimum delay between retries                                   |

| Н       | Capacitor to GND | Capacitor to GND | Auto-retry delay and count as per Equation 8 and Equation 9                                  |

| н       | Capacitor to GND | Open             | Auto-retry 4 times with finite delay between retries as per<br>Equation 8 and then latch-off |

| н       | Capacitor to GND | Short to GND     | Auto-retry indefinitely with finite delay between retries as per<br>Equation 8               |

#### 表 8-3. Pin Configurable Fault Response

To configure the part for a finite number of auto-retries with a finite auto-retry delay, first choose the capacitor value on RETRY\_DLY pin using the following equation.

$$\text{tretry_DLY}(\mu s) = \frac{128 \times (\text{Cretry_DLY}(pF) + 4 \text{ pF}) \times \text{Vretry_DLY_HYs}(V)}{\text{Iretry_DLY}(\mu A)}$$

(8)

Next, choose the capacitor value on the NRETRY pin using the following equation.

$$NRETRY = \frac{4 \times IRETRY_DLY (\mu A) \times CNRETRY (pF)}{INRETRY (\mu A) \times (CRETRY_DLY (pF) + 4 pF)}$$

(9)

The number of auto-retries is quantized to certain discrete levels as shown in otar 8-4

ota.

| 2 0-4. NRETRY Quantization Levels |               |  |  |  |  |

|-----------------------------------|---------------|--|--|--|--|

| NRETRY Calculated From Equation 9 | NRETRY Actual |  |  |  |  |

| 0 < N < 4                         | 4             |  |  |  |  |

| 4 < N < 16                        | 16            |  |  |  |  |

| 16 < N < 64                       | 64            |  |  |  |  |

| 64 < N < 256                      | 256           |  |  |  |  |

| 256 < N < 1024                    | 1024          |  |  |  |  |

|                                   |               |  |  |  |  |

# 表 8-4. NRETRY Quantization Levels

| Auto Retry Delay    | 915 ms           | 416 ms  | 91.7 ms      | 9.3 ms | 3 ms   |  |

|---------------------|------------------|---------|--------------|--------|--------|--|

| RETRY_DLY Capacitor | 22 nF            | 10 nF   | 2.2 nF       | 220 pF | 68 pF  |  |

| No. of Auto Retries | NRETRY Capacitor |         |              |        |        |  |

| 4                   |                  |         | Open         |        |        |  |

| 16                  | 47 nF            | 22 nF   | 4.7 nF       | 1 nF   | 220 pF |  |

| 64                  | 0.22 µF          | 0.1 µF  | 22 nF        | 2.2 nF | 1 nF   |  |

| 256                 | 1 µF             | 0.47 µF | 0.1 µF       | 10 nF  | 4.7 nF |  |

| 1024                | 3.3 µF           | 1.5 µF  | 0.47 µF      | 33 nF  | 10 nF  |  |

| Infinite            |                  |         | Short to GND |        | 1      |  |

## 表 8-5. NRETRY and RETRY\_DLY Combination Examples

A spreadsheet design tool TPS25980xx Design Calculator is also available for simplified calculations.

図 8-9. Auto-Retry After Fault

The auto-retry logic has a mechanism to reset the count to zero if two consecutive faults occur far apart in time. This ensures that the auto-retry response to any later fault is handled as a fresh sequence and not as a continuation of the previous fault. If the fault which triggered the shutdown and subsequent auto-retry cycle is cleared eventually and does not occur again for a duration equal to 7 retry delay timer periods starting from the last fault, the auto-retry logic resets the internal auto-retry count to zero.

# 8.5 Device Functional Modes

The TPS25980x can be pin strapped to support various configurable functional modes.

## 表 8-6. LDSTRT Handshake Functional Modes

| EN/UVLO | LDSTRT | DEVICE STATE |

|---------|--------|--------------|

| L       | Х      | Disabled     |

| Н       | L      | ON           |

| Н       | Н      | OFF          |

Refer to Load Detect/Handshake (LDSTRT) section for more details.

| EN/UVLO | RETRY_DLY        | NRETRY           | DEVICE STATE                                                                                 |

|---------|------------------|------------------|----------------------------------------------------------------------------------------------|

| L       | X                | X                | Disabled                                                                                     |

| Н       | Short to GND     | X                | No auto-retry (Latch-off)                                                                    |

| н       | Open             | Open             | Auto-retry 4 times with minimum delay between retries and then latch-off                     |

| Н       | Open             | Short to GND     | Auto-retry indefinitely with minimum delay between retries                                   |

| Н       | Capacitor to GND | Capacitor to GND | Auto-retry delay and count as per Equation 8 and Equation 9                                  |

| н       | Capacitor to GND | Open             | Auto-retry 4 times with finite delay between retries as per<br>Equation 8 and then latch-off |

| н       | Capacitor to GND | Short to GND     | Auto-retry indefinitely with finite delay between retries as per<br>Equation 8               |

Refer to Fault Response section for more details.

# 9 Application and Implementation

#### Note

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

# 9.1 Application Information

The TPS25980x device is an integrated 8-A eFuse that is typically used for hot-swap and power rail protection applications. It operates from 2.7 V to 24 V with adjustable overcurrent and undervoltage protection. It also provides optional overvoltage with various fixed internal thresholds. The device aids in controlling the inrush current and has the flexibility to configure the number of auto-retries and retry delay. The adjustable overcurrent blanking timer provides the functionality to allow transient overcurrent pulses without limiting or tripping. These devices protect source, load and internal MOSFET from potentially damaging events in systems such as PCIe cards, SSDs, HDDs, Optical Modules, Routers, Switches, Industrial PCs, Retail ePOS (Point-of-sale) terminals and Patient Monitoring Systems.

The following design procedure can be used to select the supporting component values based on the application requirement. Additionally, a spreadsheet design tool *TPS25980xx Design Calculator* is available in the web product folder.

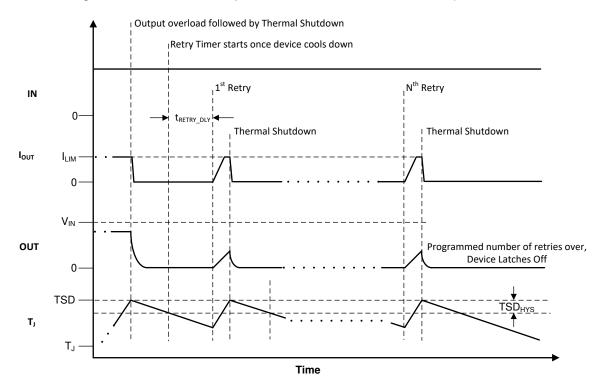

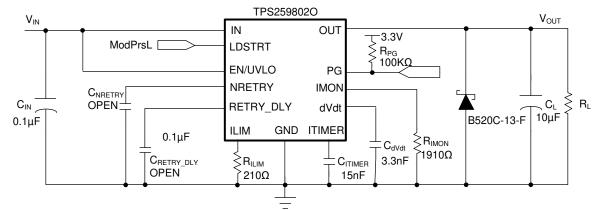

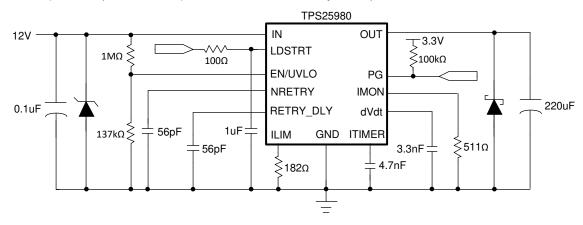

## 9.2 Typical Application: Patient Monitoring System in Medical Applications

#### 図 9-1. Typical Application Schematic - Input Protection for Patient Monitoring System

#### 9.2.1 Design Requirements

$\frac{1}{5}$  9-1 shows the design parameters for this application example.

表 9-1. Design Parameters

| <b>P</b> ( • · · · <b>P</b> • • · · · · · · · · · · · · · · · · · |               |  |  |

|-------------------------------------------------------------------|---------------|--|--|

| DESIGN PARAMETER                                                  | EXAMPLE VALUE |  |  |

| Input voltage, V <sub>IN</sub>                                    | 12 V          |  |  |

| Undervoltage lockout set point, VIN <sub>UVLO</sub>               | 10.8 V        |  |  |

| Maximum load current, I <sub>OUT</sub>                            | 6.5 A         |  |  |

| Current limit, I <sub>LIM</sub>                                   | 8 A           |  |  |

| Transient overcurrent blanking interval (t <sub>ITIMER</sub> )    | 2 ms          |  |  |

| Load capacitance, C <sub>OUT</sub>                                | 1.4 mF        |  |  |

| Load at start-up, R <sub>L(SU)</sub>                              | 10 Ω          |  |  |

| Output voltage ramp time, T <sub>dVdt</sub>                       | 20 ms         |  |  |

| Maximum ambient temperature, T <sub>A</sub>                       | 70 °C         |  |  |

| · · · · ·                                                         |               |  |  |

| 表 9-1. Design Para | meters (continued) |

|--------------------|--------------------|

|                    |                    |

| DESIGN PARAMETER                    | EXAMPLE VALUE |

|-------------------------------------|---------------|

| Retry delay, t <sub>RETRY_DLY</sub> | 100 ms        |

| No. of retries, N <sub>RETRY</sub>  | 4             |

## 9.2.2 Detailed Design Procedure

## 9.2.2.1 Device Selection

This design example considers a 12-V system operating voltage with a tolerance of  $\pm 10$  %. The rated load current is 6.5 A. If the current exceeds 8 A, then the device must allow overload current for 2-ms interval before breaking the circuit and then restart. Accordingly, the TPS259804O variant is chosen. (Refer to *Device Comparison Table* for device options.) Ambient temperatures may range from 20 °C to 70 °C. The load has a minimum input capacitance of 1.4 mF and start-up resistive load of 10  $\Omega$ . The downstream load is turned on only after the PG signal is asserted.

## 9.2.2.2 Setting the Current Limit Threshold: R<sub>ILIM</sub> Selection

The R<sub>ILIM</sub> resistor at the ILIM pin sets the overload current limit, whose value can be calculated using Equation 10.

$$\mathsf{RiLIM}(\Omega) = \frac{1460}{\mathsf{ILIM}(\mathsf{A}) - 0.11} \tag{10}$$

For  $I_{LIM} = 8 \text{ A}$ ,  $R_{ILIM}$  value is calculated to be 185.04  $\Omega$ . Choose the closest available standard value: 182  $\Omega$ , 1%. Refering to the Electrical Characteristics table, it can be verified that the minimum current limit across temperature for  $R_{ILIM}$  value of 182  $\Omega$  is 7.23 A, which is higher than the nominal rated load current (6.5 A), thereby ensuring stable operation under normal conditions.

## 9.2.2.3 Setting the Undervoltage Lockout Set Point

The undervoltage lockout (UVLO) trip point is adjusted using the external voltage divider network of  $R_{VL1}$  and  $R_{VL2}$  connected between IN, EN/UVLO and GND pins of the device. The resistor values required for setting the undervoltage are calculated using Equation 11.

$$VINUVLO = \frac{VUVLO(R) \times (RVL1 + RVL2)}{RVL2}$$

(11)

For minimizing the input current drawn from the power supply, TI recommends to use higher values of resistance for  $R_{VL1}$  and  $R_{VL2}$ . However, leakage currents due to external active components connected to the resistor string can add error to these calculations. So, the resistor string current,  $I_{RVL12}$  must be 20 times greater than the leakage current ( $I_{ENLKG}$ ).

From the device electrical specifications, UVLO rising threshold  $V_{UVLO(R)}$  = 1.2 V. From design requirements, VIN<sub>UVLO</sub> = 10.8 V. First choose the value of R<sub>VL1</sub> = 1 M $\Omega$  and use Equation 11 to calculate R<sub>VL2</sub> = 125 k $\Omega$ .

Use the closest standard 1% resistor values:  $R_{VL1}$  = 1 MΩ, and  $R_{VL2}$  = 125 kΩ

# 9.2.2.4 Choosing the Current Monitoring Resistor: R<sub>IMON</sub>

Voltage at IMON pin  $V_{IMON}$  is proportional to the output load current. This can be connected to an ADC of the downstream system for monitoring the operating condition and health of the system. The R<sub>IMON</sub> must be selected based on the maximum load current and the maximum IMON pin voltage at full-scale load current. The maximum IMON pin voltage must be selected based on the input voltage range of the ADC used or the value suggested in *VIMON(Max) Recommended Values*, whichever is lower. R<sub>IMON</sub> is set using Equation 12.

(12)

$$\mathsf{R}_{\mathsf{IMON}}(\Omega) = \frac{\mathsf{V}_{\mathsf{IMON}}(\mathsf{M})}{\mathsf{I}_{\mathsf{OUTmax}}(\mathsf{A}) \times 246 \times 10^{-6}}$$

For I<sub>LIM</sub> = 8 A and considering the operating range of ADC to be 0 V to 3.3 V, R<sub>IMON</sub> can be calculated as

$$\mathsf{R}_{\mathsf{IMON}} = \frac{3.3}{8 \times 243 \times 10^{-6}} = 1697 \,\Omega \tag{13}$$

Selecting  $R_{IMON}$  value less than shown in Equation 13 ensures that ADC limits are not exceeded for maximum value of load current. Choose closest available standard value: 1620  $\Omega$ , 1 %.

## 9.2.2.5 Setting the Output Voltage Ramp Time (T<sub>dVdt</sub>)

For a successful design, the junction temperature of device must be kept below the absolute maximum rating during both dynamic (start-up) and steady state conditions. Dynamic power stresses often are an order of magnitude greater than the static stresses, so it is important to determine the right start-up time and in-rush current limit required with system capacitance to avoid thermal shutdown during start-up with and without load.

The required ramp-up capacitor  $C_{dVdt}$  is calculated considering the two possible cases (see *Case 1: Start-Up Without Load: Only Output Capacitance*  $C_{OUT}$  *Draws Current* and *Case 2: Start-Up With Load:Output Capacitance*  $C_{OUT}$  *and Load Draw Current*)