🕳 Order

Now

#### **TPS40425**

参考資料

JAJSGE0C - JANUARY 2014 - REVISED OCTOBER 2018

# TPS40425 デュアル出力、2相、スタック可能PMBus™同期整流降圧ドラ イバレス・コントローラ、適応型電圧スケーリング(AVS)バス付き

Technical

Documents

### 1 特長

- 出荷時デフォルトは非スマート電力モード

- TPS40428とピン互換 出荷時デフォルトはス マート電力モード

- 4.5V~20Vの単一電源で動作

- 最低0.6VのV<sub>OUT</sub>

- デュアルまたは多相の同期整流降圧コントローラ

- 個別の高速AVSインターフェイス (0.5V~1.5Vの範囲)

- 高速な過渡応答

- 最大4相にスタック可能

- 2、3、4相のインターリーブ位相シフト

- 正確なカレント・シェア(電流共有)

- PMBus™インターフェイス機能

- 2mV刻みのマージン・アップまたはダウン

- フォルト制限および応答をプログラム可能

- ±0.8% V<sub>OUT</sub>

- 高精度の電流監視

- x3904による±4.5°Cの外部温度監視

- UVLOオン/オフのスレッショルドをプログラム可能

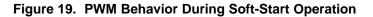

- ソフトスタート時間、ターンオン遅延、ターンオフ遅 延をプログラム可能

- オンチップのNVM (不揮発性メモリ) にカスタ ム構成を保存

- -40°C~125°Cの範囲で0.5%精度の0.6V基準電圧

- インダクタDCR電流センシング

- f<sub>SW</sub>を200kHz~1.5MHzの範囲でプログラム可能

- プリバイアス出力をサポート

- 差動リモート・センシング

- 外部クロックに同期可能

- OC/OV/UV/OTフォルト保護

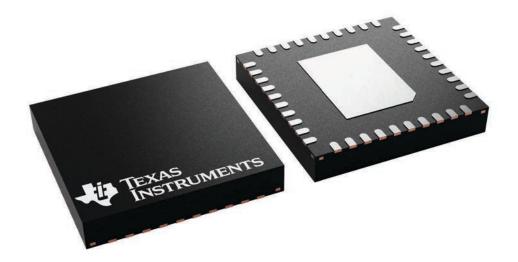

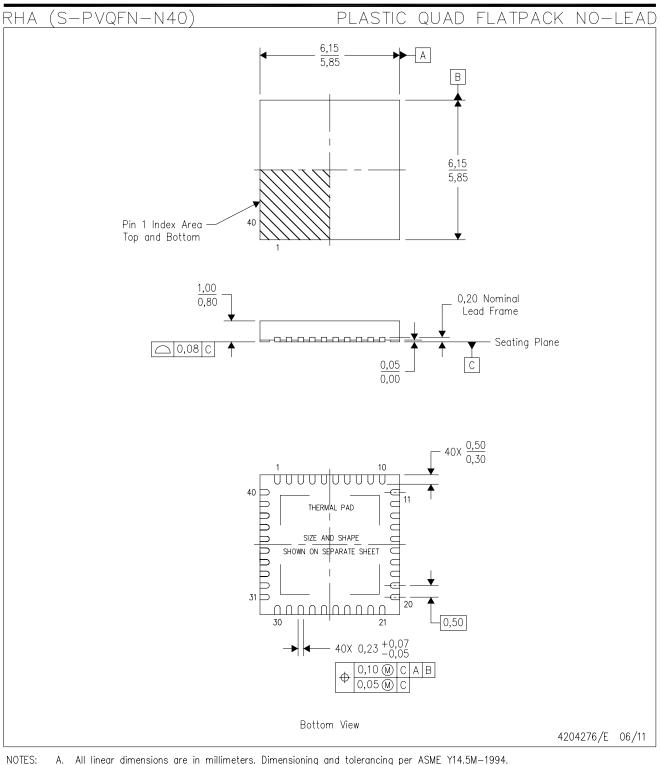

- 40ピン、6mm×6mmのQFNパッケージ

- TI電力段のサポート

- 2 アプリケーション

- ワイヤレス・インフラストラクチャ

- スイッチャ/ルータ・ネットワーク/サーバー/スト レージ

## 3 概要

🥭 Tools &

Software

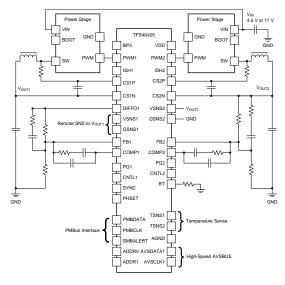

TPS40425はPMBus、同期降圧、ドライバレスのコント ローラです。出荷時のデフォルト設定では非スマート電力 モードで動作し、PMBusのプログラミングと電源再起動の 後でスマート電力モードにより動作できます。デュアル出 力または2相として構成可能です。また、最大4相までス タックでき、最大で120Aの負荷電流をサポートできます。 2、3、4相のインターリーブ位相シフトにより、入力および 出力のリップルが減少し、入力と出力の静電容量も減少し ます。

Support &

Community

22

入力電圧範囲が広いため、5Vと12Vの中間電源バスをサ ポートできます。0.5%の基準電圧は、今日のASICにおけ る高精度電圧の要求を満たしています。

TPS40425デバイスは、PMBus規格を使用して基準電 圧、フォルト制限値、UVLOスレッショルド、ソフトスタート時 間、およびターンオン/ターンオフ遅延をプログラムできま す。

さらに、このデバイスには高精度の測定システムが実装されており、各チャネルの出力電圧、電流、温度を監視できます。

製品情報

|          | 42 HH IN TH |               |

|----------|-------------|---------------|

| 型番       | パッケージ       | 本体サイズ(公称)     |

| TPS40425 | VQFN(40)    | 6.00mm×6.00mm |

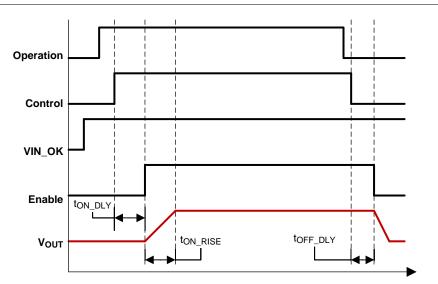

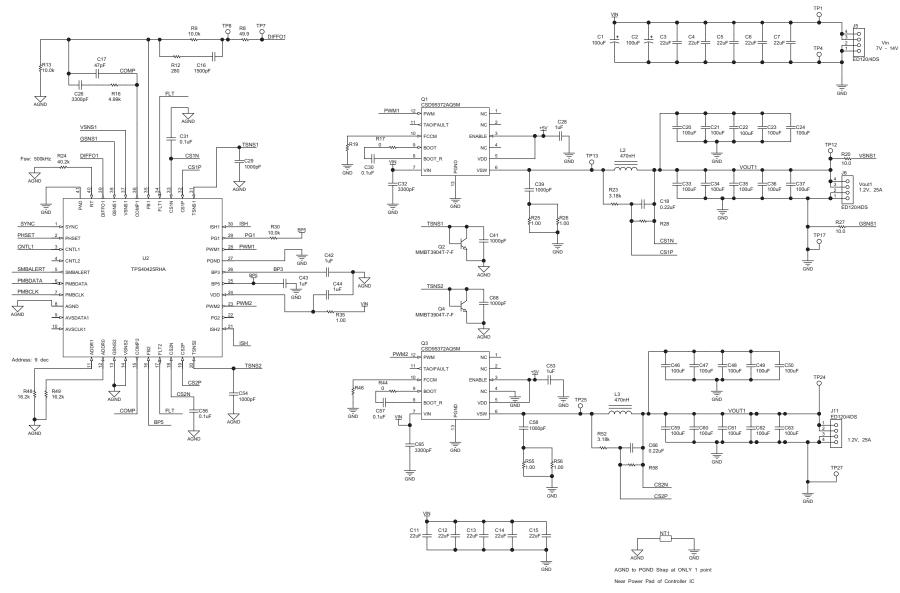

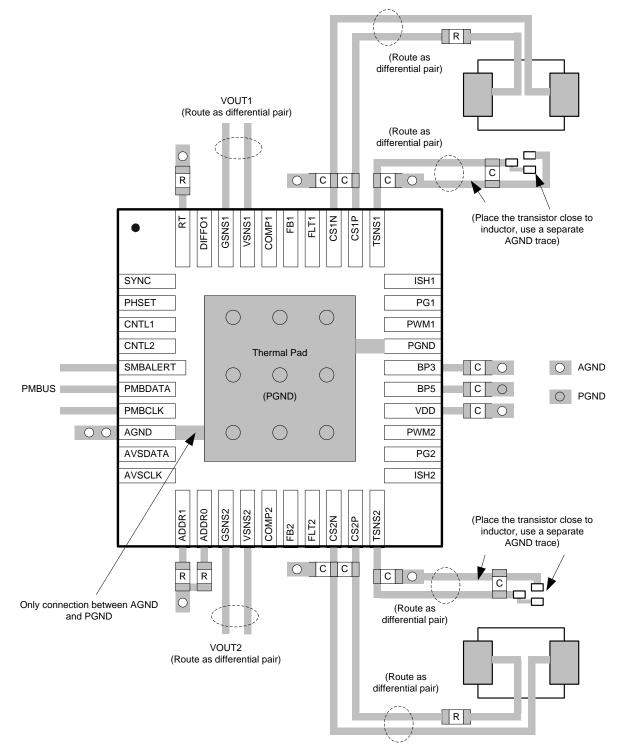

### 図 1. アプリケーション概略図 (デュアル出力)

Page

Page

# 目次

| 1 | 特長   |                                    |

|---|------|------------------------------------|

| 2 | アプ   | リケーション1                            |

| 3 | 概要   | I1                                 |

| 4 | 改訂   | '履歴2                               |

| 5 | Pin  | Configuration and Functions 4      |

| 6 | Spe  | cifications5                       |

|   | 6.1  | Absolute Maximum Ratings 5         |

|   | 6.2  | Handling Ratings6                  |

|   | 6.3  | Recommended Operating Conditions 6 |

|   | 6.4  | Thermal Information 6              |

|   | 6.5  | Electrical Characteristics 6       |

|   | 6.6  | Typical Characteristics 11         |

| 7 | Deta | ailed Description 13               |

|   | 7.1  | Overview 13                        |

|   | 7.2  | Functional Block Diagram 14        |

|   | 7.3  | Feature Description 15             |

|   | 7.4  | Device Functional Modes25          |

|   | 1.4  |                                    |

|    | 7.5  | Programming                  | 25 |

|----|------|------------------------------|----|

|    | 7.6  | Register Maps                | 30 |

|    | 7.7  | Supported PMBus Commands     | 33 |

| 8  | Арр  | lications and Implementation | 72 |

|    | 8.1  | Application Information      | 72 |

|    | 8.2  | Typical Application          | 72 |

| 9  | Pow  | ver Supply Recommendations   | 81 |

| 10 | Lay  | out                          | 82 |

|    | 10.1 | Layout Guidelines            | 82 |

|    | 10.2 | Layout Example               | 83 |

| 11 | デバ   | バイスおよびドキュメントのサポート            | 84 |

|    | 11.1 | デバイス・サポート                    | 84 |

|    | 11.2 | 商標                           | 85 |

|    | 11.3 | 静電気放電に関する注意事項                | 85 |

|    | 11.4 | Glossary                     | 85 |

| 12 | メカ   | ニカル、パッケージ、および注文情報            | 86 |

|    |      |                              |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Re | evision B (December 2016) から Revision C に変更                                                  | Page |

|----|----------------------------------------------------------------------------------------------|------|

| •  | Added PWM Behavior During Soft-start Operation section                                       | 22   |

| •  | Added information regarding TPS40425 and TPS28226 compatibility in <i>PWM Signal</i> section | 22   |

|    |                                                                                              |      |

## Revision A (July 2014) から Revision B に変更

| • | 「 <del>特長</del> 」セクションでTPS28226デバイスへの参照を削除1                                           |

|---|---------------------------------------------------------------------------------------|

| • | Added note regarding TPS40425 and TPS28226 compatibility in <i>PWM Signal</i> section |

### 2014年1月発行のものから更新

| • | 新しい標準に合わせてデータシートのフォーマットを更新                                                               | 1   |

|---|------------------------------------------------------------------------------------------|-----|

| • | Updated Pin Functions table.                                                             | . 4 |

| • | Rearranged Specifications section                                                        | 5   |

| • | Updated notes and conditions in Electrical Characteristics. No updates to specifications | 6   |

| • | Updated V <sub>OH</sub> and V <sub>OL</sub> parameters for PWM                           | 7   |

| • | Updated I <sub>OC</sub> accuracy parameter for current limit                             | 8   |

| • | Undated Detailed Description section                                                     | 13  |

| • | Updated Figure 21                                                                        | 26  |

| • | Added clarity to Table 4                                                                 | 27  |

| • | Added clarity to Table 5                                                                 | 28  |

| • | Added clarity to Table 6                                                                 | 30  |

| • | Updated MFR_SPECIFIC_16 (COMM_EEPROM_SPARE) (E0h)                                        | 62  |

| • | Updated Applications and Implementation section                                          | 72  |

| • | Updated Figure 22                                                                        | 73  |

| • | Changed 15 V to 14 V in Equation 11 and Equation 12                                      |     |

| • | Added Power Supply Recommendations section                                               | 81  |

|   |                                                                                          |     |

|  | • | ed Layout Guidelines section |  | 82 |

|--|---|------------------------------|--|----|

|--|---|------------------------------|--|----|

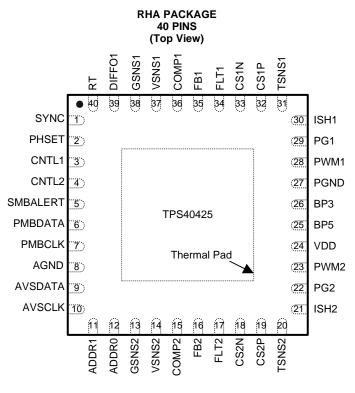

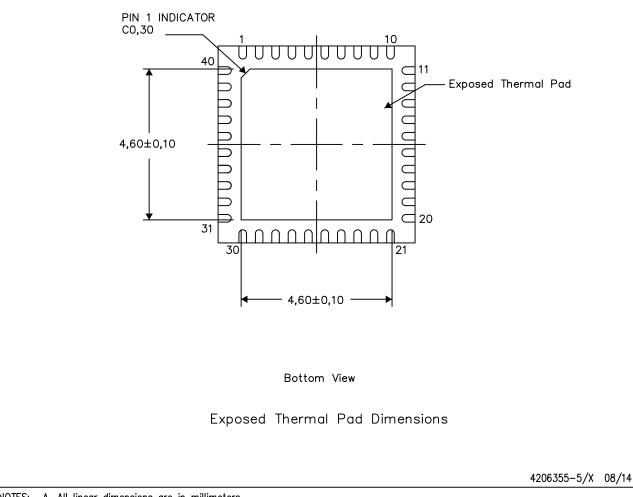

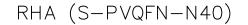

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN     |     | I/O <sup>(1)</sup> | DECODIDION                                                                                                                                                                                                           |  |  |

|---------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO. | 1/0(*)             | DESCRIPTION                                                                                                                                                                                                          |  |  |

| ADDR1   | 11  | I                  | High order address pin for PMBus device. Connect a resistor to AGND (see Table 3).                                                                                                                                   |  |  |

| ADDR0   | 12  | I                  | ow order address pin for PMBus device. Connect a resistor to AGND (see Table 3).                                                                                                                                     |  |  |

| AGND    | 8   | —                  | nalog ground pin, used for analog signal. Connect to thermal pad directly.                                                                                                                                           |  |  |

| AVSCLK  | 10  | Ι                  | AVS clock                                                                                                                                                                                                            |  |  |

| AVSDATA | 9   | Ι                  | AVS data                                                                                                                                                                                                             |  |  |

| BP3     | 26  | 0                  | .3-V bias power for logic. A low ESR ceramic capacitor with a value of 0.33 $\mu$ F or greater should be onnected closely from this pin or to AGND. The maximum suggested capacitor value is 10 $\mu$ F.             |  |  |

| BP5     | 25  | 0                  | put bypass for the internal regulator. A low ESR ceramic capacitor of 1 $\mu$ F or greater should be nected closely from this pin to PGND pin. The maximum suggested capacitor value is 10 $\mu$ F.                  |  |  |

| CNTL1   | 3   | I                  | gic level input which starts or stops channel 1. An internal 6- $\mu$ A current source pulls V <sub>CNTL1</sub> up to V <sub>BP5</sub> nen the pin is floating.                                                      |  |  |

| CNTL2   | 4   | I                  | ogic level input which starts or stops channel 2. An internal 6- $\mu$ A current source pulls V <sub>CNTL2</sub> up to V <sub>BP5</sub> //hen the pin is floating.                                                   |  |  |

| COMP1   | 36  | 0                  | Dutput of the error amplifier 1 and connection node for loop feedback components                                                                                                                                     |  |  |

| COMP2   | 15  | 0                  | Dutput of the error amplifier 2 and connection node for loop feedback components                                                                                                                                     |  |  |

| CS1N    | 33  | I                  | Negative pin of current sense amplifier for channel 1. An internal, 4-k $\Omega$ resistor pulls CS1N to 1.24 V during smart power mode operation to provide a bias voltage required by the smart power stage device. |  |  |

| CS1P    | 32  | I                  | Positive pin of current sense amplifier for channel 1                                                                                                                                                                |  |  |

| CS2N    | 18  | I                  | Negative pin of current sense amplifier for channel 2. An internal, 4-k $\Omega$ resistor pulls CS2N to 1.24 V during smart power mode operation to provide a bias voltage required by the smart power stage device. |  |  |

| CS2P    | 19  | I                  | Positive pin of current sense amplifier for channel 2                                                                                                                                                                |  |  |

| DIFFO1  | 39  | 0                  | Remote Sense Amplifier Output for channel 1                                                                                                                                                                          |  |  |

| FB1     | 35  | I                  | Inverting input to the error amplifier 1. In normal operation, the voltage on this pin is equal to the internal reference voltage. Connect to BP5 to set the channel as slave channel.                               |  |  |

(1) I = input, O = output, P = power, I/O = bi-directional

### **Pin Functions (continued)**

| PIN      |     | 1/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                          |  |  |  |

|----------|-----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | NO. | 100                | DESCRIPTION                                                                                                                                                                                                                                                          |  |  |  |

| FB2      | 16  | I                  | erting input to the error amplifier 2. In normal operation, the voltage on this pin is equal to the internal<br>erence voltage. Connect to BP5 to set the channel as slave channel.                                                                                  |  |  |  |

| FLT1     | 34  | I/O                | Fault signal of channel 1. An internal 100-k $\Omega$ resistor pulls FLT1 to BP3.                                                                                                                                                                                    |  |  |  |

| FLT2     | 17  | I/O                | ult signal of channel 2. An internal 100-k $\Omega$ resistor pulls FLT2 to BP3.                                                                                                                                                                                      |  |  |  |

| GSNS1    | 38  | I                  | Negative pin of Voltage Sense Signal for channel 1                                                                                                                                                                                                                   |  |  |  |

| GSNS2    | 13  | I                  | Negative pin of Voltage Sense Signal for channel 2                                                                                                                                                                                                                   |  |  |  |

| ISH1     | 30  | I                  | Current sharing signal of channel 1 for multi-phase mode                                                                                                                                                                                                             |  |  |  |

| ISH2     | 21  | Ι                  | ent sharing signal of channel 2 for multi-phase mode                                                                                                                                                                                                                 |  |  |  |

| PG1      | 29  | 0                  | drain power good indicator for channel 1 output voltage. This pin is pulled to ground internally in slave el.                                                                                                                                                        |  |  |  |

| PG2      | 22  | 0                  | drain power good indicator for channel 2 output voltage. This pin is pulled to ground internally in slave nel.                                                                                                                                                       |  |  |  |

| PGND     | 27  | —                  | wer GND, used for BP5 bypass capacitor. Connect to thermal pad directly.                                                                                                                                                                                             |  |  |  |

| PHSET    | 2   | I/O                | Phase set for multiphase mode                                                                                                                                                                                                                                        |  |  |  |

| PMBCLK   | 7   | Ι                  | PMBus clock pin                                                                                                                                                                                                                                                      |  |  |  |

| PMBDATA  | 6   | I/O                | MBus data pin                                                                                                                                                                                                                                                        |  |  |  |

| PWM1     | 28  | 0                  | WM signal for channel 1                                                                                                                                                                                                                                              |  |  |  |

| PWM2     | 23  | 0                  | WM signal for channel 2                                                                                                                                                                                                                                              |  |  |  |

| RT       | 40  | I                  | onnecting a resistor from this pin to AGND sets the oscillator frequency                                                                                                                                                                                             |  |  |  |

| SMBALERT | 5   | 0                  | PMBus alert pin.                                                                                                                                                                                                                                                     |  |  |  |

| SYNC     |     |                    | This is the synchronization pin for use with the external clock. The frequency of external SYNC signal must be 4 times of desired switching frequency during 1-, 2-, or 4- phases, and must be 3 times the desired switching frequency during 3-phase configuration. |  |  |  |

| TSNS1    | 31  | Ι                  | xternal temperature sense signal input for channel 1                                                                                                                                                                                                                 |  |  |  |

| TSNS2    | 20  | I                  | External temperature sense signal input for channel 2                                                                                                                                                                                                                |  |  |  |

| VDD      | 24  | I                  | Power input to the controller. A low ESR ceramic capacitor with a value of $1-\mu F$ or greater should be connected closely from this pin to AGND.                                                                                                                   |  |  |  |

| VSNS1    | 37  | Ι                  | Positive pin of voltage sense signal for channel 1                                                                                                                                                                                                                   |  |  |  |

| VSNS2    | 14  | I                  | Positive pin of voltage sense signal for channel 2                                                                                                                                                                                                                   |  |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                        |                                                                                                        | MIN  | MAX | UNIT |  |

|------------------------|--------------------------------------------------------------------------------------------------------|------|-----|------|--|

|                        | VDD                                                                                                    | -0.3 | 22  |      |  |

| Input voltage range    | CS1N, CS1P, CS2N, CS2P, GSNS1, GSNS2, ISH1, ISH2, PHSET, PMBDATA, PMBCLK, SMBALERT, SYNC, VSNS1, VSNS2 | -0.3 | 5.5 | V    |  |

|                        | AVSDATA, AVSCLK, TSNS1, TSNS2                                                                          | -0.3 | 3.6 |      |  |

|                        | CNTL1, CNTL2, FB1, FB2                                                                                 | -0.3 | 7   |      |  |

|                        | ADDR0, ADDR1, RT, BP3                                                                                  | -0.3 | 3.6 | V    |  |

| Output voltage range   | BP5, COMP1, COMP2, DIFFO1, FLT1, FLT2, PG1, PG2, PWM1, PWM2                                            | -0.3 | 7   | V    |  |

| Operating junction tem | perature, T <sub>J</sub>                                                                               | -40  | 150 | °C   |  |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 Handling Ratings

|                                           |                         |                                                                                          | MIN | MAX  | UNIT |

|-------------------------------------------|-------------------------|------------------------------------------------------------------------------------------|-----|------|------|

| T <sub>stg</sub> Storage temperature rang |                         |                                                                                          | -55 | 155  | °C   |

| M                                         | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins $^{(1)}$                    | 1   | 2000 | N/   |

| V <sub>(ESD)</sub>                        |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> |     | 1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                | MIN | MAX | UNIT |

|-----------------|--------------------------------|-----|-----|------|

| V <sub>DD</sub> | Input operating voltage        | 4.5 | 20  | V    |

| TJ              | Operating junction temperature | -40 | 125 | °C   |

### 6.4 Thermal Information

|                     | THERMAL METRIC <sup>(1)</sup>                |      | UNIT  |

|---------------------|----------------------------------------------|------|-------|

|                     |                                              |      | UNIT  |

| $R_{	hetaJA}$       | Junction-to-ambient thermal resistance       | 27.8 |       |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 17.2 |       |

| $\theta_{JB}$       | Junction-to-board thermal resistance         | 4.8  | °C/W  |

| $R_{\psi JT}$       | Junction-to-top characterization parameter   | 0.2  | °C/vv |

| $R_{\psi JB}$       | Junction-to-board characterization parameter | 4.8  |       |

| $R_{\thetaJCbot}$   | Junction-to-case (bottom) thermal resistance | 1.2  |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

$T_J = -40^{\circ}$ C to 125°C,  $V_{IN} = V_{VDD} = 12$  V, RT set for 500 kHz, all parameters at zero power dissipation (unless otherwise noted)

|                        | PARAMETER                               | TEST CONDITIONS                                 | MIN  | TYP  | MAX   | UNIT |

|------------------------|-----------------------------------------|-------------------------------------------------|------|------|-------|------|

| INPUT SUPP             | LY                                      |                                                 |      |      |       |      |

| V <sub>VDD</sub>       | Input supply voltage range              |                                                 | 4.5  |      | 20    | V    |

| IVDD                   | Input operating current                 | Switching, no driver load, non-smart power mode |      | 18.4 |       | mA   |

|                        |                                         | Not switching, non-smart power mode             |      | 17.2 |       |      |

| UVLO                   |                                         |                                                 |      |      |       |      |

| V <sub>IN(on)</sub>    | Input turn-on voltage <sup>(1)</sup>    | Default settings                                | 4    | 4.25 | 4.5   | V    |

| V <sub>IN(off)</sub>   | Input turn-off voltage <sup>(1)</sup>   | Default settings                                | 3.8  | 4    | 4.2   | V    |

| V <sub>INON(rng)</sub> | Programmable range for turn on voltage  |                                                 | 4.25 |      | 16    | V    |

| VINOFF(rng)            | Programmable range for turn off voltage |                                                 | 4    |      | 15.75 | V    |

| ERROR AMP              | LIFIER                                  |                                                 |      |      |       |      |

| V <sub>FB</sub>        | Feedback pin voltage                    | $-40^{\circ}C \le T_{J} \le 125^{\circ}C$       | 597  | 600  | 603   | mV   |

| A <sub>OL</sub>        | Open-loop gain <sup>(2)</sup>           |                                                 | 80   |      |       | dB   |

| G <sub>BWP</sub>       | Gain bandwidth product <sup>(2)</sup>   |                                                 | 50   |      |       | MHz  |

| I <sub>FB</sub>        | FB pin bias current (out of pin)        | V <sub>FB</sub> = 0.6 V                         |      |      | 100   | nA   |

|                        | Sourcing                                | $V_{FB} = 0 V$                                  | 1    |      |       |      |

| COMP                   | Sinking                                 | V <sub>FB</sub> = 1 V                           | 1    |      |       | mA   |

(1) Hysteresis of at least 150 mV is specified by design.

(2) Specified by design. Not production tested.

### **Electrical Characteristics (continued)**

$T_J = -40^{\circ}$ C to 125°C,  $V_{IN} = V_{VDD} = 12$  V, RT set for 500 kHz, all parameters at zero power dissipation (unless otherwise noted)

|                          | PARAMETER                                                                        | TEST CONDITIONS                                                            | MIN  | TYP                  | MAX  | UNIT |

|--------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|----------------------|------|------|

| BP5 REGULA               | TOR                                                                              |                                                                            | I.   |                      |      |      |

|                          | Output voltage                                                                   | I <sub>BP5</sub> = 10 mA                                                   | 4.5  | 5                    | 5.5  | V    |

| V <sub>BP5</sub>         | Dropout voltage                                                                  | $V_{VIN} - V_{BP5}, V_{VDD} = 4.5 \text{ V},$<br>$I_{BP5} = 25 \text{ mA}$ |      |                      | 400  | mV   |

| I <sub>BP5</sub>         | Output current                                                                   | V <sub>VDD</sub> = 12 V                                                    | 40   |                      |      | mA   |

| V <sub>BP5UV</sub>       | Regulator UVLO voltage <sup>(2)</sup>                                            |                                                                            | 3.3  | 3.55                 | 3.8  | V    |

| V <sub>BP5UV(hyst)</sub> | Regulator UVLO voltage hysteresis <sup>(2)</sup>                                 |                                                                            |      | 300                  |      | mV   |

| BP3 REGULA               | TOR                                                                              |                                                                            | L.   |                      |      |      |

| V <sub>BP3</sub>         | Output voltage                                                                   | V <sub>VDD</sub> = 4.5 V, I <sub>BP3</sub> ≤ 5 mA                          | 3.1  | 3.3                  | 3.5  | V    |

| OSCILLATOR               | R AND RAMP GENERATOR                                                             |                                                                            |      |                      |      |      |

|                          | Adjustment range <sup>(2)</sup>                                                  |                                                                            | 200  |                      | 1500 | kHz  |

|                          | Switching frequency <sup>(3)</sup>                                               | R <sub>RT</sub> = 100 kΩ                                                   | 180  | 200                  | 220  |      |

| fsw                      | Switching frequency <sup>(3)</sup>                                               | $R_{RT} = 40 \text{ k}\Omega$                                              | 450  | 500                  | 550  | kHz  |

|                          | Switching frequency <sup>(3)</sup>                                               | R <sub>RT</sub> = 13 kΩ                                                    | 1230 | 1370                 | 1500 |      |

| V <sub>RAMP</sub>        | Ramp amplitude (peak-to-peak)                                                    |                                                                            |      | V <sub>VDD</sub> /10 |      | V    |

| V <sub>VAL</sub>         | Valley voltage                                                                   |                                                                            |      | 1.22                 |      | V    |

| SYNCHRONI                |                                                                                  |                                                                            |      |                      |      |      |

| V <sub>SYNCH</sub>       | SYNC high-level threshold <sup>(4)</sup>                                         |                                                                            | 2    |                      |      | V    |

| V <sub>SYNCL</sub>       | SYNC low-level threshold <sup>(4)</sup>                                          |                                                                            |      |                      | 0.8  | V    |

| t <sub>SYNC</sub>        | Minimum SYNC pulse width <sup>(2)</sup>                                          |                                                                            |      |                      | 100  | ns   |

| 01110                    | Maximum PWM frequency for SYNC <sup>(2)</sup>                                    |                                                                            | 1500 |                      |      |      |

|                          | Minimum PWM frequency for SYNC <sup>(2)</sup>                                    |                                                                            |      |                      | 200  | kHz  |

| fsync                    | SYNC frequency range (increase from nominal oscillator frequency) <sup>(2)</sup> |                                                                            | -20% |                      | 20%  |      |

| PWM                      |                                                                                  |                                                                            | l.   |                      |      |      |

| V <sub>OH(pwm)</sub>     | PWM high-level output voltage                                                    | I <sub>LOAD</sub> = 500 μA                                                 | 4.5  |                      |      | V    |

| V <sub>OL(pwm)</sub>     | PWM low-level output voltage                                                     | $I_{LOAD} = 500 \mu\text{A}$                                               |      |                      | 0.5  | V    |

| t <sub>OFF(min)</sub>    | Minimum off-time                                                                 |                                                                            |      | 100                  |      | ns   |

| t <sub>ON(min)</sub>     | Minimum pulse                                                                    |                                                                            |      | 90                   |      | ns   |

| SOFT-START               | · · ·                                                                            |                                                                            | I    |                      |      |      |

|                          | Soft-start time <sup>(5)</sup>                                                   | Factory default settings                                                   |      | 2.7                  |      | ms   |

| t <sub>SS</sub>          | Programmable range <sup>(2)</sup>                                                |                                                                            | 0.6  |                      | 9    | ms   |

|                          | Accuracy over range <sup>(2)</sup>                                               |                                                                            | -15% |                      | 15%  |      |

| t <sub>ON(dly)</sub>     | Turn-on delay time <sup>(2)</sup>                                                | Factory default settings                                                   |      | 0                    |      | ms   |

| t <sub>OFF(dly)</sub>    | Turn-off delay time <sup>(2)</sup>                                               | Factory default settings                                                   |      | 0                    |      | ms   |

|                          | NSE AMPLIFIER                                                                    |                                                                            |      |                      |      |      |

| BW                       | Closed-loop bandwidth <sup>(2)</sup>                                             |                                                                            | 2    |                      |      | MHz  |

| V <sub>DIFFO(max)</sub>  | Maximum DIFFO output voltage                                                     |                                                                            |      |                      | 4.7  | V    |

| S. TO(max)               | Error voltage from DIFFO1 to (V <sub>SNS1</sub> -                                | (V <sub>SNS1</sub> -G <sub>SNS1</sub> ) = 1.0 V                            | 6    |                      | 6    | mV   |

| V <sub>DIFFO(err)</sub>  | $G_{SNS1}$                                                                       | $(V_{SNS1} - G_{SNS1}) = 3.6 V$                                            | -19  |                      | 19   |      |

|                          | Sourcing                                                                         |                                                                            | 1    |                      |      |      |

| I <sub>DIFFO</sub>       | Sinking                                                                          |                                                                            | 1    |                      |      | mA   |

(3) Apply to 1-,2- or 4-phase operation. For 3-phase operation, the switching frequency is 33% higher than the value in the table.

(4) The external SYNC pin signal must be a square waveform with 50% duty cycle.

(5) The soft-start time is the time that the internal reference voltage rises from 0 V to 600 mV.

### **Electrical Characteristics (continued)**

T<sub>J</sub> = -40°C to 125°C, V<sub>IN</sub> = V<sub>VDD</sub> = 12 V, RT set for 500 kHz, all parameters at zero power dissipation (unless otherwise noted)

|                          | PARAMETER                                                       | TEST CONDITIONS                                                 | MIN  | TYP                 | MAX | UNIT |

|--------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|------|---------------------|-----|------|

| CURRENT SI               | ENSING AMPLIFIER                                                |                                                                 |      |                     |     |      |

| M                        | Differential input valtage linear range                         | $(V_{CSxP} - V_{CSxN})$ , non-smart power mode                  | 0    |                     | 60  | mV   |

| V <sub>CS(mg)</sub>      | Differential input-voltage linear range                         | (V <sub>CSxP</sub> – V <sub>CSxN</sub> ), smart power mode      | 0    |                     | 600 |      |

| V <sub>CS(cmr)</sub>     | Input common-mode range                                         | Non-smart power mode                                            | 0    |                     | 3.6 | V    |

| V <sub>CS(cm)</sub>      | Input common-mode voltage                                       | Smart power mode                                                |      | 1.24                |     | V    |

|                          | 0                                                               | CHx_CSGAIN_SEL= 20 V/V <sup>(6)</sup> , non-smart power mode    |      | 10                  |     |      |

| A <sub>CS</sub>          | Current sensing gain                                            | CHx_CSGAIN_SEL= 20 V/V <sup>(6)</sup> , smart power mode        | 1    |                     | V/V |      |

| f <sub>co</sub>          | Closed loop bandwidth <sup>(2)</sup>                            |                                                                 |      | 0.66                |     | MHz  |

| V <sub>CS(chch)</sub>    | Amplifier output difference between two channels <sup>(7)</sup> | IOUT_CAL_GAIN = 0.503 m $\Omega$ ,<br>I <sub>PHASE</sub> = 20 A | -6%  |                     | 6%  |      |

| CURRENT LI               | MIT                                                             |                                                                 |      |                     |     |      |

| t <sub>OFF(oc)</sub>     | Off-time between restart attempts                               | Hiccup mode                                                     |      | 7 × t <sub>SS</sub> |     | ms   |

|                          | Output peak current overcurrent fault                           | Factory default settings                                        |      | 30                  |     | ٨    |

| I <sub>OC(flt)</sub>     | threshold                                                       | Programmable range                                              | 3    |                     | 50  | A    |

|                          | Output peak current overcurrent warning                         | Factory default settings                                        |      | 27                  |     | •    |

| I <sub>OC(warn)</sub>    | threshold                                                       | Programmable range                                              | 2    |                     | 49  | A    |

| 1                        | Output peak current overcurrent fault and<br>warning accuracy   | $I_{OUT}$ = 30 A, IOUT_CAL_GAIN = 0.503 m $\Omega$              | -10% |                     | 10% |      |

| I <sub>OC(acc)</sub>     | Output peak current overcurrent warning<br>accuracy             | $I_{OUT}$ = 27 A, IOUT_CAL_GAIN = 0.503 m $\Omega$              | -10% |                     | 10% |      |

| PGOOD                    |                                                                 |                                                                 |      |                     |     |      |

| V <sub>FBPGH</sub>       | FB PGOOD high threshold                                         | Factory default settings                                        |      | 675                 |     | mV   |

| V <sub>FBPGL</sub>       | FB PGOOD low threshold                                          | Factory default settings                                        |      | 525                 |     | mV   |

| V <sub>PG(acc)</sub>     | PGOOD accuracy over range                                       |                                                                 | -4%  |                     | 4%  |      |

| V <sub>pg(hyst)</sub>    | FB PGOOD hysteresis voltage                                     |                                                                 | 15   | 28                  | 45  | mV   |

| R <sub>PGOOD</sub>       | PGOOD pulldown resistance                                       | $V_{FB} = 0$ , $I_{PGOOD} = 5 \text{ mA}$                       |      | 50                  |     | Ω    |

| I <sub>PGOOD(lk)</sub>   | PGOOD pin leakage current                                       | $V_{FB}$ = 600 mV, $V_{PGOOD}$ = 5 V                            |      |                     | 20  | μA   |

| OUTPUT OVI               | ERVOLTAGE AND UNDERVOLTAGE                                      |                                                                 |      |                     |     |      |

| V <sub>FBOV</sub>        | FB pin over voltage threshold                                   | Factory default settings                                        |      | 700                 |     | mV   |

| V <sub>FBUV</sub>        | FB pin under voltage threshold                                  | Factory default settings                                        |      | 500                 |     | mV   |

| V <sub>UVOV(acc)</sub>   | FB UV/OV accuracy over range                                    |                                                                 | -4%  |                     | 4%  |      |

| V <sub>OV(hyst)</sub>    | FB OV hysteresis voltage                                        |                                                                 | 25   | 55                  | 90  | mV   |

|                          | TAGE TRIMMING AND MARGINING                                     |                                                                 |      |                     |     |      |

| V <sub>FBTM(step)</sub>  | Resolution of FB steps with trim and margin                     |                                                                 |      | 2                   |     | mV   |

| t <sub>FBTM(step)</sub>  | Transition time per trim or margin step                         | After soft-start time                                           |      | 30                  |     | μs   |

| V <sub>FBTM(max)</sub>   | Maximum FB voltage with trim or margin only                     |                                                                 |      | 660                 |     | mV   |

| V <sub>FBTM(min)</sub>   | Minimum FB voltage with trim or margin only                     |                                                                 |      | 480                 |     | mV   |

| V <sub>FBTM(rng)</sub>   | FB voltage range with trim and margin combined                  |                                                                 | 420  |                     | 660 | mV   |

| V <sub>FBMH</sub>        | Margin high FB pin voltage                                      | Factory default settings                                        |      | 660                 |     | mV   |

| V <sub>FBML</sub>        | Margin low FB pin voltage                                       | Factory default settings                                        |      | 540                 |     | mV   |

|                          | TAGE AT AVS MODE                                                |                                                                 |      |                     |     |      |

| V <sub>FBAVS(step)</sub> | Resolution of FB steps at AVS mode                              |                                                                 |      | 2                   |     | mV   |

| V <sub>FBAVS(max)</sub>  | Maximum FB voltage at AVS mode                                  |                                                                 |      | 1.5                 |     | V    |

| V <sub>FBAVS(min)</sub>  | Minimum FB voltage at AVS mode                                  |                                                                 |      | 500                 |     | mV   |

Please refer to PMBus command MFR\_SPECIFIC\_21 (OPTIONS) (E5h) section. Performance is verified under application conditions. (6)

(7)

### **Electrical Characteristics (continued)**

T<sub>J</sub> = -40°C to 125°C, V<sub>IN</sub> = V<sub>VDD</sub> = 12 V, RT set for 500 kHz, all parameters at zero power dissipation (unless otherwise noted)

|                        | PARAMETER                                                   | TEST CONDITIONS                                                                                                                                                                         | MIN   | TYP MAX     | UNIT    |

|------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|---------|

| AVS INTERFA            | ACE                                                         |                                                                                                                                                                                         |       |             |         |

| V <sub>VIO</sub>       | ASIC I/O voltage <sup>(2)</sup>                             |                                                                                                                                                                                         | 1.8   | 2.5         | V       |

| M                      | High-level input voltage, AVSCLK,                           | V <sub>VIO</sub> = 2.5 V                                                                                                                                                                | 1.75  |             | N       |

| V <sub>IH(avs)</sub>   | AVSDATA                                                     | V <sub>VIO</sub> = 1.8 V                                                                                                                                                                | 1.26  |             | V       |

| \ <i>\</i>             | Low-level input voltage, AVSCLK,                            | V <sub>VIO</sub> = 2.5 V                                                                                                                                                                |       | 0.75        | v       |

| V <sub>IL(avs)</sub>   | AVSDATA                                                     | V <sub>VIO</sub> = 1.8 V                                                                                                                                                                |       | 0.54        | V       |

| I <sub>IH(avs)</sub>   | High-level input current, AVSCLK, AVSDATA <sup>(2)</sup>    |                                                                                                                                                                                         | -50   | 50          | μA      |

| I <sub>IL(avs)</sub>   | Low-level input current, AVSCLK, AVSDATA <sup>(2)</sup>     |                                                                                                                                                                                         | -50   | 50          | μA      |

| f <sub>AVS</sub>       | AVS clock frequency range                                   |                                                                                                                                                                                         | 10    | 30          | MHz     |

| MEASUREME              | NT SYSTEM                                                   |                                                                                                                                                                                         |       |             |         |

| M <sub>VOUT(rng)</sub> | V <sub>OUT</sub> measurement range                          |                                                                                                                                                                                         | 0.5   | 3.6         | V       |

| M <sub>VOUT(acc)</sub> | V <sub>OUT</sub> measurement accuracy <sup>(7)</sup>        | $V_{OUT} = 1 \text{ V}, 0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}$                                                                                              | -0.8% | 0.8%        |         |

| M <sub>IOUT(rng)</sub> | I <sub>OUT</sub> measurement range <sup>(8)</sup>           |                                                                                                                                                                                         | 0     | 50          | Α       |

| M <sub>IOUT(acc)</sub> | I <sub>OUT</sub> measurement accuracy <sup>(7)</sup>        | $I_{OUT} \ge 20 \text{ A}, \text{ IOUT_CAL_GAIN} = 0.503 \text{ m}\Omega, 0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}, \text{ V}_{\text{CSxN}} \le 2.5 \text{ V}$ | -640  | 640         | mA      |

| PMBus INTER            | RFACE <sup>(9)</sup>                                        | L                                                                                                                                                                                       |       |             |         |

| V <sub>IH</sub>        | High-level input voltage, CLK, DATA, CNTL                   |                                                                                                                                                                                         | 2.1   |             |         |

| V <sub>IL</sub>        | Low-level input voltage, CLK, DATA, CNTL                    |                                                                                                                                                                                         |       | 0.8         | V       |

| I <sub>IH</sub>        | High-level input current, CLK, DATA, CNTL                   | Pin voltage = 3.3 V                                                                                                                                                                     | -10   | 10          |         |

| I <sub>IL</sub>        | Low-level input current, CLK, DATA, CNTL                    | Pin voltage = 0 V                                                                                                                                                                       | -10   | 10          | μA      |

| V <sub>OL</sub>        | Low-level output voltage, DATA, SMBALRT                     | I <sub>OUT</sub> = 4 mA                                                                                                                                                                 |       | 0.4         | V       |

| I <sub>OH</sub>        | High-level output open drain leakage current, DATA, SMBALRT | V <sub>OUT</sub> = V <sub>BP5</sub>                                                                                                                                                     | 0     | 10          | μA      |

| I <sub>OL</sub>        | Low-level output open drain current, DATA, SMBALRT          |                                                                                                                                                                                         | 4     |             | mA      |

| C <sub>OUT</sub>       | Pin capacitance, CLK, DATA <sup>(2)</sup>                   |                                                                                                                                                                                         |       | 1           | pF      |

| f <sub>PMB</sub>       | PMBus operating frequency range                             | Slave mode                                                                                                                                                                              | 10    | 400         | kHz     |

| t <sub>BUF</sub>       | Bus free time between START and STOP <sup>(2)</sup>         |                                                                                                                                                                                         | 1.3   |             |         |

| t <sub>HD:STA</sub>    | Hold time after repeated START <sup>(2)</sup>               |                                                                                                                                                                                         | 0.6   |             | -       |

| t <sub>SU:STA</sub>    | Repeated START set-up time <sup>(2)</sup>                   |                                                                                                                                                                                         | 0.6   |             | μs      |

| t <sub>SU:STO</sub>    | STOP setup time <sup>(2)</sup>                              |                                                                                                                                                                                         | 0.6   |             | -       |

|                        |                                                             | Receive mode                                                                                                                                                                            | 0     |             |         |

| t <sub>HD:DAT</sub>    | Data hold time <sup>(2)</sup>                               | Transmit mode                                                                                                                                                                           | 300   |             | ns      |

| t <sub>SU:DAT</sub>    | Data setup time <sup>(2)</sup>                              |                                                                                                                                                                                         | 100   |             | 1       |

| t <sub>TIMEOUT</sub>   | Error signal/detect <sup>(2)</sup>                          |                                                                                                                                                                                         | 25    | 35          | ms      |

| t <sub>LOW:MEXT</sub>  | Cumulative clock low master extend time <sup>(2)</sup>      |                                                                                                                                                                                         | -     | 10          | ms      |

| tLOW:SEXT              | Cumulative clock low slave extend time <sup>(2)</sup>       |                                                                                                                                                                                         |       | 25          | ms      |

| t <sub>LOW</sub>       | Clock low time <sup>(2)</sup>                               |                                                                                                                                                                                         | 1.3   |             | μs      |

| t <sub>HIGH</sub>      | Clock high time <sup>(2)</sup>                              |                                                                                                                                                                                         | 0.6   |             | μs      |

| t <sub>FALL</sub>      | CLK/DATA fall time <sup>(2)</sup>                           |                                                                                                                                                                                         | 0.0   | 300         | 24      |

|                        | CLK/DATA rise time <sup>(2)</sup>                           |                                                                                                                                                                                         |       | 300         | ns      |

| t <sub>RISE</sub>      | Retention of configuration parameters <sup>(2)</sup>        | $T_J = 25^{\circ}C$                                                                                                                                                                     | 100   | 300         | Year    |

| t <sub>RETENTION</sub> | Number of nonvolatile erase/write cycles <sup>(2)</sup>     |                                                                                                                                                                                         |       |             |         |

| Write_cycles           |                                                             | $T_J = 25^{\circ}C$                                                                                                                                                                     | 20    |             | K cycle |

| PMBus ADDR             |                                                             |                                                                                                                                                                                         | a     |             |         |

| I <sub>ADD</sub>       | Address pin bias current                                    |                                                                                                                                                                                         | 8.775 | 9.75 10.725 | μA      |

(8)

The actual measurement range is limited by the IOUT\_CAL\_GAIN command. See the IOUT\_CAL\_GAIN (38h) section. The device supports both 100-kHz and 400-kHz bus speeds. The PMBus timing parameters in this table is for operation at 400 kHz. If the PMBus operating frequency is 100 kHz, refer to SMBus specification for timing parameters. (9)

## **Electrical Characteristics (continued)**

$T_J = -40^{\circ}$ C to 125°C,  $V_{IN} = V_{VDD} = 12$  V, RT set for 500 kHz, all parameters at zero power dissipation (unless otherwise noted)

|                          | PARAMETER                                                         | TEST CONDITIONS                                                    | MIN  | TYP | MAX  | UNIT  |  |

|--------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|------|-----|------|-------|--|

| INITIALIZAT              | ION TIME                                                          | · · · · ·                                                          |      |     |      |       |  |

| t <sub>INI</sub>         | Initialization time after BP3 voltage is ready <sup>(2)</sup>     |                                                                    |      | 1   |      | ms    |  |

| TEMPERATU                | JRE SENSE AND THERMAL SHUTDOWN                                    |                                                                    |      |     |      |       |  |

| T <sub>SD</sub>          | Junction shutdown temperature <sup>(2)</sup>                      |                                                                    |      | 160 |      | °C    |  |

| T <sub>HYST</sub>        | Thermal shutdown hysteresis <sup>(2)</sup>                        |                                                                    |      | 20  |      | Ĵ     |  |

| I <sub>TSNS(ratio)</sub> | Ratio of bias current flowing out of TSNS pin, state 2 to state 1 | Non-smart power mode                                               | 9.7  | 10  | 10.3 | μΑ/μΑ |  |

| I <sub>TSNS(1)</sub>     | State 1 current out of TSNS pin                                   | Non-smart power mode                                               |      | 10  |      | μA    |  |

| I <sub>TSNS(2)</sub>     | State 2 current out of TSNS pin                                   | Non-smart power mode                                               |      | 100 |      | μA    |  |

| T <sub>SNS(acc)</sub>    | External temperature sense accuracy <sup>(7)</sup>                | $-40^{\circ}C \le T_{SNS} \le 125^{\circ}C$ , Non-smart power mode | -4.5 |     | 4.5  | °C    |  |

| ente(doo)                |                                                                   | $-40^{\circ}C \le T_{SNS} \le 125^{\circ}C$ , Smart power mode     | -3   |     | 3    |       |  |

| <b>-</b>                 | Overtemperature fault limit <sup>(2)</sup>                        | Factory default settings                                           |      | 125 |      | °C    |  |

| T <sub>OT(fit)</sub>     | OT fault limit range <sup>(2)</sup>                               |                                                                    | 120  |     | 165  | Ĵ     |  |

| <b>-</b>                 | Overtemperature warning limit <sup>(2)</sup>                      | Factory default settings                                           |      | 100 |      |       |  |

| T <sub>OT(warn)</sub>    | OT warning limit range <sup>(2)</sup>                             |                                                                    | 100  |     | 140  | °C    |  |

| T <sub>OT(step)</sub>    | OT fault/warning step                                             |                                                                    |      | 1   |      | °C    |  |

| T <sub>OT(hys)</sub>     | OT fault/warning hysteresis <sup>(2)</sup>                        |                                                                    |      | 20  |      | °C    |  |

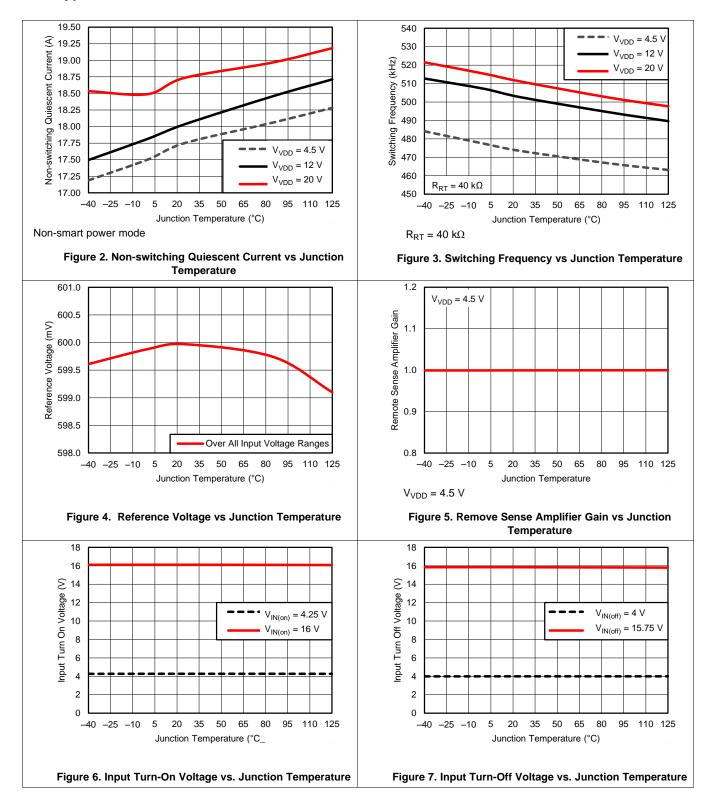

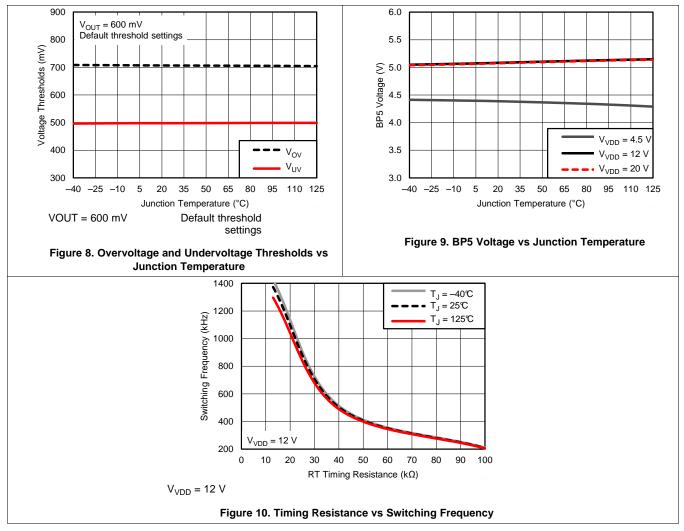

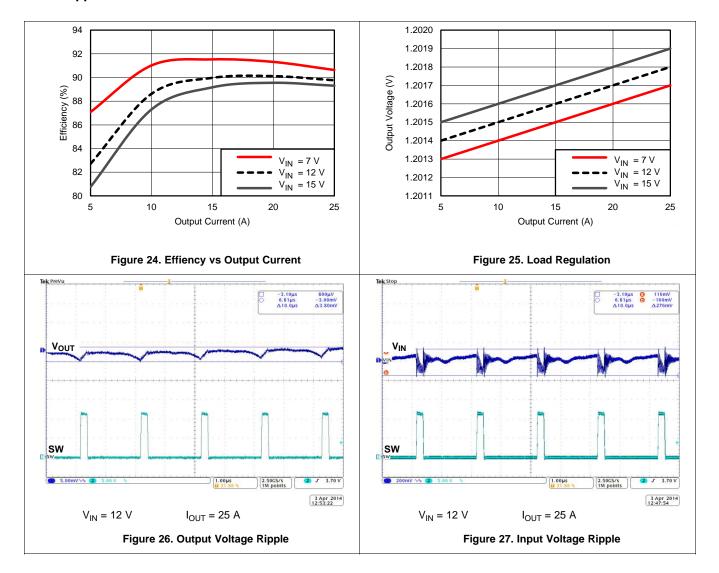

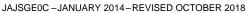

### 6.6 Typical Characteristics

### **Typical Characteristics (continued)**

## 7 Detailed Description

### 7.1 Overview

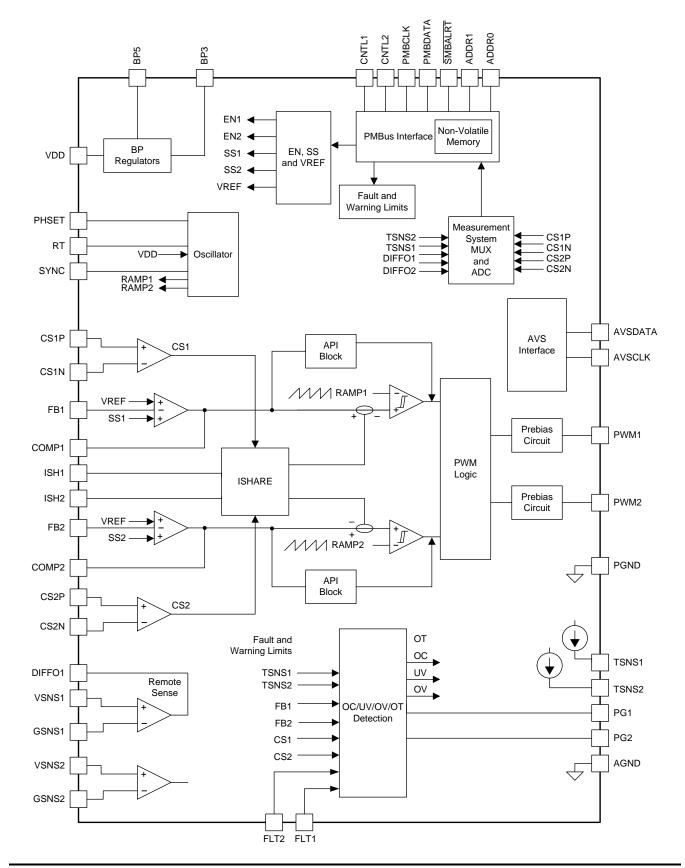

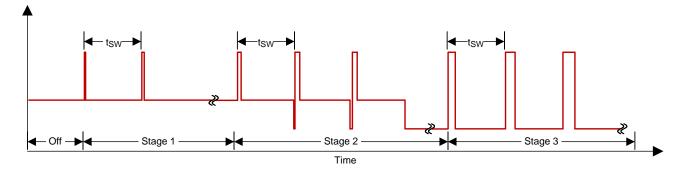

The TPS40425 device is a PMBus synchronous buck driverless controller. It can be configured as a dual-output or single output two phase. It is also stackable up to 4 phases to support load current as high as 120 A. Interleaved phase shift for 2-, 3-, or 4-phase operation reduces the input and output ripples therefore reducing input and output capacitance.

When operating in dual-output mode, the device implements voltage mode control with input feed-forward architecture. With this architecture, the benefits are less noise sensitivity, no control instability issues for small DCR applications, and a smaller minimum controllable on-time, often desired for high conversion ratio applications. In multi-phase mode, the device implements a current-sharing loop to ensure a balance of current between phases.

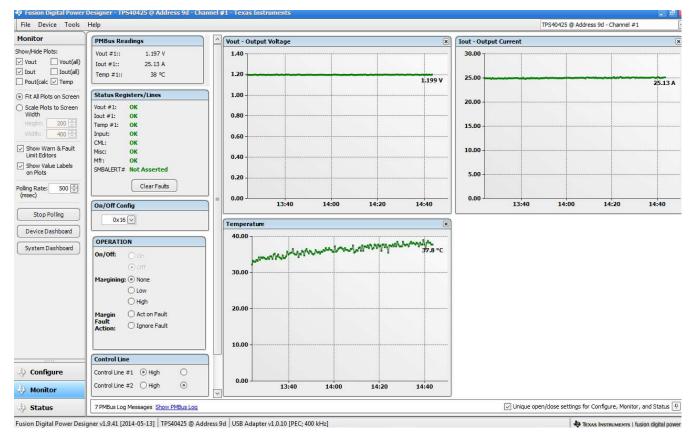

The wide input voltage range supports 5-V and 12-V intermediate buses. The 0.5% reference voltage satisfies the need for precision voltage required by modern ASICs. PMBus functionality allows the TPS40425 device to program margining function, reference voltage, fault limit, UVLO threshold, soft-start time and turn-on delay time and turn-off delay time. In addition, an accurate measurement system monitors the output voltages, currents and temperatures for individual channels.

## 7.2 Functional Block Diagram

### 7.3 Feature Description

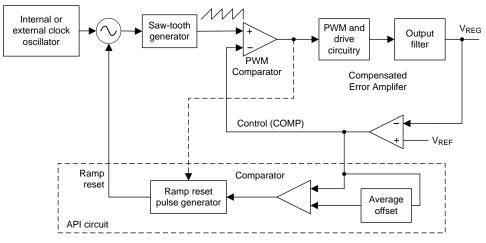

#### 7.3.1 Asynchronous Pulse Injection (API)

The TPS40425 device implements a TI proprietary control scheme to achieve fast transient response. This scheme has the following key features:

- Voltage mode with API (asynchronous pulse injection) technology

- Fast transient response to reduce output capacitance

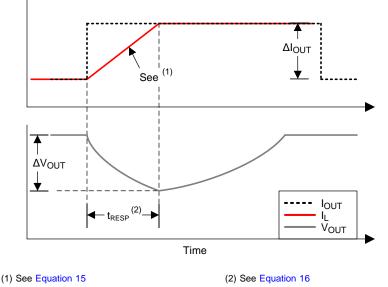

Figure 11 shows the control loop with API technology. The control scheme continuously senses the voltage on the COMP pin to determine a transient event that could require a sudden increase in duty-cycle. Upon detecting such an event, additional pulses are asynchronously injected in the PWM stream to quickly respond to the transient and arrest any undershoot in the output voltage.

Refer to the MFR\_SPECIFIC\_32 (API\_OPTIONS) (F0h) section for more information.

The API response can be delayed by compensation, parasitic impedance between the output inductor and the voltage sense point. If the delay is large, the asynchronous PWM might inject too much energy and result in overshoot during load step-up. In this case, it is imperative to optimize the compensation and reduce the parasitic impedance. If these efforts cannot reduce the overshoot to an acceptable level, disable the API function.

Figure 11. API Block Diagram

#### 7.3.2 Adaptive Voltage Scaling (AVS)

AVS provides output voltage scaling. AVSBus is a 2-wire communication link that enables bi-directional communication between one ASIC and one or more slave devices for controlling voltage scaling. The two wires required for communication are AVS\_Clock and AVS\_Data. The AVSBus interface could be used exclusively once PMBus has configured the device properly. The AVS commands can select channel 1 or channel 2 of slave device.

AVSBus is scalable for use with multiple slave devices, and allows for independent control of multiple rails within each slave. This scalability is achieved without sacrificing response time for simpler designs with a single slave, by means of configuration settings.

NOTE

PMBus commands are required to:

- configure the device to AVS mode

- set AVS address for the device

- set transition slew rate of output voltage

**TPS40425**

JAJSGE0C – JANUARY 2014 – REVISED OCTOBER 2018

### Feature Description (continued)

### 7.3.3 Switching Frequency and Synchronization

A resistor from the RT pin to AGNG sets the switching frequency ( $f_{SW}$ ). The  $R_{RT}$  resistor value is calculated in Equation 1 for switching frequencies below 800 kHz. For switching frequencies above 800 kHz, refer to Table 1 for  $R_{RT}$  resistor values.

$$R_{RT} = \frac{20 \times 10^9}{f_{SW}}$$

where

- $R_{RT}$  is the resistor from RT pin to AGND, in  $\Omega$

- f<sub>SW</sub> is the desired switching frequency, in Hz

The switching frequency during 3-phase operation is 1.33 times of that at 1-, 2-, or 4-phase operation with the same RT resistor value. Use Equation 2 to calculate the RT resistor value for 3-phase operation.

$$\mathsf{R}_{\mathsf{RT}} = \frac{26.67 \times 10^9}{\mathsf{f}_{\mathsf{SW}}}$$

where

- $R_{\text{RT}}$  is the resistor from RT pin to AGND, in  $\Omega$

- *f*<sub>SW</sub> is the desired switching frequency, in Hz

|   |                                              | J                                         |

|---|----------------------------------------------|-------------------------------------------|

| Y | SWITCHING FREQUENCY<br>f <sub>SW</sub> (kHz) | TIMING RESISTANCE<br>R <sub>RT</sub> (kΩ) |

|   | 1520                                         | 11                                        |

|   | 1450                                         | 11.8                                      |

|   | 1400                                         | 12.4                                      |

|   | 1370                                         | 13                                        |

|   | 1208                                         | 15                                        |

|   | 948                                          | 20                                        |

|   | 776                                          | 24.9                                      |

|   | 1400<br>1370<br>1208<br>948                  | 12.4<br>13<br>15<br>20                    |

### Table 1. Setting the Switching Frequency

The accuracy of the frequency setting is  $\pm 10\%$ . For 3-phase and 4-phase applications, the RT resistors should be identical for both the controllers. In 3-phase and 4-phase applications, the device achieves clock and phase synchronization between the two controllers by connecting the SYNC pins and PHSET pins of the master controller to the corresponding pins on the slave controller. Phase configuration indicating number of phases is set according to the PMBus manufacturer specific command MFR\_SPECIFIC\_22 (E6h).

The switching frequency can be synchronized by an external clock on the SYNC pin. The frequency of the SYNC signal must be 4 times the switching frequency during 1-, 2-, or 4-phase operation, and must be 3 times the switching frequency during 3-phase operation. The SYNC signal must be a square waveform with 50% duty cycle. The high-level threshold must be above 2 V, and the low-level threshold must be below 0.8 V. The change on SYNC and PHSET setting occurs only after a power re-cycle.

### 7.3.4 Voltage Reference

The 600-mV bandgap cell is internally connected to the non-inverting input of the error amplifier. The reference voltage is 600 mV with  $\pm 0.5\%$  between  $-40^{\circ}$ C and  $125^{\circ}$ C.

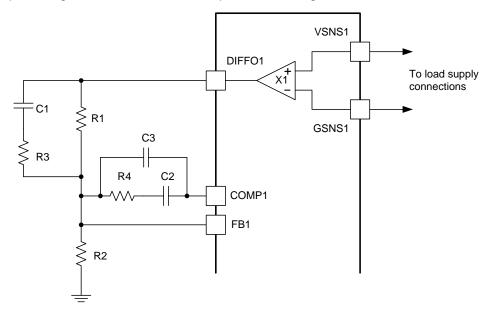

### 7.3.5 Output Voltage and Remote Sensing Amplifier

Setting the output voltage is very similar to that of a traditional analog controller using a voltage divider from the output to the feedback (FB) pin. The output voltage must be divided to the nominal reference voltage of 600 mV. Figure 12 shows the typical connections for the controller. The voltage at the load is sensed using the unity gain differential voltage sense amplifier. This type of sensing provides better load regulation (see electrical specifications for the maximum output voltage of the differential sense amplifier).

(1)

(2)

To prevent output voltage out of regulation, ensure the maximum allowed DIFFO1 voltage ( $V_{BP5} - 0.2$  V) is larger than actual output voltage at any time including when BP5 ramps down. For output voltages above the DIFFO1 pin specification, connect the output voltage directly to the junction of R1 and C1, leave DIFFO1 open and do not connect the VSNS1 pin to the output voltage. If the design includes a resistor divider before the remote sensing amplifier, the output voltage readout on PMBus is equal to the voltage between VSNS1 and GSNS1.

Figure 12. Setting the Output Voltage

$$R2 = V_{FB} \frac{R1}{(V_{OUT} - V_{FB})}$$

where

- V<sub>FB</sub> is the feedback voltage

- V<sub>OUT</sub> is the desired output voltage

- R1 and R2 are in the same units

(3)

### DESIGN NOTE

There is no DIFFO2 pin. In dual-output mode, VSNS2 and GSNS2 are connected to the load for channel 2 and the DIFFO2 signal is used internally for voltage monitoring. Connect the output directly to the junction of R1 and C1 for channel 2 to set the output voltage and for feedback.

The feedback voltage can be changed –30% to 10% from the nominal 600 mV using PMBus commands. The output voltage can vary by the same percentage.

### 7.3.6 Current Sensing and Temperature Sensing Modes

The TPS40425 device can operate in two modes established by current and temperature sensing methods. The device operates in non-smart power mode with the factory default setting, and it can also operate in non-smart power mode after PMBus programing and power reboot. Refer to the MFR\_SPECIFIC\_21 (OPTIONS) (E5h) section for more information. Consider using the TPS40428 device if smart power mode in factory default setting is preferred in the application. Refer to the TPS40428 device datasheet (SLUSBV0) for more information.

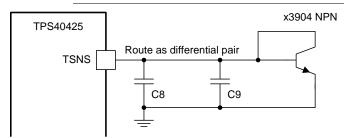

### 7.3.6.1 Non Smart-Power Operation

Current sensing is based on inductor DCR (direct current resistance) sensing or a separate current sense resistor. Temperature sensing must be based on the  $\Delta$ Vbe measurement of an external diode (x3904). This mode can be used with standard power-stages, such as the CSD95372A.

TPS40425 JAJSGE0C – JANUARY 2014 – REVISED OCTOBER 2018

www.ti.com

If inductor DCR is used for current sensing, the TPS40425 device compensates for the temperature variation of DCR value by using the temperature sensed at the external sensor for that channel. The temperaturecompensated DCR value is used both for reporting inductor current over PMBus and for overcurrent fault and warning functions.

If a sense resistor is used for current sensing and the temperature variation of resistor value is very small, the temperature compensation in the TPS40425 device can be disabled. See the *MFR\_SPECIFIC\_21 (OPTIONS) (E5h)* section for more information.

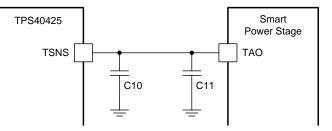

#### 7.3.6.2 Smart-Power Operation.

The current sensing function in the TPS40425 device is based on sensed voltage reported by the smart powerstage (at 5 mV/A). No temperature compensation is needed on the controller side. Temperature sensing is based on the voltage reported by the smart power-stage (at 8 mV/°C + 400 mV offset). This mode can be used with the smart power-stage (CSD95378B). During smart-power mode operation, an internal 10-x factor is applied to the current readout, therefore the IOUT\_CAL\_GAIN must be set to 0.5 m $\Omega$  instead of 5 m $\Omega$ .

#### NOTE

Both channels of the TPS40425 device need to operate in the same operating mode (either non smart-power or smart-power) at all times. The factory default setting is non-smart-power mode. An operation mode change occurs only after a power re-cycle.

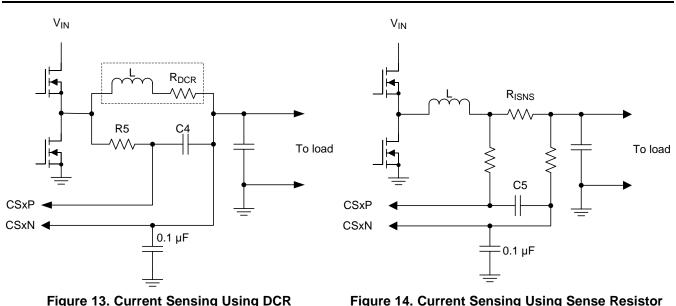

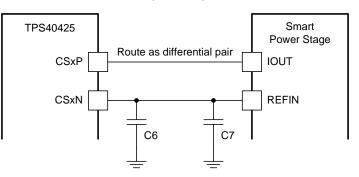

### 7.3.7 Current Sensing

During non smart-power operation and while the controller uses inductor DCR for current sensing as shown in Figure 13, a filter must be used to remove the large AC component of voltage across the inductor and leave only the component of the voltage that appears across the resistance of the inductor. The values of R5 and C4 for the ideal case can be found using Equation 4. The time constant of the R-C filter should be equal to or greater than the time constant of the inductor. If the time constants are equal, the voltage appearing across C4 is the current in the inductor multiplied the inductor resistance. The voltage across C4 perfectly reflects the inductor ripple current in this case and there is no reason to have a shorter R-C time constant.