TPS7A84 JAJSM55B – JANUARY 2016 – REVISED JUNE 2021

# TPS7A84 大電流 (3A)、高精度 (1%)、 低ノイズ (4.4µV<sub>RMS</sub>)、LDO 電圧レギュレータ

# 1 特長

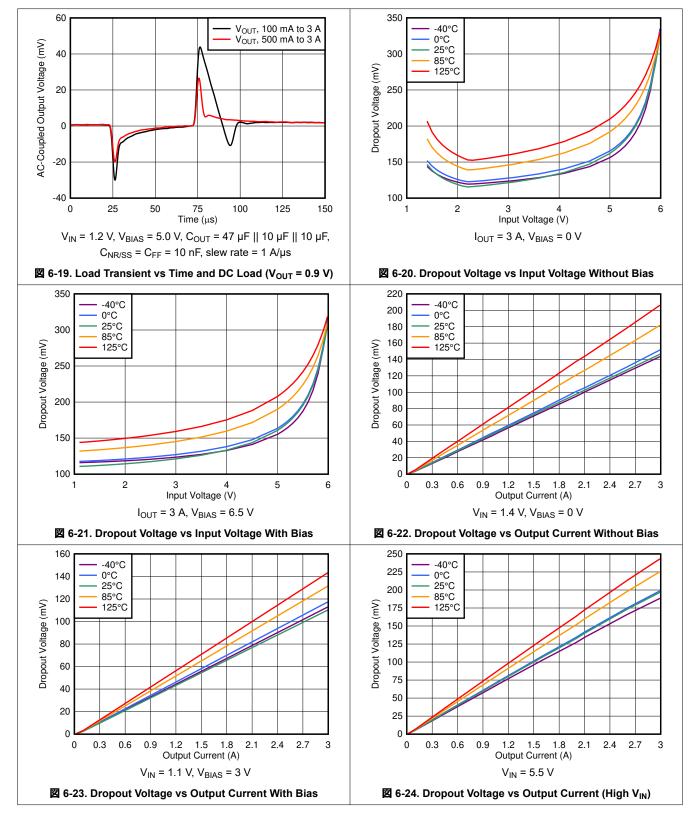

- 低ドロップアウト:180mV (最大値)、3A 時

- ライン、負荷、温度の全範囲にわたって 1% (最大値) の精度

- 出力電圧ノイズ:

- 0.8V 出力で 4.4µV<sub>RMS</sub>

- 5.0V 出力で 7.7µV<sub>RMS</sub>

- 入力電圧範囲:

- BIAS なし:1.4V~6.5V

- BIAS あり:1.1V~6.5V

- ANY-OUT<sup>™</sup> 動作:

- 出力電圧範囲:0.8V~3.95V

- 可変動作:

- 出力電圧範囲:0.8V~5.0V

- 電源リップル除去:

500kHz 時に 40dB

- 非常に優れた負荷過渡応答

- 可変ソフトスタート突入電流制御

- オープン・ドレインのパワー・グッド (PG) 出力

- 47µF 以上のセラミック出力コンデンサで安定

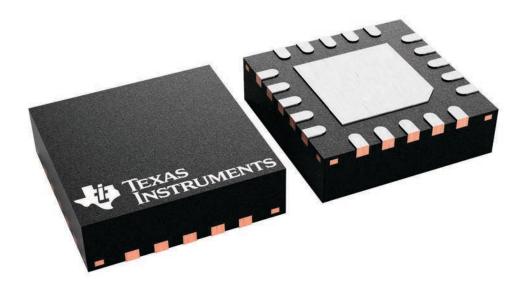

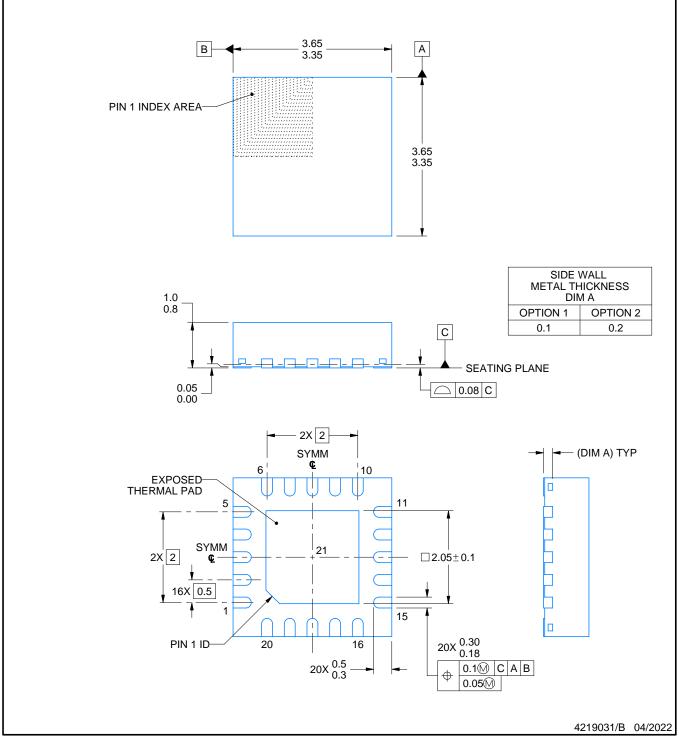

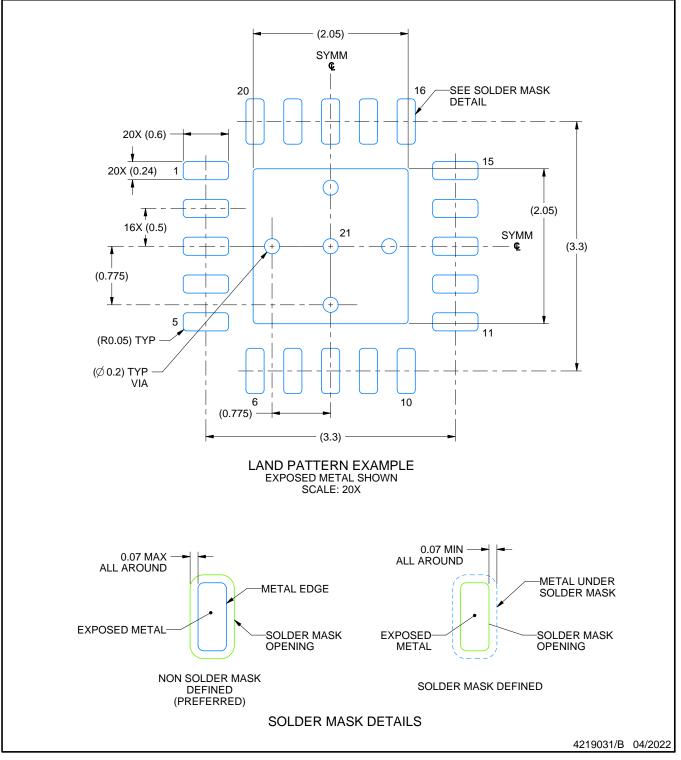

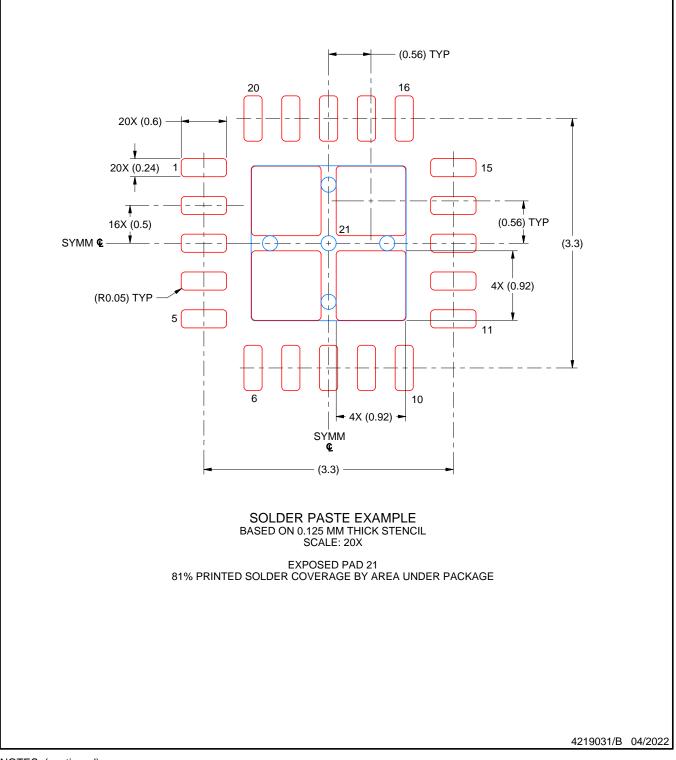

- 3.5mm × 3.5mm、20 ピンの VQFN

# 2 アプリケーション

- マクロ・リモート無線ユニット (RRU)

- 屋外バックホール・ユニット

- アクティブ・アンテナ・システム (AAS)の mMIMO

- 超音波スキャナ

- 実験室およびフィールド計測

- ・ センサ、画像処理、レーダー

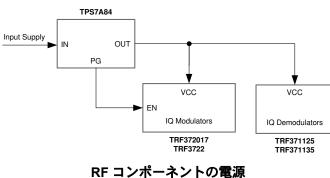

# Bias Supply BIAS IN TPS7A84 OUT EN Signal EN PG Vod DSP, ASIC, FPGA C6000

# デジタル負荷の電源

# 3 概要

TPS7A84 は低ノイズ (4.4µV<sub>RMS</sub>)、低ドロップアウトのリニ ア・レギュレータ (LDO) で、3A を供給でき、ドロップアウト は最大でわずか 180 mV です。このデバイスの出力電圧 はピンにより 0.8V~3.95V にプログラム可能で、外付けの 分圧抵抗を使用して 0.8V~5.0V に調整可能です。

TPS7A84 は、低ノイズ(4.4µV<sub>RMS</sub>)、高 PSRR、大出力電 流という特性により、高速通信、ビデオ、医療機器、検査、 計測などのアプリケーションで使用されるノイズに敏感な 部品への電源供給に理想的です。TPS7A84 は、電源で 発生する位相ノイズとクロック・ジッタを抑制する高い性能 を備えているため、高性能のシリアライザ / デシリアライザ (SerDes)、A/D コンバータ (ADC)、D/A コンバータ (DAC)、RF コンポーネントの電源供給に理想的です。特 に、RF アンプにはこのデバイスの高い性能と 5.0V 出力 能力が役立ちます。

デジタル負荷 (ASIC (Application-Specific Integrated Circuit)、FPGA (Field-Programmable Gate Array)、 DSP (Digital Signal Processor) など) で低入力電圧、低 出力電圧 (LILO) 動作を必要とする場合、TPS7A84 の非 常に優れた精度 (負荷および温度の全範囲にわたって 0.75%)、リモート・センシング、優れた過渡性能、ソフトスタ ート機能によって最適のシステム性能が保証されます。

多用途な TPS7A84 は、要求の厳しい各種のアプリケー ションの部品として最適な選択肢です。

#### 製品情報(1)

| 部品番号    | パッケージ     | 本体サイズ (公称)      |  |  |  |  |  |

|---------|-----------|-----------------|--|--|--|--|--|

| TPS7A84 | VQFN (20) | 3.50mm × 3.50mm |  |  |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

53

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 www.ti.comで閲覧でき、その内容が常に優先されます。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 | 特長                                   | . 1 |

|---|--------------------------------------|-----|

|   | アプリケーション                             |     |

|   | 概要                                   |     |

|   | Revision History                     |     |

|   | Pin Configurations and Functions     |     |

| 6 | Specifications                       | .4  |

|   | 6.1 Absolute Maximum Ratings         | .4  |

|   | 6.2 ESD Ratings                      | . 4 |

|   | 6.3 Recommended Operating Conditions | 5   |

|   | 6.4 Thermal Information              | 5   |

|   | 6.5 Electrical Characteristics       | 6   |

|   | 6.6 Typical Characteristics          | .8  |

| 7 | Detailed Description                 |     |

|   | 7.1 Overview                         | 15  |

|   | 7.2 Functional Block Diagram         | 16  |

|   | 7.3 Feature Description              | 16  |

|   | 7.4 Device Functional Modes          | 18  |

|   |                                      |     |

| 8 Application and Implementation                      | . 19 |

|-------------------------------------------------------|------|

| 8.1 Application Information                           |      |

| 8.2 Typical Applications                              |      |

| 9 Power Supply Recommendations                        |      |

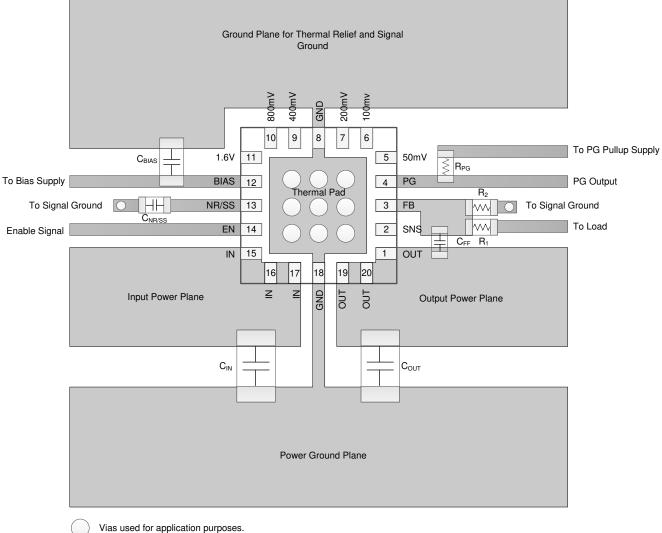

| 10 Layout                                             |      |

| 10.1 Layout Guidelines                                |      |

| 10.2 Layout Example                                   |      |

| 11 Device and Documentation Support                   |      |

| 11.1 Device Support                                   | .39  |

| 11.2 Documentation Support                            |      |

| 11.3 Receiving Notification of Documentation Updates. | . 39 |

| 11.4 サポート・リソース                                        | .39  |

| 11.5 Trademarks                                       |      |

| 11.6 Electrostatic Discharge Caution                  |      |

| 11.7 Glossary                                         | .40  |

| 12 Mechanical, Packaging, and Orderable               |      |

| Information                                           | . 40 |

|                                                       |      |

# 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| C | hanges from Revision A (January 2016) to Revision B (June 2021)                                                | Page            |

|---|----------------------------------------------------------------------------------------------------------------|-----------------|

| • | 文書全体にわたって表、図、相互参照の採番方法を更新                                                                                      | 1               |

| • | アプリケーションセクションにリンクを追加                                                                                           |                 |

| • | Changed title of Figure 8                                                                                      |                 |

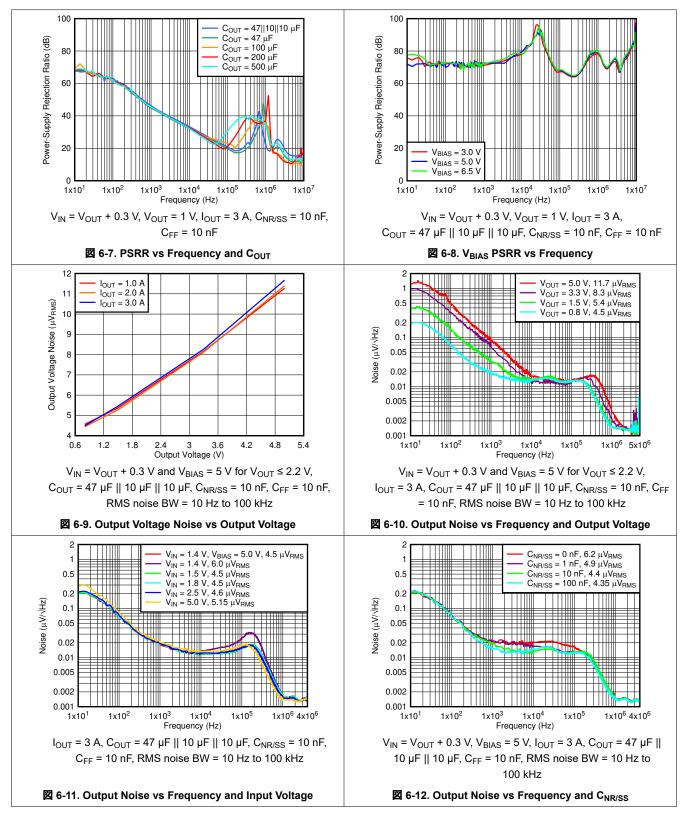

| • | Added RMS noise BW condition to Figure 9 through Figure 12                                                     |                 |

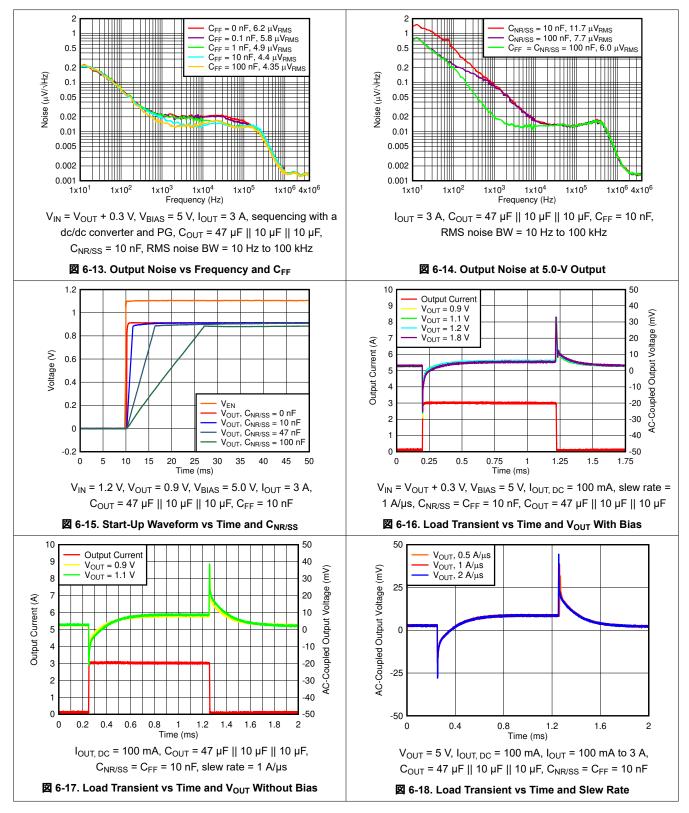

| • | Changed conditions of Figure 13 and Figure 14                                                                  |                 |

| • | Changed the Bias Rail section for clarification                                                                |                 |

| • | Changed Programmable Soft-Start section for clarification                                                      | 17              |

| • | Added last paragraph to Internal Current Limit section                                                         |                 |

| • | Moved Soft-Start and In-Rush Current section                                                                   | 20              |

| • | Added Charge Pump Noise section                                                                                | 21              |

| • | Changed equation 4: changed V <sub>REF</sub> to V <sub>NR/SS</sub>                                             |                 |

| • | Added Current Sharing section                                                                                  | 25              |

| • | Changed Table 5                                                                                                | 25              |

| • | Changed Figure 47                                                                                              | <mark>26</mark> |

| • | Added R <sub>PJ</sub> to Figure 48                                                                             | 27              |

| • | Changed Undervoltage Lockout (UVLO) Operation section                                                          | 28              |

| • | Changed Behavior when Transitioning from Dropout into Regulation section                                       | 29              |

| • | Changed Load Transient Response section                                                                        | 29              |

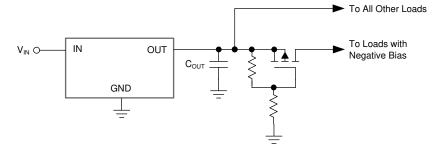

| • | Changed title of Negatively-Biased Output section                                                              | 30              |

| • | Added Reverse Current Protection section                                                                       | 30              |

| • | Changed equation 9 from $P_D = (V_{OUT} - V_{IN}) \times I_{OUT}$ to $P_D = (V_{IN} - V_{OUT}) \times I_{OUT}$ | 31              |

| • | Added equation 11                                                                                              | 31              |

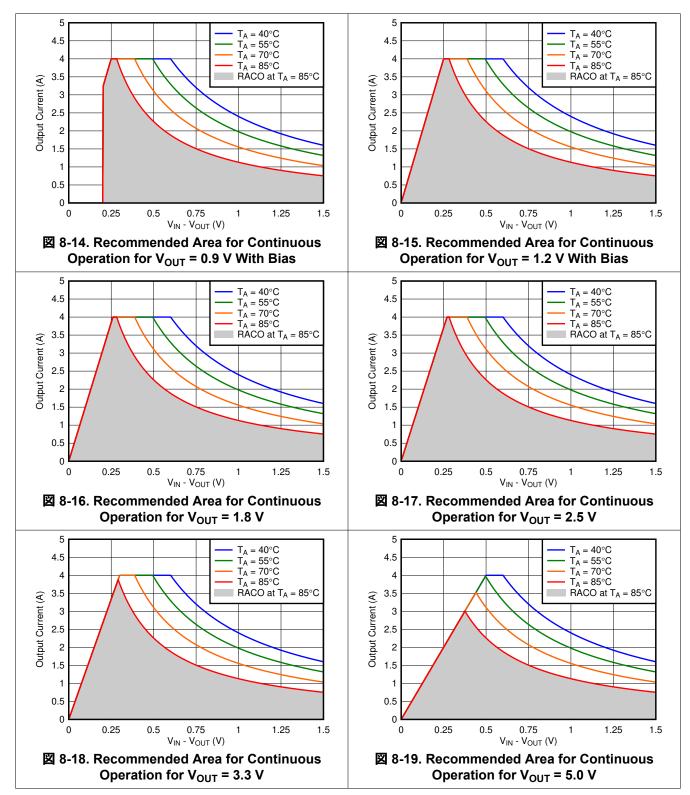

| • | Added Recommended Area for Continuous Operation section                                                        | 32              |

| • | Changed Table 8                                                                                                | 39              |

| С | hanges from Revision * (January 2016) to Revision A (January 2016)                                             | Page            |

| 量産用にリリー | ス | <br> | <br> | <br> | <br>1 |

|---------|---|------|------|------|-------|

•

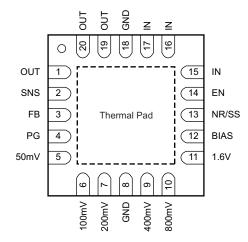

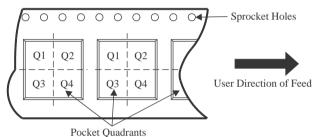

# **5** Pin Configurations and Functions

# 図 5-1. RGR Package, 3.5-mm × 3.5-mm, 20-Pin VQFN, Top View

#### 表 5-1. Pin Functions

| PIN         |           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 50mV        | 5         |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 100mV       | 6         | 1   | ANY-OUT voltage setting pins. Connect these pins to ground, SNS, or leave floating. Connecting these pins to ground                                                                                                                                                                                                                                                                                                                                  |

| 200mV       | )mV 7     |     | increases the output voltage, whereas connecting these pins to SNS increases the resolution of the ANY-OUT network                                                                                                                                                                                                                                                                                                                                   |

| 400mV       | 9         |     | but decreases the range of the network; multiple pins can be simultaneously connected to GND or SNS to select the desired output voltage. Leave these pins floating (open) when not in use. See the ANY-OUT Programmable Output                                                                                                                                                                                                                      |

| 800mV       | 10        | 1   | Voltage section for additional details.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1.6V        | 11        | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BIAS        | 12        | I   | BIAS supply voltage. This pin enables the use of low-input voltage, low-output (LILO) voltage conditions (that is, $V_{IN} = 1.2$ V, $V_{OUT} = 1$ V) to reduce power dissipation across the die. The use of a BIAS voltage improves dc and ac performance for $V_{IN} \le 2.2$ V. A 10-µF capacitor or larger must be connected between this pin and ground. If not used, this pin must be left floating or tied to ground.                         |

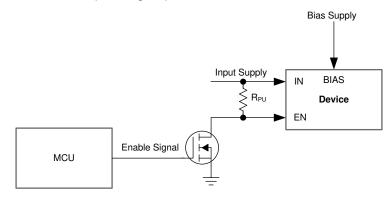

| EN          | 14        | I   | Enable pin. Driving this pin to logic high enables the device; driving this pin to logic low disables the device. If enable functionality is not required, this pin must be connected to IN. If enable functionality is required, $V_{EN}$ must always be high after $V_{IN}$ is established when a BIAS supply is used. See the <i>Sequencing Requirements</i> section for more details.                                                            |

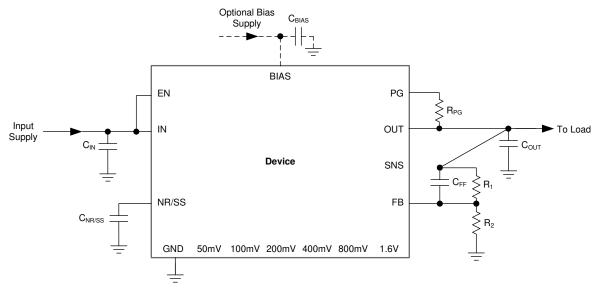

| FB          | 3         | I   | Feedback pin connected to the error amplifier. Although not required, a 10-nF feed-forward capacitor from FB to OUT (as close to the device as possible) is recommended to maximize ac performance. The use of a feed-forward capacitor can disrupt PG (power good) functionality. See the <i>ANY-OUT Programmable Output Voltage</i> and <i>Adjustable Operation</i> sections for more details.                                                     |

| GND         | 8, 18     | _   | Ground pin. These pins must be connected to ground, the thermal pad, and each other with a low-impedance connection.                                                                                                                                                                                                                                                                                                                                 |

| IN          | 15-17     | I   | Input supply voltage pin. A 47- $\mu$ F or larger ceramic capacitor (25 $\mu$ F or greater of capacitance) from IN to ground is recommended to reduce the impedance of the input supply. Place the input capacitor as close to the input as possible. See the <i>Input and Output Capacitor Requirements</i> ( $C_{IN}$ and $C_{OUT}$ ) section for more details.                                                                                    |

| NR/SS       | 13        | _   | Noise-reduction and soft-start pin. Connecting an external capacitor between this pin and ground reduces reference voltage noise and also enables the soft-start function. Although not required, a 10-nF or larger capacitor is recommended to be connected from NR/SS to GND (as close to the pin as possible) to maximize ac performance. See the <i>Noise-Reduction and Soft-Start Capacitor</i> (C <sub>NR/SS</sub> ) section for more details. |

| OUT         | 1, 19, 20 | 0   | Regulated output pin. A 47- $\mu$ F or larger ceramic capacitor (25 $\mu$ F or greater of capacitance) from OUT to ground is required for stability and must be placed as close to the output as possible. Minimize the impedance from the OUT pin to the load. See the <i>Input and Output Capacitor Requirements</i> (C <sub>IN</sub> and C <sub>OUT</sub> ) section for more details.                                                             |

| PG          | 4         | ο   | Active-high, power-good pin. An open-drain output indicates when the output voltage reaches 89.3% of the target. The use of a feed-forward capacitor can disrupt PG (power good) functionality. See the <i>Power-Good Function</i> section for more details.                                                                                                                                                                                         |

| SNS 2 I     |           | I   | Output voltage sense input pin. This pin connects the internal $R_1$ resistor to the output. Connect this pin to the load side of the output trace only if the ANY-OUT feature is used. If the ANY-OUT feature is not used, leave this pin floating. See the ANY-OUT Programmable Output Voltage and Adjustable Operation sections for more details.                                                                                                 |

| Thermal pad | -         | -   | Connect the thermal pad to a large-area ground plane. The thermal pad is internally connected to GND.                                                                                                                                                                                                                                                                                                                                                |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over junction temperature range (unless otherwise noted)<sup>(1)</sup>

|             |                                                                | MIN     | MAX                                  | UNIT |

|-------------|----------------------------------------------------------------|---------|--------------------------------------|------|

|             | IN, BIAS, PG, EN                                               | -0.3    | 7.0                                  |      |

|             | IN, BIAS, PG, EN (5% duty cycle, pulse duration = 200 $\mu$ s) | -0.3    | 7.5                                  |      |

| Voltage     | SNS, OUT                                                       | -0.3    | V <sub>IN</sub> + 0.3 <sup>(2)</sup> | V    |

|             | NR/SS, FB                                                      | -0.3    | 3.6                                  |      |

|             | 50mV, 100mV, 200mV, 400mV, 800mV, 1.6V                         | -0.3    | V <sub>OUT</sub> + 0.3               |      |

| Current     | OUT                                                            | Interna | ally limited                         | А    |

| Current     | PG (sink current into device)                                  |         | 5                                    | mA   |

| Temperature | Operating junction, T <sub>J</sub>                             | -55     | 150                                  | °C   |

|             | Storage, T <sub>stg</sub>                                      | -55     | 150                                  | C    |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The absolute maximum rating is  $V_{IN}$  + 0.3 V or 7.0 V, whichever is smaller.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over junction temperature range (unless otherwise noted)

|                    |                                                                    | MIN | NOM                           | MAX                | UNIT |

|--------------------|--------------------------------------------------------------------|-----|-------------------------------|--------------------|------|

| V <sub>IN</sub>    | Input supply voltage range                                         | 1.1 |                               | 6.5                | V    |

| V <sub>BIAS</sub>  | Bias supply voltage range <sup>(1)</sup>                           | 3.0 |                               | 6.5                | V    |

| V <sub>OUT</sub>   | Output voltage range <sup>(2)</sup>                                | 0.8 |                               | 5                  | V    |

| V <sub>EN</sub>    | Enable voltage range                                               | 0   |                               | V <sub>IN</sub>    | V    |

| I <sub>OUT</sub>   | Output current                                                     | 0   |                               | 3                  | А    |

| C <sub>IN</sub>    | Input capacitor                                                    | 10  | 47                            |                    | μF   |

| C <sub>OUT</sub>   | Output capacitor                                                   | 47  | 47    10    10 <sup>(3)</sup> |                    | μF   |

| R <sub>PG</sub>    | Power-good pullup resistance                                       | 10  |                               | 100                | kΩ   |

| C <sub>NR/SS</sub> | NR/SS capacitor                                                    |     | 10                            |                    | nF   |

| C <sub>FF</sub>    | Feed-forward capacitor                                             |     | 10                            |                    | nF   |

| R <sub>1</sub>     | Top resistor value in feedback network for adjustable operation    |     | 12.1 <sup>(4)</sup>           |                    | kΩ   |

| R <sub>2</sub>     | Bottom resistor value in feedback network for adjustable operation |     |                               | 160 <sup>(5)</sup> | kΩ   |

| TJ                 | Operating junction temperature                                     | -40 |                               | 125                | °C   |

(1) BIAS supply is required when the V<sub>IN</sub> supply is below 1.4 V. Conversely, no BIAS supply is required when the V<sub>IN</sub> supply is higher than or equal to 1.4 V. A BIAS supply helps improve dc and ac performance for V<sub>IN</sub> ≤ 2.2 V.

(2) This output voltage range does not include device accuracy or accuracy of the feedback resistors.

(3) The recommended output capacitors are selected to optimize PSRR for the frequency range of 400 kHz to 700 kHz. This frequency range is a typical value for dc-dc supplies.

(4) The 12.1-k $\Omega$  resistor is selected to optimize PSRR and noise by matching the internal R<sub>1</sub> value.

(5) The upper limit for the R<sub>2</sub> resistor is to ensure accuracy by making the current through the feedback network much larger than the leakage current into the feedback node.

# 6.4 Thermal Information

|                       |                                              | TPS7A84    |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGR (VQFN) | UNIT |

|                       |                                              | 20 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 35.4       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 47.6       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 12.3       | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.5        | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 12.4       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.0        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

over operating junction temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ),  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(nom)} + 0.4$  V (whichever is greater),  $V_{BIAS} =$  open,  $V_{OUT(nom)} = 0.8$  V<sup>(2)</sup>, OUT connected to 50  $\Omega$  to GND<sup>(3)</sup>,  $V_{EN} = 1.1$  V,  $C_{IN} = 10$   $\mu$ F,  $C_{OUT} = 47$   $\mu$ F,  $C_{NR/SS}$  without  $C_{FF}$ , and PG pin pulled up to  $V_{IN}$  with 100 k $\Omega$  (unless otherwise noted); typical values are at  $T_J = 25^{\circ}C$

|                                          | PARAMETER                                                                        | 2                           | TEST CONDITIONS                                                                                                                                       | MIN                    | TYP                         | MAX                    | UNIT     |

|------------------------------------------|----------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------|------------------------|----------|

| V <sub>IN</sub>                          | Input supply voltag                                                              | e range <sup>(1)</sup>      |                                                                                                                                                       | 1.1                    |                             | 6.5                    | V        |

| V <sub>BIAS</sub>                        | Bias supply voltage                                                              | e range <sup>(1)</sup>      | V <sub>IN</sub> = 1.1 V                                                                                                                               | 3.0                    |                             | 6.5                    | V        |

| / <sub>FB</sub>                          | Feedback voltage                                                                 |                             |                                                                                                                                                       |                        | 0.8                         |                        | V        |

| V <sub>NR/SS</sub>                       | NR/SS pin voltage                                                                |                             |                                                                                                                                                       |                        | 0.8                         |                        | V        |

| VUVLO1(IN)                               | Input supply UVLO                                                                | with BIAS                   | $V_{IN}$ rising with $V_{BIAS}$ = 3.0 V                                                                                                               |                        | 1.02                        | 1.085                  | V        |

| V <sub>HYS1(IN)</sub>                    | V <sub>UVLO1(IN)</sub> hysteres                                                  | is                          | V <sub>BIAS</sub> = 3.0 V                                                                                                                             |                        | 320                         |                        | mV       |

| V <sub>UVLO2(IN)</sub>                   | Input supply UVLO                                                                | without BIAS                | V <sub>IN</sub> rising                                                                                                                                |                        | 1.31                        | 1.39                   | V        |

| V <sub>HYS2(IN)</sub>                    | V <sub>UVLO2(IN)</sub> hysteres                                                  | is                          |                                                                                                                                                       |                        | 253                         |                        | mV       |

| V <sub>UVLO(BIAS)</sub>                  | Bias supply UVLO                                                                 |                             | V <sub>BIAS</sub> rising, V <sub>IN</sub> = 1.1 V                                                                                                     |                        | 2.83                        | 2.9                    | V        |

| V <sub>HYS(BIAS)</sub>                   | V <sub>UVLO(BIAS)</sub> hystere                                                  | esis                        | V <sub>IN</sub> = 1.1 V                                                                                                                               |                        | 290                         |                        | mV       |

|                                          |                                                                                  | Danga                       | Using the ANY-OUT pins                                                                                                                                | 0.8 – 1.0%             |                             | 3.95 + 1.0%            | V        |

|                                          |                                                                                  | Range                       | Using external resistors <sup>(4)</sup>                                                                                                               | 0.8 – 1.0%             |                             | 5.0 + 1.0%             | v        |

| V <sub>OUT</sub>                         | Output voltage                                                                   | Accuracy <sup>(4) (5)</sup> | $0.8 \text{ V} \le \text{V}_{\text{OUT}} \le 5 \text{ V}, 5 \text{ mA} \le \text{I}_{\text{OUT}} \le 3 \text{ A}, \text{ over } \text{V}_{\text{IN}}$ | -1.0%                  |                             | 1.0%                   |          |

|                                          |                                                                                  | Accuracy with<br>BIAS       | $V_{IN}$ = 1.1 V, 5 mA ≤ $I_{OUT}$ ≤ 3 A,<br>3.0 V ≤ $V_{BIAS}$ ≤ 6.5 V                                                                               | -0.75%                 |                             | 0.75%                  |          |

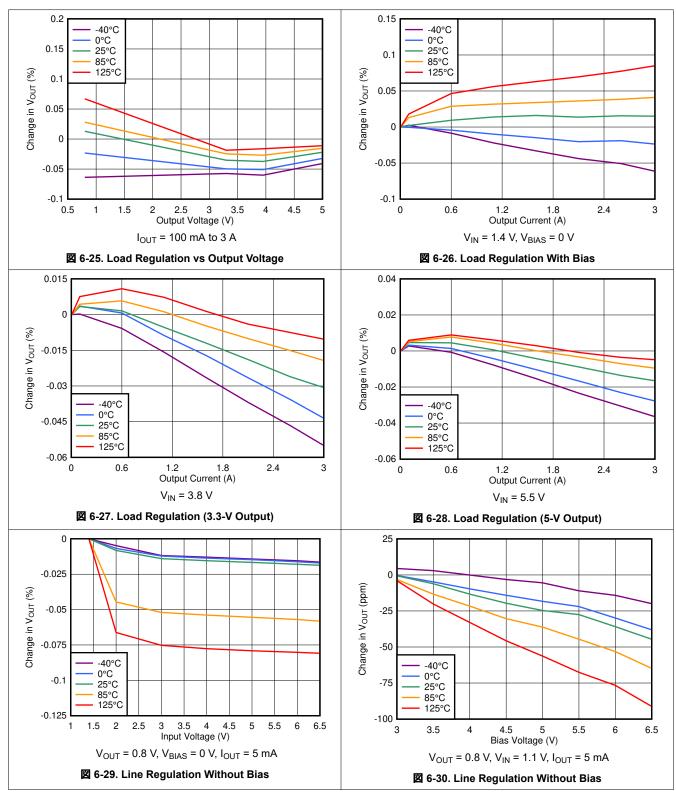

| ΔV <sub>OUT</sub> /<br>ΔV <sub>IN</sub>  | Line regulation                                                                  |                             | I <sub>OUT</sub> = 5 mA, 1.4 V ≤ V <sub>IN</sub> ≤ 6.5 V                                                                                              |                        | 0.0035                      |                        | mV/V     |

| Δ\/ουτ/                                  |                                                                                  |                             | 5 mA $\leq$ I <sub>OUT</sub> $\leq$ 3 A, 3.0 V $\leq$ V <sub>BIAS</sub> $\leq$ 6.5 V, V <sub>IN</sub> = 1.1 V                                         |                        | 0.07                        |                        |          |

| ΔV <sub>OUT</sub> /<br>ΔI <sub>OUT</sub> | Load regulation                                                                  |                             | $5 \text{ mA} \le I_{\text{OUT}} \le 3 \text{ A}$                                                                                                     |                        | 0.08                        |                        | 250 mV/A |

|                                          |                                                                                  |                             | $5 \text{ mA} \le I_{\text{OUT}} \le 3 \text{ A}, \text{ V}_{\text{OUT}} = 5.0 \text{ V}$                                                             |                        | 0.4                         |                        |          |

|                                          |                                                                                  |                             | V <sub>IN</sub> = 1.4 V, I <sub>OUT</sub> = 3 A, V <sub>FB</sub> = 0.8 V – 3%                                                                         |                        | 156                         | 250                    |          |

| Vno                                      | Dropout voltage                                                                  |                             | $V_{\text{IN}}$ = 5.4 V, $I_{\text{OUT}}$ = 3 A, $V_{\text{FB}}$ = 0.8 V $-$ 3%                                                                       |                        | 220                         | 340                    | mV       |

| 50                                       | Load regulation Dropout voltage Output current limit Short-circuit current limit |                             | $V_{IN}$ = 1.1 V, $V_{BIAS}$ = 5.0 V,<br>$I_{OUT}$ = 3 A, $V_{FB}$ = 0.8 V – 3%                                                                       |                        | 110                         | 180                    |          |

| I <sub>LIM</sub>                         | Output current limit                                                             | t                           | $V_{OUT}$ forced at 0.9 × $V_{OUT(nom)}$ ,<br>$V_{IN} = V_{OUT(nom)} + 0.4 V$                                                                         | 3.7                    | 4.2                         | 4.7                    | А        |

| sc                                       | Short-circuit curren                                                             | ıt limit                    | $R_{LOAD} = 20 \text{ m}\Omega$                                                                                                                       |                        | 1.0                         |                        | Α        |

|                                          |                                                                                  |                             | V <sub>IN</sub> = 6.5 V, I <sub>OUT</sub> = 5 mA                                                                                                      |                        | 2.8                         | 4                      | m۸       |

| I <sub>GND</sub>                         | GND pin current                                                                  |                             | V <sub>IN</sub> = 1.4 V, I <sub>OUT</sub> = 3 A                                                                                                       |                        | 4.2                         | 5.5                    | mA       |

|                                          |                                                                                  |                             | Shutdown, PG = open, $V_{IN}$ = 6.5 V, $V_{EN}$ = 0.5 V                                                                                               |                        |                             | 25                     | μA       |

| EN                                       | EN pin current                                                                   |                             | $V_{IN}$ = 6.5 V, $V_{EN}$ = 0 V and 6.5 V                                                                                                            | -0.1                   |                             | 0.1                    | μA       |

| BIAS                                     | BIAS pin current                                                                 |                             | $V_{IN}$ = 1.1 V, $V_{BIAS}$ = 6.5 V,<br>$V_{OUT(nom)}$ = 0.8 V, $I_{OUT}$ = 3 A                                                                      |                        | 2.3                         | 3.5                    | mA       |

| V <sub>IL(EN)</sub>                      | EN pin low-level in<br>(disable device)                                          | put voltage                 |                                                                                                                                                       | 0                      |                             | 0.5                    | V        |

| V <sub>IH(EN)</sub>                      | EN pin high-level ir<br>(enable device)                                          | nput voltage                |                                                                                                                                                       | 1.1                    |                             | 6.5                    | V        |

| V <sub>IT(PG)</sub>                      | PG pin threshold                                                                 |                             | For falling V <sub>OUT</sub>                                                                                                                          | 82% × V <sub>OUT</sub> | 88.3% ×<br>V <sub>OUT</sub> | 93% × V <sub>OUT</sub> | V        |

| V <sub>HYS(PG)</sub>                     | PG pin hysteresis                                                                |                             | For rising V <sub>OUT</sub>                                                                                                                           |                        | 1% × V <sub>OUT</sub>       |                        | V        |

| V <sub>OL(PG)</sub>                      | PG pin low-level ou                                                              | utput voltage               | V <sub>OUT</sub> < V <sub>IT(PG)</sub> , I <sub>PG</sub> = –1 mA<br>(current into device)                                                             |                        |                             | 0.4                    | V        |

| lkg(PG)                                  | PG pin leakage cur                                                               | rrent                       | $V_{OUT}$ > $V_{IT(PG)}$ , $V_{PG}$ = 6.5 V                                                                                                           |                        |                             | 1                      | μA       |

| NR/SS                                    | NR/SS pin charging                                                               | g current                   | V <sub>NR/SS</sub> = GND, V <sub>IN</sub> = 6.5 V                                                                                                     | 4.0                    | 6.2                         | 9.0                    | μA       |

| FB                                       | FB pin leakage cur                                                               | rent                        | V <sub>IN</sub> = 6.5 V                                                                                                                               | -100                   |                             | 100                    | nA       |

# 6.5 Electrical Characteristics (continued)

over operating junction temperature range ( $T_J = -40^{\circ}$ C to +125°C),  $V_{IN} = 1.4$  V or  $V_{IN} = V_{OUT(nom)} + 0.4$  V (whichever is greater),  $V_{BIAS} =$  open,  $V_{OUT(nom)} = 0.8$  V<sup>(2)</sup>, OUT connected to 50  $\Omega$  to GND<sup>(3)</sup>,  $V_{EN} = 1.1$  V,  $C_{IN} = 10$  µF,  $C_{OUT} = 47$  µF,  $C_{NR/SS}$  without  $C_{FF}$ , and PG pin pulled up to  $V_{IN}$  with 100 k $\Omega$  (unless otherwise noted); typical values are at  $T_J = 25^{\circ}$ C

|                                     | PARAMETER                      | TEST CONDIT                                                                                                                                                                                                               | IONS                                                                                                                                                                                                                          | MIN TY | P MAX | UNIT              |  |

|-------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------------------|--|

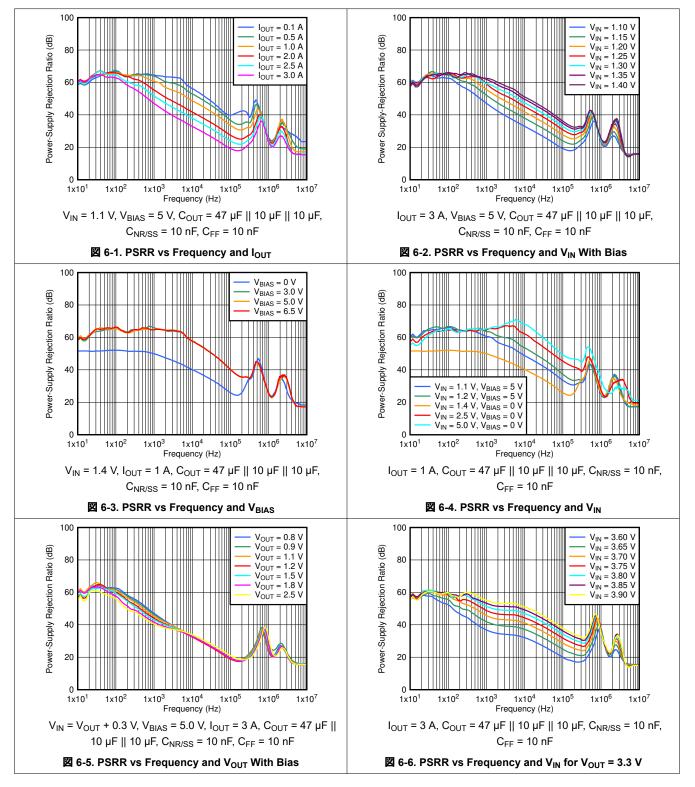

|                                     |                                |                                                                                                                                                                                                                           | f = 10 kHz,<br>V <sub>OUT</sub> = 0.8 V,<br>V <sub>BIAS</sub> = 5.0 V                                                                                                                                                         | 2      | 42    |                   |  |

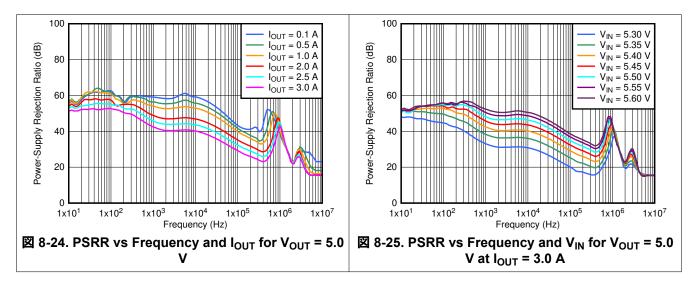

| PSRR                                | Power-supply ripple rejection  | $V_{IN} - V_{O UT} = 0.4 V,$<br>$I_{OUT} = 3 A, C_{NR/SS} = 100 nF,$<br>$C_{FF} = 10 nF, C_{OUT} =$                                                                                                                       | f = 500 kHz, V <sub>OUT</sub><br>= 0.8 V, V <sub>BIAS</sub> =<br>5.0 V                                                                                                                                                        | 3      | 39    | dB                |  |

|                                     |                                | 47 μF    10 μF    10 μF                                                                                                                                                                                                   | f = 10 kHz,<br>V <sub>OUT</sub> = 5.0 V                                                                                                                                                                                       | 2      | 40    |                   |  |

|                                     |                                |                                                                                                                                                                                                                           | f = 500 kHz, V <sub>OUT</sub><br>= 5.0 V                                                                                                                                                                                      | 2      | 25    |                   |  |

| V <sub>n</sub> Output noise voltage |                                | $\begin{array}{l} BW=10\ Hz\ to\ 100\ kHz, V_{IN}=1.1\ V,\\ V_{OUT}=0.8\ V, V_{BIAS}=5.0\ V, I_{OUT}=3\ A,\\ C_{NR/SS}=100\ nF, \ C_{FF}=10\ nF,\\ C_{OUT}=47\ \mu F \parallel 10\ \mu F \parallel 10\ \mu F \end{array}$ |                                                                                                                                                                                                                               | 4      | .4    | μV <sub>RMS</sub> |  |

| • 11                                |                                | ,                                                                                                                                                                                                                         | $\begin{array}{l} BW = 10 \; Hz \; to \; 100 \; kHz, \\ V_{OUT} = 5.0 \; V, \; I_{OUT} = 3 \; A, \; C_{NR/SS} = 100 \; nF, \\ C_{FF} = 10 \; nF, \; C_{OUT} = 47 \; \muF \;    \; 10 \; \muF \;    \; 10 \; \muF \end{array}$ |        | .7    |                   |  |

| <b>-</b>                            |                                | Shutdown, temperature incre                                                                                                                                                                                               | Shutdown, temperature increasing                                                                                                                                                                                              |        | 60    | °C                |  |

| T <sub>sd</sub>                     | Thermal shutdown temperature   | Reset, temperature decreasi                                                                                                                                                                                               | ng                                                                                                                                                                                                                            | 14     | 40    |                   |  |

| TJ                                  | Operating junction temperature |                                                                                                                                                                                                                           |                                                                                                                                                                                                                               | -40    | 125   | °C                |  |

(1) BIAS supply is required when the V<sub>IN</sub> supply is below 1.4 V. Conversely, no BIAS supply is required when the V<sub>IN</sub> supply is higher than or equal to 1.4 V. A BIAS supply helps improve dc and ac performance for V<sub>IN</sub> ≤ 2.2 V.

(2)  $V_{OUT(nom)}$  is the calculated  $V_{OUT}$  target value from the ANY-OUT in a fixed configuration. In an adjustable configuration,  $V_{OUT(nom)}$  is the expected  $V_{OUT}$  value set by the external feedback resistors.

(3) This 50- $\Omega$  load is disconnected when the test conditions specify an I<sub>OUT</sub> value.

(4) When the device is connected to external feedback resistors at the FB pin, external resistor tolerances are not included.

(5) The device is not tested under conditions where  $V_{IN} > V_{OUT} + 1.7 V$  and  $I_{OUT} = 3 A$ , because the power dissipation is higher than the maximum rating of the package.

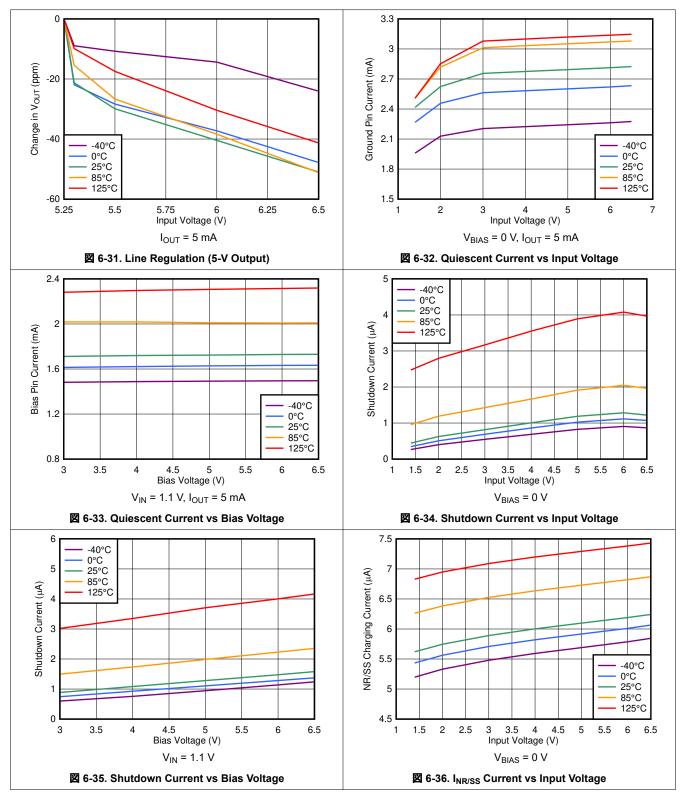

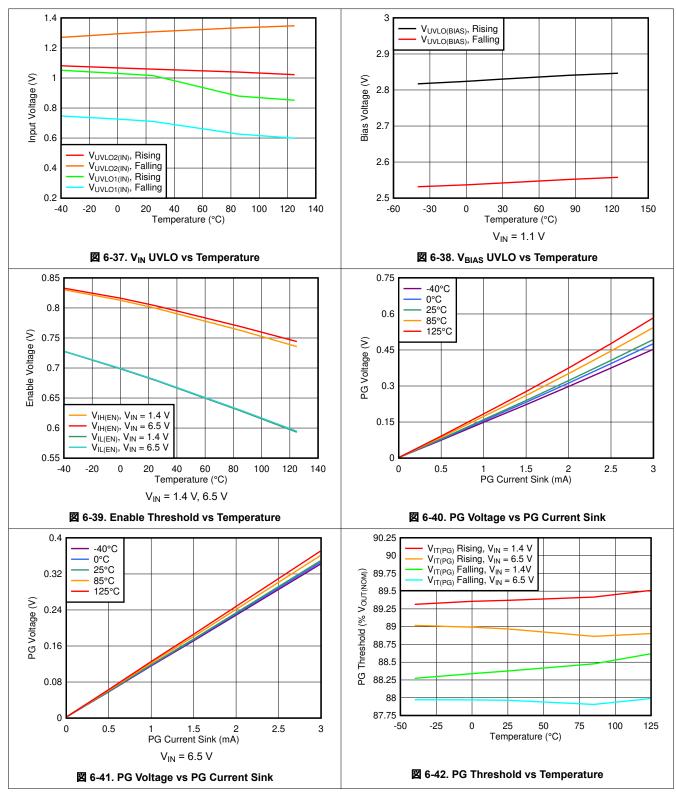

# 6.6 Typical Characteristics

# 7 Detailed Description

# 7.1 Overview

The TPS7A84 is a high-current (3 A), low-noise (4.4  $\mu$ V<sub>RMS</sub>), high accuracy (1%) low-dropout linear voltage regulator (LDO). These features make the device a robust solution to solve many challenging problems in generating a clean, accurate power supply.

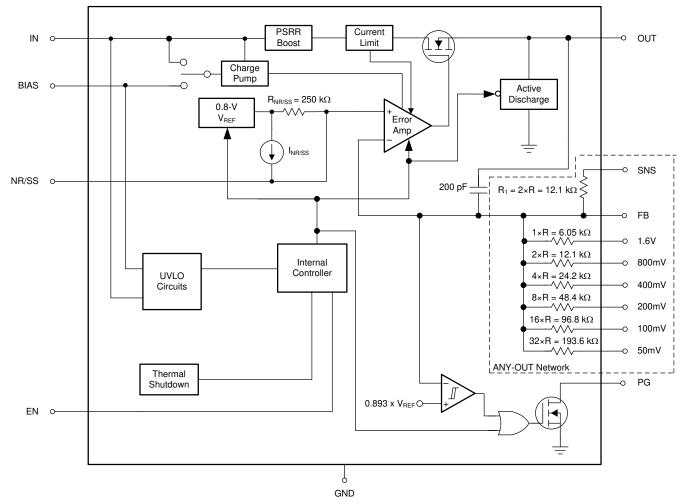

The TPS7A84 has several features that make the device useful in a variety of applications. As detailed in the *Functional Block Diagram* section, these features include:

- Low-noise, high-PSRR output

- ANY-OUT resistor network

- Optional bias rail

- Power-good output

- Programmable soft-start

- Foldback current limit

- Enable circuitry

- · Active discharge

- Thermal protection

Overall, these features make the TPS7A84 the component of choice because of its versatility and ability to generate a supply for most applications.

# 7.2 Functional Block Diagram

For the ANY-OUT network, the ratios between the values are highly accurate as a result of matching, but the actual resistance can vary significantly from the numbers listed.

# 7.3 Feature Description

# 7.3.1 Low-Noise, High-PSRR Output

The TPS7A84 includes a low-noise reference and error amplifier ensuring minimal noise during operation. The NR/SS capacitor ( $C_{NR/SS}$ ) and feed-forward capacitor ( $C_{FF}$ ) are the easiest way to reduce device noise.  $C_{NR/SS}$  filters the noise from the reference and  $C_{FF}$  filters the noise from the error amplifier. The noise contribution from the charge pump is minimal. The overall noise of the system at low output voltages can be reduced by using a bias rail because this rail provides more headroom for internal circuitry.

The high power-supply rejection ratio (PSRR) of the TPS7A84 ensures minimal coupling of input supply noise to the output. The PSRR performance is primarily results from a high-bandwidth, high-gain error amplifier and an innovative circuit to boost the PSRR between 200 kHz and 1 MHz.

The combination of a low noise-floor and high PSRR ensure that the device provides a clean supply to the application; see the *Optimizing Noise and PSRR* section for more information on optimizing the noise and PSRR performance.

# 7.3.2 Integrated Resistance Network (ANY-OUT)

An internal feedback resistance network is provided, allowing the TPS7A84 output voltage to be programmed easily between 0.8 V to 3.95 V with a 50-mV step by tying the ANY-OUT pins to ground. Tying the ANY-OUT pins to SNS increases the resolution but limits the range of the output voltage because the effective value of  $R_1$

is decreased. Use the ANY-OUT network for excellent accuracy across output voltage and temperature; see the *Application and Implementation* section for more details.

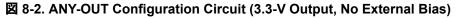

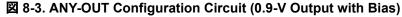

# 7.3.3 Bias Rail

The device features a bias rail to enable low-input voltage, low-output (LILO) voltage operation by providing power to the internal circuitry of the device. The bias rail is required for operation with  $V_{IN}$  < 1.4 V.

An internal power MUX supplies the greater of either the input voltage or the bias voltage to an internal charge pump to power the internal circuitry. Unlike other LDOs that have a bias supply, the TPS7A84 does not have a minimum bias voltage with respect to the input supply because an internal charge pump is used instead.

The internal charge pump multiples the output voltage of the power MUX by a factor of 4 to a maximum of typically 8 V; therefore, using a bias supply with  $V_{IN} \le 2.2$  V is recommended for optimal dc and ac performance. Sequencing requirements exist for when the bias rail is used; see the *Sequencing Requirements* section for more details.

### 7.3.4 Power-Good Function

The power-good circuit monitors the voltage at the feedback pin to indicate the status of the output voltage. When the feedback pin voltage falls below the PG threshold voltage ( $V_{IT(PG)} + V_{HYS(PG)}$ , typically 89.3%), the PG pin open-drain output engages and pulls the PG pin close to GND. When the feedback voltage exceeds the  $V_{IT(PG)}$  threshold by an amount greater than  $V_{HYS(PG)}$  (typically 91.3%), the PG pin becomes high impedance. By connecting a pullup resistor to an external supply, any downstream device can receive power-good as a logic signal that can be used for sequencing. Make sure that the external pullup supply voltage results in a valid logic signal for the receiving device or devices. Using a pullup resistor from 10 k $\Omega$  to 100 k $\Omega$  is recommended. Using an external voltage detector device such as the TPS3702 is also recommended in applications where more accurate voltage monitoring or overvoltage monitoring is required.

The use of a feed-forward capacitor ( $C_{FF}$ ) can cause glitches on start-up, and the power-good circuit may not function normally below the minimum input supply range. For more details on the use of the power-good circuitry, see the *Power-Good Operation* section.

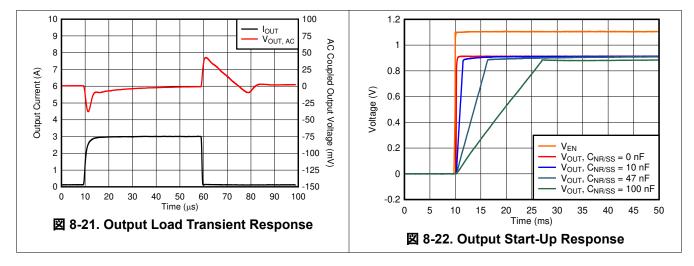

# 7.3.5 Programmable Soft-Start

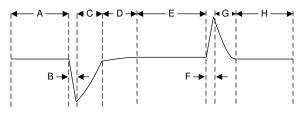

Soft-start refers to the ramp-up time of the output voltage during LDO turn-on after EN and UVLO exceed the respective threshold voltages. The noise-reduction capacitor ( $C_{NR/SS}$ ) serves a dual purpose of both governing output noise reduction and programming the soft-start ramp time during turn-on. The start-up ramp is monotonic.

The majority of the ramp is linear; however, there is an offset voltage in the error amplifier that can cause a small initial jump in output voltage; see the *Application and Implementation* section on implementing a soft-start.

# 7.3.6 Internal Current Limit (I<sub>LIM</sub>)

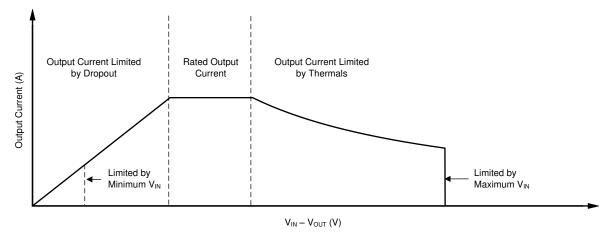

The internal current limit circuit is used to protect the LDO against high-load current faults or shorting events. During a current-limit event, the LDO sources constant current; therefore, the output voltage falls with decreased load impedance. Thermal shutdown can activate during a current limit event because of the high power dissipation typically found in these conditions. To ensure proper operation of the current limit, minimize the inductances to the input and load. Continuous operation in current limit is not recommended.

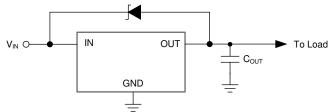

The foldback current limit crosses 0 A when  $V_{OUT} < 0$  V and prevents the device from turning on into a negatively-biased output. See the *Negatively-Biased Output* section on additional ways to ensure start-up when the TPS7A84 output is pulled below ground.

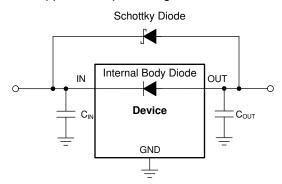

If  $V_{OUT} > V_{IN} + 0.3$  V, then reverse current can flow from the output to the input. The reverse current can cause damage to the device; therefore, limit this reverse current to 10% of the rated output current of the device. See the *Reverse Current Protection* section for more details.

# 7.3.7 Enable

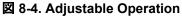

The enable pin for the TPS7A84 is active high. The output of the TPS7A84 is turned on when the enable pin voltage is greater than its rising voltage threshold (1.1 V, max), and the output of the TPS7A84 is turned off when the enable pin voltage is less than its falling voltage threshold (0.5 V, min). A voltage less than 0.5 V on the

enable pin disables all internal circuits. At the next turn-on this voltage ensures a normal start-up waveform with in-rush control, provided there is enough time to discharge the output capacitance.

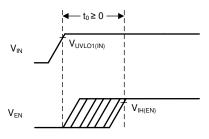

When the enable functionality is not desired, EN must be tied to  $V_{IN}$ . However, when the enable functionality is desired, the enable voltage must come after  $V_{IN}$  is above  $V_{UVLO1(IN)}$  when a BIAS rail is used. See the *Application and Implementation* section for further details.

### 7.3.8 Active Discharge Circuit

The TPS7A84 has an internal pulldown MOSFET that connects a resistance of several hundred ohms to ground when the device is disabled to actively discharge the output voltage when the device is disabled.

Do not rely on the active discharge circuit for discharging a large amount of output capacitance after the input supply has collapsed because reverse current can possibly flow from the output to the input. This reverse current flow can cause damage to the device. Limit reverse current to no more than 5% of the device rated current for a short period of time.

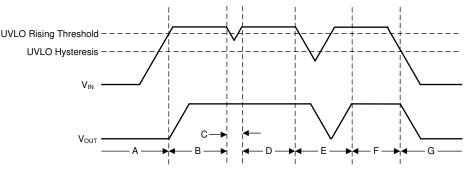

### 7.3.9 Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit monitors the input and bias voltage ( $V_{IN}$  and  $V_{BIAS}$ , respectively) to prevent the device from turning on before  $V_{IN}$  and  $V_{BIAS}$  rise above the lockout voltage. The UVLO circuit also disables the output of the device when  $V_{IN}$  or  $V_{BIAS}$  fall below the lockout voltage. The UVLO circuit responds quickly to glitches on  $V_{IN}$  or  $V_{BIAS}$  and attempts to disable the output of the device if either of these rails collapse. As a result of the fast response time of the input supply UVLO circuit, fast and short line transients well below the input supply UVLO falling threshold can cause momentary glitches when asserted or when recovered from the transient. See the *Application and Implementation* section for more details.

### 7.3.10 Thermal Protection

The TPS7A84 contains a thermal shutdown protection circuit to disable the device when thermal junction temperature ( $T_J$ ) of the main pass-FET exceeds 160°C (typical). Thermal shutdown hysteresis assures that the LDO resets again (turns on) when the temperature falls to 140°C (typical). The thermal time-constant of the semiconductor die is fairly short, and thus the device cycles on and off when thermal shutdown is reached until the power dissipation is reduced.

For reliable operation, limit the junction temperature to a maximum of 125°C. Operation above 125°C can cause the device to exceed its operational specifications. Although the internal protection circuitry of the TPS7A84 is designed to protect against thermal overload conditions, this circuitry is not intended to replace proper heat sinking. Continuously running the TPS7A84 into thermal shutdown or above a junction temperature of 125°C reduces long-term reliability.

# 7.4 Device Functional Modes

# 7.4.1 Operation with 1.1 V $\leq$ V<sub>IN</sub> < 1.4 V

The TPS7A84 requires a bias voltage on the BIAS pin greater than or equal to 3.0 V if the high-current input supply voltage is between 1.1 V to 1.4 V. The bias voltage pin consumes 2.3 mA, nominally.

# 7.4.2 Operation with 1.4 V $\leq$ V\_{IN} $\leq$ 6.5 V

If the input voltage is equal to or exceeds 1.4 V, no BIAS voltage is required. The TPS7A84 is powered from either the input supply or the BIAS supply, whichever is greater. For higher performance, a BIAS rail is recommended for  $V_{IN} \le 2.2$  V.

#### 7.4.3 Shutdown

Shutting down the device reduces the ground current of the device to a maximum of 25  $\mu$ A.

# 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

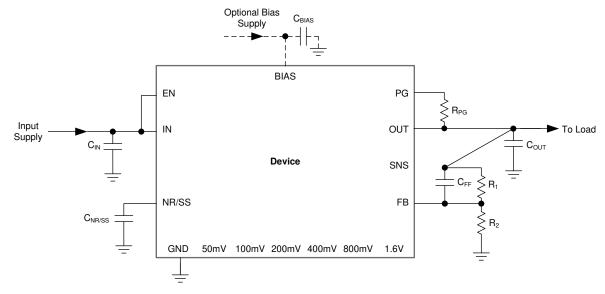

# 8.1 Application Information

The TPS7A84 is a linear voltage regulator with an input range of 1.1 V to 6.5 V and an output voltage range of 0.8 V to 5.0 V with a 1% accuracy and a 3-A maximum output current. The TPS7A84 has an integrated charge pump for ease of use and an external bias rail to allow for the lowest dropout across the entire output voltage range.

#### 8.1.1 Recommended Capacitor Types

The TPS7A84 is designed to be stable using low equivalent series resistance (ESR) ceramic capacitors at the input, output, and noise-reduction pin (NR, pin 13). Multilayer ceramic capacitors have become the industry standard for these types of applications and are recommended, but must be used with good judgment. Ceramic capacitors that employ X7R-, X5R-, and COG-rated dielectric materials provide relatively good capacitive stability across temperature, whereas the use of Y5V-rated capacitors is discouraged because of large variations in capacitance.

Regardless of the ceramic capacitor type selected, ceramic capacitance varies with operating voltage and temperature. As a rule of thumb, derate ceramic capacitors by at least 50%. The input and output capacitors recommended herein account for a capacitance derating of approximately 50%, but at high  $V_{IN}$  and  $V_{OUT}$  conditions (that is,  $V_{IN} = 5.5$  V to  $V_{OUT} = 5.0$  V) the derating can be greater than 50% and must be taken into consideration.

# 8.1.2 Input and Output Capacitor Requirements (CIN and COUT)

The TPS7A84 is designed and characterized for operation with ceramic capacitors of 47  $\mu$ F or greater (22  $\mu$ F or greater of capacitance) at the output and 10  $\mu$ F or greater (5  $\mu$ F or greater of capacitance) at the input. Using at least a 47- $\mu$ F capacitor is highly recommended at the input to minimize input impedance. Place the input and output capacitors as near as practical to the respective input and output pins to minimize trace parasitics. If the trace inductance from the input supply to the TPS7A84 is high, a fast current transient can cause V<sub>IN</sub> to ring above the absolute maximum voltage rating and damage the device. This situation can be mitigated by additional input capacitors to dampen the ringing and to keep it below the device absolute maximum ratings.

A combination of multiple output capacitors boosts the high-frequency PSRR, as illustrated in several of the PSRR curves. The combination of one 0805-sized, 47-µF ceramic capacitor in parallel with two 0805-sized,

10- $\mu$ F ceramic capacitors with a sufficient voltage rating in conjunction with the PSRR boost circuit optimizes PSRR for the frequency range of 400 kHz to 700 kHz, a typical range for dc-dc supply switching frequency. This 47- $\mu$ F || 10- $\mu$ F || 10- $\mu$ F combination also ensures that at high input voltage and high output voltage configurations, the minimum effective capacitance is met. Many 0805-sized, 47- $\mu$ F ceramic capacitors have a voltage derating of approximately 60% to 80% at 5.0 V, so the addition of the two 10- $\mu$ F capacitors ensures that the capacitance is at or above 22  $\mu$ F.

#### 8.1.3 Noise-Reduction and Soft-Start Capacitor (C<sub>NR/SS</sub>)

The TPS7A84 features a programmable, monotonic, voltage-controlled soft-start that is set with an external capacitor ( $C_{NR/SS}$ ). The use of an external  $C_{NR/SS}$  is highly recommended, especially to minimize in-rush current into the output capacitors. This soft-start eliminates power-up initialization problems when powering field-programmable gate arrays (FPGAs), digital signal processors (DSPs), or other processors. The controlled voltage ramp of the output also reduces peak in-rush current during start-up, minimizing start-up transients to the input power bus.

To achieve a monotonic start-up, the TPS7A84 error amplifier tracks the voltage ramp of the external soft-start capacitor until the voltage approaches the internal reference. The soft-start ramp time depends on the soft-start charging current ( $I_{NR/SS}$ ), the soft-start capacitance ( $C_{NR/SS}$ ), and the internal reference ( $V_{NR/SS}$ ). Soft-start ramp time can be calculated with  $\overrightarrow{$  1:

$t_{SS} = (V_{NR/SS} \times C_{NR/SS}) / I_{NR/SS}$

Note that I<sub>NR/SS</sub> is provided in the *Electrical Characteristics* table and has a typical value of 6.2 µA.

The noise-reduction capacitor, in conjunction with the noise-reduction resistor, forms a low-pass filter (LPF) that filters out the noise from the reference before being gained up with the error amplifier, thereby reducing the device noise floor. The LPF is a single-pole filter and the cutoff frequency can be calculated with  $\gtrsim 2$ . The typical value of  $R_{NR}$  is 250 k $\Omega$ . Increasing the  $C_{NR/SS}$  capacitor has a greater affect because the output voltage increases when the noise from the reference is gained up even more at higher output voltages. For low-noise applications, a 10-nF to 1-µF  $C_{NR/SS}$  is recommended.

$f_{cutoff} = 1/(2 \times \pi \times R_{NR} \times C_{NR/SS})$

# 8.1.4 Feed-Forward Capacitor (C<sub>FF</sub>)

Although a feed-forward capacitor ( $C_{FF}$ ) from the FB pin to the OUT pin is not required to achieve stability, a 10-nF external feed-forward capacitor optimizes the transient, noise, and PSRR performance. A higher capacitance  $C_{FF}$  can be used; however, the start-up time is longer and the power-good signal can incorrectly indicate that the output voltage is settled. For a detailed description, see the *Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator* application report.

#### 8.1.5 Soft-Start and In-Rush Current

Soft-start refers to the ramp-up characteristic of the output voltage during LDO turn-on after EN and UVLO achieve threshold voltage. The noise-reduction capacitor serves a dual purpose of both governing output noise reduction and programming the soft-start ramp during turn-on.

In-rush current is defined as the current into the LDO at the IN pin during start-up. In-rush current then consists primarily of the sum of load current and the current used to charge the output capacitor. This current is difficult to measure because the input capacitor must be removed, which is not recommended. However, this soft-start current can be estimated by  $\vec{x}$  3:

$$I_{OUT(t)} = \left[\frac{C_{OUT} \times dV_{OUT}(t)}{dt}\right] + \left[\frac{V_{OUT}(t)}{R_{LOAD}}\right]$$

where:

- V<sub>OUT</sub>(t) is the instantaneous output voltage of the turn-on ramp

- dV<sub>OUT</sub>(t) / dt is the slope of the V<sub>OUT</sub> ramp

- R<sub>LOAD</sub> is the resistive load impedance

# 8.1.6 Optimizing Noise and PSRR

The ultra-low noise floor and PSRR of the device can be improved by careful selection of:

- C<sub>NR/SS</sub> for the low-frequency range

- C<sub>FF</sub> in the mid-band frequency range

- C<sub>OUT</sub> for the high-frequency range

- V<sub>IN</sub> V<sub>OUT</sub> for all frequencies, and

- V<sub>BIAS</sub> at lower input voltages

A larger noise-reduction capacitor improves low-frequency PSRR by filtering any noise coupling from the input into the reference. The feed-forward capacitor can be optimized to place a pole-zero pair near the edge of the loop bandwidth and push out the loop bandwidth, thus improving mid-band PSRR. Larger output capacitors and various output capacitors can be used to improve high-frequency PSRR.

(1)

(2)

(3)

A higher input voltage improves the PSRR by giving the device more headroom to respond to noise on the input; see the  $\cancel{2}$  6-2 curve. A bias rail also improves the PSRR at lower input voltages because greater headroom is provided for the internal circuits.

The noise-reduction capacitor filters out low-frequency noise from the reference and the feed-forward capacitor reduces output voltage noise by filtering out the mid-band frequency noise. However, a large feed-forward capacitor can create some new issues that are discussed in the *Pros and Cons of Using a Feed-Forward Capacitor with a Low Dropout Regulator* application report.

A large output capacitor reduces high-frequency output voltage noise. Additionally, a bias rail or higher input voltage improves the noise because greater headroom is provided for the internal circuits.

$\pm$  8-1 lists the output voltage noise for the 10-Hz to 100-kHz band at a 5.0-V output for a variety of conditions with an input voltage of 5.4 V, an R<sub>1</sub> of 12.1 kΩ, and a load current of 3 A. The 5.0-V output is chosen because this output is the worst-case condition for output voltage noise.

| OUTPUT VOLTAGE NOISE<br>(μV <sub>RMS</sub> ) | C <sub>NR/SS</sub> (nF) | C <sub>FF</sub> (nF) | C <sub>OUT</sub> (μF) |

|----------------------------------------------|-------------------------|----------------------|-----------------------|

| 11.7                                         | 10                      | 10                   | 47    10    10        |

| 7.7                                          | 100                     | 10                   | 47    10    10        |

| 6                                            | 100                     | 100                  | 47    10    10        |

| 7.4                                          | 100                     | 10                   | 1000                  |

| 5.8                                          | 100                     | 100                  | 1000                  |

表 8-1. Output Noise Voltage at a 5.0-V Output

# 8.1.7 Charge Pump Noise

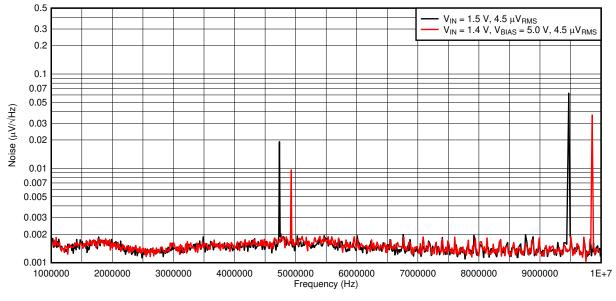

The device internal charge pump generates a minimal amount of noise, as shown in  $\boxtimes$  8-1.

Using a bias rail minimizes the internal charge pump noise when the internal voltage is clamped, thereby reducing the overall output noise floor.

The high-frequency components of the output voltage noise density curve are filtered out in most applications by using 10-nF to 100-nF bypass capacitors close to the load. Using a ferrite bead between the LDO output and the load input capacitors forms a pi-filter, further reducing the high-frequency noise contribution.

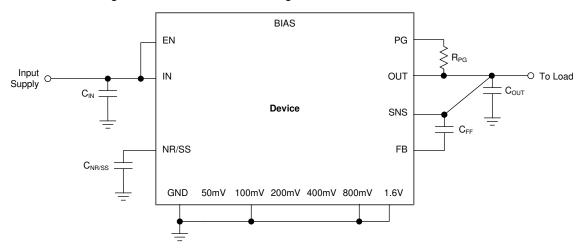

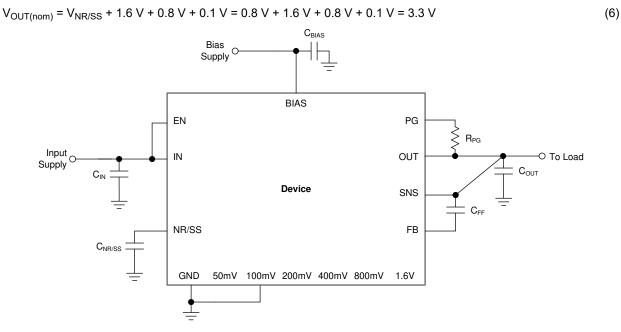

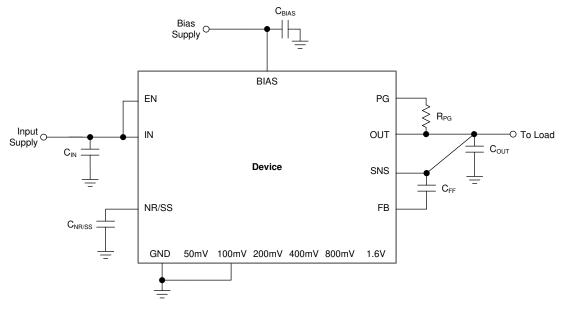

### 8.1.8 ANY-OUT Programmable Output Voltage

The TPS7A84 can use either external resistors or the internally-matched ANY-OUT feedback resistor network to set output voltage. The ANY-OUT resistors are accessible via pin 2 and pins 5 to 11 and are used to program the regulated output voltage. Each pin is can be connected to ground (active) or left open (floating), or connected to SNS. ANY-OUT programming is set by  $\pm$  4 as the sum of the internal reference voltage (V<sub>NR/SS</sub> = 0.8 V) plus the accumulated sum of the respective voltages assigned to each active pin; that is, 50mV (pin 5), 100mV (pin 6), 200mV (pin 7), 400mV (pin 9), 800mV (pin 10), or 1.6V (pin 11).  $\pm$  8-2 summarizes these voltage values associated with each active pin setting for reference. By leaving all program pins open or floating, the output is thereby programmed to the minimum possible output voltage equal to V<sub>FB</sub>.

$V_{OUT} = V_{NR/SS} + (\Sigma ANY-OUT Pins to Ground)$

(4)

| ANY-OUT PROGRAM PINS (Active Low) | ADDITIVE OUTPUT VOLTAGE LEVEL |  |

|-----------------------------------|-------------------------------|--|

| Pin 5 (50mV)                      | 50 mV                         |  |

| Pin 6 (100mV)                     | 100 mV                        |  |

| Pin 7 (200mV)                     | 200 mV                        |  |

| Pin 9 (400mV)                     | 400 mV                        |  |

| Pin 10 (800mV)                    | 800 mV                        |  |

| Pin 11 (1.6V)                     | 1.6 V                         |  |

表 8-2 ANV-OUT Programmable Output Voltage

$\frac{1}{8}$  8-3 provides a full list of target output voltages and corresponding pin settings when the ANY-OUT pins are only tied to ground or left floating. The voltage setting pins have a binary weight; therefore, the output voltage can be programmed to any value from 0.8 V to 3.95 V in 50-mV steps when tying these pins to ground. There are several alternative ways to set the output voltage. The program pins can be driven using external general-purpose input/output pins (GPIOs), manually connected using 0-Ω resistors (or left open), or hardwired by the given layout of the printed circuit board (PCB) to set the ANY-OUT voltage. As with the adjustable operation, the output voltage is set according to  $\pm$  5 except that R<sub>1</sub> and R<sub>2</sub> are internally integrated and matched for higher accuracy. Tying any of the ANY-OUT pins to SNS can increase the resolution of the internal feedback network by lowering the value of R<sub>1</sub>. See the *Increasing ANY-OUT Resolution for LILO Conditions* section for additional information.

$V_{OUT} = V_{NR/SS} \times (1 + R_1 / R_2)$

(5)

#### Note

For output voltages greater than 3.95 V, use a traditional adjustable configuration (see the *Adjustable Operation* section).

| 表 8-3. User-Configurable Output Voltage Settings |      |       |       |       |       |      |  |                              |      |       |       |       |       |      |

|--------------------------------------------------|------|-------|-------|-------|-------|------|--|------------------------------|------|-------|-------|-------|-------|------|

| V <sub>OUT(NOM)</sub><br>(V)                     | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |  | V <sub>OUT(NOM)</sub><br>(V) | 50mV | 100mV | 200mV | 400mV | 800mV | 1.6V |

| 0.80                                             | Open | Open  | Open  | Open  | Open  | Open |  | 2.40                         | Open | Open  | Open  | Open  | Open  | GND  |

| 0.85                                             | GND  | Open  | Open  | Open  | Open  | Open |  | 2.45                         | GND  | Open  | Open  | Open  | Open  | GND  |

| 0.90                                             | Open | GND   | Open  | Open  | Open  | Open |  | 2.50                         | Open | GND   | Open  | Open  | Open  | GND  |

| 0.95                                             | GND  | GND   | Open  | Open  | Open  | Open |  | 2.55                         | GND  | GND   | Open  | Open  | Open  | GND  |

| 1.00                                             | Open | Open  | GND   | Open  | Open  | Open |  | 2.60                         | Open | Open  | GND   | Open  | Open  | GND  |

| 1.05                                             | GND  | Open  | GND   | Open  | Open  | Open |  | 2.65                         | GND  | Open  | GND   | Open  | Open  | GND  |

| 1.10                                             | Open | GND   | GND   | Open  | Open  | Open |  | 2.70                         | Open | GND   | GND   | Open  | Open  | GND  |

| 1.15                                             | GND  | GND   | GND   | Open  | Open  | Open |  | 2.75                         | GND  | GND   | GND   | Open  | Open  | GND  |

| 1.20                                             | Open | Open  | Open  | GND   | Open  | Open |  | 2.80                         | Open | Open  | Open  | GND   | Open  | GND  |

| 1.25                                             | GND  | Open  | Open  | GND   | Open  | Open |  | 2.85                         | GND  | Open  | Open  | GND   | Open  | GND  |

| 1.30                                             | Open | GND   | Open  | GND   | Open  | Open |  | 2.90                         | Open | GND   | Open  | GND   | Open  | GND  |

| 1.35                                             | GND  | GND   | Open  | GND   | Open  | Open |  | 2.95                         | GND  | GND   | Open  | GND   | Open  | GND  |

| 1.40                                             | Open | Open  | GND   | GND   | Open  | Open |  | 3.00                         | Open | Open  | GND   | GND   | Open  | GND  |

| 1.45                                             | GND  | Open  | GND   | GND   | Open  | Open |  | 3.05                         | GND  | Open  | GND   | GND   | Open  | GND  |

| 1.50                                             | Open | GND   | GND   | GND   | Open  | Open |  | 3.10                         | Open | GND   | GND   | GND   | Open  | GND  |

| 1.55                                             | GND  | GND   | GND   | GND   | Open  | Open |  | 3.15                         | GND  | GND   | GND   | GND   | Open  | GND  |

| 1.60                                             | Open | Open  | Open  | Open  | GND   | Open |  | 3.20                         | Open | Open  | Open  | Open  | GND   | GND  |

| 1.65                                             | GND  | Open  | Open  | Open  | GND   | Open |  | 3.25                         | GND  | Open  | Open  | Open  | GND   | GND  |

| 1.70                                             | Open | GND   | Open  | Open  | GND   | Open |  | 3.30                         | Open | GND   | Open  | Open  | GND   | GND  |

| 1.75                                             | GND  | GND   | Open  | Open  | GND   | Open |  | 3.35                         | GND  | GND   | Open  | Open  | GND   | GND  |

| 1.80                                             | Open | Open  | GND   | Open  | GND   | Open |  | 3.40                         | Open | Open  | GND   | Open  | GND   | GND  |

| 1.85                                             | GND  | Open  | GND   | Open  | GND   | Open |  | 3.45                         | GND  | Open  | GND   | Open  | GND   | GND  |

| 1.90                                             | Open | GND   | GND   | Open  | GND   | Open |  | 3.50                         | Open | GND   | GND   | Open  | GND   | GND  |

| 1.95                                             | GND  | GND   | GND   | Open  | GND   | Open |  | 3.55                         | GND  | GND   | GND   | Open  | GND   | GND  |

| 2.00                                             | Open | Open  | Open  | GND   | GND   | Open |  | 3.60                         | Open | Open  | Open  | GND   | GND   | GND  |

| 2.05                                             | GND  | Open  | Open  | GND   | GND   | Open |  | 3.65                         | GND  | Open  | Open  | GND   | GND   | GND  |

| 2.10                                             | Open | GND   | Open  | GND   | GND   | Open |  | 3.70                         | Open | GND   | Open  | GND   | GND   | GND  |

| 2.15                                             | GND  | GND   | Open  | GND   | GND   | Open |  | 3.75                         | GND  | GND   | Open  | GND   | GND   | GND  |

| 2.20                                             | Open | Open  | GND   | GND   | GND   | Open |  | 3.80                         | Open | Open  | GND   | GND   | GND   | GND  |