Order

Now

Support & Community

## TUSB3410, TUSB3410I

Reference

Desian

SLLS519J-MARCH 2002-REVISED JULY 2017

# TUSB3410 USB to Serial Port Controller

#### **Device Overview** 1

#### **Features** 1.1

- Fully Compliant With USB 2.0 Full-Speed Specifications: TID#40340262

- Supports 12-Mbps USB Data Rate (Full Speed)

- Supports USB Suspend, Resume, and Remote Wake-Up Operations

- Configurable to Bus-Powered and Self-Powered Operation

- Supports a Total of Three Input and Three Output (Interrupt, Bulk) Endpoints

- Integrated 8052 Microcontroller With:

- 256 × 8 RAM for Internal Data

- 10K  $\times$  8 ROM (With USB and I<sup>2</sup>C Bootloader)

- 16K × 8 RAM for Code Space Loadable From Host or I<sup>2</sup>C Port

- 2K x 8 Shared RAM Used for Data Buffers and Endpoint Descriptor Blocks (EDBs)

- Master I<sup>2</sup>C Controller for EEPROM Device Access

- MCU Operates at 24 MHz, Providing 2-MIPS Operation

- 128-ms Watchdog Timer

#### 1.2 Applications

- Modems

- Peripherals:

Printers, Handheld Devices, and so on

#### 1.3 Description

- **Enhanced UART Features:**

- Software and Hardware Flow Control

- Automatic RS-485 Bus Transceiver Control, With and Without Echo

- Selectable IrDA Mode for Up to 115.2-kbps Transfer

- Software-Selectable Baud Rate From 50 BPS to 921.6 kbps

- Programmable Serial-Interface Characteristics

- 5-, 6-, 7-, or 8-Bit Characters

- Even, Odd, or No Parity-bit Generation and Detection

- 1-, 1.5-, or 2-Stop Bit Generation

- Line Break Generation and Detection

- Internal Test and Loopback Capabilities

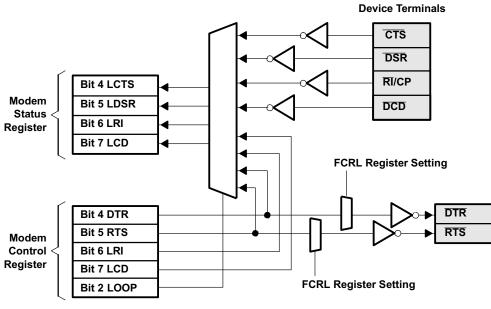

- Modem Control Functions (CTS, RTS, DSR, RI and DCD)

- Internal Diagnostic Capability

- Loopback Control for Communications Link-Fault Isolation

- Break, Parity, Overrun, Framing-Error Simulation

- Medical Meters

- DSP and µC Interface

- The TUSB3410 device provides bridging between a USB port and an enhanced UART serial port. The device contains an 8052 microcontroller unit (MCU) with 16KB of RAM that can be loaded from the host or from the external onboard memory through an I<sup>2</sup>C. The device also contains 10KB of ROM that allows the MCU to configure the USB port at boot time. The ROM code also contains an I<sup>2</sup>C bootloader. All device functions (such as the USB command decoding, UART setup, and error reporting) are managed by the internal MCU firmware in unison with the PC host.

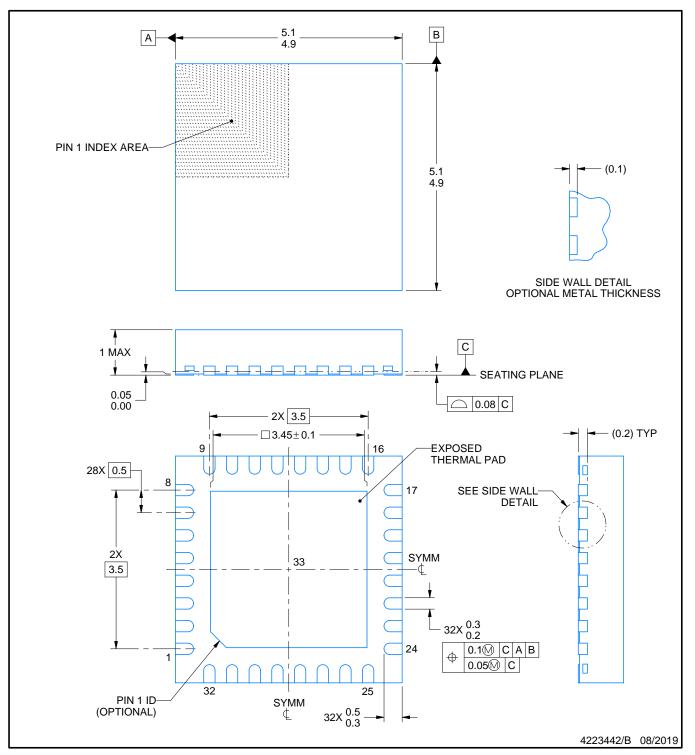

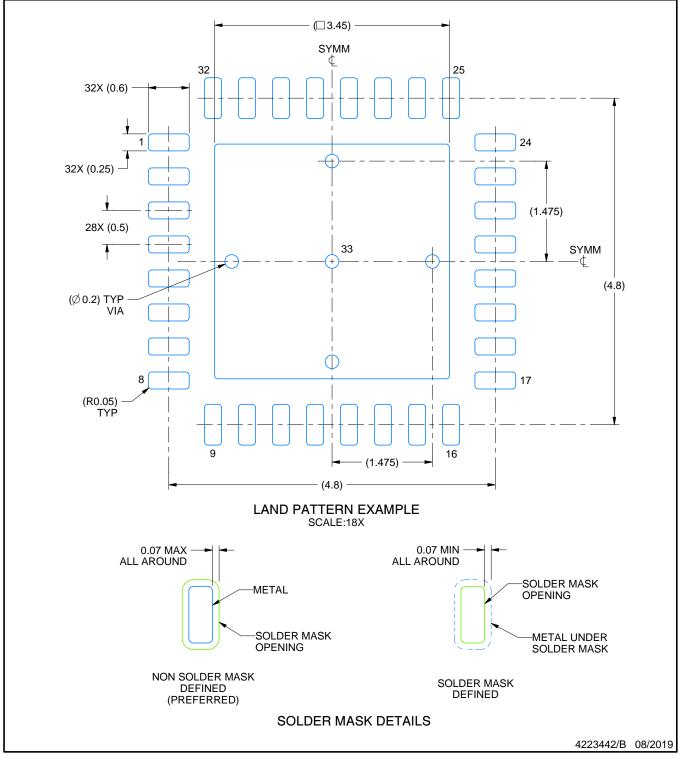

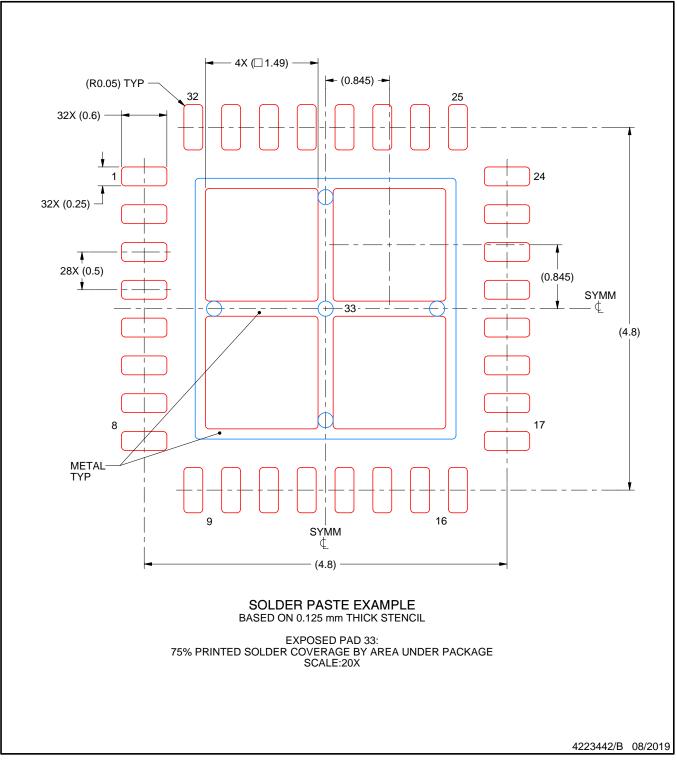

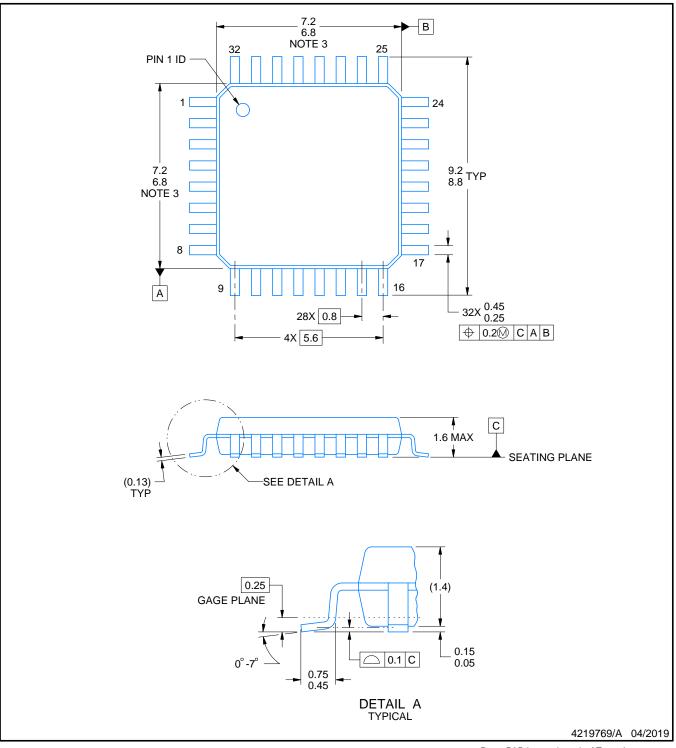

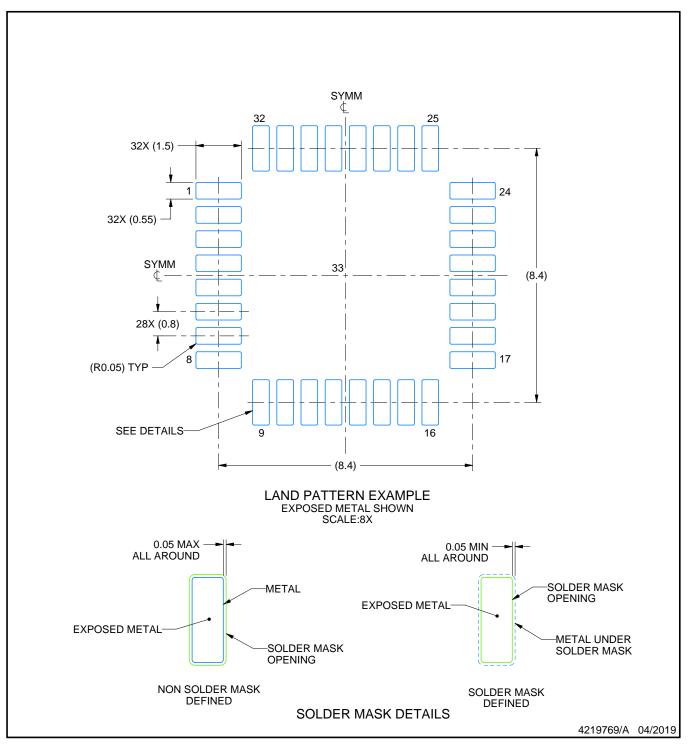

| Device Information |           |                   |  |  |  |  |

|--------------------|-----------|-------------------|--|--|--|--|

| PART NUMBER        | BODY SIZE |                   |  |  |  |  |

| TUSP2440           | VQFN (32) | 5.00 mm × 5.00 mm |  |  |  |  |

| TUSB3410           | LQFP (32) | 7.00 mm × 7.00 mm |  |  |  |  |

1. For all available packages, see the orderable addendum at the end of the data sheet.

TUSB3410, TUSB3410I SLLS519J-MARCH 2002-REVISED JULY 2017

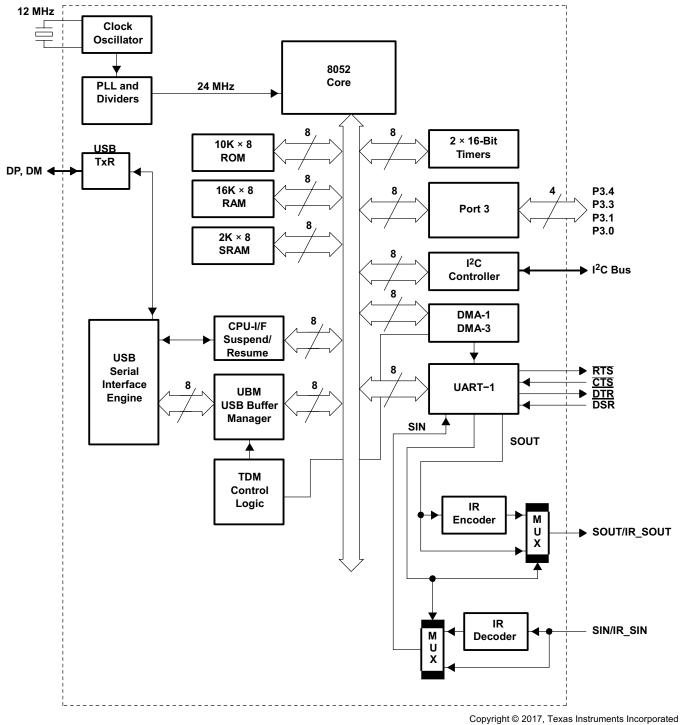

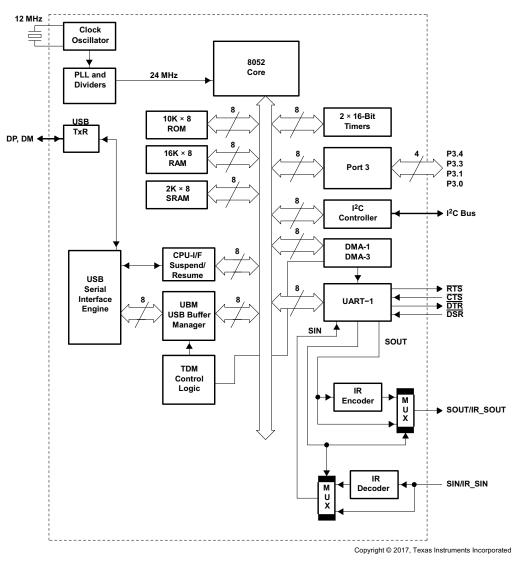

#### 1.4 Functional Block Diagram

Copyright © 2002–2017, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Dev  | ice Overview <u>1</u>                              |

|---|------|----------------------------------------------------|

|   | 1.1  | Features <u>1</u>                                  |

|   | 1.2  | Applications                                       |

|   | 1.3  | Description 1                                      |

|   | 1.4  | Functional Block Diagram 2                         |

| 2 | Rev  | ision History <u>3</u>                             |

| 3 | Pin  | Configuration and Functions 4                      |

|   | 3.1  | Pin Diagrams 4                                     |

| 4 | Spe  | cifications <u>6</u>                               |

|   | 4.1  | Absolute Maximum Ratings 6                         |

|   | 4.2  | ESD Ratings                                        |

|   | 4.3  | Recommended Operating Conditions                   |

|   | 4.4  | Thermal Information 6                              |

|   | 4.5  | Electrical Characteristics 7                       |

|   | 4.6  | Timing and Switching Characteristics Information 8 |

|   | 4.7  | Typical Characteristics 9                          |

| 5 | Deta | iled Description <u>10</u>                         |

|   | 5.1  | Overview <u>10</u>                                 |

|   | 5.2  | Functional Block Diagram 11                        |

|   | 5.3  | Device Functional Modes 11                         |

|   | 5.4  | Processor Subsystems <u>16</u>                     |

|   |      |                                                    |

|   | 5.5   | Memory                                             | <u>24</u> |

|---|-------|----------------------------------------------------|-----------|

|   | 5.6   | Boot Modes                                         | <u>67</u> |

| 6 | Appl  | ication, Implementation, and Layout                | <u>84</u> |

|   | 6.1   | Application Information                            | <u>84</u> |

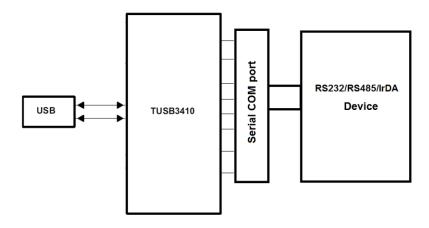

|   | 6.2   | Typical Application                                | <u>84</u> |

|   | 6.3   | Layout                                             | <u>88</u> |

|   | 6.4   | Power Supply Recommendations                       | <u>90</u> |

|   | 6.5   | Crystal Selection                                  | <u>90</u> |

|   | 6.6   | External Circuit Required for Reliable Bus Powered |           |

|   |       | Suspend Operation                                  | <u>91</u> |

| 7 | Devi  | ce and Documentation Support                       | <u>92</u> |

|   | 7.1   | Documentation Support                              | <u>92</u> |

|   | 7.2   | Related Links                                      | <u>92</u> |

|   | 7.3   | Receiving Notification of Documentation Updates    | <u>92</u> |

|   | 7.4   | Community Resources                                | <u>92</u> |

|   | 7.5   | Trademarks                                         | <u>92</u> |

|   | 7.6   | Electrostatic Discharge Caution                    | <u>92</u> |

|   | 7.7   | Glossary                                           | <u>92</u> |

| 8 | Mech  | nanical Packaging and Orderable                    |           |

|   | Infor | mation                                             | <u>93</u> |

|   | 8.1   | Packaging Information                              | <u>93</u> |

|   |       |                                                    |           |

#### **Revision History** 2

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision I (November 2015) to Revision J                                                                                                                              | Page      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Changed pin 21 From: DTR To: active low DTR in the Pin Functions table                                                                                                             | <u>5</u>  |

| <ul> <li>Changed the description of bit 7 CONT in USBCTL: USB Control Register (Addr:FFFCh), CONT= 0 From:<br/>enabled To: disables, CONT= 1 From: disbaled To: enabled</li> </ul> | <u>40</u> |

| -                                                                                                                                                                                  |           |

#### Changes from Revision H (April 2013) to Revision I

| • | Added Pin Configuration and Functions section, ESD Ratings table, Thermal Information table, Typical          |   |

|---|---------------------------------------------------------------------------------------------------------------|---|

|   | Characteristics section, Feature Description section, Device Functional Modes, Application and Implementation |   |

|   | section, Power Supply Recommendations section, Layout section, Device and Documentation Support section,      |   |

|   | and Mechanical, Packaging, and Orderable Information section                                                  | 1 |

| • | Deleted Ordering Information table.                                                                           | 1 |

#### Page

# STRUMENTS

www.ti.com

# 3 Pin Configuration and Functions

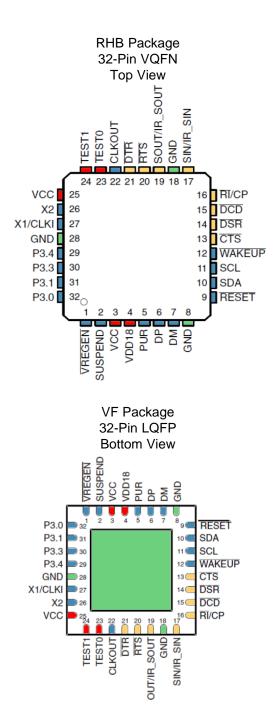

#### 3.1 Pin Diagrams

RUMENTS www.ti.com

#### **Pin Functions**

| PIN          |           | 1/0 | DESCRIPTION                                                                                                                                                    |

|--------------|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME         | NO.       | I/O | DESCRIPTION                                                                                                                                                    |

| CLKOUT       | 22        | 0   | Clock output (controlled by bits 2 (CLKOUTEN) and 3(CLKSLCT) in the MODECNFG register (see <sup>(1)</sup> and Section 5.5.5.5)                                 |

| CTS          | 13        | Ι   | UART: Clear to send <sup>(2)</sup>                                                                                                                             |

| DCD          | 15        | Ι   | UART: Data carrier detect <sup>(2)</sup>                                                                                                                       |

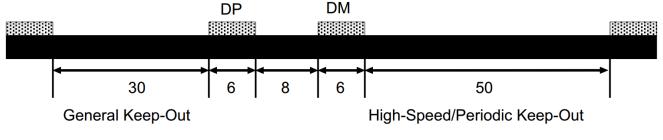

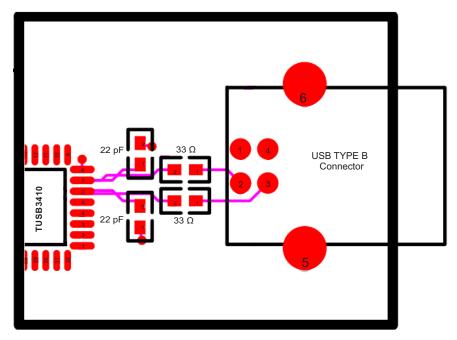

| DM           | 7         | I/O | Upstream USB port differential data minus                                                                                                                      |

| DP           | 6         | I/O | Upstream USB port differential data plus                                                                                                                       |

| DSR          | 14        | Ι   | UART: Data set ready <sup>(2)</sup>                                                                                                                            |

| DTR          | 21        | 0   | UART: Data terminal ready <sup>(1)</sup>                                                                                                                       |

| GND          | 8, 18, 28 | GND | Digital ground                                                                                                                                                 |

| P3.0         | 32        | I/O | General-purpose I/O 0 (port 3, terminal 0) <sup>(3)(4)(5)</sup>                                                                                                |

| P3.1         | 31        | I/O | General-purpose I/O 1 (port 3, terminal 1) <sup>(3)(4)(5)</sup>                                                                                                |

| P3.3         | 30        | I/O | General-purpose I/O 3 (port 3, terminal 3) <sup>(3)(4)(5)</sup>                                                                                                |

| P3.4         | 29        | I/O | General-purpose I/O 4 (port 3, terminal 4) <sup>(3)(4)(5)</sup>                                                                                                |

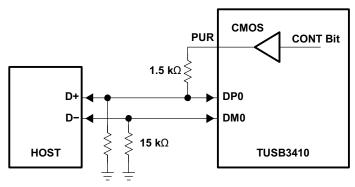

| PUR          | 5         | 0   | Pullup resistor connection <sup>(6)</sup>                                                                                                                      |

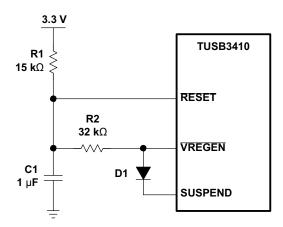

| RESET        | 9         | Ι   | Device master reset input <sup>(2)</sup>                                                                                                                       |

| RI/CP        | 16        | Ι   | UART: Ring indicator <sup>(2)</sup>                                                                                                                            |

| RTS          | 20        | 0   | UART: Request to send <sup>(1)</sup>                                                                                                                           |

| SCL          | 11        | 0   | Master I <sup>2</sup> C controller: clock signal <sup>(1)</sup>                                                                                                |

| SDA          | 10        | I/O | Master I <sup>2</sup> C controller: data signal <sup>(1)(4)</sup>                                                                                              |

| SIN/IR_SIN   | 17        | Ι   | UART: Serial input data / IR Serial data input <sup>(7)</sup>                                                                                                  |

| SOUT/IR_SOUT | 19        | 0   | UART: Serial output data / IR Serial data output <sup>(8)</sup>                                                                                                |

| SUSPEND      | 2         | 0   | Suspend indicator terminal <sup>(3)</sup> . When this terminal is asserted high, the device is in suspend mode.                                                |

| TEST0        | 23        | Ι   | Test input (for factory test only). This terminal must be tied to VCC through a 10-k $\Omega$ resistor.                                                        |

| TEST1        | 24        | Ι   | Test input (for factory test only) <sup>(4)</sup> . This terminal must be tied to VCC through a 10-k $\Omega$ resistor.                                        |

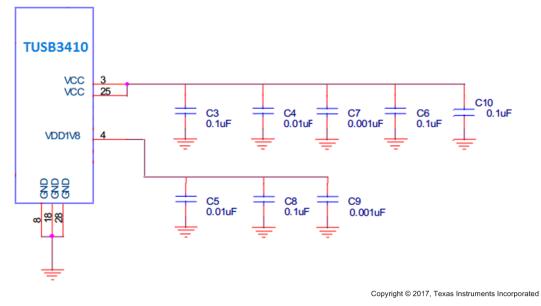

| VCC          | 3, 25     | PWR | 3.3 V                                                                                                                                                          |

| VDD18        | 4         | PWR | 1.8-V supply. An internal voltage regulator generates this supply voltage when terminal VREGEN is low. When VREGEN is high, 1.8 V must be supplied externally. |

| VREGEN       | 1         | Ι   | This active-low terminal is used to enable the 3.3-V to 1.8-V voltage regulator.                                                                               |

| WAKEUP       | 12        | Ι   | Remote wake-up request terminal. When low, wakes up system <sup>(4)</sup>                                                                                      |

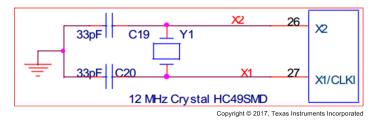

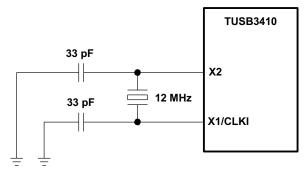

| X1/CLKI      | 27        | I   | 12-MHz crystal input or clock input                                                                                                                            |

| X2           | 26        | 0   | 12-MHz crystal output                                                                                                                                          |

3-state CMOS output (±4-mA drive and sink) (1)

TTL-compatible, hysteresis input

(2) (3)

3-state CMOS output ( $\pm$ 12-mA drive and sink) TTL-compatible, hysteresis input, with internal 100-µA active pullup resistor (4)

The MCU treats the outputs as open drain types in that the output can be driven low continuously, but a high output is driven for two clock cycles and then the output is high impedance. (5)

3-state CMOS output (±8-mA drive and sink) (6)

TTL-compatible input without hysteresis, with internal 100- $\mu$ A active pullup resistor Normal or IR mode: 3-state CMOS output (±4-mA drive and sink) (7)

(8)

# **4** Specifications

#### 4.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                 |                                     |            | MIN  | MAX                   | UNIT |

|-----------------|-------------------------------------|------------|------|-----------------------|------|

| $V_{CC}$        | Supply voltage                      |            | -0.5 | 3.6                   | V    |

| VI              | Input voltage                       |            | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Vo              | Output voltage                      |            | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| I <sub>IK</sub> | I <sub>IK</sub> Input clamp current |            |      | ±20                   | mA   |

| I <sub>OK</sub> | Output clamp current                |            |      | ±20                   | mA   |

| т               | Storage temperature                 | Industrial | -65  | 150                   | °C   |

| I stg           | Storage temperature                 | Standard   | -55  | 150                   |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 4.2 ESD Ratings

|                               |                                              |                                                                  |          | VALUE | UNIT |

|-------------------------------|----------------------------------------------|------------------------------------------------------------------|----------|-------|------|

| Flastrastatia diasharra (FCD) |                                              | Human Body Model (HBM), per ANSI/ESDA/JEDEC JS001 <sup>(1)</sup> |          | ±2000 | V    |

| V <sub>ESI</sub>              | Electrostatic discharge (ESD)<br>performance | Charged Device Model (CDM), per JESD22-C101 <sup>(2)</sup>       | All pins | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 4.3 Recommended Operating Conditions

|                 |                          |                  | MIN                 | TYP MAX             | UNIT |

|-----------------|--------------------------|------------------|---------------------|---------------------|------|

| V <sub>CC</sub> | Supply voltage           |                  | 3                   | 3.3 3.6             | V    |

| VI              | Input voltage            |                  | 0                   | V <sub>CC</sub>     | V    |

|                 | TTL                      | 2                | V <sub>CC</sub>     | V                   |      |

| VIH             | High-level input voltage | CMOS             | $0.7 \times V_{CC}$ | V <sub>CC</sub>     | v    |

| V               | Low lovel input veltage  | TTL              | 0                   | 0.8                 | V    |

| V <sub>IL</sub> | Low-level input voltage  | CMOS             | 0                   | $0.2 \times V_{CC}$ | v    |

| -               | Operating temperature    | Commercial range | 0                   | 70                  | °C   |

| T <sub>A</sub>  | Operating temperature    | Industrial range | -40                 | 85                  | °C   |

#### 4.4 Thermal Information

|                       |                                              | TUS        |           |      |  |

|-----------------------|----------------------------------------------|------------|-----------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN) | VF (LQFP) | UNIT |  |

|                       |                                              | 32         | 32 PINS   |      |  |

| $R_{	hetaJA}$         | Junction-to-ambient thermal resistance       | 32.1       | 70.5      | °C/W |  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 24.6       | 31.4      | °C/W |  |

| $R_{\theta J B}$      | Junction-to-board thermal resistance         | 6.5        | 28.3      | °C/W |  |

| ΨJT                   | Junction-to-top characterization parameter   | 0.2        | 2.2       | °C/W |  |

| Ψјв                   | Junction-to-board characterization parameter | 6.5        | 28.2      | °C/W |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 24.6       | 31.4      | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and C Package Thermal Metrics application report.

# 4.5 Electrical Characteristics

$T_A = 25^{\circ}C, V_{CC} = 3.3 \text{ V} \pm 5\%, V_{SS} = 0 \text{ V}$

|                   | PARAMETER                                         |                              | TEST CONDITIONS                     | MIN                   | TYP MAX               | UNIT |

|-------------------|---------------------------------------------------|------------------------------|-------------------------------------|-----------------------|-----------------------|------|

|                   | L Pada Jacob La strant ca Rana                    | TTL                          |                                     | V <sub>CC</sub> – 0.5 |                       |      |

| V <sub>OH</sub>   | High-level output voltage CMO                     |                              | I <sub>OH</sub> = -4 mA             | V <sub>CC</sub> – 0.5 |                       | V    |

|                   |                                                   | TTL                          | 1 4 0                               |                       | 0.5                   | V    |

| V <sub>OL</sub>   | Low-level output voltage                          | CMOS                         | $I_{OL} = 4 \text{ mA}$             |                       | 0.5                   |      |

| V                 | Desitive threshold veltage                        | TTL                          |                                     |                       | 1.8                   | V    |

| V <sub>IT+</sub>  | Positive threshold voltage                        | CMOS                         | $V_{I} = V_{IH}$                    |                       | $0.7 \times V_{CC}$   | v    |

| V                 | Negotive threehold veltage                        | TTL                          |                                     | 0.8                   | 1.8                   | V    |

| V <sub>IT</sub> - | Negative threshold voltage                        | CMOS                         | $V_{I} = V_{IH}$                    | $0.2 \times V_{CC}$   |                       | v    |

| V                 |                                                   | TTL                          |                                     | 0.3                   | 0.7                   | V    |

| V <sub>hys</sub>  | Hysteresis (V <sub>IT+</sub> – V <sub>IT-</sub> ) | CMOS                         | $V_{I} = V_{IH}$                    | $0.17 \times V_{CC}$  | 0.3 × V <sub>CC</sub> | v    |

|                   | High-level input current                          | TTL                          |                                     |                       | ±20                   | μA   |

| I <sub>IH</sub>   |                                                   | CMOS                         | $V_{I} = V_{IH}$                    |                       | ±1                    |      |

|                   | Law barrel formation model                        |                              |                                     | ±20                   |                       |      |

| IIL               | Low-level input current                           | $\frac{1}{1} V_{I} = V_{IL}$ |                                     |                       | ±1                    | μA   |

| I <sub>OZ</sub>   | Output leakage current (Hi-Z)                     |                              | $V_{I} = V_{CC} \text{ or } V_{SS}$ |                       | ±20                   | μA   |

| I <sub>OL</sub>   | Output low drive current                          |                              |                                     | 0.1                   |                       | mA   |

| I <sub>OH</sub>   | Output high drive current                         |                              |                                     | 0.1                   |                       | mA   |

|                   | Supply current (operating)                        |                              | Serial data at 921.6 k              |                       | 15                    | mA   |

| I <sub>CC</sub>   | Supply current (suspended)                        |                              |                                     |                       | 200                   | μA   |

|                   | Clock duty cycle <sup>(1)</sup>                   |                              |                                     |                       | 50%                   |      |

|                   | Jitter specification <sup>(1)</sup>               |                              |                                     |                       | ±100                  | ppm  |

| CI                | Input capacitance                                 |                              |                                     |                       | 18                    | pF   |

| Co                | Output capacitance                                |                              |                                     |                       | 10                    | pF   |

(1) Applies to all clock outputs

## 4.6 Timing and Switching Characteristics Information

## 4.6.1 Wakeup Timing (WAKEUP or RI/CP Transitions)

The TUSB3410 device can be brought out of the suspended state, or woken up, by a command from the host. The TUSB3410 device also supports remote wakeup and can be awakened by either of two input signals. A low pulse on the WAKEUP terminal or a low-to-high transition on the RI/CP terminal wakes up the device.

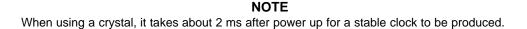

#### NOTE

For reliable operation, either condition must persist for approximately 3-ms minimum, which allows time for the crystal to power up because in the suspend mode, the crystal interface is powered down. The state of the  $\overline{WAKEUP}$  or  $\overline{RI}/CP$  terminal is then sampled by the clock to verify there was a valid wake-up event.

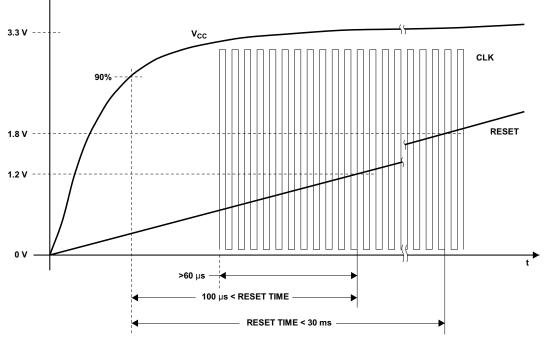

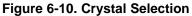

#### 4.6.2 Reset Timing

There are three requirements for the reset signal timing. First, the minimum reset pulse duration is 100  $\mu$ s. At power up, this time is measured from the time the power ramps up to 90% of the nominal V<sub>CC</sub> until the reset signal exceeds 1.2 V. The second requirement is that the clock must be valid during the last 60  $\mu$ s of the reset window. The third requirement is that, according to the USB specification, the device must be ready to respond to the host within 100 ms. This means that within the 100-ms window, the device must come out of reset, load any pertinent data from the I<sup>2</sup>C EEPROM device, and transfer execution to the application firmware if any is present. Because the latter two events can require significant time, the amount of which can change from system to system, TI recommends having the device come out of reset within 30 ms, leaving 70 ms for the other events to complete. This means the reset signal must rise to 1.8 V within 30 ms.

These requirements are depicted in Figure 4-1. When using a 12-MHz crystal, the clock signal may take several milliseconds to ramp up and become valid after power up. Therefore, the reset window may need to be elongated up to 10 ms or more to ensure that there is a 60-µs overlap with a valid clock.

Figure 4-1. Reset Timing

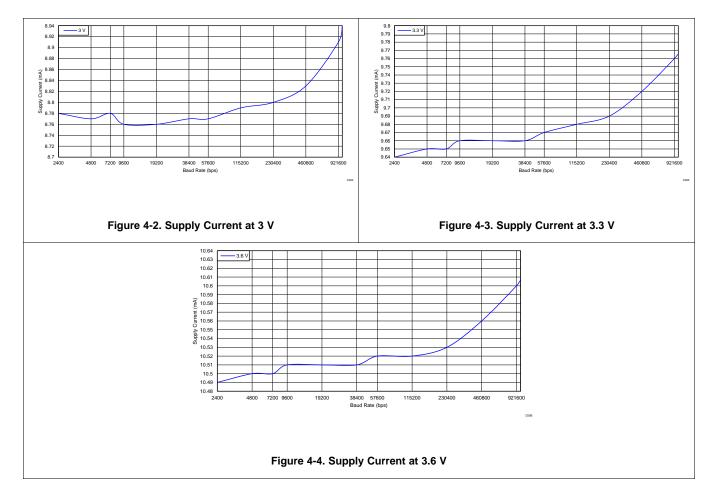

# 4.7 Typical Characteristics

TEXAS INSTRUMENTS www.ti.com

# 5 Detailed Description

#### 5.1 Overview

The TUSB3410 device provides bridging between a USB port and an enhanced UART serial port. The TUSB3410 device contains all the necessary logic to communicate with the host computer using the USB bus. It contains an 8052 microcontroller unit (MCU) with 16K bytes of RAM that can be loaded from the host or from the external on-board memory through an I<sup>2</sup>C bus. It also contains 10K bytes of ROM that allow the MCU to configure the USB port at boot time. The ROM code also contains an I<sup>2</sup>C bootloader. All device functions, such as the USB command decoding, UART setup, and error reporting, are managed by the internal MCU firmware under the auspices of the PC host.

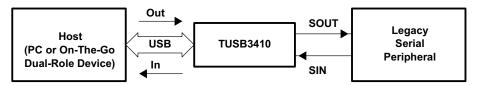

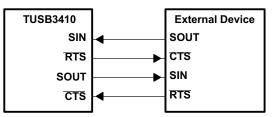

The TUSB3410 device can be used to build an interface between a legacy serial peripheral device and a PC with USB ports, such as a legacy-free PC. When configured, data flows from the host to the TUSB3410 device through USB OUT commands and then out from the TUSB3410 device on the SOUT line. Conversely, data flows into the TUSB3410 device on the SIN line and then into the host through USB IN commands.

Figure 5-1. Data Flow

#### 5.2 Functional Block Diagram

Figure 5-2. USB-to-Serial (Single Channel) Controller Block Diagram

#### 5.3 Device Functional Modes

The TUSB3410 device controls its USB interface in response to USB commands, and this action is independent of the serial port mode selected. On the other hand, the serial port can be configured in three different modes.

As with any interface device, data movement is the main function of the TUSB3410 device, but typically the initial configuration and error handling consume most of the support code. The following sections describe the various modes the device can be used in and the means of configuring the device.

## 5.3.1 USB Interface Configuration

The TUSB3410 device contains onboard ROM microcode, which enables the MCU to enumerate the device as a USB peripheral. The ROM microcode can also load application code into internal RAM from either external memory through the I<sup>2</sup>C bus or from the host through the USB.

Copyright © 2002–2017, Texas Instruments Incorporated

#### 5.3.1.1 External Memory Case

After reset, the TUSB3410 device is disconnected from the USB. Bit 7 (CONT) in the USBCTL register (see Section 5.5.5.4) is cleared. The TUSB3410 device checks the I<sup>2</sup>C port for the existence of valid code; if it finds valid code, then the device uploads the code from the external memory device into the RAM program space. When loaded, the TUSB3410 device connects to the USB by setting the CONT bit; then, enumeration and configuration are performed. This is the most likely use of the device.

#### 5.3.1.2 Host Download Case

If the valid code is not found at the I<sup>2</sup>C port, then the TUSB3410 device connects to the USB by setting bit 7 (CONT) in the USBCTL register (see Section 5.5.5.4), and then an enumeration and default configuration are performed. The host can download additional microcode into RAM to tailor the application. Then, the MCU causes a disconnect and reconnect by clearing and setting the CONT bit, which causes the TUSB3410 device to be re-enumerated with a new configuration.

#### 5.3.2 USB Data Movement

From the USB perspective, the TUSB3410 device looks like a USB peripheral device. It uses endpoint zero as its control endpoint, as do all USB peripherals. It also configures up to three input and three output endpoints, although most applications use one bulk input endpoint for data in, one bulk output endpoint for data out, and one interrupt endpoint for status updates. The USB configuration likely remains the same regardless of the serial port configuration.

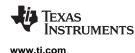

Most data is moved from the USB side to the UART side and from the UART side to the USB side using on-chip DMA transfers. Some special cases may use programmed I/O under control of the MCU.

#### 5.3.3 Serial Port Setup

The serial port requires a few control registers to be written to configure its operation. This configuration likely remains the same regardless of the data mode used. These registers include the line control register that controls the serial word format and the divisor registers that control the baud rate.

These registers are usually controlled by the host application.

#### 5.3.4 Serial Port Data Modes

The serial port can be configured in three different, although similar, data modes: the RS-232 data mode, the RS-485 data mode, and the IrDA data mode. Similar to the USB mode, when configured for a specific application, it is unlikely that the mode would be changed. The different modes affect the timing of the serial input and output or the use of the control signals. However, the basic serial-to-parallel conversion of the receiver and parallel-to-serial conversion of the transmitter remain the same in all modes. Some features are available in all modes, but are only applicable in certain modes. For instance, software flow control through Xoff/Xon characters can be used in all modes, but would usually only be used in RS-232 or IrDA mode because the RS-485 mode is half-duplex communication. Similarly, hardware flow control through RTS/CTS (or DTR/DSR) handshaking is available in RS-232 or IrDA mode. However, this would probably be used only in RS-232 mode, because in IrDA mode only the SIN and SOUT paths are optically coupled.

#### 5.3.4.1 RS-232 Data Mode

The default mode is called the RS-232 mode and is typically used for full duplex communication on SOUT and SIN. In this mode, the modem control outputs (RTS and DTR) communicate to a modem or are general outputs. The modem control inputs (CTS, DSR, DCD, and RI/CP) communicate to a modem or are general inputs. Alternatively, RTS and CTS (or DTR and DSR) can throttle the data flow on SOUT and SIN to prevent receive FIFO overruns. Finally, software flow control through Xoff/Xon characters can be used for the same purpose (see Section 5.2).

This mode represents the most general-purpose applications, and the other modes are subsets of this mode.

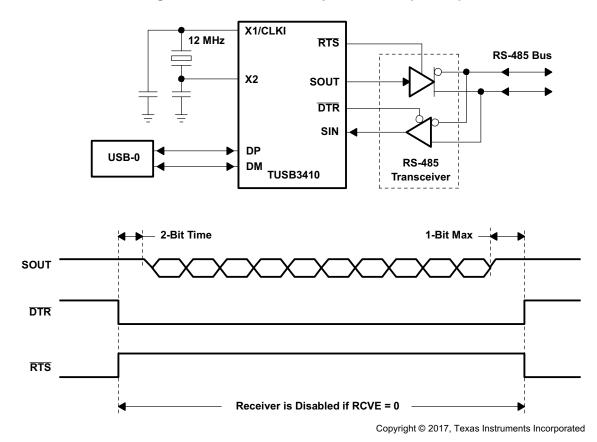

#### 5.3.4.2 RS-485 Data Mode

The RS-485 mode is very similar to the RS-232 mode in that the SOUT and SIN formats remain the same. Because RS-485 is a bus architecture, it is inherently a single duplex communication system. The TUSB3410 device in RS-485 mode controls the RTS and DTR signals such that either can enable an RS-485 driver or RS-485 receiver. When in RS-485 mode, the enable signals for transmitting are automatically asserted whenever the DMA is set up for outbound data.

#### NOTE

The receiver can be left enabled while the driver is enabled to allow an echo if desired, but when receive data is expected, the driver must be disabled. This precludes use of hardware flow control, because this is a half-duplex operation, it would not be effective. Software flow control is supported, but may be of limited value.

The RS-485 mode is enabled by setting bit 7 (485E) in the FCRL register (see Section 5.5.7.4), and bit 1 (RCVE) in the MCR register (see Section 5.5.7.6) allows the receiver to eavesdrop while in the RS-485 mode.

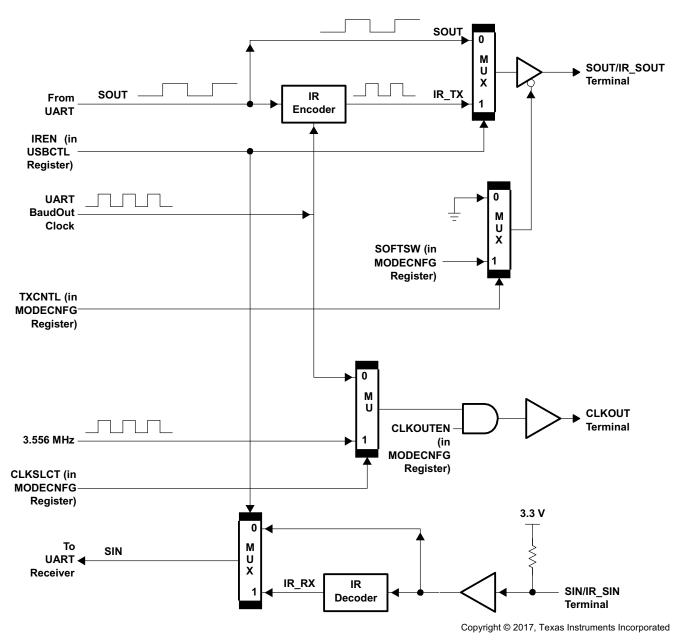

#### 5.3.4.3 IrDA Data Mode

The IrDA mode encodes SOUT and decodes SIN in the manner prescribed by the IrDA standard, up to 115.2 kbps. Connection to an external IrDA transceiver is required. Communications is usually full duplex. Generally, in an IrDA system, only the SOUT and SIN paths are connected so hardware flow control is usually not an option. Software flow control is supported (see Section 5.2).

The IrDA mode is enabled by setting bit 6 (IREN) in the USBCTL register (see Section 5.5.5.4).

The IR encoder and decoder circuitry work with the UART to change the serial bit stream into a series of pulses and back again. For every zero bit in the outbound serial stream, the encoder sends a low-to-high-to-low pulse with the duration of 3/16 of a bit frame at the middle of the bit time. For every one bit in the serial stream, the output remains low for the entire bit time.

The decoding process consists of receiving the signal from the IrDA receiver and converting it into a series of zeroes and ones. As the converse to the encoder, the decoder converts a pulse to a zero bit and the lack of a pulse to a one bit.

TUSB3410, TUSB3410I

SLLS519J-MARCH 2002-REVISED JULY 2017

www.ti.com

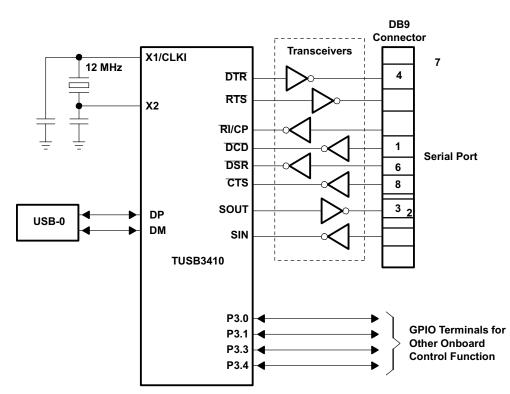

Figure 5-3. RS-232 and IR Mode Select

Copyright © 2017, Texas Instruments Incorporated

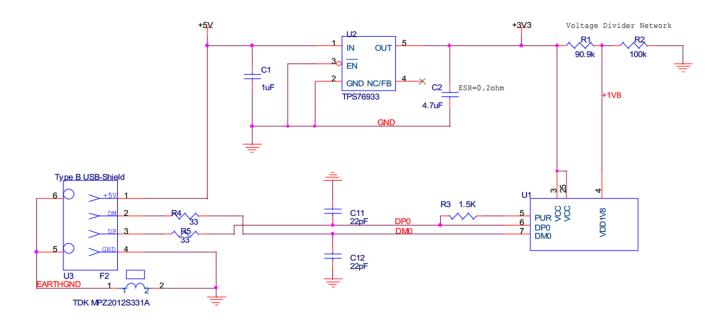

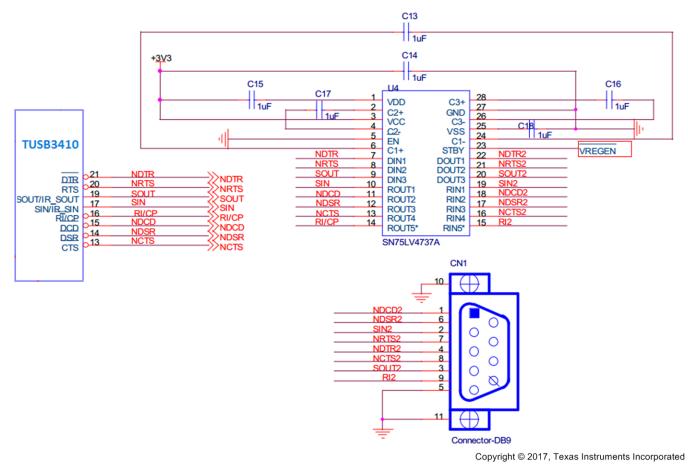

Figure 5-4. USB-to-Serial Implementation (RS-232)

#### Figure 5-5. RS-485 Bus Implementation

TRUMENTS

www.ti.com

#### 5.4 Processor Subsystems

#### 5.4.1 DMA Controller

#### 5.4.1.1 Bulk Data I/O Using the EDB

The UBM (USB buffer manager) and the DMAC (DMA controller) access the EDB to fetch buffer parameters for IN and OUT transactions (IN and OUT are with respect to host). In this discussion, it is assumed that:

- The MCU initialized the EDBs

- DMA-continuous mode is being used

- Double buffering is being used

- The X/Y toggle is controlled by the UBM

#### 5.4.1.1.1 IN Transaction (TUSB3410 to Host)

- 1. The MCU initializes the IEDB (64-byte packet, and double buffering is used) and the following DMA registers:

- DMACSR3: Defines the transaction time-out value.

- DMACDR3: Defines the IEDB being used and the DMA mode of operation (continuous mode).

Once this register is set with EN = 1, the transfer starts.

- 2. The DMA transfers data from the UART to the X buffer. When a block of 64 bytes is transferred, the DMA updates the byte count and sets NAK to 0 in the input endpoint byte count register (indicating to the UBM that the X buffer is ready to be transferred to host). The UBM starts X-buffer transfer to host using the byte-count value in the input endpoint byte count register and toggles the X/Y bit. The DMA continues transferring data from a device to Y buffer. At the end of the block transfer, the DMA updates the byte count and sets NAK to 0 in the input endpoint byte count register (indicating to the UBM that the Y buffer is ready to be transferred to host). The DMA continues the transfer, the DMA updates the yte count and sets NAK to 0 in the input endpoint byte count register (indicating to the UBM that the Y buffer is ready to be transferred to host). The DMA continues the transfer from the device to host, alternating between X and Y buffers without MCU intervention.

- 3. Transfer termination: The DMA/UBM continues the data transfer, alternating between the X and Y buffers. Termination of the transfer can happen under the following conditions:

- Stop Transfer: The host notifies the MCU (through control-end-point) to stop the transfer. Under this condition, the MCU sets bit 7 (EN) to 0 in the DMACDR register.

- Partial Packet: The device receiver has no data to be transferred to host. Under this condition, the byte-count value is less than 64 when the transaction timer time-out occurs. When the DMA detects this condition, it sets bit 1 (TXFT) to 1 and bit 0 (OVRUN) to 0 in the DMACSR3 register, updates the byte count and NAK bit in the input endpoint byte count register, and interrupts the MCU. The UBM transfers the partial packet to host.

- Buffer Overrun: The host is busy, X and Y buffers are full (X-NAK = 0 and Y-NAK = 0), and the

DMA cannot write to these buffers. The transaction time-out stops the DMA transfer, the DMA sets

bit 1 (TXFT) to 1 and bit 0 (OVRUN) to 1 in the DMACSR3 register, and interrupts the MCU.

- UART Error Condition: When receiving from a UART, a receiver-error condition stops the DMA and sets bit 1 (TXFT) to 1 and bit 0 (OVRUN) to 0 in the DMACSR3 register, but the EN bit remains set at 1. Therefore, the DMA does not interrupt the MCU. However, the UART generates a status interrupt, notifying the MCU that an error condition has occurred.

#### 5.4.1.1.2 OUT Transaction (Host to TUSB3410)

- 1. The MCU initializes the OEDB (64-byte packet, and double buffering is used) and the following DMA registers:

- **DMACSR1:** Provides an indication of a partial packet.

- DMACDR1: Defines the output endpoint being used, and the DMA mode of operation (continuous mode). When the EN bit is set to 1 in this register, the transfer starts.

- 2. The UBM transfers data from host to X buffer. When a block of 64 bytes is transferred, the UBM updates the byte count and sets NAK to 1 in the output endpoint byte count register (indicating to DMA that the X buffer is ready to be transferred to the UART). The DMA starts X buffer transfer using the byte-count value in the output endpoint byte count register. The UBM continues transferring data from host to Y buffer. At the end of the block transfer, the UBM updates the byte count and sets NAK to 1 in the output endpoint byte count register (indicating to DMA that the Y buffer is ready to be transferred to device). The DMA continues the transfer from the X and Y buffers to the device, alternating between X and Y buffers without MCU intervention.

- 3. Transfer termination: The DMA/UBM continues the data transfer alternating between X and Y buffers. The termination of the transfer can happen under the following conditions:

- **Stop Transfer:** The host notifies the MCU (through control-end point) to stop the transfer. Under this condition, the MCU sets EN to 0 in the DMACDR1 register.

- Partial Packet: UBM receives a partial packet from host. Under this condition, the byte-count value is less than 64. When the DMA detects this condition, it transfers the partial packet to the device, sets PPKT to 1, updates NAK to 0 in the output endpoint byte count register and interrupts MCU.

# 5.4.2 UART

#### 5.4.2.1 UART Data Transfer

Figure 5-6 illustrates the data transfer between the UART and the host using the DMA controller and the USB buffer manager (UBM). A buffer of 512 bytes is reserved for buffering the UART channel (transmit and receive buffers). The UART channel has 64 bytes of double-buffer space (X and Y buffer). When the DMA writes to the X buffer, the UBM reads from the Y buffer. Similarly, when the DMA reads from the X buffer, the UBM writes to the Y buffer. The DMA channel is configured to operate in the continuous mode (by setting bit 5 (CNT) in the DMACDR registers = 1). Once the MCU enables the DMA, data transfer toggles between the UMB and the DMA without MCU intervention. See Section 5.4.1.1.1 for DMA transfer-termination condition.

#### 5.4.2.1.1 Receiver Data Flow

The UART receiver has a 32-byte FIFO. The receiver FIFO has two trigger levels. One is the high-level mark (HALT), which is set to 12 bytes, and the other is the low-level mark (RESUME), which is set to 4 bytes. When the HALT mark is reached, either the RTS terminal goes high or Xoff is transmitted (depending on the auto setting). When the FIFO reaches the RESUME mark, then either the RTS terminal goes low or Xon is transmitted.

Figure 5-6. Receiver and Transmitter Data Flow

#### 5.4.2.1.2 Hardware Flow Control

Figure 5-7 illustrates the connection necessary to achieve hardware flow control. The CTS and RTS signals are provided for this purpose. Auto CTS and auto RTS (and Xon/Xoff) can be enabled and disabled independently by programming the UART flow control register (FCRL).

Copyright © 2017, Texas Instruments Incorporated

Figure 5-7. Auto Flow Control Interconnect

#### 5.4.2.1.3 Auto RTS (Receiver Control)

In this mode, the RTS output terminal signals the receiver-FIFO status to an external device. The RTS output signal is controlled by the high- and low-level marks of the FIFO. When the high-level mark is reached, RTS goes high, signaling to an external sending device to halt its transfer. Conversely, when the low-level mark is reached, RTS goes low, signaling to an external sending device to resume its transfer.

Data transfer from the FIFO to the X and Y buffer is performed by the DMA controller. See Section 5.4.1.1.1 for DMA transfer-termination condition.

#### 5.4.2.1.4 Auto CTS (Transmitter Control)

In this mode, the  $\overline{\text{CTS}}$  input terminal controls the transfer from internal buffer (X or Y) to the TDR. When the DMA controller transfers data from the Y buffer to the TDR and the  $\overline{\text{CTS}}$  input terminal goes high, the DMA controller is suspended until  $\overline{\text{CTS}}$  goes low. Meanwhile, the UBM is transferring data from the host to the X buffer. When  $\overline{\text{CTS}}$  goes low, the DMA resumes the transfer. Data transfer continues alternating between the X and Y buffers, without MCU intervention. See Section 5.4.1.1.2 for DMA transfer-termination condition.

#### 5.4.2.1.5 Xon/Xoff Receiver Flow Control

To enable Xon/Xoff flow control, certain bits within the modem control register must be set as follows: MCR bit 5 = 1 and MCR bits 6 and 7 = 00. In this mode, the Xon/Xoff bytes are transmitted to an external sending device to control the transmission of the device. When the high-level mark (of the FIFO) is reached, the Xoff byte is transmitted, signaling to an external sending device to halt its transfer. Conversely, when the low-level mark is reached, the Xon byte is transmitted, signaling to an external sending device to resume its transfer. The data transfer from the FIFO to X and Y buffer is performed by the DMA controller.

#### 5.4.2.1.6 Xon/Xoff Transmit Flow Control

To enable Xon/Xoff flow control, certain bits within the modem control register must be set as follows: MCR bit 5 = 1 and MCR bits 6 and 7 = 00. In this mode, the incoming data are compared to the XON and XOFF registers. If a match to XOFF is detected, the DMA is paused. If a match to XON is detected, the DMA resumes. Meanwhile, the UBM is transferring data from the host to the X-buffer. The MCU does not switch the buffers unless the Y buffer is empty and the X-buffer is full. When Xon is detected, the DMA resumes the transfer.

# 5.4.3 **PC** Port

#### 5.4.3.1 Random-Read Operation

A random read requires a dummy byte-write sequence to load in the data word address. Once the deviceaddress word and the data-word address are clocked out and acknowledged by the device, the MCU starts a current-address sequence. The following describes the sequence of events to accomplish this transaction.

#### 5.4.3.1.1 Device Address + EPROM [High Byte]

- 1. The MCU clears bit 1 (SRD) within the I2CSTA register. This forces the I<sup>2</sup>C controller not to generate a stop condition after the contents of the I2CDAI register are received.

- 2. The MCU clears bit 0 (SWR) within the I2CSTA register. This forces the I<sup>2</sup>C controller not to generate a stop condition after the contents of the I2CDAO register are transmitted.

- 3. The MCU writes the device address (bit 0 (R/W) = 0) to the I2CADR register (write operation)

- 4. The MCU writes the high byte of the EEPROM address into the I2CDAO register (this starts the transfer on the SDA line).

- 5. Bit 3 (TXE) in the I2CSTA register is automatically cleared (indicates busy) by writing data to the I2CDAO register.

- 6. The contents of the I2CADR register are transmitted to EEPROM (preceded by start condition on SDA).

- 7. The contents of the I2CDAO register are transmitted to EEPROM (EPROM address).

- 8. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register has been transmitted.

- 9. A stop condition is not generated.

## 5.4.3.1.2 EPROM [Low Byte]

- 1. The MCU writes the low byte of the EEPROM address into the I2CDAO register.

- 2. Bit 3 (TXE) in the I2CSTA register is automatically cleared (indicates busy) by writing to the I2CDAO register.

- 3. The contents of the I2CDAO register are transmitted to the device (EEPROM address).

- 4. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register has been transmitted.

- 5. This completes the dummy write operation. At this point, the EEPROM address is set and the MCU can do either a single- or a sequential-read operation.

#### 5.4.3.2 Current-Address Read Operation

When the EEPROM address is set, the MCU can read a single byte by executing the following steps:

- 1. The MCU sets bit 1 (SRD) in the I2CSTA register to 1. This forces the I<sup>2</sup>C controller to generate a stop condition after the I2CDAI-register contents are received.

- 2. The MCU writes the device address (bit 0 (R/W) = 1) to the I2CADR register (read operation).

- 3. The MCU writes a dummy byte to the I2CDAO register (this starts the transfer on SDA line).

- 4. Bit 7 (RXF) in the I2CSTA register is cleared (RX is empty).

- 5. The contents of the I2CADR register are transmitted to the device (preceded by start condition on SDA).

- 6. The data from EEPROM are latched into the I2CDAI register (stop condition is transmitted).

- 7. Bit 7 (RXF) in the I2CSTA register is set and interrupts the MCU, indicating that the data are available.

- 8. The MCU reads the I2CDAI register. This clears bit 7 (RXF) in the I2CSTA register.

#### 5.4.3.3 Sequential-Read Operation

When the EEPROM address is set, the MCU can execute a sequential read operation by executing the following steps (this example illustrates a 32-byte sequential read):

#### 5.4.3.3.1 Device Address

- 1. The MCU clears bit 1 (SRD) in the I2CSTA register. This forces the I<sup>2</sup>C controller to not generate a stop condition after the I2CDAI register contents are received.

- 2. The MCU writes the device address (bit 0 (R/W) = 1) to the I2CADR register (read operation).

- 3. The MCU writes a dummy byte to the I2CDAO register (this starts the transfer on the SDA line).

- 4. Bit 7 (RXF) in the I2CSTA register is cleared (RX is empty).

- 5. The contents of the I2CADR register are transmitted to the device (preceded by start condition on SDA).

#### 5.4.3.3.2 N-Byte Read (31 Bytes)

- 1. The data from the device is latched into the I2CDAI register (stop condition is not transmitted).

- 2. Bit 7 (RXF) in the I2CSTA register is set and interrupts the MCU, indicating that data is available.

- 3. The MCU reads the I2CDAI register. This clears bit 7 (RXF) in the I2CSTA register.

- 4. This operation repeats 31 times.

#### 5.4.3.3.3 Last-Byte Read (Byte 32)

- 1. MCU sets bit 1 (SRD) in the I2STA register to 1. This forces the I<sup>2</sup>C controller to generate a stop condition after the I2CDAI register contents are received.

- 2. The data from the device is latched into the I2CDAI register (stop condition is transmitted).

- 3. Bit 7 (RXF) in the I2CSTA register is set and interrupts the MCU, indicating that data is available.

- 4. The MCU reads the I2CDAI register. This clears bit 7 (RXF) in the I2CSTA register.

#### 5.4.3.4 Byte-Write Operation

The byte-write operation involves three phases: device address + EPROM [high byte] phase, EPROM [low byte] phase, and EPROM [DATA] phase. The following describes the sequence of events to accomplish the byte-write transaction.

#### 5.4.3.4.1 Device Address + EPROM [High Byte]

- 1. The MCU sets clears the SWR bit in the I2CSTA register. This forces the I<sup>2</sup>C controller to not generate a stop condition after the contents of the I2CDAO register are transmitted.

- 2. The MCU writes the device address (bit 0 (R/W) = 0) to the I2CADR register (write operation).

- 3. The MCU writes the high byte of the EEPROM address into the I2CDAO register (this starts the transfer on the SDA line).

- 4. Bit 3 (TXE) in the I2CSTA register is cleared (indicates busy).

- 5. The contents of the I2CADR register are transmitted to the device (preceded by start condition on SDA).

- 6. The contents of the I2CDAO register are transmitted to the device (EEPROM high address).

- 7. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register contents have been transmitted.

#### 5.4.3.4.2 EPROM [Low Byte]

- 1. The MCU writes the low byte of the EEPROM address into the I2CDAO register.

- 2. Bit 3 (TXE) in the I2CSTA register is cleared (indicating busy).

- 3. The contents of the I2CDAO register are transmitted to the device (EEPROM address).

- 4. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register contents have been transmitted.

#### 5.4.3.4.3 EPROM [DATA]

- 1. The MCU sets bit 0 (SWR) in the I2CSTA register. This forces the I<sup>2</sup>C controller to generate a stop condition after the contents of the I2CDAO register are transmitted.

- 2. The data to be written to the EPROM is written by the MCU into the I2CDAO register.

- 3. Bit 3 (TXE) in the I2CSTA register is cleared (indicates busy).

- 4. The contents of the I2CDAO register are transmitted to the device (EEPROM data).

- 5. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register contents have been transmitted.

- 6. The I<sup>2</sup>C controller generates a stop condition after the contents of the I2CDAO register are transmitted.

#### 5.4.3.5 Page-Write Operation

The page-write operation is initiated in the same way as byte write, with the exception that a stop condition is not generated after the first EPROM [DATA] is transmitted. The following describes the sequence of writing 32 bytes in page mode.

#### 5.4.3.5.1 Device Address + EPROM [High Byte]

- 1. The MCU clears bit 0 (SWR) in the I2CSTA register. This forces the I<sup>2</sup>C controller to not generate a stop condition after the contents of the I2CDAO register are transmitted.

- 2. The MCU writes the device address (bit 0 (R/W) = 0) to the I2CADR register (write operation).

- 3. The MCU writes the high byte of the EEPROM address into the I2CDAO register.

- 4. Bit 3 (TXE) in the I2CSTA register is cleared (indicating busy).

- 5. The contents of the I2CADR register are transmitted to the device (preceded by start condition on SDA).

- 6. The contents of the I2CDAO register are transmitted to the device (EEPROM address).

- 7. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register contents have been transmitted.

#### 5.4.3.5.2 EPROM [Low Byte]

- 1. The MCU writes the low byte of the EEPROM address into the I2CDAO register.

- 2. Bit 3 (TXE) in the I2CSTA register is cleared (indicates busy).

- 3. The contents of the I2CDAO register are transmitted to the device (EEPROM address).

- 4. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register contents have been transmitted.

#### 5.4.3.5.3 EPROM [DATA]—31 Bytes

- 1. The data to be written to the EEPROM are written by the MCU into the I2CDAO register.

- 2. Bit 3 (TXE) in the I2CSTA register is cleared (indicates busy).

- 3. The contents of the I2CDAO register are transmitted to the device (EEPROM data).

- 4. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register contents have been transmitted.

- 5. This operation repeats 31 times.

#### 5.4.3.5.4 EPROM [DATA]—Last Byte

- 1. The MCU sets bit 0 (SWR) in the I2CSTA register. This forces the I<sup>2</sup>C controller to generate a stop condition after the contents of the I2CDAO register are transmitted.

- 2. The MCU writes the last date byte to be written to the EEPROM, into the I2CDAO register.

- 3. Bit 3 (TXE) in the I2CSTA register is cleared (indicates busy).

- 4. The contents of the I2CDAO register are transmitted to EEPROM (EEPROM data).

- 5. Bit 3 (TXE) in the I2CSTA register is set and interrupts the MCU, indicating that the I2CDAO register contents have been transmitted.

- 6. The I<sup>2</sup>C controller generates a stop condition after the contents of the I2CDAO register are transmitted.

# 5.5 Memory

# 5.5.1 MCU Memory Map

Figure 5-8 illustrates the MCU memory map under boot and normal operation.

#### NOTE

The internal 256 bytes of RAM are not shown, because they are assumed to be in the standard 8052 location (0000h to 00FFh). The shaded areas represent the internal ROM/RAM.

• When bit 0 (SDW) of the ROMS register is 0 (boot mode)

The 10K ROM is mapped to address (0x0000–0x27FF) and is duplicated in location (0x8000–0xA7FF) in code space. The internal 16K RAM is mapped to address range (0x0000–0x3FFF) in data space. Buffers, MMR, and I/O are mapped to address range (0xF800–0xFFFF) in data space.

#### • When bit 0 (SDW) is 1 (normal mode)

The 10K ROM is mapped to (0x8000-0xA7FF) in code space. The internal 16K RAM is mapped to address range (0x0000-0x3FFF) in code space. Buffers, MMR, and I/O are mapped to address range (0xF800-0xFFFF) in data space.

|                | Boot N       | lode (SDW = 0)      |  | Normal M                     | ode  | (SDW = 1) |

|----------------|--------------|---------------------|--|------------------------------|------|-----------|

|                | CODE         |                     |  |                              | CODE |           |

| 0000h<br>27FFh | 10K Boot ROM | (16K)<br>Read/Write |  | 16K<br>Code RAM<br>Read Only |      |           |

| 3FFFh          |              |                     |  |                              |      |           |

|                |              |                     |  |                              |      |           |

| 8000h<br>A7FFh | 10K Boot ROM |                     |  | 10K Boot ROM                 |      |           |

|                |              |                     |  |                              |      |           |

| F800h<br>FF7Fh |              | 2K Data             |  |                              |      | 2K Data   |

| FF80h<br>FFFFh |              | MMR                 |  |                              |      | MMR       |

Figure 5-8. MCU Memory Map

# 5.5.2 Registers

#### 5.5.2.1 Miscellaneous Registers

#### 5.5.2.1.1 ROMS: ROM Shadow Configuration Register (Addr:FF90h)

This register is used by the MCU to switch from boot mode to normal operation mode (boot mode is set on power-on reset only). In addition, this register provides the device revision number and the ROM/RAM configuration.

| 7   | 6   | 5   | 4    | 3    | 2    | 1    | 0   |

|-----|-----|-----|------|------|------|------|-----|

| ROA | S1  | S0  | RSVD | RSVD | RSVD | RSVD | SDW |

| R/O | R/O | R/O | R/O  | R/O  | R/O  | R/O  | R/W |

| BIT | NAME   | RESET     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-----|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|     |        |           | This bit enables/disables boot ROM. (Shadow the ROM).                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 0   | SDW    | SDW 0     | SDW = 0 When clear, the MCU executes from the 10K boot ROM space. The boot ROM appears in two locations: 0000h and 8000h. The 16K RAM is mapped to XDATA space; therefore, a read/write operation is possible. This bit is set by the MCU after the RAM load is completed. The MCU cannot clear this bit; it is cleared on power-up reset or watchdog time-out reset.     |  |  |  |

|     |        |           | SDW = 1 When set by the MCU, the 10K boot ROM maps to location 8000h, and the 16K RAM is mapped to code space, starting at location 0000h. At this point, the MCU executes from RAM, and the write operation is disabled (no write operation is possible in code space).                                                                                                  |  |  |  |

| 4-1 | RSVD   | No effect | These bits are always read as 0000b.                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 6-5 | S[1:0] | No effect | Code space size. These bits define the ROM or RAM code-space size (bit 7 (ROA) defines ROM or RAM).<br>These bits are permanently set to 10b, indicating 16K bytes of code space, and are not affected by reset (see<br>Table 5-1).<br>00 = 4K bytes code space size<br>01 = 8K bytes code space size<br>10 = 16K bytes code space size<br>11 = 32K bytes code space size |  |  |  |

| 7   | ROA    | No effect | ROM or RAM version. This bit indicates whether the code space is RAM or ROM based. This bit is permanently set to 1, indicating the code space is RAM, and is not affected by reset (see Table 5-1).<br>ROA = 0 Code space is ROM<br>ROA = 1 Code space is RAM                                                                                                            |  |  |  |

#### Table 5-1. ROM and RAM Size Definition Table

| ROM              | IS REGISTI       | ER               | DOOT DOM           | DAM CODE           | DOM CODE            |

|------------------|------------------|------------------|--------------------|--------------------|---------------------|

| ROA              | S1               | S0               | BOOT ROM           | RAM CODE           | ROM CODE            |

| 0                | 0                | 0                | None               | None               | 4K                  |

| 0                | 0                | 1                | None               | None               | 8K                  |

| 0                | 1                | 0                | None               | None               | 16K (reserved)      |

| 1                | 1                | 1                | None               | None               | 32K (reserved)      |

| 1                | 0                | 0                | 10K                | 4K                 | None                |

| 1                | 0                | 1                | 10K                | 8K                 | None                |

| 1 <sup>(1)</sup> | 1 <sup>(1)</sup> | 0 <sup>(1)</sup> | 10K <sup>(1)</sup> | 16K <sup>(1)</sup> | None <sup>(1)</sup> |

| 1                | 1                | 1                | 10K                | 32K (reserved)     | None                |

(1) This is the hardwired setting.

#### 5.5.2.1.2 Boot Operation (MCU Firmware Loading)

Because the code space is in RAM (with the exception of the boot ROM), the TUSB3410 firmware must be loaded from an external source. Two sources are available for booting: one from an external serial EEPROM connected to the I<sup>2</sup>C bus and the other from the host through the USB. On device reset, bit 0 (SDW) in the ROMS register (see Section 5.5.2.1.1) and bit 7 (CONT) in the USBCTL register (see Section 5.5.5.4) are cleared. This configures the memory space to boot mode (see Table 5-3) and keeps the device disconnected from the host. The first instruction is fetched from location 0000h (which is in the 10K ROM). The 16K RAM is mapped to XDATA space (location 0000h). The MCU executes a read from an external EEPROM and tests whether it contains the code (by testing for boot signature). If it contains the code, then the MCU reads from EEPROM and writes to the 16K RAM in XDATA space. If it does not contain the code, then the MCU proceeds to boot from the USB.

When the code is loaded, the MCU sets the SDW bit to 1 in the ROMS register. This switches the memory map to normal mode; that is, the 16K RAM is mapped to code space, and the MCU starts executing from location 0000h. When the switch is done, the MCU sets the CONT bit to 1 in the USBCTL register. This connects the device to the USB and results in normal USB device enumeration.

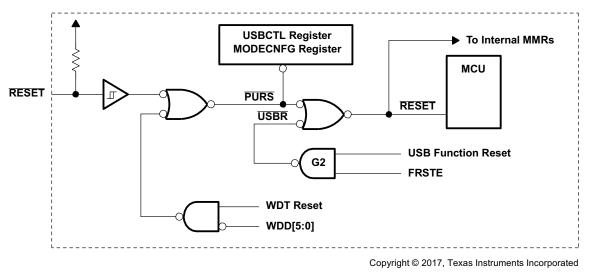

#### 5.5.2.1.3 WDCSR: Watchdog Timer, Control, and Status Register (Addr:FF93h)

A watchdog timer (WDT) with 1-ms clock is provided. If this register is not accessed for a period of 128 ms, then the WDT counter resets the MCU (see Figure 5-9). The watchdog timer is enabled by default and can be disabled by writing a pattern of 101010b into the WDD[5:0] bits. The 1-ms clock for the watchdog timer is generated from the SOF pulses. Therefore, for the watchdog timer to count, bit 7 (CONT) in the USBCTL register (see Section 5.5.5.4) must be set.

| 7    | 6   | 5    | 4    | 3    | 2    | 1    | 0   |

|------|-----|------|------|------|------|------|-----|

| WDD0 | WDR | WDD5 | WDD4 | WDD3 | WDD2 | WDD1 | WDT |

| R/W  | R/C | R/W  | R/W  | R/W  | R/W  | R/W  | W/O |

| BIT | NAME     | RESET | FUNCTION                                                                                                                                                                                                                                                                                                          |  |  |  |

|-----|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0   | WDT      | 0     | MCU must write a 1 to this bit to prevent the watchdog timer from resetting the MCU. If the MCU does not write a 1 in a period of 128 ms, the watchdog timer resets the device. Writing a 0 has no effect on the watchdog timer. (The watchdog timer is a 7-bit counter using a 1-ms CLK.) This bit is read as 0. |  |  |  |

| 5-1 | WDD[5:1] | 00000 | These bits disable the watchdog timer. For the timer to be disabled these bits must be set to 10101b and bit 7 (WDD0) must also be set to 0. If any other pattern is present, then the watchdog timer is in operation.                                                                                            |  |  |  |

|     |          |       | Watchdog reset indication bit. This bit indicates if the reset occurred due to power-on reset or watchdog timer reset.                                                                                                                                                                                            |  |  |  |

| 6   | WDR      | 0     | WDR = 0 A power-up reset occurred                                                                                                                                                                                                                                                                                 |  |  |  |

|     |          |       | WDR = 1 A watchdog time-out reset occurred. To clear this bit, the MCU must write a 1. Writing a 0 has no effect.                                                                                                                                                                                                 |  |  |  |

| 7   | WDD0     | 1     | This bit is one of the six disable bits for the watchdog timer. This bit must be cleared in order for the watchdog timer to be disabled.                                                                                                                                                                          |  |  |  |

#### 5.5.3 Buffers + I/O RAM Map

The address range from F800h to FFFFh (2K bytes) is reserved for data buffers, setup packet, endpoint descriptors block (EDB), and all I/O. There are 128 locations reserved for memory-mapped registers (MMR). Table 5-2 represents the XDATA space allocation and access restriction for the DMA, USB buffer manager (UBM), and MCU.

| DESCRIPTION                                | ADDRESS RANGE | UBM ACCESS          | DMA ACCESS                           | MCU<br>ACCESS |

|--------------------------------------------|---------------|---------------------|--------------------------------------|---------------|

| Internal MMRs<br>(Memory-Mapped Registers) | FFFFh-FF80h   | No<br>(Only EDB-0)  | No<br>(only data register and EDB-0) | Yes           |

| EDB<br>(Endpoint Descriptors Block)        | FF7Fh-FF08h   | Only for EDB update | Only for EDB update                  | Yes           |

| Setup Packet                               | FF07h-FF00h   | Yes                 | No                                   | Yes           |

| Input Endpoint-0 Buffer                    | FEFFh-FEF8h   | Yes                 | Yes                                  | Yes           |

| Output Endpoint-0 Buffer                   | FEF7h-FEF0h   | Yes                 | Yes                                  | Yes           |

| Data Buffers                               | FEEFh-F800h   | Yes                 | Yes                                  | Yes           |

#### Table 5-2. XDATA Space

# Table 5-3. Memory-Mapped Registers Summary (XDATA Range = FF80h $\rightarrow$ FFFFh)

| ADDRESS     | REGISTER | DESCRIPTION                                |

|-------------|----------|--------------------------------------------|

| FFFFh       | FUNADR   | Function address register                  |

| FFFEh       | USBSTA   | USB status register                        |

| FFFDh       | USBMSK   | USB interrupt mask register                |

| FFFCh       | USBCTL   | USB control register                       |

| FFFBh       | MODECNFG | Mode configuration register                |

| FFFAh-FFF4h | _        | Reserved                                   |

| FFF3h       | I2CADR   | I <sup>2</sup> C-port address register     |

| FFF2h       | I2CDATI  | I <sup>2</sup> C-port data input register  |

| FFF1h       | I2CDATO  | I <sup>2</sup> C-port data output register |

| FFF0h       | I2CSTA   | I <sup>2</sup> C-port status register      |

| FFEFh       | SERNUM7  | Serial number byte 7 register              |

| FFEEh       | SERNUM6  | Serial number byte 6 register              |

| FFEDh       | SERNUM5  | Serial number byte 5 register              |

| FFECh       | SERNUM4  | Serial number byte 4 register              |

| FFEBh       | SERNUM3  | Serial number byte 3 register              |

| FFEAh       | SERNUM2  | Serial number byte 2 register              |

| FFE9h       | SERNUM1  | Serial number byte 1 register              |

| FFE8h       | SERNUM0  | Serial number byte 0 register              |

| FFE7h-FFE6h | —        | Reserved                                   |

| FFE5h       | DMACSR3  | DMA-3: Control and status register         |

| FFE4h       | DMACDR3  | DMA-3: Channel definition register         |

| FFE3h-FFE2h | Reserved |                                            |

| FFE1h       | DMACSR1  | DMA-1: Control and status register         |

| FFE0h       | DMACDR1  | DMA-1: Channel definition register         |

| FFDFh-FFACh | —        | Reserved                                   |

| FFABh       | MASK     | UART: Interrupt mask register              |

| FFAAh       | XOFF     | UART: Xoff register                        |

| FFA9h       | XON      | UART: Xon register                         |

Copyright © 2002–2017, Texas Instruments Incorporated

| (XDATA Range = FF80h $\rightarrow$ FFFFh) (continued) |           |                                            |  |  |  |

|-------------------------------------------------------|-----------|--------------------------------------------|--|--|--|

| ADDRESS                                               | REGISTER  | DESCRIPTION                                |  |  |  |

| FFA8h                                                 | DLH       | UART: Divisor high-byte register           |  |  |  |

| FFA7h                                                 | DLL       | UART: Divisor low-byte register            |  |  |  |

| FFA6h                                                 | MSR       | UART: Modem status register                |  |  |  |

| FFA5h                                                 | LSR       | UART: Line status register                 |  |  |  |

| FFA4h                                                 | MCR       | UART: Modem control register               |  |  |  |

| FFA3h                                                 | FCRL      | UART: Flow control register                |  |  |  |

| FFA2h                                                 | LCR       | UART: Line control registers               |  |  |  |

| FFA1h                                                 | TDR       | UART: Transmitter data registers           |  |  |  |

| FFA0h                                                 | RDR       | UART: Receiver data registers              |  |  |  |

| FF9Eh                                                 | PUR_3     | GPIO: Pullup register for port 3           |  |  |  |

| FF9Dh-FF94h                                           | —         | Reserved                                   |  |  |  |

| FF93h                                                 | WDCSR     | Watchdog timer control and status register |  |  |  |

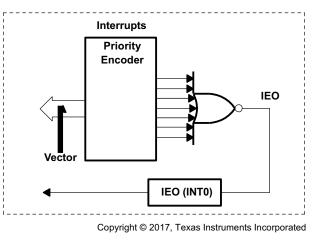

| FF92h                                                 | VECINT    | Vector interrupt register                  |  |  |  |

| FF91h                                                 | —         | Reserved                                   |  |  |  |

| FF90h                                                 | ROMS      | ROM shadow configuration register          |  |  |  |

| FF8Fh-FF84h                                           | —         | Reserved                                   |  |  |  |

| FF83h                                                 | OEPBCNT_0 | Output endpoint_0: Byte count register     |  |  |  |

| FF82h                                                 | OEPCNFG_0 | Output endpoint_0: Configuration register  |  |  |  |

| FF81h                                                 | IEPBCNT_0 | Input endpoint_0: Byte count register      |  |  |  |

| FF80h                                                 | IEPCNFG_0 | Input endpoint_0: Configuration register   |  |  |  |

# Table 5-3. Memory-Mapped Registers Summary

#### Table 5-4. EDB Memory Locations

| ADDRESS     | REGISTER    | DESCRIPTION                             |

|-------------|-------------|-----------------------------------------|

| FF7Fh-FF60h | —           | Reserved                                |

| FF5Fh       | IEPSIZXY_3  | Input endpoint_3: X-Y buffer size       |

| FF5Eh       | IEPBCTY_3   | Input endpoint_3: Y-byte count          |

| FF5Dh       | IEPBBAY_3   | Input endpoint_3: Y-buffer base address |

| FF5Ch       | —           | Reserved                                |

| FF5Bh       | —           | Reserved                                |

| FF5Ah       | IEPBCTX_3   | Input endpoint_3: X-byte count          |

| FF59h       | IEPBBAX     | Input endpoint_3: X-buffer base address |

| FF58h       | IEPCNF_3    | Input endpoint_3: Configuration         |

| FF57h       | IEPSIZXY_2v | Input endpoint_2: X-Y buffer size       |

| FF56h       | IEPBCTY_2   | Input endpoint_2: Y-byte count          |

| FF55h       | IEPBBAY_2   | Input endpoint_2: Y-buffer base address |

| FF54h       | —           | Reserved                                |

| FF53h       | —           | Reserved                                |

| FF52h       | IEPBCTX_2   | Input endpoint_2: X-byte count          |

| FF51h       | IEPBBAX_2   | Input endpoint_2: X-buffer base address |

| FF50h       | IEPCNF_2    | Input endpoint_2: Configuration         |

| FF4Fh       | IEPSIZXY_1  | Input endpoint_1: X-Y buffer size       |

| FF4Eh       | IEPBCTY_1   | Input endpoint_1: Y-byte count          |

| FF4Dh       | IEPBBAY_1   | Input endpoint_1: Y-buffer base address |

| FF4Ch       | —           | Reserved                                |

| FF4Bh       | —           | Reserved                                |

| ADDRESS        | REGISTER   | DESCRIPTION                              |

|----------------|------------|------------------------------------------|

| FF4Ah          | IEPBCTX_1  | Input endpoint_1: X-byte count           |

| FF49h          | _          |                                          |

| FF48h          | IEPBBAX_1  | Input endpoint_1: X-buffer base address  |

| FF400<br>FF47h | IEPCNF_1   | Input endpoint_1: Configuration          |

|                | _          | Reserved                                 |

| FF20h          |            |                                          |

| FF1Fh          | OEPSIZXY_3 | Output endpoint_3: X-Y buffer size       |

| FF1Eh          | OEPBCTY_3  | Output endpoint_3: Y-byte count          |

| FF1Dh          | OEPBBAY_3  | Output endpoint_3: Y-buffer base address |

| FF1Bh-FF1Ch    | _          | Reserved                                 |

| FF1Ah          | OEPBCTX_3  | Output endpoint_3: X-byte count          |