参考資料

UCC256402, UCC256403, UCC256404 JAJSHM6E - JUNE 2019 - REVISED FEBRUARY 2021

# UCC25640x 超低可聴ノイズ、超低スタンバイ電力の LLC 共振コントローラ

### 1 特長

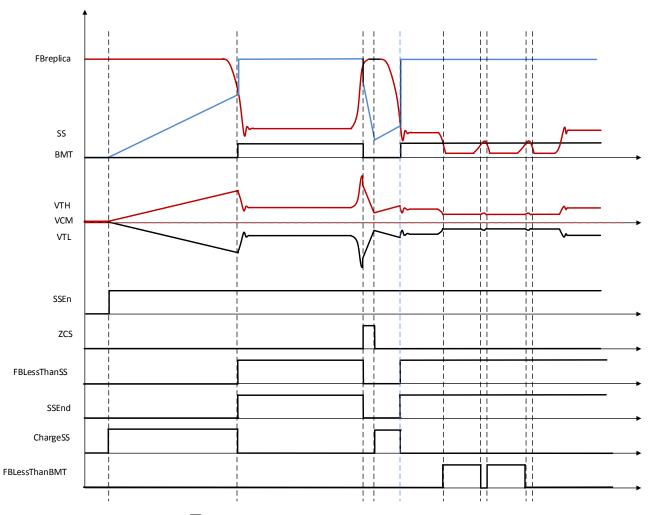

- 最適化された低消費電力モードおよびバースト・モー ド・アルゴリズム

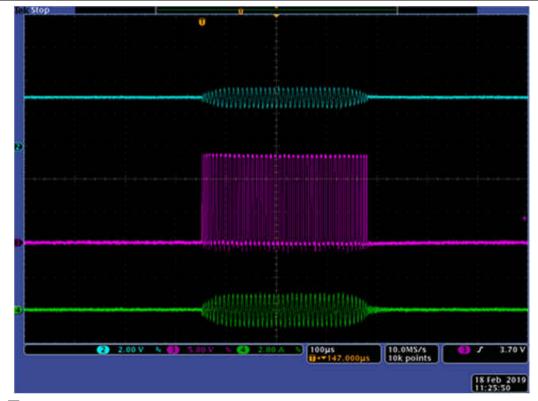

- ソフトオン / ソフトオフ期間付きのバースト・モード

- 無負荷時およびスタンバイ時の可聴ノイズを最小化

- ユーザーがバースト・モードをディセーブル可能

- フォトカプラの低消費電力動作

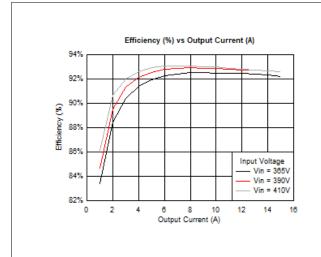

- DoE Level VI および EU CoC Tier-2 外部電源規 格を上回る効率性能

- ハイブリッド・ヒステリシス制御 (HHC)

- クラス最高の過渡応答

- バースト・モードの高速終了

- 堅牢なアダプティブ・デッドタイム制御

- ソース電流 0.6A、シンク電流 1.2A の駆動能力を備え た高電圧ゲート・ドライバ内蔵

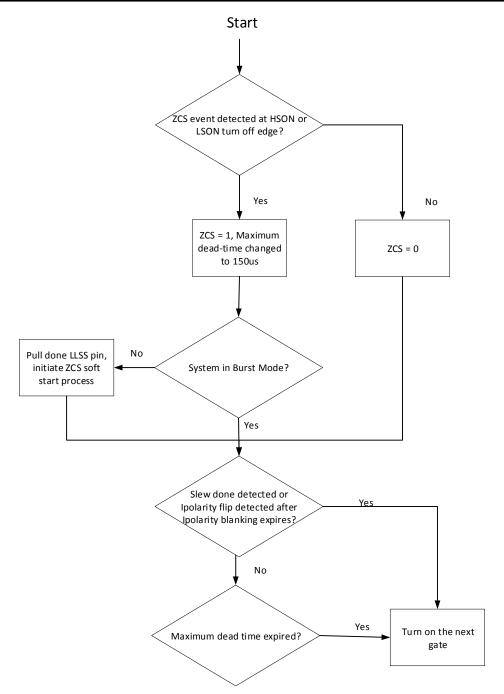

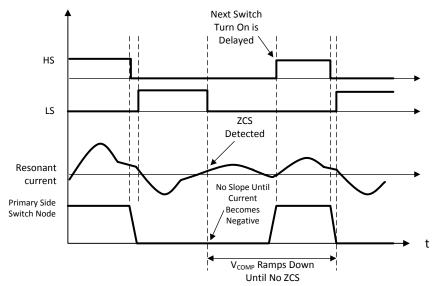

- 堅牢な容量性領域 (ZCS) 回避方式

- 過熱、出力過電圧、入力低電圧保護、 3レベルの過電流保護

- 高電圧スタートアップ機能を内蔵

- アクティブ X コンデンサ放電機能

# 2 アプリケーション

- テレビ用 SMPS 電源

- 照明

- AC/DC アダプタ

- 電動工具

- 医療用電源

- 多機能プリンタ

- エンタープライズやシネマ用プロジェクタ

- PC 電源

- ゲーム機の電源

### 3 概要

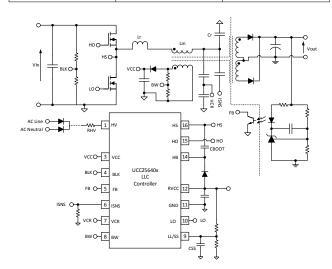

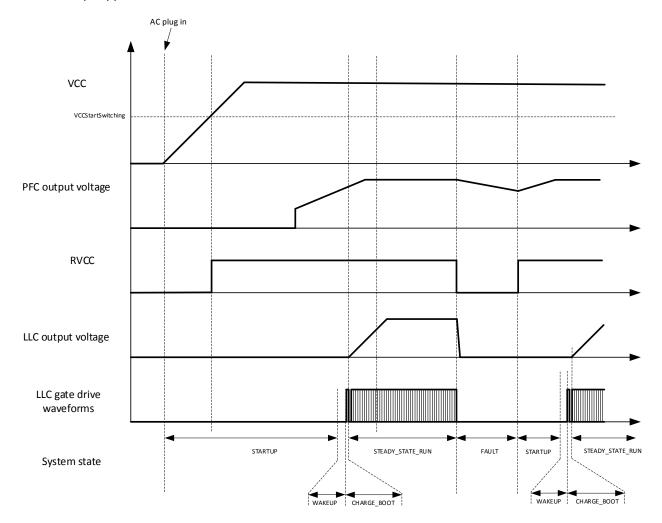

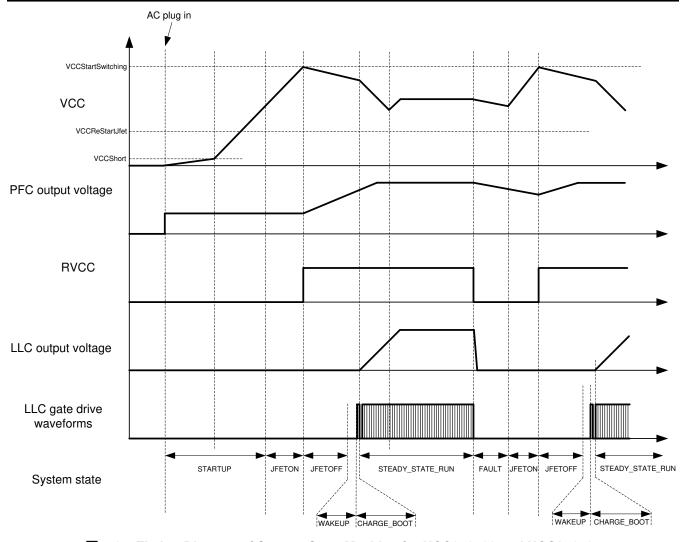

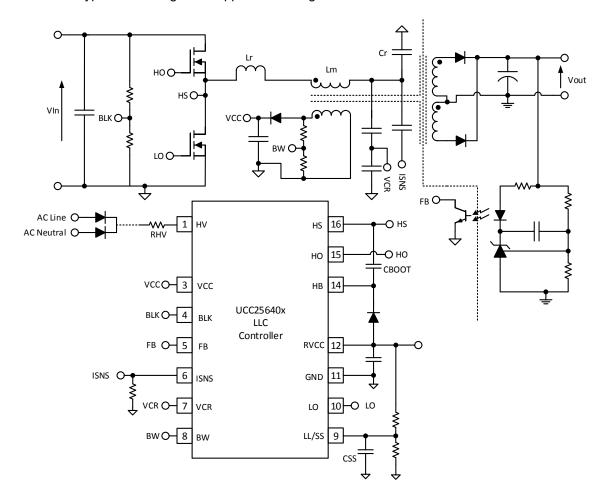

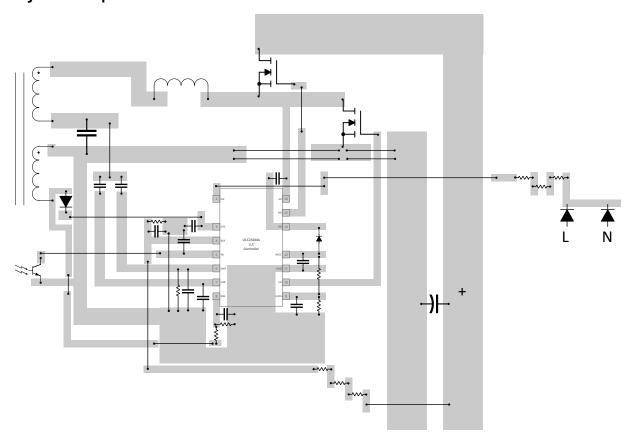

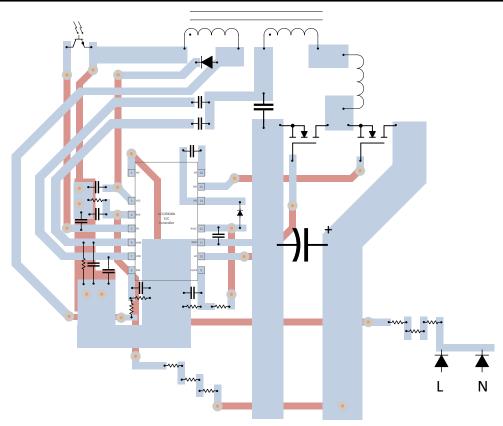

UCC25640x は、高電圧ゲート・ドライバを内蔵したフル機 能の LLC コントローラです。本デバイスは、最小限の外付 け部品で完全な電源システムを構築するため、PFC コント ローラと組み合わせるように設計されています。その結果 完成する電源システムは、スタンバイ電力コンバータを別 途必要とせずに、スタンバイ電力の最も厳格な要件を満た すように設計されています。

UCC25640x は、ソフトオン / ソフトオフ期間付き高効率バ ースト・モードにより、スタンバイ動作時の可聴ノイズを最小 限に抑えることができます。バースト電力レベルとヒステリ シスをプログラムできるため、効率とバースト・モード動作を 簡単に最適化できます。バースト・モードは、ピン構成によ りディセーブルすることもできます。UCC25640x は、クラ ス最高のラインおよび負荷過渡応答を実現するため、ハイ ブリッド・ヒステリシス制御を採用しています。

UCC25640x は LLC コンバータの動作を適切に制御お よび保護するために設計された広範な機能を備えていま す。UCC28056/UCC28064A PFC コントローラ、 UCC24624 同期整流コントローラと組み合わせることで、 完全な電源ソリューションを実現できます。

### 製品情報

| 部品番号      | パッケージ | 本体サイズ (公称)    |  |  |  |  |  |

|-----------|-------|---------------|--|--|--|--|--|

| UCC256402 | SOIC  | 9.9mm × 3.9mm |  |  |  |  |  |

| UCC256403 | SOIC  | 9.9mm × 3.9mm |  |  |  |  |  |

| UCC256404 | SOIC  | 9.9mm × 3.9mm |  |  |  |  |  |

簡略回路図

# **Table of Contents**

| 2 アプリケーション                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 7.2 Functional Block Diagram                                                                                                                                              | 17                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| <b>4</b> / / //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             | 18                                                      |

| 3 概要                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             | 32                                                      |

| 4 Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8 Power Supply Recommendations                                                                                                                                              |                                                         |

| Device Comparison Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8.1 VCC Pin Capacitor                                                                                                                                                       |                                                         |

| 5 Pin Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.2 Boot Capacitor                                                                                                                                                          |                                                         |

| Pin Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3 8.3 RVCC Pin Capacitor3                                                                                                                                                   |                                                         |

| 6 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5 9 Layout                                                                                                                                                                  |                                                         |

| 6.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <sub>5</sub> 9.1 Layout Guidelines                                                                                                                                          |                                                         |

| 6.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 9.2 Layout Example5                                                                                                                                                       |                                                         |

| 6.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 10 Device and Documentation Support                                                                                                                                       |                                                         |

| 6.4 Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6 10.1 Documentation Support                                                                                                                                                |                                                         |

| 6.5 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6 10.2 Related Links                                                                                                                                                        |                                                         |

| 6.6 Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10.3 Receiving Notification of Documentation                                                                                                                                |                                                         |

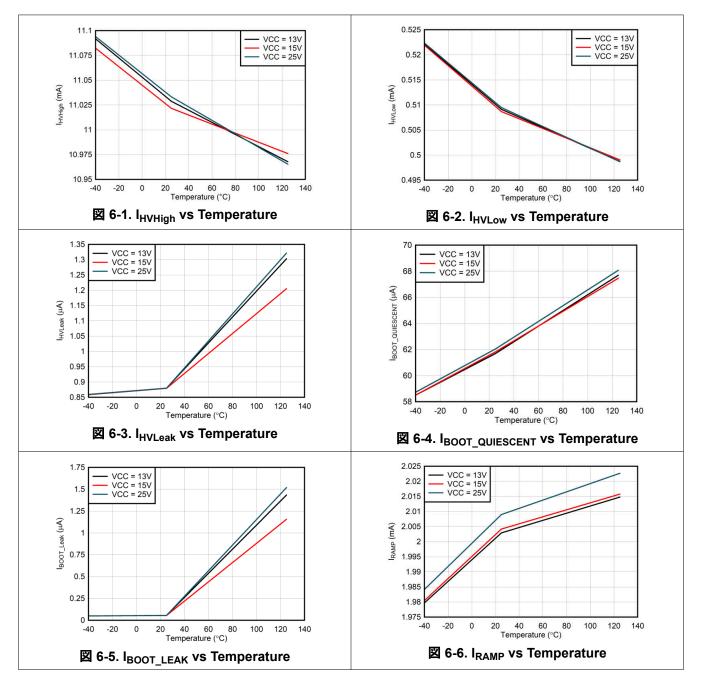

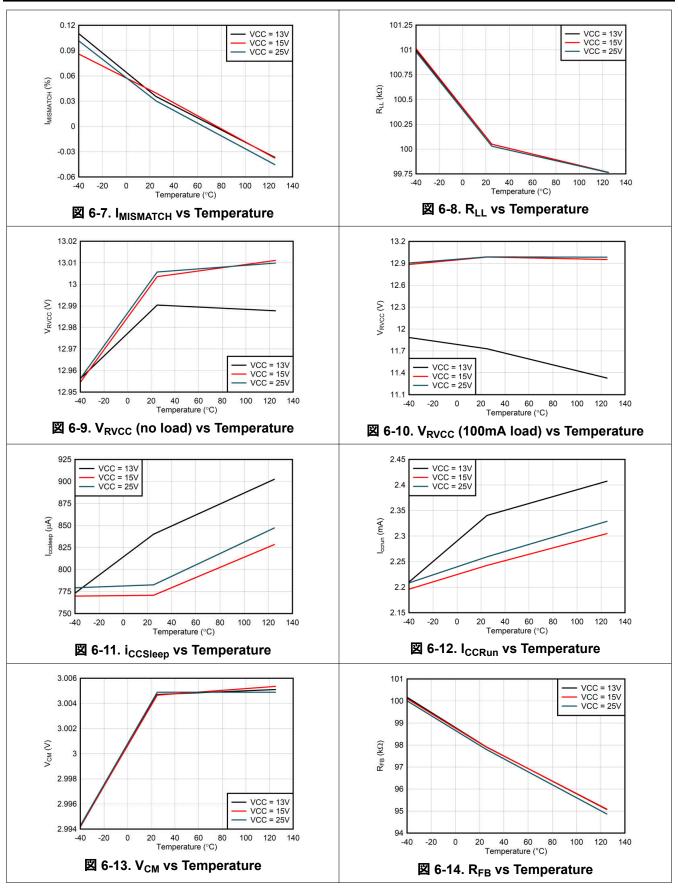

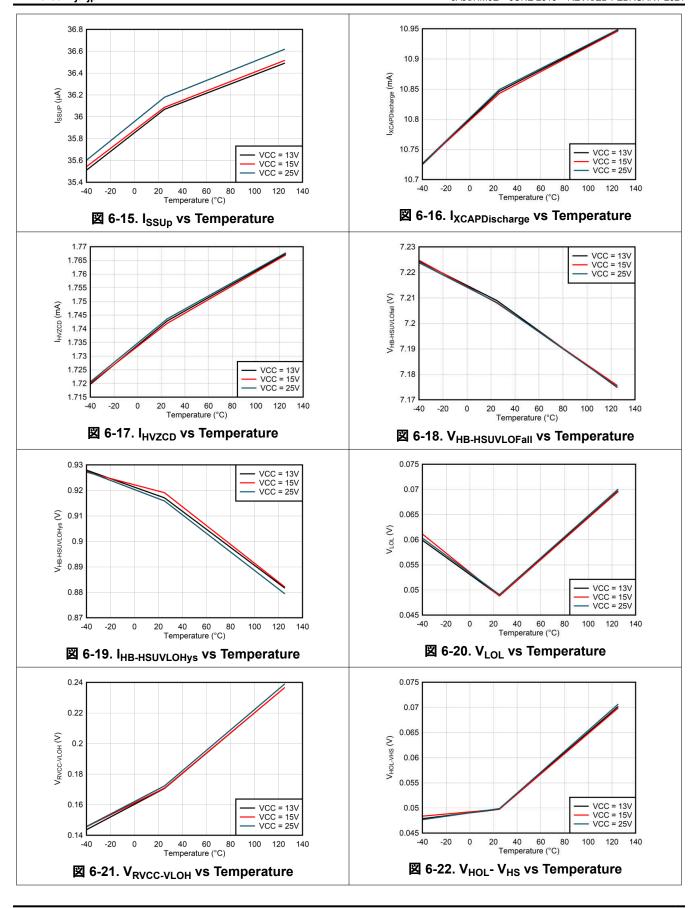

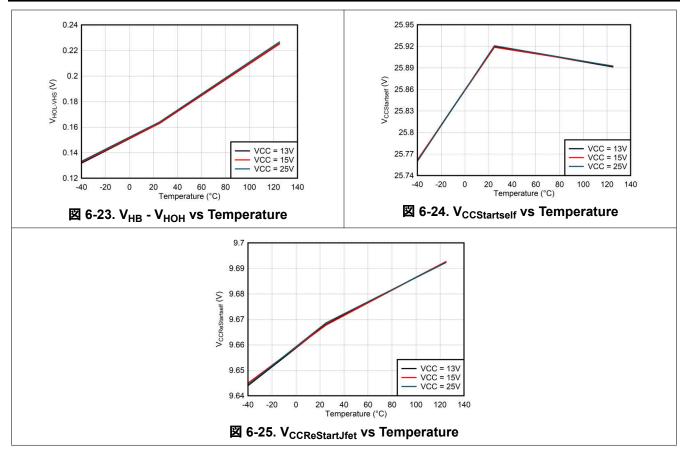

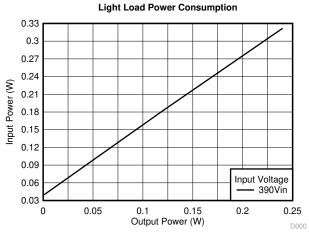

| 6.7 Typical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11 10.4 Community Resources                                                                                                                                                 |                                                         |

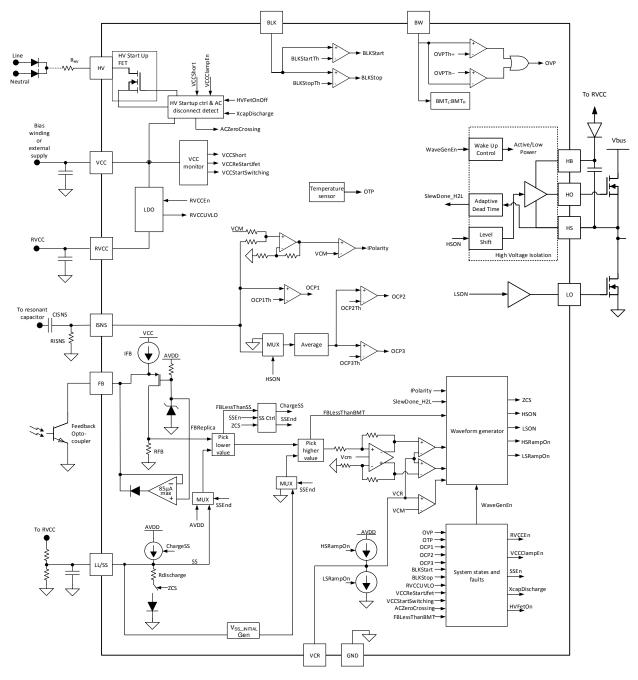

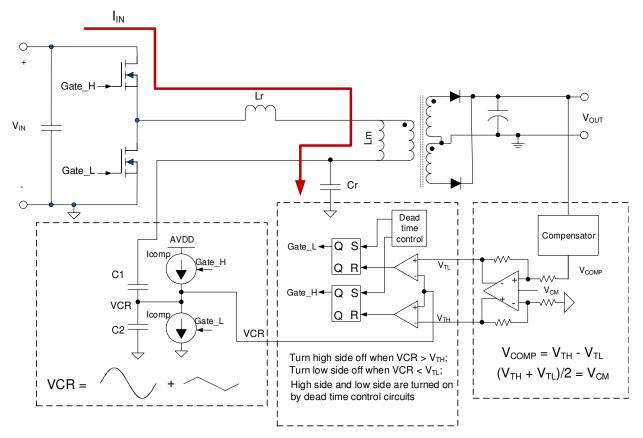

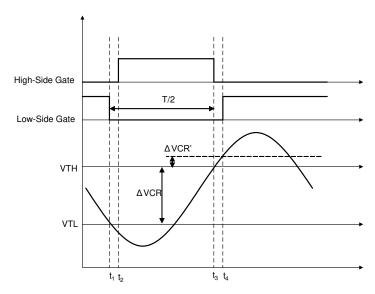

| 7 Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                             | 73                                                      |

| 7.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                             |                                                         |

| <b>4 Revision History</b><br>資料悉号末尾の英字け改訂を表しています <i>そ</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 一の改訂層豚け茁語版に進じています                                                                                                                                                           |                                                         |

| 4 Revision History<br>資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                             | Page                                                    |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |                                                         |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202<br>・ Updated Absolute Maximum Ratings HV,<br>Changes from Revision C (March 2020) to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum                                                                                             | Page                                                    |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202<br>・ Updated Absolute Maximum Ratings HV,<br>Changes from Revision C (March 2020) to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum                                                                                             | Page                                                    |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202<br>・ Updated Absolute Maximum Ratings HV,<br>Changes from Revision C (March 2020) to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum  D Revision D (September 2020)                                                              | Page                                                    |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202<br>・ Updated Absolute Maximum Ratings HV,<br>Changes from Revision C (March 2020) to<br>・ Added update to Device Comparison Tab<br>Changes from Revision B (November 201                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum  D Revision D (September 2020)  Dile  9) to Revision C (March 2020)                         | Page<br>Page                                            |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202<br>• Updated Absolute Maximum Ratings HV,<br>Changes from Revision C (March 2020) to<br>• Added update to Device Comparison Tab<br>Changes from Revision B (November 201<br>• パッケージの説明を SOIC (14) から SOIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum  D Revision D (September 2020)  Dile                                                        | Page Page                                               |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 2020)  Updated Absolute Maximum Ratings HV,  Changes from Revision C (March 2020) to  Added update to Device Comparison Tab  Changes from Revision B (November 2010)  パッケージの説明を SOIC (14) から SOIC  Changed name of Pin 2 from Missing to F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum  D Revision D (September 2020)  Dile                                                        | Page Page                                               |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 2020)  Updated Absolute Maximum Ratings HV,  Changes from Revision C (March 2020) to  Added update to Device Comparison Tab  Changes from Revision B (November 2010)  Changes from Revision B (November 2010)  Changed name of Pin 2 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Form Changed name of Pin 13 from Missing to Pin 14 from Missing to Pin 15 from Missing to Pin 15 from Missing to Pin 16 from Missing to Pin 16 from Missing to Pin 17 from Missing to Pin 18 from | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum  D Revision D (September 2020)  Dile  9) to Revision C (March 2020)  に変更                    | Page Page                                               |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 202<br>・ Updated Absolute Maximum Ratings HV,<br>Changes from Revision C (March 2020) to<br>・ Added update to Device Comparison Tab<br>Changes from Revision B (November 201<br>・ パッケージの説明を SOIC (14) から SOIC<br>・ Changed name of Pin 2 from Missing to Form Changed name of Pin 13 from Missing to Form Added description of BLK OVP threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum  D Revision D (September 2020)  Dile  9) to Revision C (March 2020)  に変更  Removed Removed S | Page Page 3                                             |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 2020)  Updated Absolute Maximum Ratings HV,  Changes from Revision C (March 2020) to  Added update to Device Comparison Tab  Changes from Revision B (November 2010)  Changes from Revision B (November 2010)  Changed name of Pin 2 from Missing to Found to Changed name of Pin 13 from Missing to Found to Added description of BLK OVP threshold Added input over voltage protection description description description of BLK OVP threshold Added input over voltage protection description of BLK OVP threshold Added input over voltage protection description of BLK OVP threshold Added input over voltage protection description of BLK OVP threshold Added input over voltage protection description of BLK OVP threshold Added input over voltage protection description of BLK OVP threshold threshold in the protection of BLK OVP threshold threshold input over voltage protection description of BLK OVP threshold threshold input over voltage protection description of BLK OVP threshold threshold input over voltage protection description of BLK OVP threshold threshold threshold input over voltage protection description of BLK OVP threshold thresh | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum                                                                                             | Page 93 93 94 94 95 95 95 95 95 95 95 95 95 95 95 95 95 |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 2020)  Updated Absolute Maximum Ratings HV,  Changes from Revision C (March 2020) to  Added update to Device Comparison Tab  Changes from Revision B (November 2010)  Changes from Revision B (November 2010)  Changed name of Pin 2 from Missing to Form Changed name of Pin 13 from Missing to Form Added description of BLK OVP threshold Added input over voltage protection descent Changed R <sub>FB</sub> to R <sub>LL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum                                                                                             | Page Page 3                                             |

| 資料番号末尾の英字は改訂を表しています。そ<br>Changes from Revision D (September 2020)  Updated Absolute Maximum Ratings HV,  Changes from Revision C (March 2020) to  Added update to Device Comparison Tab  Changes from Revision B (November 2010)  Changes from Revision B (November 2010)  Changed name of Pin 2 from Missing to Form Changed name of Pin 13 from Missing to Form Added description of BLK OVP threshold Added input over voltage protection descent Changed R <sub>FB</sub> to R <sub>LL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20) to Revision E (February 2021)  HB Input Voltage from 640 V to 700 V maximum                                                                                             | Page Page 3                                             |

マーケティング・ステータスを事前情報から量産データに変更。......1

Changes from Revision A (August 2019) to Revision B (November 2019)

Page

# **Device Comparison Table**

| Device                    | Integrated High<br>Voltage Startup | Integrated X-<br>Capacitor<br>Discharge | Requires<br>External Bias<br>Supply | Burst Soft On and Soft Off | BLK OVP | BW OVP Mode |

|---------------------------|------------------------------------|-----------------------------------------|-------------------------------------|----------------------------|---------|-------------|

| UCC256402                 | Yes                                | No                                      | No                                  | No                         | No      | Restart     |

| UCC256402A                | Yes                                | No                                      | No                                  | No                         | Yes     | Restart     |

| UCC256403                 | No                                 | No                                      | Yes                                 | Yes                        | No      | Restart     |

| UCC256403A                | No                                 | No                                      | Yes                                 | No                         | No      | Latch       |

| UCC256404                 | Yes                                | Yes                                     | No                                  | Yes                        | No      | Restart     |

| UCC256404A                | Yes                                | Yes                                     | No                                  | No                         | No      | Latch       |

| UCC256404B <sup>(1)</sup> | Yes                                | Yes                                     | No                                  | Yes                        | No      | Restart     |

<sup>(1)</sup> The X capacitor discharge feature of this device has not been tested by certification agency and was qualified by similarity under the existing UCC25640x certification

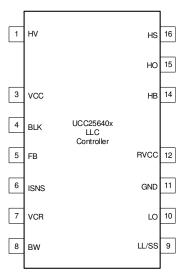

# **5 Pin Configuration and Functions**

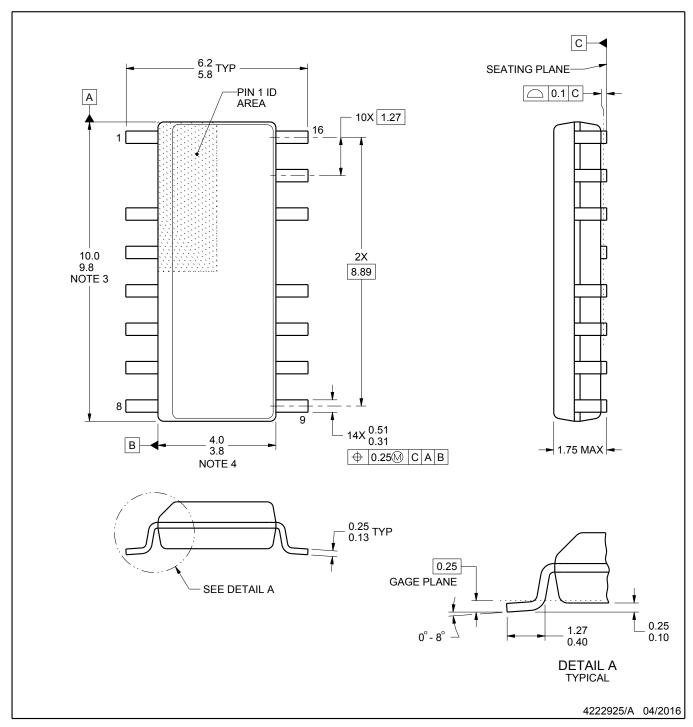

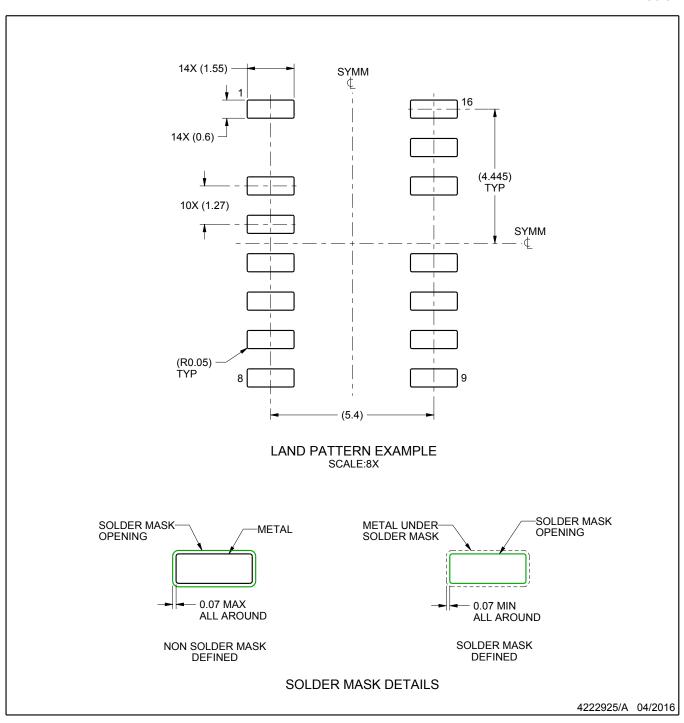

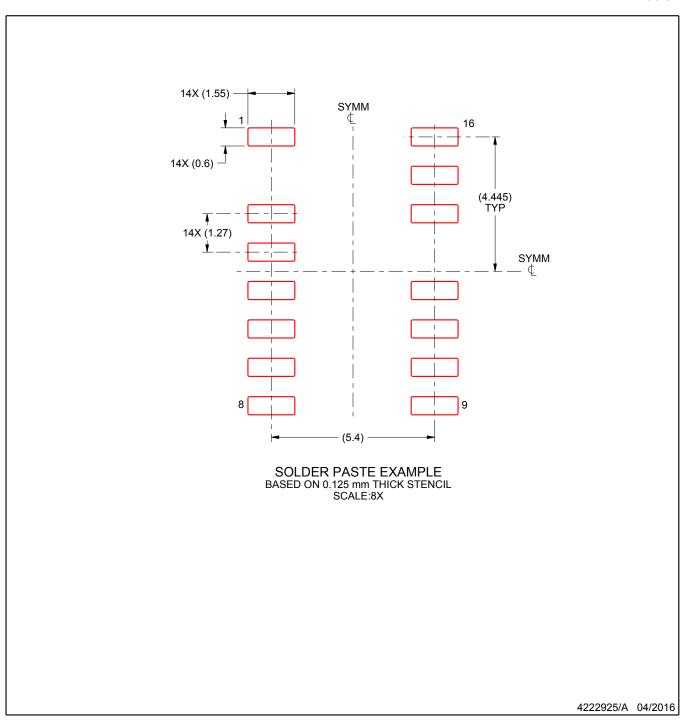

図 5-1. DDB Package 16-Pin SOIC (Pins 2, 13 removed) Top View

### **Pin Functions**

| P    | PIN |     | DESCRIPTION                                                                                                                                                                                                                                                                                       |

|------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                       |

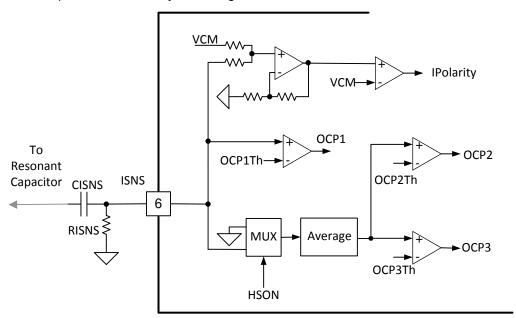

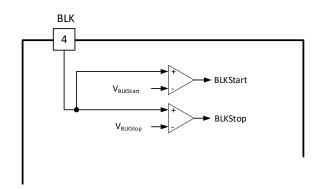

| BLK  | 4   | I   | This pin is used to sense the LLC stage input voltage level. A resistor divider should be used to attenuate the signal before it is applied to this pin. The voltage level on this pin will determine when the LLC converter starts/stops switching.                                              |

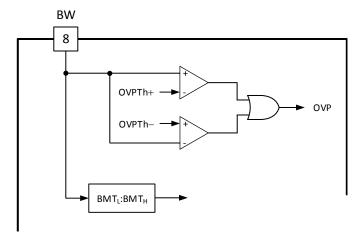

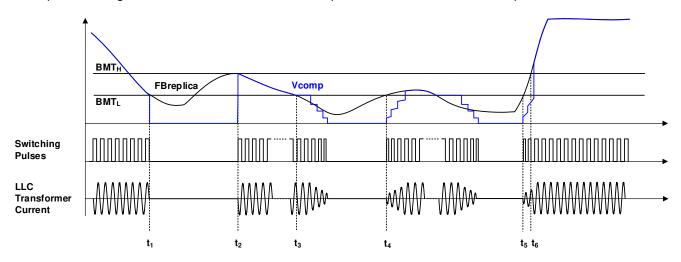

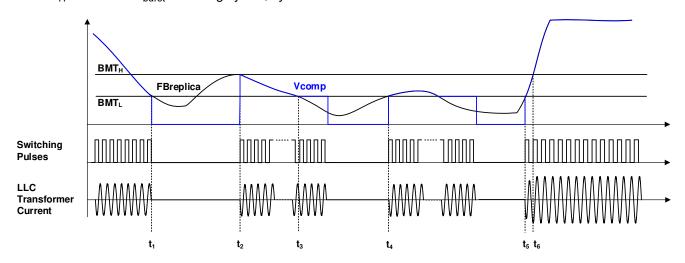

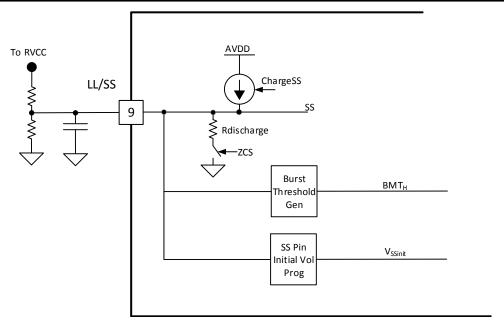

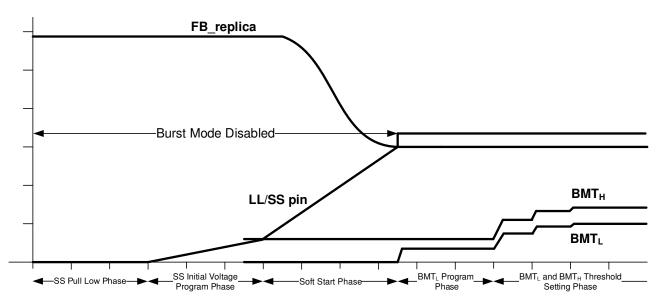

| BW   | 8   | I   | This pin is used to sense the output voltage through the bias winding. The sensed voltage is used for output over voltage protection. During startup, the pin is also used to program the ratio between the two burst mode thresholds ( $BMT_L$ and $BMT_H$ ).                                    |

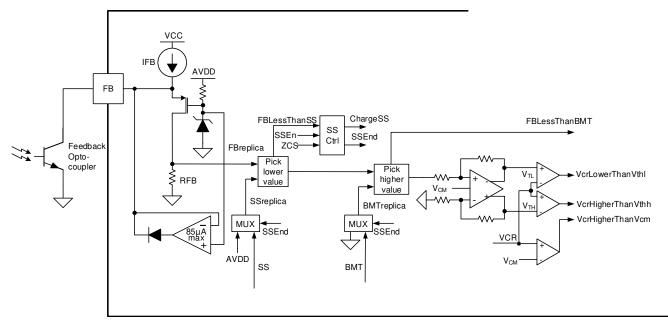

| FB   | 5   | I   | LLC stage control feedback input. The amount of current sourced from this pin will determine the LLC input power level.                                                                                                                                                                           |

| GND  | 11  | G   | Ground reference for all signals.                                                                                                                                                                                                                                                                 |

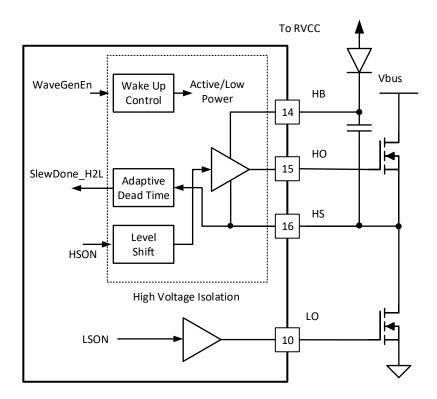

| НВ   | 14  | I   | High-side gate-drive floating supply voltage. The bootstrap capacitor is connected between this pin and HS pin. A high voltage, high speed diode should be connected from RVCC to this pin to supply power to the high-side gate-driver during the period when the low-side MOSFET is conducting. |

| НО   | 15  | 0   | High-side floating gate-drive output.                                                                                                                                                                                                                                                             |

| HS   | 16  | I   | High-side gate-drive floating ground. Current return for the high-side gate-drive current.                                                                                                                                                                                                        |

| P       | PIN |     | DESCRIPTION                                                                                                                                                                                                                                                                                      |  |

|---------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                      |  |

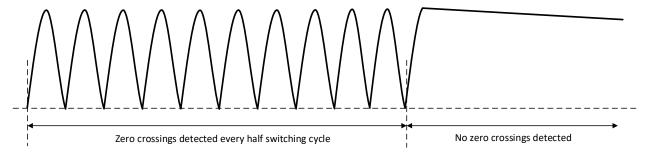

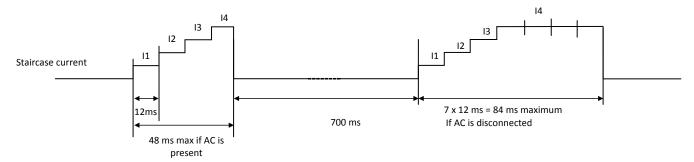

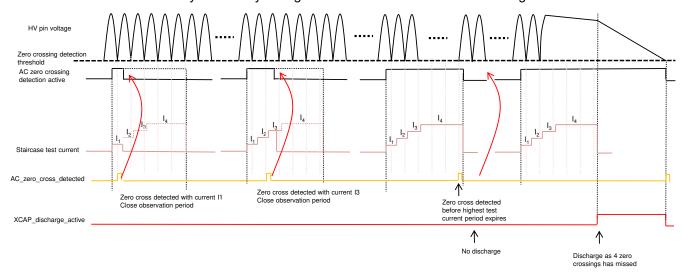

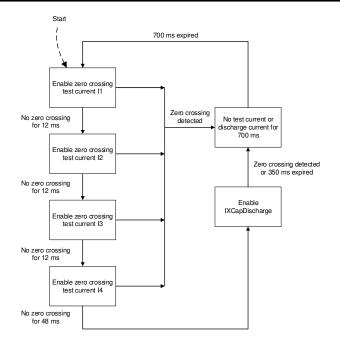

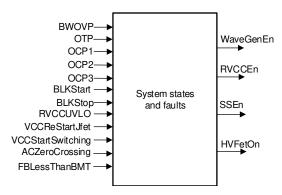

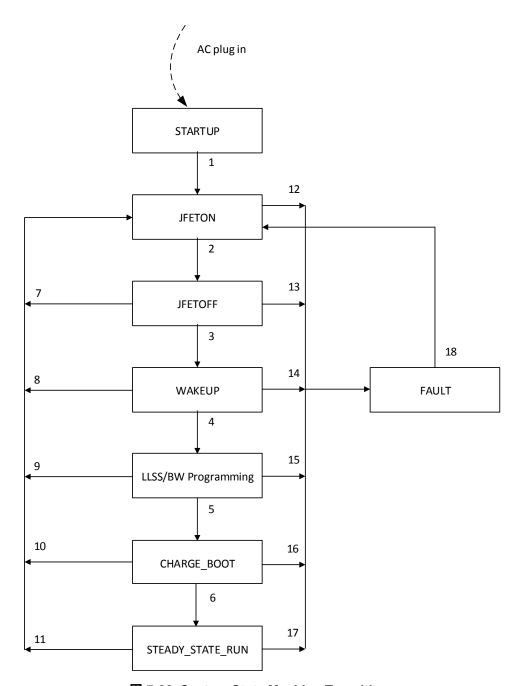

| HV      | 1   | I   | Connects to internal HV startup JFET. For UCC256402 and UCC256404, this pin provides start up power for both PFC and LLC stage. This pin also monitors the AC line voltage for x-capacitor discharge function. For UCC256403, this pin needs to be connected to ground.                          |  |