www.tij.co.jp JAJSBF2

# 4.5V~14V入力、 高電流同期バック・コンバータ

# 特長

● 入力電圧範囲: 4.5V~14V

● パワー・ブロック・テクノロジを内蔵

● 最大出力電流:25A

● 固定周波数オプション:300kHz、500kHz、1MHz

● ハイサイドおよびローサイドMOSFETのR<sub>DS(on)</sub> センシング

● プログラミング可能なソフト・スタート

● リファレンス電圧:600mV、精度1%

● フィードフォワード付き電圧モード制御

● プリバイアス出力をサポート

● 過熱シャットダウン

● 22ピンの5mm×6mm PQFN PowerPAD™パッケージ

# アプリケーション

- ポイント・オブ・ロード(POL)電源モジュール

- 通信およびネットワーク・アプリケーション用の高密度 DC/DCコンバータ

# 概要

TPS56221は、4.5V~14Vの電源で動作するよう設計された、 高効率、高電流の同期バック・コンバータです。最大25Aの負荷で 最小0.6Vの出力電圧を生成できます。NexFET™パワーMOSFET の内蔵により、省スペースと使いやすさを実現しています。

電圧モード制御を実装し、電圧フィードフォワード補償により入力電圧の変化に対して瞬時に応答します。

TPS56221は、熱特性強化型22ピンPQFN(DQP) PowerPAD™ パッケージで供給されます。

ソフト・スタート、過電流保護(OCP)レベル、ループ補償など、ユーザ・プログラミング可能な各種の機能により、設計の柔軟性が高まります。OCPレベルは、ILIMピンと回路のグランドとの間に接続される1個の外付け抵抗によってプログラミングできます。最初のパワーオン・シーケンス中、デバイスは校正サイクルに入り、ILIMピンの電圧を測定して、内部OCP電圧レベルを設定します。動作中、プログラミングされたOCP電圧レベルが、ローサイドFETのオン時の電圧降下と比較され、過電流状態が発生しているかどうかが確認されます。過電流状態の場合は、シャットダウン/再起動サイクルに入り、障害が解消されるまでこのサイクルを繰り返します。

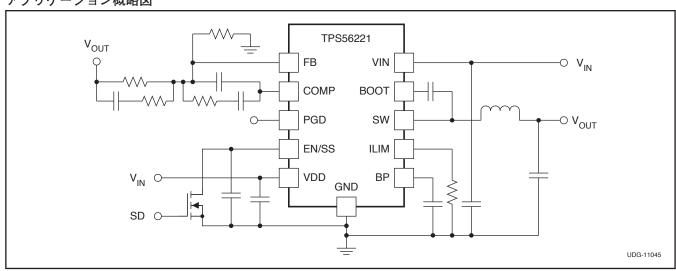

#### アプリケーション概略図

PowerPAD, NexFETは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補 助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。

Tiおよび日本Tiは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLUSAH5 翻訳版

最新の英語版資料 http://www.ti.com/lit/gpn/tps56221

# 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時に、MOSゲートに対する静電破壊を防止するために、リード線どうしを短絡しておくか、デバイスを導電性のフォームに入れる必要があります。

## 製品情報

| TA          | パッケージ          | ピン | 出荷形態    | 最小数量 | 型番           |

|-------------|----------------|----|---------|------|--------------|

| 4000- 45000 | プラスチックQFN(DQP) | 22 | テープ・リール | 250  | TPS56221DQPT |

| –40°C∼150°C |                |    | テーノ・リール | 2500 | TPS56221DQPR |

## 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

|                         |                                        | VAL  | UE   | 単位 |

|-------------------------|----------------------------------------|------|------|----|

|                         |                                        | MIN  | TYP  | 平辺 |

|                         | VDD, VIN                               | -0.3 | 16.5 | V  |

|                         | SW                                     | -3   | 25   |    |

| Waltana Danasa          | SW (< 100 ns pulse width, 10 µJ)       | -5   |      |    |

| Voltage Range           | BOOT                                   | -0.3 | 30   |    |

|                         | BOOT-SW (differential from BOOT to SW) | -0.3 | 7    |    |

|                         | COMP, PGOOD, FB, BP, EN/SS, ILIM       | -0.3 | 7    |    |

|                         | (HBM) QSS 009-105 (JESD22-A114A)       |      | 2    | kV |

| Electrostatic discharge | (CBM) QSS 009-147 (JESD22-C101B.01)    |      | 1.5  |    |

|                         | Junction, T <sub>J</sub>               | -40  | 150  | °C |

| Temperature             | Storage, T <sub>stq</sub>              | -55  | 150  |    |

<sup>(1)</sup> 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 熱特性について

|                  |                                              | TPS56221 |      |

|------------------|----------------------------------------------|----------|------|

|                  | THERMAL METRIC <sup>(1)</sup>                | PQFN     | 単位   |

|                  |                                              | 22 PINS  |      |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 34.6     |      |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 22.9     |      |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.6      | °C/W |

| ΨЈВ              | Junction-to-board characterization parameter | 5.0      |      |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 0.3      |      |

<sup>(1)</sup> 従来の熱特性パラメータと新しい熱特性パラメータの詳細については、アプリケーション・レポート『IC Package Thermal Metrics』 (SPRA953) を参照してください。

## 推奨動作条件

動作温度範囲内(特に記述のない限り)

|          |                                | MIN | TYP MAX | 単位 |

|----------|--------------------------------|-----|---------|----|

| $V_{DD}$ | VIN Input voltage              | 4.5 | 14      | ٧  |

| $T_{J}$  | Operating junction temperature | -40 | 125     | °C |

# 電気的特性

|                                  | パラメータ                                                         | テスト条件                                                                                                                                                             | MIN                   | TYP                 | MAX                   | 単位  |

|----------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------|-----------------------|-----|

| VOLTAGE                          | REFERENCE                                                     | 1                                                                                                                                                                 | <u> </u>              |                     |                       |     |

|                                  |                                                               | $T_J = 25^{\circ}C, 4.5 \text{ V} \le V_{VDD} \le 14 \text{ V}$                                                                                                   | 597                   | 600                 | 603                   |     |

| $V_{FB}$                         | FB input voltage                                              | -40°C ≤ T <sub>J</sub> ≤ 125°C,<br>4.5 V ≤ V <sub>VDD</sub> ≤ 14 V                                                                                                | 594                   | 600                 | 606                   | mV  |

| INPUT SUP                        | PLY                                                           |                                                                                                                                                                   |                       |                     |                       |     |

| $V_{VDD}$                        | Input supply voltage range                                    |                                                                                                                                                                   | 4.5                   |                     | 14                    | V   |

| IVDD <sub>SD</sub>               | Shutdown supply current                                       | V <sub>EN/SS</sub> = 0.2 V                                                                                                                                        |                       | 80                  | 120                   | μΑ  |

| IVDD <sub>Q</sub>                | Quiescent, non-switching                                      | Let EN/SS float, V <sub>FB</sub> = 1 V                                                                                                                            |                       | 2.5                 | 5.0                   | mA  |

| V <sub>UVLO</sub>                | UVLO ON Voltage                                               |                                                                                                                                                                   | 4.0                   |                     | 4.3                   | V   |

| V <sub>UVLO(HYS)</sub>           | UVLO hysteresis                                               |                                                                                                                                                                   | 500                   |                     | 700                   | mV  |

|                                  | OFT-START                                                     |                                                                                                                                                                   |                       |                     |                       |     |

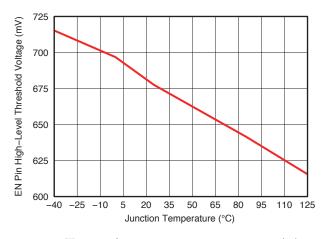

| V <sub>IH</sub>                  | High-level input voltage, EN/SS                               |                                                                                                                                                                   | 0.55                  | 0.70                | 1.00                  | V   |

| V <sub>IL</sub>                  | Low-level input voltage, EN/SS                                |                                                                                                                                                                   | 0.27                  | 0.30                | 0.33                  | V   |

| I <sub>SS</sub>                  | Soft-start source current                                     |                                                                                                                                                                   | 8                     | 10                  | 12                    | μΑ  |

| V <sub>SS</sub>                  | Soft-start voltage level – Start of ramp                      |                                                                                                                                                                   | 0.4                   | 0.8                 | 1.3                   | V   |

| BP REGUL                         | ATOR                                                          |                                                                                                                                                                   | <u> </u>              |                     |                       |     |

| V <sub>BP</sub>                  | Output voltage                                                | I <sub>BP</sub> = 10 mA                                                                                                                                           | 6.2                   | 6.5                 | 6.8                   | V   |

| $V_{DO}$                         | Regulator dropout voltage, V <sub>VDD</sub> – V <sub>BP</sub> | I <sub>BP</sub> = 25 mA, V <sub>VDD</sub> = 4.5 V                                                                                                                 |                       | 70                  | 125                   | mV  |

| OSCILLATO                        | OR                                                            |                                                                                                                                                                   | <u>'</u>              |                     |                       |     |

|                                  |                                                               | $R_{COMP} = 40.2 \text{ k}\Omega,$<br>4.5 V ≤ V <sub>VDD</sub> ≤ 14 V                                                                                             | 270                   | 300                 | 330                   | kHz |

| $f_{SW}$                         | Switching Frequency                                           | $R_{COMP}$ = open,<br>4.5 V $\leq$ V <sub>VDD</sub> $\leq$ 14 V                                                                                                   | 450                   | 500                 | 550                   | kHz |

|                                  |                                                               | $R_{COMP}$ = 13.3 kΩ,<br>4.5 V ≤ V <sub>VDD</sub> ≤ 14 V                                                                                                          | 0.8                   | 0.95                | 1.1                   | MH  |

| V <sub>RAMP</sub> <sup>(1)</sup> | Ramp amplitude                                                |                                                                                                                                                                   | V <sub>VDD</sub> /6.6 | V <sub>VDD</sub> /6 | V <sub>VDD</sub> /5.4 | V   |

| PWM                              |                                                               |                                                                                                                                                                   |                       |                     |                       |     |

|                                  |                                                               | $\begin{split} f_{\text{sW}} &= 300 \text{ kHz}, \text{ V}_{\text{FB}} = 0 \text{ V}, \\ 4.5 \text{ V} &\leq \text{V}_{\text{VDD}} \leq 14 \text{ V} \end{split}$ | 93%                   |                     |                       |     |

| D <sub>MAX</sub> <sup>(1)</sup>  | Maximum duty cycle                                            | $f_{SW} = 500 \text{ kHz}, V_{FB} = 0 \text{ V},$<br>4.5 V \leq V_{VDD} \leq 14 V                                                                                 | 90%                   |                     |                       |     |

|                                  |                                                               | $f_{SW} = 1 \text{ MHz}, V_{FB} = 0 \text{ V},$<br>4.5 V \le V_{VDD} \le 14 V                                                                                     | 85%                   |                     |                       |     |

| t <sub>ON(min)</sub> (1)         | Minimum controllable pulse width                              |                                                                                                                                                                   |                       |                     | 100                   | ns  |

| ERROR AN                         | IPLIFIER                                                      |                                                                                                                                                                   |                       |                     |                       |     |

| GBWP (1)                         | Gain bandwidth product                                        |                                                                                                                                                                   | 10                    | 24                  |                       | MH  |

| A <sub>O</sub> L <sup>(1)</sup>  | Open loop gain                                                |                                                                                                                                                                   | 60                    |                     |                       | dB  |

| I <sub>IB</sub>                  | Input bias current (current out of FB pin)                    | V <sub>FB</sub> = 0.6 V                                                                                                                                           |                       |                     | 75                    | nA  |

| I <sub>EAOP</sub>                | Output source current                                         | V <sub>FB</sub> = 0 V                                                                                                                                             | 1.5                   |                     |                       | mA  |

| I <sub>EAOM</sub>                | Output sink current                                           | V <sub>FB</sub> = 1 V                                                                                                                                             | 1.5                   | -                   | -                     | m/  |

<sup>(1)</sup> 設計で確認されています。実製品のテストは行っていません。

# 電気的特性

|                                    | パラメータ                                                         | テスト条件                                                                                           | MIN      | TYP  | MAX | 単位    |

|------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------|------|-----|-------|

| POWER GO                           | OOD                                                           |                                                                                                 | <u> </u> |      |     |       |

| V <sub>OV</sub>                    | Feedback upper voltage limit for PGOOD                        |                                                                                                 | 655      | 675  | 700 | mV    |

| V <sub>UV</sub>                    | Feedback lower voltage limit for PGOOD                        |                                                                                                 | 500      | 525  | 550 |       |

| V <sub>PGD-HYST</sub>              | PGOOD hysteresis voltage at FB                                |                                                                                                 |          | 30   | 45  |       |

| R <sub>PGD</sub>                   | PGOOD pull down resistance                                    | V <sub>FB</sub> = 0 V, I <sub>FB</sub> = 5 mA                                                   |          | 30   | 70  | Ω     |

| I <sub>PGDLK</sub>                 | PGOOD leakage current                                         | $550~\text{mV} < \text{V}_{\text{FB}} < 655~\text{mV}, \\ \text{V}_{\text{PGOOD}} = 5~\text{V}$ |          | 10   | 20  | μΑ    |

| OUTPUT ST                          | rage .                                                        |                                                                                                 | ·        |      |     |       |

| R <sub>HI</sub>                    | High-side device resistance                                   | $T_J = 25^{\circ}C$ , $(V_{BOOT} - V_{SW}) = 5.5 \text{ V}$                                     |          | 4.5  | 6.5 | mΩ    |

| R <sub>LO</sub>                    | Low side device resistance                                    | $T_J = 25^{\circ}C$                                                                             |          | 1.9  | 2.7 |       |

|                                    | RENT PROTECTION (OCP)                                         |                                                                                                 | ·        |      |     |       |

| t <sub>PSSC(min)</sub> (2)         | Minimum pulse time during short circuit                       |                                                                                                 |          | 250  |     | ns    |

| t <sub>BLNKH</sub> (2)             | Switch leading-edge blanking pulse time (high-side detection) |                                                                                                 |          | 150  |     |       |

| I <sub>OCH</sub>                   | OC threshold for high-side FET                                | $T_J = 25^{\circ}C$ , $(V_{BOOT} - V_{SW}) = 5.5 \text{ V}$                                     | 45       | 54   | 65  | Α     |

| I <sub>ILIM</sub>                  | ILIM current source                                           | $T_J = 25^{\circ}C$                                                                             |          | 10.0 |     | μΑ    |

| V <sub>OCLPRO</sub> <sup>(2)</sup> | Programmable OC range for low side FET                        | T <sub>J</sub> = 25°C                                                                           | 12       |      | 100 | mV    |

| t <sub>OFF</sub>                   | OC retry cycles on EN/SS pin                                  |                                                                                                 |          | 4    |     | Cycle |

| BOOT DIOD                          | DE                                                            |                                                                                                 | <u>'</u> |      |     |       |

| $V_{DFWD}$                         | Bootstrap diode forward voltage                               | I <sub>BOOT</sub> = 5 mA                                                                        |          | 0.8  |     | V     |

|                                    | SHUTDOWN                                                      | •                                                                                               |          |      |     |       |

| T <sub>JSD</sub> (2)               | Junction shutdown temperature                                 |                                                                                                 |          | 145  |     | °C    |

| T <sub>JSDH</sub> (2)              | Hysteresis                                                    |                                                                                                 |          | 20   |     | °C    |

<sup>(2)</sup> 設計で確認されています。実製品のテストは行っていません

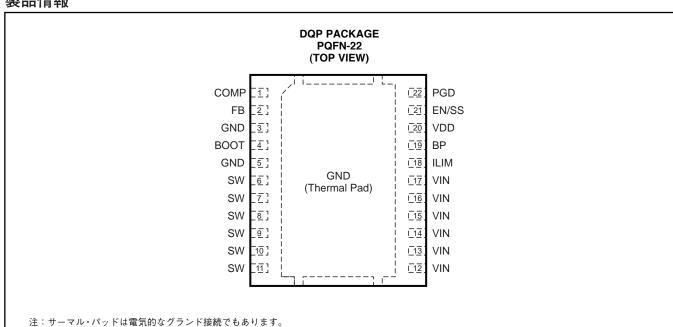

#### ピン機能

| ヒノ俄   |              |     |                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | ピン           | I/O | 説明                                                                                                                                                                                                                                                                                                                                                                                       |

| 名前    | 番号           |     |                                                                                                                                                                                                                                                                                                                                                                                          |

| воот  | 4            | 0   | ハイサイドFETのゲート駆動電圧。このピンとSWピンの間に、100nF(標準)のコンデンサを接続する必要があります。SWでの電圧スパイクを減らすには、BOOTコンデンサと直列に $5\Omega\sim10\Omega$ のBOOT抵抗を配置して、ハイサイドFETのスタートアップを遅くすることができます。                                                                                                                                                                                                                                |

| BP    | 19           | 0   | 内部レギュレータの出力バイパス。このピンとGNDの間に1 $\mu$ F以上の低ESRバイパス・セラミック・コンデンサを接続します。                                                                                                                                                                                                                                                                                                                       |

| COMP  | 1            | 0   | 誤差増幅器の出力、ループ帰還部品の接続ノード。オプションで、このピンとGNDの間に40.2k $\Omega$ の抵抗を配置することにより、スイッチング周波数をデフォルト値の500kHzではなく300kHzに設定できます。このピンとGNDの間に13.3k $\Omega$ の抵抗を配置すると、スイッチング周波数を1MHzに設定できます。                                                                                                                                                                                                                |

| EN/SS | 21           | I   | 外部ユーザ・コマンドによってコントローラを開始または停止するための論理レベル入力。このピンをフローティングにすると、コントローラがオンになります。このピンをLowにすると、コントローラがディスエーブルになります。これは、ソフト・スタート・プログラミング・ピンでもあります。このピンとGNDの間に接続するコンデンサによって、ソフト・スタート時間がプログラミングされます。コンデンサは、10μAの内部電流ソースによって充電されます。結果としてこのピンに生じる電圧ランプは、0.8V(typ)低くレベル・シフトした後、誤差増幅器への第2の非反転入力としても使用されます。出力レギュレーションは、内部のレベル・シフトされた電圧ランプにより、この電圧が内部リファレンス電圧600mVに達するまで制御されます。このピンの電圧ランプは1.4V(typ)まで達します。 |

| FB    | 2            | - 1 | 誤差増幅器への反転入力。通常動作時、このピンの電圧は内部リファレンス電圧に等しくなります。                                                                                                                                                                                                                                                                                                                                            |

| GND   | 3<br>5       | _   | デバイスのグランド・リファレンス                                                                                                                                                                                                                                                                                                                                                                         |

| GND   | サーマル・<br>パッド | _   | デバイスのグランド・リファレンス。これは、デバイスからの放熱に使用されるサーマル・パッドでもあります。この接続には、2つの目的があります。1つは、デバイスの電気的グランド接続を提供することです。もう1つは、デバイスのダイからPCBへの熱インピーダンスの低いパスを提供することです。このパッドは、外部でグランド・プレーンに接続する必要があります。                                                                                                                                                                                                             |

| ILIM  | 18           | I   | このピンとGNDの間に抵抗を接続することで、デバイス(ローサイドFET)の過電流スレッショルドが設定されます。                                                                                                                                                                                                                                                                                                                                  |

| PGD   | 22           | 0   | オープン・ドレインのパワー・グッド出力。                                                                                                                                                                                                                                                                                                                                                                     |

|       | 6            |     |                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 7            |     |                                                                                                                                                                                                                                                                                                                                                                                          |

| CW    | 8            | 1 . | │<br>│適応型クロス導通防止回路のセンス・ライン。フライング・ハイサイドFETドライバのコモン接続として機                                                                                                                                                                                                                                                                                                                                  |

| SW    | 9            | - 1 | 能します。                                                                                                                                                                                                                                                                                                                                                                                    |

|       | 10           | 1   |                                                                                                                                                                                                                                                                                                                                                                                          |

|       | 11           | 1   |                                                                                                                                                                                                                                                                                                                                                                                          |

| VDD   | 20           | I   | コントローラへの電源入力。このピンからGNDの近くに1μFの低ESRバイパス・セラミック・コンデンサを接続する必要があります。                                                                                                                                                                                                                                                                                                                          |

# ピン機能

|        | ピン | I/O | 説明                   |

|--------|----|-----|----------------------|

| 名前     | 番号 |     |                      |

|        | 12 |     |                      |

|        | 13 |     |                      |

| I VINI | 14 |     | <br> ハイサイドFETへの電源入力。 |

| VIN    | 15 | ı   | ハイリイドFEIへの电源入力。<br>  |

|        | 16 |     |                      |

|        | 17 |     |                      |

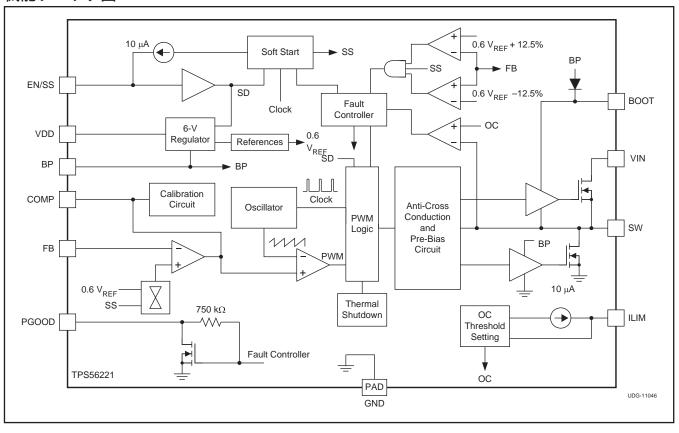

# 機能ブロック図

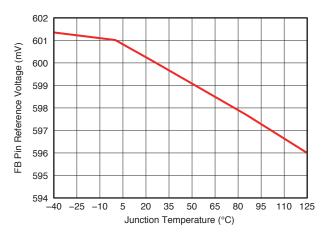

## 標準的特性

図1. リファレンス電圧 対 接合部温度

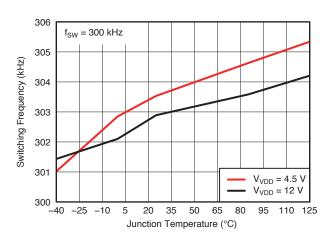

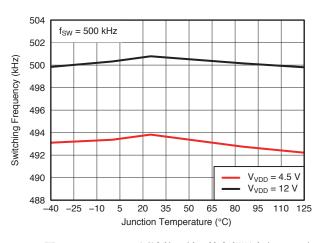

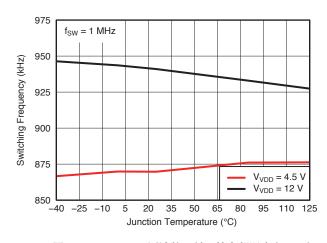

図 2. スイッチング周波数 対 接合部温度 (300kHz)

図 3. スイッチング周波数 対 接合部温度 (500kHz)

図 4. スイッチング周波数 対 接合部温度 (1MHz)

**図 5**. ENピンHighレベル・スレッショルド電圧 対 接合部温度

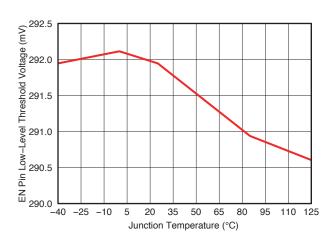

**図 6**. ENピンLowレベル・スレッショルド電圧 対 接合部温度

# 標準的特性

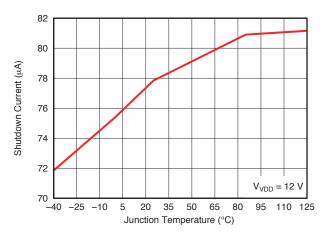

図7.シャットダウン電流 対 接合部温度

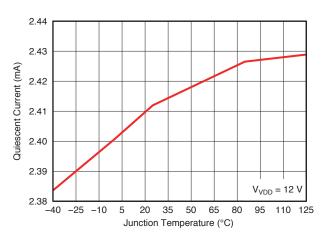

図 8. 静止電流 対 接合部温度

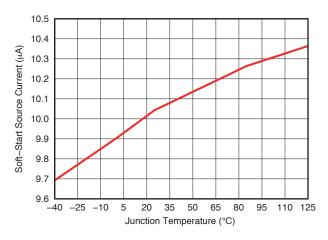

図9.ソフト・スタート・ソース電流 対 接合部温度

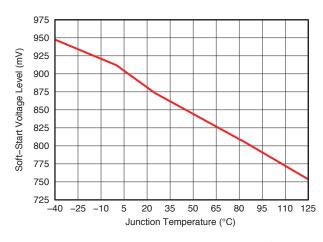

図 10. ソフト・スタート電圧レベル 対 接合部温度

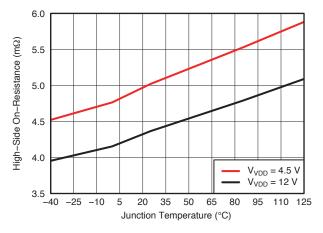

図11. ハイサイド・オン抵抗 対 接合部温度

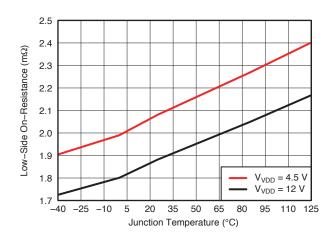

図 12. ローサイド・オン抵抗 対 接合部温度

# 標準的特性

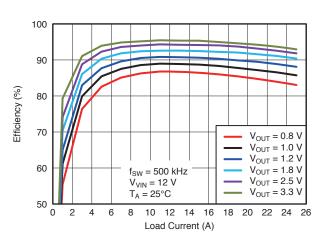

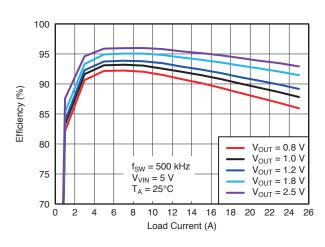

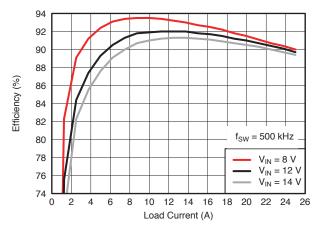

図15の効率曲線は、 $0.5\mu$ Hの出力インダクタおよび $0.75m\Omega$ の最大DCRで測定されています。図16の効率曲線は、 $0.3\mu$ Hの出力インダクタおよび $0.54m\Omega$ の最大DCRで測定されています。

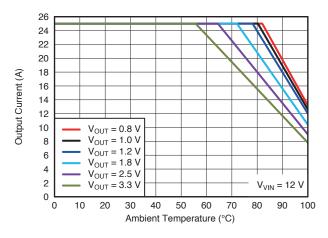

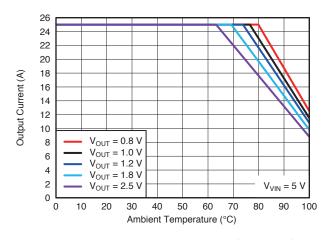

図17および図18の電力ディレーティング曲線は、4"×3.25"、0.062"厚のFR4基板(6層、1オンス銅)上で測定されています。

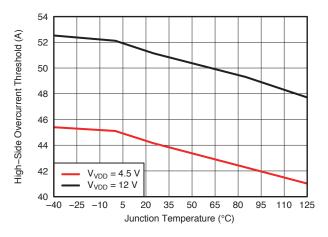

図 **13**. ハイサイド過電流スレッショルド 対 接合部温度

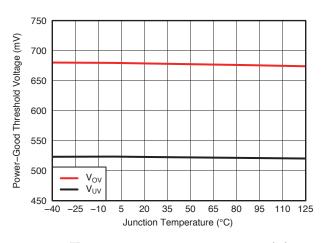

**図 14**. パワー・グッド・スレッショルド電圧 対 接合部温度

図 15. 効率 対 負荷電流(V<sub>VIN</sub> = 12V)

図 16. 効率 対 負荷電流(V<sub>VIN</sub> = 5V)

図 17. 出力電流 対 周囲温度 (V<sub>VIN</sub> = 12V)

図 18. 出力電流 対 周囲温度  $(V_{VIN} = 5V)$

## アプリケーション情報

#### 概要

TPS56221は、2個のNチャネルNexFET™パワーMOSFETを内蔵した、25Aの高性能同期バック・コンバータです。電圧モード制御を実装し、電圧フィードフォワード補償により入力電圧の変化に対して瞬時に応答します。プリバイアス機能により、壊れやすい負荷に対して損傷を与える懸念がなくなります。

#### 電圧リファレンス

600mVのバンド・ギャップ・セルが、内部で誤差増幅器の非反転入力に接続されています。リファレンス電圧は、ユニティ・ゲイン構成の誤差増幅器と共にトリミングされ、最終レギュレーション電圧から増幅器オフセットが除去されます。リファレンス電圧の公差は1%であり、ユーザは非常に精確な電源を設計することが可能です。

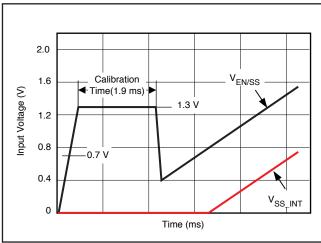

図 **19**. スタートアップ・シーケンスおよびタイミング

## イネーブル機能、スタートアップ・シーケンスお よびタイミング

入力電源が印加されると、40μAの内部電流ソースによって、EN/SSとGNDの間に接続されたソフト・スタート・コンデンサの充電が開始されます。コンデンサ両端の電圧が0.7Vまで上昇すると、内部BPレギュレータがイネーブルになり、校正が開始されます。合計校正時間は約1.9msです。図19を参照してください。校正中、デバイスは次の2つの機能を実行します。

## COMPピンのインピーダンス・センス

デバイスはCOMPピンでのインピーダンスをサンプリングし、動作スイッチング周波数を決定します。COMPピンとGNDの間に抵抗を接続しない場合、スイッチング周波数はデフォルト値の500kHzに設定されます。COMPピンとGNDの間に $40.2k\Omega \pm 10\%$ の抵抗を接続すると、スイッチング周波数は300kHzに設定されます。また、COMPピンとGNDの間に $13.3k\Omega \pm 10\%$ の抵抗を接続すると、スイッチング周波数は1MHzに設定されます。

1.1msの期間が経過した後、COMPピンは0.8msの間Lowになります。これにより、スタートアップ時に帰還ループが適切に設定され、コンバータがスイッチングを開始するときに、コンバータの出力での急激な出力上昇が防止されます。

# 過電流保護 (OCP) 設定

デバイスは、ILIMピンとGNDの間に接続された抵抗に10μA (typ)をソースします。この抵抗に生じる電圧に係数2を乗じた値がサンプリングされ、入力のサイクルまたはEN/SSの切り替え時まで、ローサイドFETのOCPトリップ・レベルとして内部でラッチされます。

EN/SSの電圧は、校正前および校正中は内部で1.3Vにクランプされ、校正完了後の放電時間を最小限にしています。放電電流は $140\mu$ Aの内部電流ソースから得られ、電圧を0.4Vまで降下させます。その後、 $10\mu$ Aの内部電流ソースを使用してコンデンサを充電することにより、ソフト・スタートを開始します。結果としてこのピンに生じる電圧ランプは、800mV(typ)低くレベル・シフトした後、誤差増幅器への第20非反転入力として使用されます。したがって、実際のソフト・スタートは、このピンの電圧が800mVに達するまで開始されません。

EN/SSピンをフローティングにすると、コントローラは自動的に起動します。デバイスがシャットダウン・モードに入るようにするには、EN/SSを270mV未満にプルダウンする必要があります。

### ソフト・スタート時間

TPS56221のソフト・スタート時間は、1個のコンデンサを選択することでユーザ・プログラミングできます。このコンデンサは、EN/SSピンから供給される10μAの電流によって充電されます。実際の出力上昇時間は、600mVの範囲でこの10μAによってコンデンサが充電されるまでにかかる時間です。校正と、実際のEN/SSピン電圧から誤差増幅器に印加される電圧との間のオフセット(800mV)により、ある程度の初期遅延があります。

ソフト・スタートは閉ループ内で行われます。つまり、誤差増幅器がソフト・スタート期間中全体にわたって出力電圧を制御し、デューティ・サイクル制限方式のソフト・スタートのように帰還ループが開になることはありません。誤差増幅器には2つの非反転入力があり、一方は600mVのリファレンス電圧、もう一方はオフセットされたEN/SSピン電圧に接続されています。誤差増幅器は、この2つのうち低い方の電圧にFBピンを制御します。EN/SSピンの電圧が約1.4V(800mVのオフセット電圧+600mVのリファレンス電圧)を過ぎて上昇すると、600mVのリファレンス電圧が支配的な入力となり、コンバータは最終レギュレーション電圧に到達しています。

出力電圧に対して特定のソフト·スタート上昇時間を設定するために必要な容量は、式(1)で与えられます。

$$C_{SS} = \left(\frac{I_{SS}}{V_{FB}}\right) \times t_{SS} \tag{1}$$

ここで

- C<sub>SS</sub>は、EN/SSピンの必要な容量 (nF) です。

- I<sub>SS</sub>は、ソフト・スタート・ソース電流 (10μA)です。

- V<sub>FR</sub>は、帰還リファレンス電圧 (0.6V) です。

- tssは、目的のソフト・スタート上昇時間 (ms) です。

#### 発振回路

COMPピンとGNDの間に抵抗を接続しない場合、発振周波数は内部で $500 \mathrm{kHz}$ に固定されます。オプションとして、COMPピンとGNDの間に $40.2 \mathrm{k}\Omega$ の抵抗を接続すると、周波数が $300 \mathrm{kHz}$ に設定されます。また、COMPピンとGNDの間に $13.3 \mathrm{k}\Omega$ の抵抗を接続すると、周波数が $1 \mathrm{MHz}$ に設定されます。

#### 過電流保護 (OCP)

ILIMでのプログラミング可能なOCPレベルは、 $6mV\sim50mV$ です。スケール・ファクタが2に設定され、ローサイドFETでの実際のOCトリップ点は、 $12mV\sim100mV$ の範囲内です。

校正中に $R_{OCSET}$ での電圧降下が300mVに達した場合 ( $R_{OCSET}$ 抵抗が搭載されない場合も含む)、OC保護がディスエーブルになります。ディスエーブルになると、ローサイドおよびハイサイドの電流センスが行われません。

ハイサイドFETのOCPレベルは、54A(typ)に固定されています。ハイサイドOCPでは、パルス毎の電流制限が行われます。

ローサイドFETのOCPセンスは、サンプル/ホールドを使用した真のインダクタ・バレー電流検出です。 $R_{OCSET}$ は式 (2) で計算できます。

$$R_{OCSET} = \left(I_{OUT(max)} - \left(\frac{I_{P-P}}{2}\right)\right) \times 95 + 500$$

(2)

ここで

- I<sub>P-P</sub>は、ピーク・ツー・ピーク・インダクタ電流 (A) です。

- $I_{OUT(max)}$ は、OCPのトリップ点 (A) です。

- $R_{OC(set)}$ は、OCPレベルの設定に使用される抵抗 ( $\Omega$ ) です。

過電流 (OC) 状態は、ローサイドFETおよびハイサイドFETでの電圧降下をセンスすることで検出されます。いずれかのFETでの電圧降下がOCスレッショルドを超えた場合、カウンタのカウントが1増加します。いずれのFETでもOC状態が検出されない場合、カウントは1減少します。3つのOCパルスが加算されると、障害状態が宣言され、ソフト・スタート機能がヒカップ・モードで繰り返されます。ヒカップ・モードでは、通常動作中に過電流状態が検出された場合には4回のダミーのソフト・スタート・タイムアウトに続いて真のソフト・スタートが1回発生し、起動中に最初から過電流状態が検出された場合には、5回のダミーのソフト・スタート・タイムアウトに続いて真のソフト・スタートが1回発生します。このサイクルが、障害状態が解消されるまで無制限に繰り返されます。

#### 入力低電圧誤動作防止(UVLO)

TPS56221は、固定の入力低電圧誤動作防止 (UVLO) 機能を備えています。デバイスがオンになるには、次の条件が満足されている必要があります。

- EN/SSピンの電圧がVIHより高い

- 入力電圧がUVLOオン電圧 (V<sub>UVLO</sub>)を超えている

UVLOには、最小500mVのヒステリシスが組み込まれています。

#### プリバイアス・スタートアップ

TPS56221には、出力がプリバイアスされている状態でのスタートアップ中に、出力から電流を引き込むのを防ぐための、独自の回路が含まれています。出力がプリバイアスされている場合、内部ソフト・スタート電圧が誤差増幅器の入力(FBピン)を上回るまで、PWMパルスは生成されません。ソフト・スタート電圧が誤差増幅器の入力を上回ると、コントローラは、短いオン時間で同期整流器を起動することにより、同期整流をゆっくりと開始します。次に、そのオン時間が(1-D)で示される時間と一致するまで(Dはコンバータのデューティ・サイクル)、オン時間をサイクル毎にインクリメントします。

このアプローチにより、プリバイアス出力から電流がシンクされるのを防ぎ、出力電圧のスタートアップとレギュレーションまでの上昇が円滑に制御されるようにしています。

## パワー・グッド

TPS56221には、コンバータにとって出力が良好であることを示す機能があります。これは、オープン・ドレイン出力信号であり、電源の出力がレギュレーション範囲外である可能性を示す状況が存在する場合、Lowになります。これには、次のような状況が含まれます。

- V<sub>FB</sub>が公称値から±12.5%以上外れている

- ソフト・スタートがアクティブである

- 短絡状況が検出された

注: デバイスに電源が供給されていない場合、パワー・グッド 通知に補助電源が使われていると、PGOODはGNDレベル 近くにプルダウンできません。この場合、PGOODプルダウン・デバイスのドレイン - ゲート間に接続されている内 蔵抵抗により、PGOODピンはGNDに対するダイオードのように機能します。

#### 過熱シャットダウン

デバイスの接合部温度が $145^{\circ}$ Cの過熱シャットダウン制限に達すると、PWMおよび発振回路がオフになります。ハイサイドFETとローサイドFETの両方がオフに保持されます。接合部が所定のレベル(標準 $125^{\circ}$ C)まで冷却されると、PWMは、通常のパワーアップ・サイクル時と同様にソフト・スタートを開始します。

# 設計例

## 概要

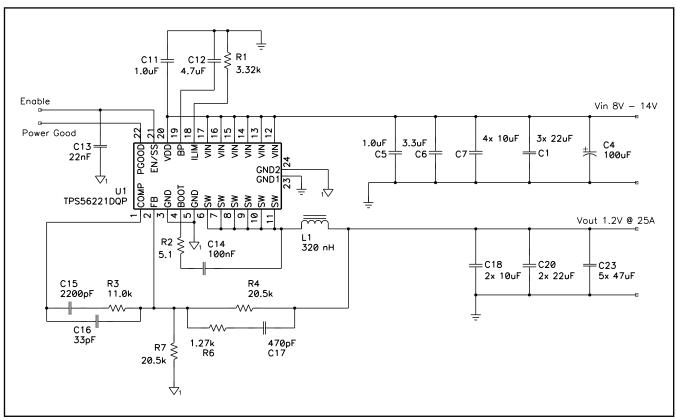

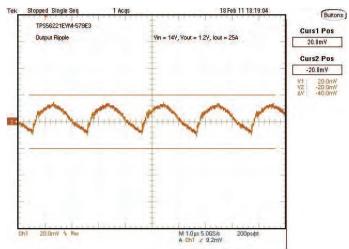

この設計例は、TPS56221大電流バック・コンバータを使用した、12V入力から1.2V/25A出力の設計を示しています。システム仕様を表1に示します。

|                         | パラメータ        | 測定条件                                              | MIN   | TYP | MAX   | 単位              |

|-------------------------|--------------|---------------------------------------------------|-------|-----|-------|-----------------|

| V <sub>IN</sub>         | 入力電圧         |                                                   | 8.0   |     | 14    | ٧               |

| V <sub>IN(ripple)</sub> | 入力リップル       | I <sub>OUT</sub> = 25 A                           |       |     | 0.5   | ٧               |

| V <sub>OUT</sub>        | 出力電圧         | 0 A ≤ I <sub>OUT</sub> ≤ 25 A                     | 1.164 | 1.2 | 1.236 | V               |

|                         | ライン・レギュレーション | 8 V ≤ V <sub>IN</sub> ≤ 14 V                      |       |     | 0.5%  |                 |

|                         | ロード・レギュレーション | 0 A ≤ I <sub>OUT</sub> ≤ 25 A                     |       |     | 0.5%  |                 |

| V <sub>RIPPLE</sub>     | 出力リップル       | I <sub>OUT</sub> = 25 A                           |       |     | 24    | mV              |

| V <sub>OVER</sub>       | 出力オーバーシュート   | 10 A ≤ I <sub>OUT</sub> ≤ 20 A                    |       | 50  |       | mV              |

| V <sub>UNDER</sub>      | 出力アンダーシュート   | 10 A ≤ I <sub>OUT</sub> ≤ 20 A                    |       | 50  |       | mV              |

| I <sub>OUT</sub>        | 出力電流         | 8 V ≤ V <sub>IN</sub> ≤ 14 V                      | 0     |     | 25    | Α               |

| t <sub>SS</sub>         | ソフト・スタート時間   | V <sub>IN</sub> = 12 V                            |       | 1.5 |       | ms              |

| I <sub>SCP</sub>        | 短絡電流トリップ点    |                                                   | 30    |     |       | Α               |

| η                       | 効率           | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 12.5 A |       | 90  |       | %               |

| f <sub>SW</sub>         | スイッチング周波数    |                                                   |       | 500 |       | kHz             |

|                         | サイズ          |                                                   |       |     | 0.6   | In <sup>2</sup> |

**表 1**. 設計例のパラメータ

図 20. 設計例の回路図

#### 設計手順

## スイッチング周波数の選択

この設計では、小サイズと高効率のバランスを取るために、500kHzのスイッチング周波数を使用します。

#### インダクタの選択 (L1)

同期バック・パワー・インダクタは、一般に、約20%~40%のピーク・ツー・ピーク・リップル電流 (I<sub>RIPPLE</sub>) に対してサイズが選択されます。

この目標リップル電流により、必要なインダクタ・サイズは式(3)で計算できます。

$$L \approx \frac{V_{IN(max)} - V_{OUT}}{0.3 \times I_{OUT}} \times \frac{V_{OUT}}{V_{IN(max)}} \times \frac{1}{f_{SW}}$$

$$= \frac{14 \text{ V} - 1.2 \text{ V}}{0.3 \times 25 \text{ A}} \times \frac{1.2 \text{ V}}{14 \text{ V}} \times \frac{1}{500 \text{ kHz}} = 293 \text{ nH}$$

(3)

標準のインダクタ値として300nHを選択し、 $I_{RIPPLE}$  = 7.3Aとします。

インダクタを流れるRMS電流は、式(4)で近似されます。

$$I_{L(rms)} = \sqrt{\left(I_{L(avg)}\right)^{2} + \left(\frac{1}{12} \times \left(I_{RIPPLE}\right)^{2}\right)}$$

$$= \sqrt{\left(I_{OUT}\right)^{2} + \left(\frac{1}{12} \times \left(I_{RIPPLE}\right)^{2}\right)}$$

$$= \sqrt{\left(25\right)^{2} + \left(\frac{1}{12} \times \left(7.3\right)^{2}\right)} = 25.09 \text{ A}$$

(4)

#### 出力コンデンサの選択(C18、C20、C23)

出力コンデンサは、一般に出力過渡応答に基づいて選択されます。式(5)および式(6)は、ループ帯域幅における遅延を考慮して電圧偏差を過大評価しています。これらの式を使用して、必要な出力容量を決定できます。

$V_{\rm IN(min)}$  > 2 ×  $V_{\rm OUT}$ の場合は、オーバーシュート(式 (5)) を使用して最小出力容量を計算します。 $V_{\rm IN(min)}$  < 2× $V_{\rm OUT}$ の場合は、アンダーシュート(式 (6)) を使用して最小出力容量を計算します。

$$V_{OVER} < \frac{I_{TRAN}}{C_{OUT}} \times \Delta T = \frac{I_{TRAN}}{C_{OUT}} \times \frac{I_{TRAN} \times L}{V_{OUT}}$$

$$= \frac{\left(I_{TRAN}\right)^{2} \times L}{V_{OUT} \times C_{OUT}}$$

(5)

$$V_{UNDER} < \frac{I_{TRAN}}{C_{OUT}} \times \Delta T = \frac{I_{TRAN}}{C_{OUT}} \times \frac{I_{TRAN} \times L}{V_{IN} - V_{OUT}}$$

$$= \frac{\left(I_{TRAN}\right)^2 \times L}{\left(V_{IN} - V_{OUT}\right) \times C_{OUT}} \tag{6}$$

$$C_{OUT(min)} = \frac{\left(I_{TRAN(max)}\right)^2 \times L}{\left(V_{OUT}\right) \times V_{OVER}} = \frac{\left(10\right)^2 \times 300 \text{nH}}{1.2 \times 50 \text{mV}}$$

$$= 500 \,\mu\text{F} \tag{7}$$

最小容量が決まると、最大許容ESRは最大リップル電圧によって決定され、式(8)で近似されます。

$$\begin{split} ESR_{MAX} &= \frac{V_{RIPPLE(tot)} - V_{RIPPLE(cap)}}{I_{RIPPLE}} \\ &= \frac{V_{RIPPLE(tot)} - \left(\frac{I_{RIPPLE}}{8 \times C_{OUT} \times f_{SW}}\right)}{I_{RIPPLE}} \\ &= \frac{24 \text{mV} - \left(\frac{7.8 \text{A}}{8 \times 500 \, \mu \text{F} \times 500 \, \text{kHz}}\right)}{7.8 \, \text{A}} = 2.5 \, \text{m}\Omega \end{split}$$

この設計の低ESRおよび高容量要件を満たすため、5個の  $100\mu$ F、1210セラミック・コンデンサを選択します。ESLおよび誘導性リンギングの低減のため、3個の $22\mu$ F、1206セラミック・コンデンサおよび2個の $10\mu$ F、0805セラミック・コンデンサを追加します。複数の種類のコンデンサおよび異なるサイズのセラミック・コンデンサを組み合わせることで、出力コンデンサのフィルタリング周波数に対して、より広い帯域が提供されます。

## インダクタのピーク電流定格

出力容量を使用して、スタートアップ時の充電電流を計算し、インダクタの最小飽和電流定格を決定することが可能です。スタートアップ時の充電電流は、式(9)で近似されます。

$$I_{CHARGE} = \frac{V_{OUT} \times C_{OUT}}{t_{SS}} = \frac{1.2 \text{ V} \times 586 \,\mu\text{F}}{1.5 \,\text{ms}} = 0.469 \text{A}$$

(9)

$$I_{L(peak)} = I_{OUT(max)} + (\frac{1}{2} \times I_{RIPPLE}) + I_{CHARGE}$$

= 25 A + (\frac{1}{2} \times 7.8A) + 0.469A = 29.4A (10)

|                      | パラメータ       | VALUE | 単位 |

|----------------------|-------------|-------|----|

| L                    | インダクタンス     | 300   | nH |

| I <sub>L(rms)</sub>  | RMS電流(熱定格)  | 25.08 | Α  |

| I <sub>L(peak)</sub> | ピーク電流(飽和定格) | 29.4  | Α  |

表2 インダクタ要件一覧

## ブートストラップ・コンデンサ (C14)

ブートストラップ・コンデンサは、ハイサイド・スイッチのオン時間中に、ハイサイド・ドライバへの電力を維持します。内蔵MOSFETの要件に従い、 $C_{\rm BOOT}$ には、最小10Vの定格を持つ100nFのコンデンサを使用します。

## ブートストラップ・抵抗(R2)

ブートストラップ抵抗は、SW電圧の立ち上がりエッジを緩やかにすることで、リンギングの低減とEMIの向上に役立ちます。データシートの推奨事項に従い、5.1Ωの抵抗を選択します。

## VDDバイパス・コンデンサ(C11)

TPS56221の推奨ピン終端条件に従い、VDDは1.0μFのコンデンサでGNDにバイパスします。

#### BP5バイパス・キャパシタ(C12)

TPS56221の推奨ピン終端条件に従い、VDDは $1.0\mu$ F以上のコンデンサでGNDにバイパスします。追加のフィルタリングとノイズ耐性向上のために、 $4.7\mu$ Fのコンデンサを選択します。

## ソフト·スタート·コンデンサ (C13)

ソフト・スタート・コンデンサは、制御されたスムーズなスタートアップを実現するため、誤差増幅器に一定のランプ電圧を供給します。ソフト・スタート・コンデンサの大きさは、式 (11)を使って計算します。

$$C_{SS} = \frac{I_{SS}}{V_{EB}} \times t_{SS} = \frac{10 \,\mu\text{A}}{0.6 \,\text{V}} \times 1.5 \,\text{ms} = 25 \,\text{nF} \approx 22 \,\text{nF}$$

(11

#### 電流制限(R1)

TPS56221は、オフ時間の終わりに内部ローサイドFETで生じる負の降下を使用して、インダクタの谷電流を測定します。最大負荷から最小30%の超過を考慮し、プログラミング抵抗は式 (12)で選択されます。

$$R_{OCSET} = 95 \times \left( 1.3 \times I_{OUT(max)} - \left( \frac{I_{RIPPLE}}{2} \right) \right) + 500 \Omega$$

$$= 95 \times \left( 1.3 \times 25 \text{ A} - \left( \frac{7.8 \text{ A}}{2} \right) \right) + 500 \Omega$$

$$= 3.23 \text{ k}\Omega \approx 3.32 \text{ k}\Omega$$

(12)

#### 帰還分圧抵抗(R4、R7)

TPS56221コンバータでは、0.600Vの内部固定リファレンスを持つ完全なオペアンプが使用されます。帰還電流とノイズ耐性のバランスのために、 $R4は10k\Omega\sim50k\Omega$ の範囲で選択されます。 $R4を20.5k\Omega$ に設定した場合、出力電圧は式 (13) で与えられる分圧抵抗によってプログラミングされます。

$$R_{BIAS} = \frac{V_{FB} \times R_{FB}}{\left(V_{OUT} - V_{FB}\right)} = \frac{0.600 \text{ V} \times 20.5 \text{ k}\Omega}{1.2 \text{ V} - 0.600 \text{ V}} = 20.5 \text{ k}\Omega \approx 20.5 \text{ k}\Omega$$

(13)

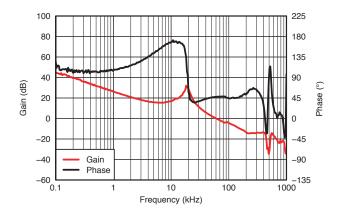

## 補償(C15、C16、C17、R3、R6)

TPS40kループ安定性ツールを、 $60 \mathrm{kHz}$ の帯域幅と $60^\circ$ の位相マージン、およびR4 =  $20.5 \mathrm{k}\Omega$ に対して使用すると、以下の値が得られます。

- $C17 = C_1 = 470pF$

- $C15 = C_2 = 2200 pF$

- $C16 = C_3 = 33pF$

- $R6 = R_2 = 1.27 k\Omega$

- $R3 = R_3 = 11.0 k\Omega$

# 設計例の特性

12V入力~1.2V出力、0A~25A出力電流

図 21. 効率 対 負荷電流

図 22. ループ応答

図 23. 出力リップル20mV/div、1.0μs/div、 帯域幅20MHz、AC結合

| 記号  | 数量 | 値               | 説明                         | サイズ                   | 部品番号         | メーカー      |

|-----|----|-----------------|----------------------------|-----------------------|--------------|-----------|

| C1  | 3  | 22 μF           | コンデンサ、セラミック、25V, X5R, 20%  | 1210                  | Std          | Std       |

| C4  | 1  | 100 μF          | コンデンサ、アルミ、16VDC, ±20%      | D8                    | EEEFP1C101AP | Panasonic |

| C5  | 1  | 1.0 μF          | コンデンサ、セラミック、25V, X7R, 20%  | 0805                  | Std          | Std       |

| C6  | 1  | 3.3 μF          | コンデンサ、セラミック、25V, X7R, 20%  | 0805                  | Std          | Std       |

| C7  | 4  | 10 μF           | コンデンサ、セラミック、25V, X7R, 20%  | 1206                  | Std          | Std       |

| C11 | 1  | 1.0 μF          | コンデンサ、セラミック、25V, X5R, 20%  | 0805                  | Std          | Std       |

| C12 | 1  | 4.7 μF          | コンデンサ、セラミック、10V, X5R, 20%  | 0805                  | Std          | Std       |

| C13 | 1  | 22 μF           | コンデンサ、セラミック、16V, X7R, 20%  | 0402                  | Std          | Std       |

| C14 | 1  | 100 μF          | コンデンサ、セラミック、16V, X7R, 20%  | 0402                  | Std          | Std       |

| C15 | 1  | 2200 pF         | コンデンサ、セラミック、25V, X7R, 10%  | 0402                  | Std          | Std       |

| C16 | 1  | 33 pF           | コンデンサ、セラミック、25V, COG, 10%  | 0402                  | Std          | Std       |

| C17 | 1  | 470 pF          | コンデンサ、セラミック、25V, COG, 10%  | 0402                  | Std          | Std       |

| C18 | 2  | 10 μF           | コンデンサ、セラミック、6.3V, X5R, 20% | 0805                  | Std          | Std       |

| C20 | 2  | 22 μF           | コンデンサ、セラミック、6.3V, X5R, 20% | 1206                  | Std          | Std       |

| C23 | 5  | 47 μF           | コンデンサ、セラミック、6.3V, X5R, 20% | 1210                  | Std          | Vishay    |

| L1  | 1  | 320 nH          | インダクタ、SMTパワー、±15%          | 0.394 x<br>0.476 inch | PA2202-321NL | Pulse     |

| R1  | 1  | 3.32 kΩ         | 抵抗、チップ、Chip, 1/16W, 1%     | 0402                  | Std          | Std       |

| R2  | 1  | 5.1 Ω           | 抵抗、チップ、Chip, 1/16W, 1%     | 0402                  | Std          | Std       |

| R3  | 1  | 11.0 kΩ         | 抵抗、チップ、Chip, 1/16W, 1%     | 0402                  | Std          | Std       |

| R4  | 1  | 20.5 kΩ         | 抵抗、チップ、Chip, 1/16W, 1%     | 0402                  | Std          | Std       |

| R6  | 1  | 1.27 kΩ         | 抵抗、チップ、Chip, 1/16W, 1%     | 0402                  | Std          | Std       |

| R7  | 1  | 20.5 kΩ         | 抵抗、チップ、Chip, 1/16W, 1%     | 0402                  | Std          | Std       |

| U1  | 1  | TPS56221D<br>QP | 25A、600kHz、同期バック・コンバータ     | QFN-22 6 × 5 mm       | TPS56221DQP  | TI        |

表 3. TPS56221設計例の部品表

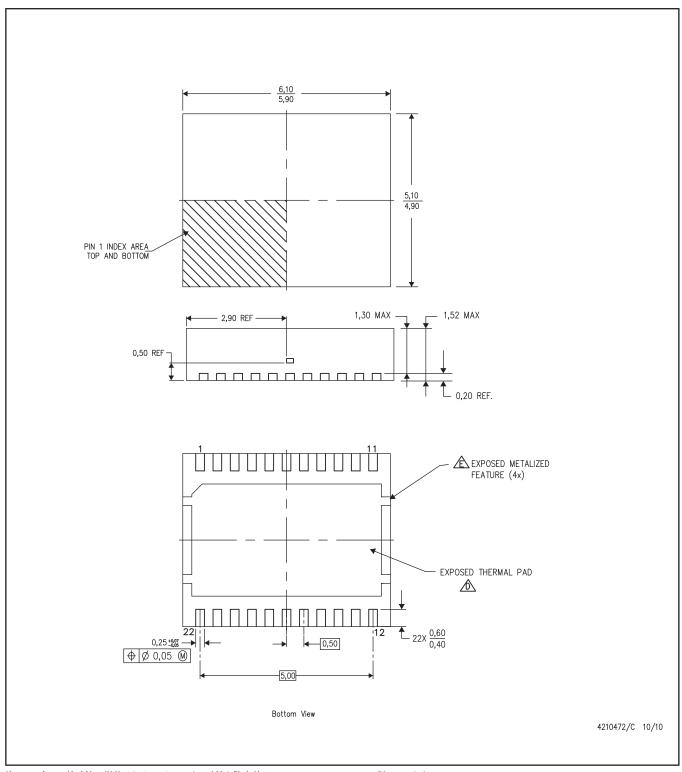

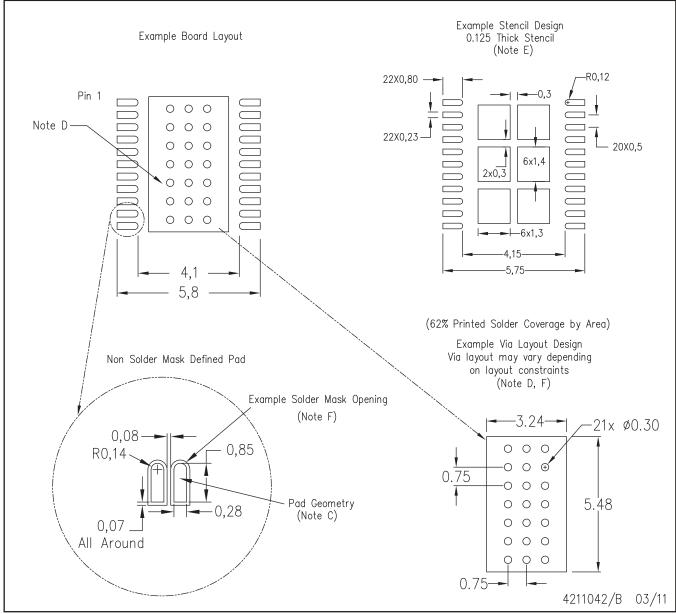

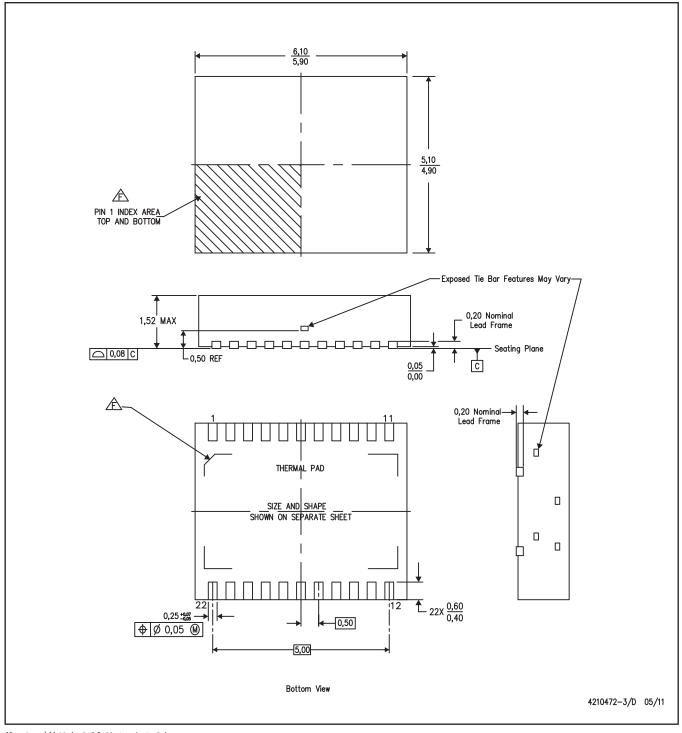

## DQP(R-PSON-N22)

- 注:A. 全ての線寸法の単位はミリメートルです。寸法と許容差はASME Y14.5M- 1994に従っています。

- B. 図は予告なく変更することがあります。

- C. SON(Small Outline No-Lead) パッケージ構成 最良の熱特性および機械的特性を得るには、パッケージのサーマル・パッドを基板に半田付けする必要があります。

- **企** 金属化はベンダのオプションで、パッケージには含まれていない場合があります。

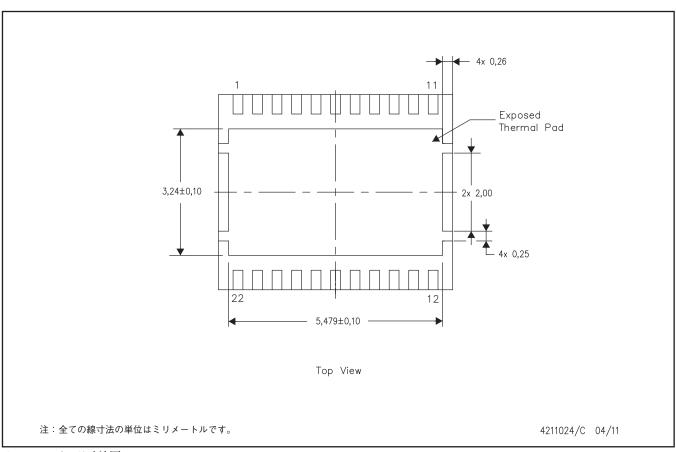

# サーマルパッド・メカニカル・データ

## DQP(R-PSON-N22)

#### 熱的特性に関する資料

このパッケージには、外部ヒートシンクに直接接続するように設計された、露出したサーマル・パッドが装備されています。このサーマル・パッドは、プリント基板 (PCB)をヒートシンクとして使用できるように、PCBに直接半田付けする必要があります。また、サーマル・ビアを使用して、サーマル・パッドをグランド・プレーンまたはPCB内に設計された特別なヒートシンク構造に直接接続することができます。この設計により、ICからの熱伝導が最適化されます。

QFN(Quad Flatpack No-Lead) パッケージとその利点については、アプリケーション・レポート『Quad Flatpack No-Lead SON PCB』(Texas Instruments文献番号SLUA271)を参照してください。このドキュメントは、ホームページwww.ti.comで入手できます。

このパッケージの露出したサーマル・パッドの寸法を次の図に示します。に設計された、露出したサーマル・パッドが装備されています。

サーマル・パッド寸法図

- 注:A. 直線寸法はすべてミリメートル単位です。

- B. 本図は予告なしに変更することがあります。

- C. 代替設計には、IPC-7351規格を推奨します。

- D. 本パッケージは、サーマルパッドを基板に半田付けするように設計されています。具体的な熱的特性情報、ヴィア条件、および推奨基板レイアウトについては、アプリケーション・ノート「QFNパッケージ」テキサス・インスツルメンツ文献番号SLUA271および製品データシートも参照願います。これらの文献はwww.ti.com < http://www.ti.com > で入手できます。

- E. 台形壁面やラウンドコーナーにレーザー・カッティング・アパーチャを行うと、ペーストのリリースが容易になります。推奨のステンシル設計については、基板組立元に問合せ願います。ステンシル設計の検討については、IPC7525規格を参照願います。

- F. 半田マスク公差については、基板製造元に問合せ願います。

## パッケージ情報

#### 製品情報

| Orderable<br>Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>  | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|---------------------|-----------------------|-----------------|--------------------|------|----------------|--------------------------|----------------------|------------------------------|-----------------------------|

| TPS56221DQPR        | ACTIVE                | SON             | DQP                | 22   | 2500           | Pb-Free (RoHS<br>Exempt) | CU SN                | Level-2-260C-1 YEAR          |                             |

| TPS56221DQPT        | ACTIVE                | SON             | DQP                | 22   | 250            | Pb-Free (RoHS<br>Exempt) | CU SN                | Level-2-260C-1 YEAR          |                             |

(1)マーケティング・ステータスは次のように定義されています。

ACTIVE: 製品デバイスが新規設計用に推奨されています。

LIFEBUY: TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND: 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW: デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free(RoHS)、Pb-Free(RoHS Expert)およびGreen(RoHS & no Sb/Br)があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free" (鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green (RoHS & no Sb/Br)**: TIにおける "Green" は、"Pb-Free" (RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

<sup>(3)</sup>MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金 額を超える責任は負いかねます。

# パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

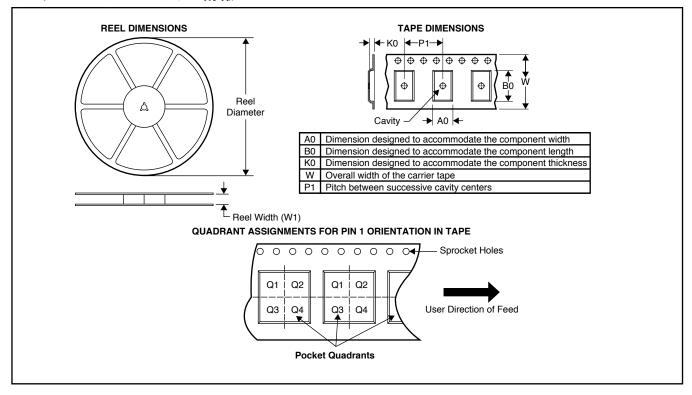

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS56221DQPR | SON             | DQP                | 22   | 2500 | 330.0                    | 12.4                     | 5.3        | 6.3        | 1.8        | 8.0        | 12.0      | Q1               |

| TPS56221DQPT | SON             | DQP                | 22   | 250  | 180.0                    | 12.4                     | 5.3        | 6.3        | 1.8        | 8.0        | 12.0      | Q1               |

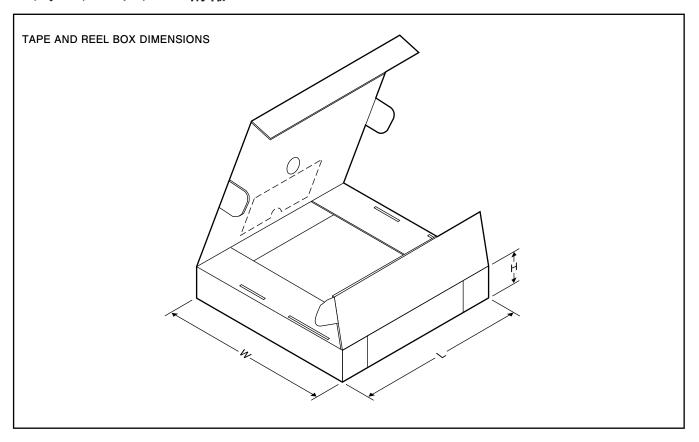

# パッケージ・マテリアル情報

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS56221DQPR | SON          | DQP             | 22   | 2500 | 346.0       | 346.0      | 29.0        |

| TPS56221DQPT | SON          | DQP             | 22   | 250  | 210.0       | 185.0      | 35.0        |

## DQP(R-PSON-N22)

- 注:A. 寸法はすべてミリメートルです。

- B. 本図は予告なく変更することがあります。 C. SON(Small Outline No-Lead)パッケージ構成

- D. 最良の熱特性および機械的特性を得るには、パッケージのサーマル・パッドを基板に半田付けする必要があります。

- E. 露出したサーマル・パッドの寸法に関する詳細は、製品データシートを参照してください。 ピン1識別は、パッケージの上下両面の示された領域内にあります。 ピン1識別は、モールド、マークまたは金属を使用して施されます。

**INSTRUMENTS**

(SLUSAH5)

#### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありませ ん。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated