TPS61030 TPS61031 TPS61032

www.tij.co.jp JAJS377

# 96%効率 スイッチ電流4A、同期整流方式昇圧コンバータ

# 特長

- 入力電圧1.8 V から1 A 出力が可能な効率96%の同期整流方式昇圧コンバータ

- デバイス静止時自己消費電流: 20µA (Typ)

- 入力電圧範囲: 1.8V~5.5V

- 最高5.5Vまの可変出力電圧製品、および固定出力 電圧製品

- パワー・セーブ・モードにより低出力電流時の効率 を改善

- ロー・バッテリー・コンパレータ内蔵

- 低EMIコンバータ(アンチリンギング・スイッチ内蔵)

- シャットダウン時負荷と電源を遮断

- 過熱保護

- 4mm × 4mmの小型QFN16ピンパッケージと TSSOP16ピンパッケージ

# アプリケーション

● 単セルのリチウム系電池また2セルの乾電池を電源 とするポータブル・オーディオ・プレーヤ やPDAな どの携帯機器

# 概要

TPS6103xは、1セルのリチウム・イオン、リチウム・ポリマー 電池あるいは2セルから3セルのアルカリ、ニッカド、ニッケル 水素電池を電源とする製品の電源ソリューションを提供する製 品です。コンバータは外部の抵抗デバイダによる設定か、チッ プ内部で固定に設定された値での安定した出力電圧を生成しま す。 高い効率の電力変換能力により、出力電圧5Vで1Aの電 流供給を入力電圧が1.8Vに低下するまで供給することができま す。昇圧コンバータは、固定周波数のパルス幅変調 (PWM) コン トローラと最大の効率を実現するため同期整流器を使用してい ます。負荷電流が低い時、コンバータは広い負荷電流範囲にわ たって高効率を維持するためパワー・セーブ・モードに切り替わ ります。パワー・セーブ・モードはディスエーブルにすることが でき、その場合コンバータは全域で固定のスイッチング周波数 で動作します。製品はSYNCピンにクロックを入力することに より外部クロックに同期して動作させる事ができます。昇圧 スイッチの最大ピーク電流は4500mAに制限されています。

コンバータは電池からの消費を最小限に抑えるためディスエーブルにすることができます。シャットダウン時負荷は電池から完全に切り離されます。低EMIモードはリンギングを低減するのに使用され、コンバータが不連続モードになった時の放射電磁エネルギーを低くします。このデバイスは  $4 \times 4 \text{ mm}$ の 16 ピンQFN PowerPAD M パッケージ (RSA) および<math>16 ピンTSSOP PowerPAD パッケージ (PWP) で供給されています。

PowerPADは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を

Tlおよび日本Tlは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

SLUS534D 翻訳版

最新の英語版資料 http://focus.ti.com/lit/ds/symlink/tps61030.pdf

# 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

#### 製品情報(1)

| T <sub>A</sub> | OUTPUT VOLTAGE<br>DC/DC | パッケージ                  | PART NUMBER <sup>(2)</sup> |

|----------------|-------------------------|------------------------|----------------------------|

|                | Adjustable              |                        | TPS61030PWP                |

|                | 3.3 V                   | 16-Pin TSSOP PowerPAD™ | TPS61031PWP                |

| 40°C ∼ 85°C    | 5 V                     |                        | TPS61032PWP                |

| 40 C ~ 85 C    | Adjustable              |                        | TPS61030RSA                |

|                | 3.3 V                   | 16-Pin QFN             | TPS61031RSA                |

|                | 5 V                     |                        | TPS61032RSA                |

- (1) その他の固定出力電圧バージョンについては弊社にお問い合わせください。

- (2) パッケージはテープ/リールで供給されます。デバイス·タイプの末尾にRを付けてください(例、TPS61030PWPRまたは TPS61030RSAR)。個数はPWPパッケージ製品ではリール当たり2000個で、RSAパッケージ製品ではリール当たり3000個です。

#### 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

|                                                          | TPS6103x      |

|----------------------------------------------------------|---------------|

| Input voltage range on LBI                               | −0.3 V ~ 3.6V |

| Input voltage range on SW, VOUT, LBO, VBAT, SYNC, EN, FB | −0.3V ~ 7V    |

| Maximum junction temperature T <sub>J</sub>              | -40°C ∼ 150°C |

| Storage temperature range T <sub>stg</sub>               | -65°C ~ 150°C |

(1) 絶対最大定格以上のストレスは、製品に恒久的・致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作を意味するものではありません。絶対最大定格の状態に長時間置くことは、本製品の信頼性に影響を与えることがあります。

#### 推奨動作条件

|                                                             | MIN | NOM MAX | 単  | 位        |

|-------------------------------------------------------------|-----|---------|----|----------|

| Supply voltage at VBAT, V <sub>I</sub>                      | 1.8 | 5.5     | '  | <b>/</b> |

| Operating ambient temperature range, T <sub>A</sub>         | -40 | 85      | ຶ( | С        |

| Operating virtual junction temperaturerange, T <sub>J</sub> | -40 | 125     | °( | С        |

# 電気的特性

over recommended free-air temperature range and over recommended input voltage range (typical at an ambient temperature range of 25°C) (特に記述のない限り)

| DC/DC             | STAGE                           |       |                                                                      |                   |                     |           |            |

|-------------------|---------------------------------|-------|----------------------------------------------------------------------|-------------------|---------------------|-----------|------------|

|                   | パラメータ                           |       | テスト条件                                                                | MIN               | TYP                 | MAX       | 単位         |

| V <sub>I</sub>    | Input voltage range             |       |                                                                      | 1.8               |                     | 5.5       | V          |

| Vo                | TPS61030 output voltage range   |       |                                                                      | 1.8               |                     | 5.5       | V          |

| $V_{FB}$          | TPS61030 feedback voltage       |       |                                                                      | 490               | 500                 | 510       | mV         |

| f                 | Oscillator frequency            |       |                                                                      | 500               | 600                 | 700       | kHz        |

|                   | Frequency range for synchroniza | ation |                                                                      | 500               |                     | 700       | kHz        |

|                   | Switch current limit            |       | VOUT = 5 V                                                           | 3600              | 4000                | 4500      | mA         |

|                   | Start-up current limit          |       |                                                                      |                   | $0.4 \times I_{SW}$ |           | mA         |

|                   | SWN switch on resistance        |       | VOUT = 5 V                                                           |                   | 55                  |           | mΩ         |

|                   | SWP switch on resistance        |       | VOUT = 5 V                                                           |                   | 55                  |           | mΩ         |

|                   | Total accuracy                  |       |                                                                      | -3%               |                     | 3%        |            |

|                   | Line regulation                 |       |                                                                      |                   |                     | 0.6%      |            |

|                   | Load regulation                 |       |                                                                      |                   |                     | 0.6%      |            |

|                   | Outros and assument             | VBAT  | I <sub>O</sub> = 0 mA, V <sub>EN</sub> = VBAT = 1.8 V,<br>VOUT = 5 V |                   | 10                  | 25        | μΑ         |

|                   | Quiescent current               |       | I <sub>O</sub> = 0 mA, V <sub>EN</sub> = VBAT = 1.8 V,<br>VOUT = 5 V |                   | 10                  | 20        | μА         |

|                   | Shutdown current                |       | V <sub>EN</sub> = 0 V, VBAT = 2.4 V                                  |                   | 0.1                 | 1         | μΑ         |

| CONT              | ROL STAGE                       |       |                                                                      |                   |                     |           |            |

|                   | パラメータ                           |       | テスト条件                                                                | MIN               | TYP                 | MAX       | 単 位        |

| $V_{\text{UVLO}}$ | Under voltage lockout threshold |       | V <sub>LBI</sub> voltage decreasing                                  |                   | 1.5                 |           | V          |

| $V_{IL}$          | LBI voltage threshold           |       | V <sub>LBI</sub> voltage decreasing                                  | 490               | 500                 | 510       | mV         |

|                   | LBI input hysteresis            |       |                                                                      |                   | 10                  |           | mV         |

|                   | LBI input current               |       | EN = VBAT or GND                                                     |                   | 0.01                | 0.1       | μА         |

|                   | LBO output low voltage          |       | $V_O = 3.3 \text{ V}, I_{OI} = 100 \mu\text{A}$                      |                   | 0.04                | 0.4       | V          |

|                   | LBO output low current          |       |                                                                      |                   | 100                 |           | μА         |

|                   | LBO output leakage current      |       | V <sub>LBO</sub> = 7 V                                               |                   | 0.01                | 0.1       | μА         |

| $V_{IL}$          | EN, SYNC input low voltage      |       |                                                                      |                   |                     | 0.2 ×VBAT | V          |

| $V_{IH}$          | EN, SYNC input high voltage     |       |                                                                      | $0.8 \times VBAT$ |                     |           | V          |

|                   | EN, SYNC input current          |       | Clamped on GND or VBAT                                               |                   | 0.01                | 0.1       | μΑ         |

|                   | Overtemperature protection      |       |                                                                      |                   | 140                 |           | $^{\circ}$ |

|                   | Overtemperature hysteresis      |       |                                                                      |                   | 20                  |           | $^{\circ}$ |

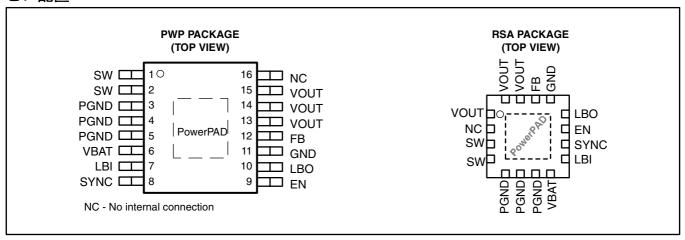

## ピン配置

# 端子機能

|           | 端子         |           |     |                                                                           |  |  |  |

|-----------|------------|-----------|-----|---------------------------------------------------------------------------|--|--|--|

| NAME      | NO.        |           | I/O | 機能                                                                        |  |  |  |

| NAME      | PWP        | RSA       |     |                                                                           |  |  |  |

| EN        | 9          | 11        | I   | イネーブル入力端子 (1/VBATの場合イネーブル、0/GNDの場合ディスエーブル                                 |  |  |  |

| FB        | 12         | 14        | I   | 可変出力電圧バージョンの電圧フィードバック端子                                                   |  |  |  |

| GND       | 11         | 13        | I/O | コントロール/ロジック・グランド                                                          |  |  |  |

| LBI       | 7          | 9         | I   | ロー・バッテリー・コンパレータ入力端子 (ENによりコンパレータはイネーブル)                                   |  |  |  |

| LBO       | 10         | 12        | 0   | ロー・バッテリー・コンパレータ出力端子 (オープン・ドレイン)                                           |  |  |  |

| NC        | 16         | 2         |     | 接続なし                                                                      |  |  |  |

| SYNC      | 8          | 10        | I   | パワー・セーブ・モードのイネーブル/ディスエーブル (1/VBATの場合ディスエーブル、0/GNDの場合イネーブル、外部同期運転用のクロック信号) |  |  |  |

| SW        | 1, 2       | 3, 4      | I   | 昇圧/整流スイッチ入力                                                               |  |  |  |

| PGND      | 3, 4, 5    | 5, 6, 7   | I/O | 電源グランド                                                                    |  |  |  |

| VBAT      | 6          | 8         | I   | 電源電圧                                                                      |  |  |  |

| VOUT      | 13, 14, 15 | 1, 15, 16 | 0   | 昇圧コンバータの出力端子                                                              |  |  |  |

| PowerPAD™ |            |           |     | 熱放散が適切に行われるようはんだ付けしなければなりません。<br>PGNDに接続してください。                           |  |  |  |

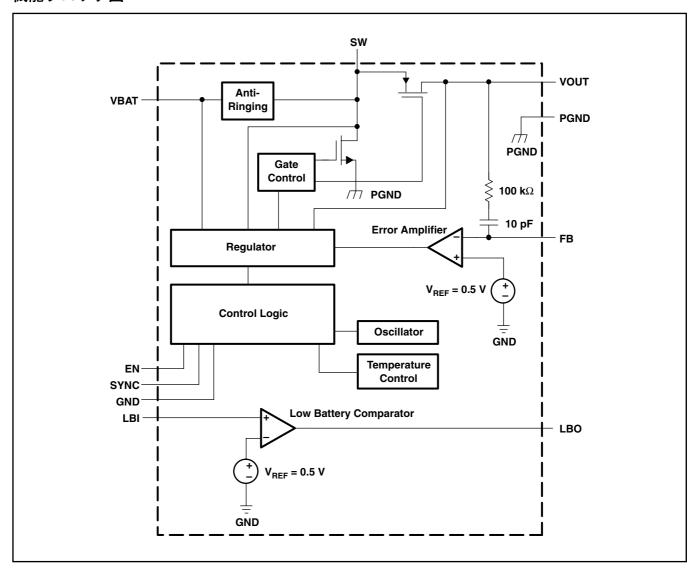

# 機能ブロック図

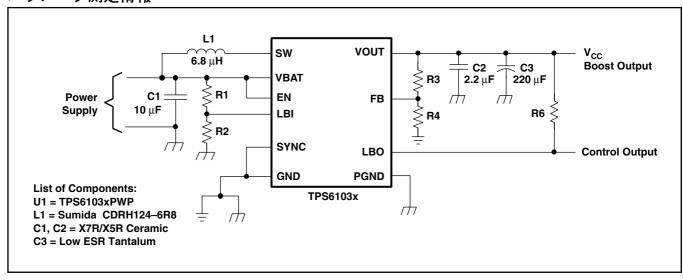

## パラメータ測定情報

# グラフ一覧

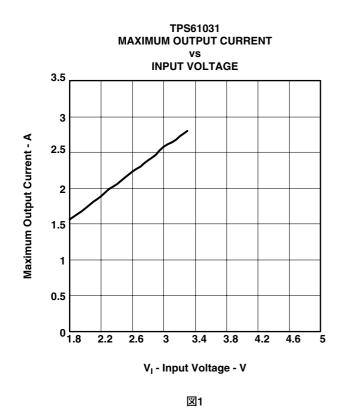

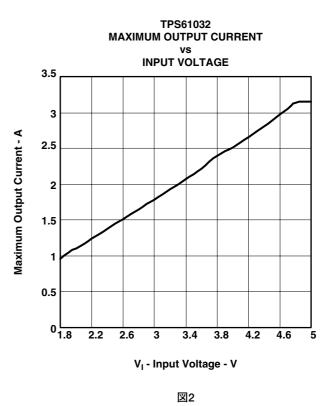

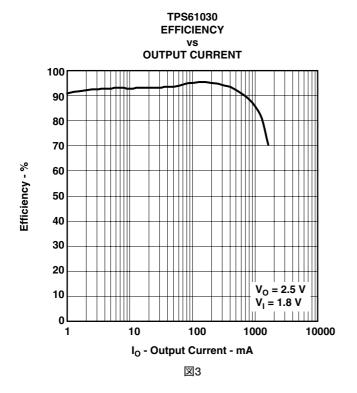

| DC/DC Converter                    |                                                                                                   | 図    |  |

|------------------------------------|---------------------------------------------------------------------------------------------------|------|--|

| Maximum output current             | vs Input voltage                                                                                  | 1, 2 |  |

|                                    | vs Output current (TPS61030) (V <sub>O</sub> = 2.5 V, V <sub>I</sub> = 1.8 V, VSYNC = 0 V)        | 3    |  |

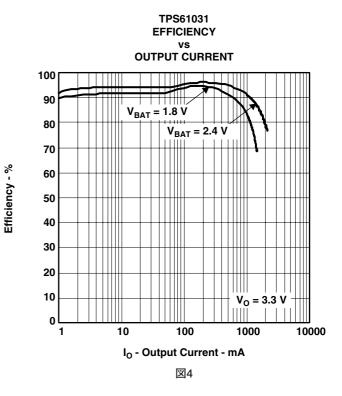

|                                    | vs Output current (TPS61031) (V <sub>O</sub> = 3.3 V, V <sub>I</sub> = 1.8 V, 2.4 V, VSYNC = 0 V) | 4    |  |

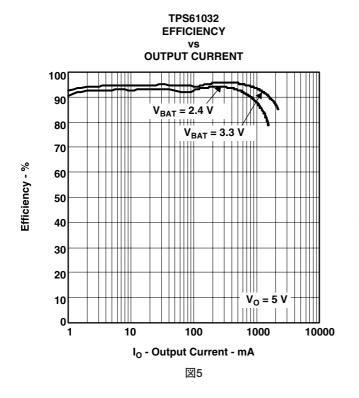

| Efficiency                         | vs Output current (TPS61032) (V <sub>O</sub> = 5.0 V, V <sub>I</sub> = 2.4 V, 3.3 V, VSYNC = 0 V) | 5    |  |

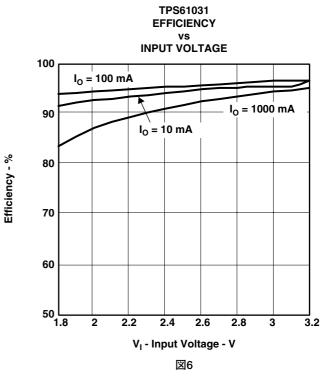

|                                    | vs Input voltage (TPS61031) (I <sub>O</sub> = 10 mA, 100 mA, 1000 mA, VSYNC = 0 V)                | 6    |  |

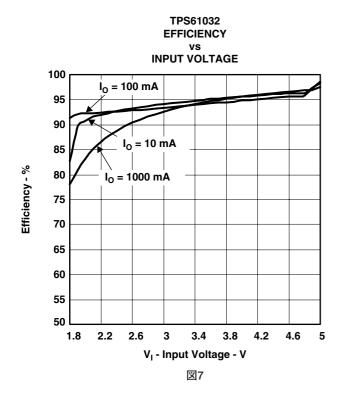

|                                    | vs Input voltage (TPS61032) (I <sub>O</sub> = 10 mA, 100 mA, 1000 mA, VSYNC = 0 V)                | 7    |  |

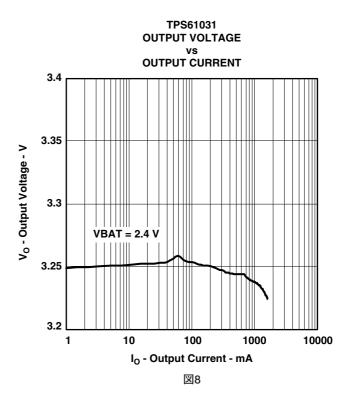

| Outroot and the sec                | vs Output current (TPS61031) (V <sub>I</sub> = 2.4 V)                                             | 8    |  |

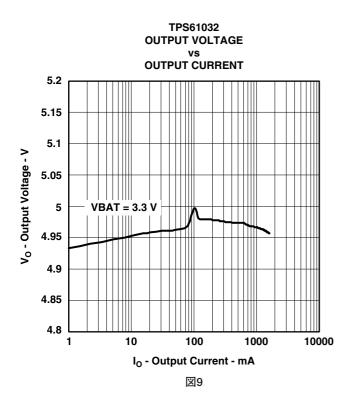

| Output voltage                     | vs Output current (TPS61032) (V <sub>I</sub> = 3.3 V)                                             | 9    |  |

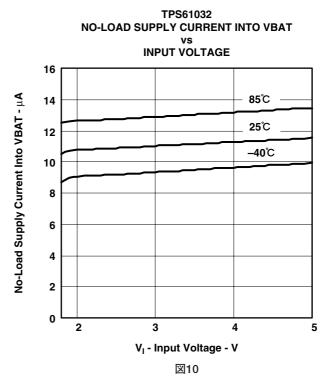

| No-load supply current into VBAT   | vs Input voltage (TPS61032)                                                                       | 10   |  |

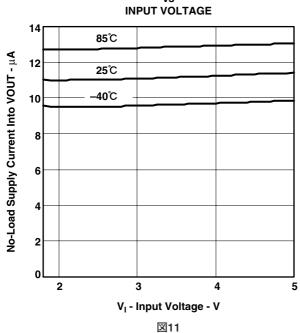

| No-load supply current into VOUT   | vs Input voltage (TPS61032)                                                                       | 11   |  |

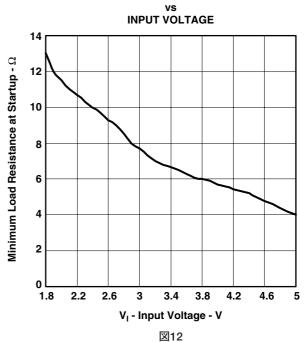

| Minimum Load Resistance at Startup | vs Input voltage (TPS61032)                                                                       | 12   |  |

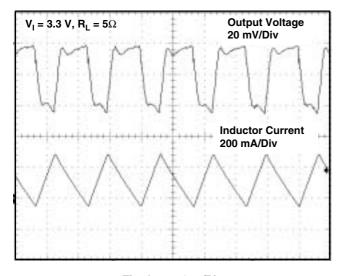

|                                    | Output voltage in continuous mode (TPS61032)                                                      | 13   |  |

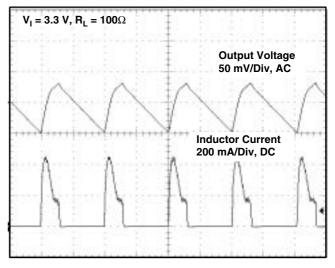

|                                    | Output voltage in power save mode (TPS61032)                                                      | 14   |  |

| Waveforms                          | Load transient response (TPS61032)                                                                |      |  |

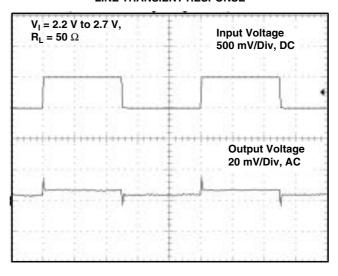

|                                    | Line transient response (TPS61032)                                                                | 16   |  |

|                                    | DC/DC converter start-up after enable (TPS61032)                                                  | 17   |  |

TPS61032 NO-LOAD SUPPLY CURRENT INTO VOUT vs INPUT VOLTAGE

#### MINIMUM LOAD RESISTANCE AT START-UP

TPS61032

OUTPUT VOLTAGE IN CONTINUOUS MODE

Timebase - 1  $\mu$ s/Div

図13

TPS61032 OUTPUT VOLTAGE IN POWER SAVE MODE

Timebase - 200 μs/Div

図14

#### TPS61032 LOAD TRANSIENT RESPONSE

# V<sub>I</sub> = 2.5 V, I<sub>L</sub> = 80 mA to 800 mA 500 mA/Div, DC

Timebase - 2ms/Div

図15

#### TPS61032 LINE TRANSIENT RESPONSE

Timebase - 2ms/Div

図16

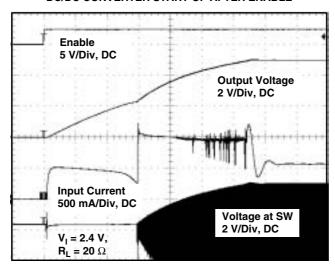

#### TPS61032 DC/DC CONVERTER START-UP AFTER ENABLE

Timebase - 400 µs/Div

図17

## 詳細説明

#### コントローラ回路

このデバイスは固定周波数の多重フィードフォワード・コントローラ・トポロジが基礎となっています。入力電圧、出力電圧、NMOSスイッチの電圧降下はモニタされ、レギュレータに直接送られます。従って、コンバータの動作状態が変化するとデューティ・サイクルを直接制御するため、コントロール・ループや誤差増幅器を通るゆっくりとした経路をとる必要はありません。誤差増幅器によって決まる、コントロール・ループは、小信号誤差を取り扱うことのみで十分です。FBピンへのフィードバック電圧または固定電圧バージョンでは内部抵抗デバイダからの小信号誤差の入力は正確で安定した電圧を生成するため内部基準電圧と比較されます。

また、スイッチとインダクタを流れる最大電流を制限するためNMOSスイッチのピーク電流も検出されます。ピーク電流制限値は標準で4000mAに設定されています。内部の温度センサにより電力消費が過度な場合にデバイスが過熱するのを防止します。

#### 同期整流器

このデバイスは同期整流を実現するためNチャネルおよび PチャネルMOSFETトランジスタを内蔵しています。一般に使 用されているショットキー·ダイオードが低オン抵抗RDS(ON) のPMOSスイッチに置き換えられているため、電力変換効率は 96%にも達します。NMOSスイッチの大電流によるグランド・ シフトを避けるため、2つの別々のグランド・ピンが使用されて います。すべてのコントロール機能に対する基準はGNDピン です。NMOSスイッチのソースはPGNDに接続されています。 この両方のグランドはPCB上でGNDピンの近くで1点のみで接 続しなければなりません。コンバータがシャットダウンされて いる時に負荷を入力から切り離すため特別な回路が用いられて います。従来の同期整流回路では、ハイサイドPMOSの寄生ダ イオードがシャットダウン時に順方向にバイアスされるため、 電池から出力に電流が流れてしまいます。しかし、このデバイ スはハイサイドPMOSの寄生ダイオードのカソードに特別な回 路を取り込み、レギュレータがイネーブルでない時(EN = "L" レベル) ソースから切り離しています。

システム設計の技術者にとってこの機能の利点とは、コンバータのシャットダウン時電池が消耗しないことです。確実に 電池をコンバータの出力から切り離すための設計上の追加部品 は不要です。

#### デバイスのイネーブル

ENピンを"H"レベルにセットする事によりデバイスは動作するようになります。ENピンがGNDにセットされた場合デバイスはシャットダウン・モードになります。シャットダウン・モードでは、レギュレータはスイッチングを停止し、ロー・バッテリー・コンパレータを含むすべての内部コントロール回路はオフに切り換わり、負荷は入力から分離されます("同期整流器"の項参照)。また、このことは、シャットダウン時には出力電圧は入力電圧より下に低下するということを意味しています。コンバータの起動時、電池から大きなピーク電流が流れないようにするためデューティ・サイクルとピーク電流は起動時設定により制限されています。

### 低電圧ロックアウト

低電圧ロックアウト機能によりVBATピンの電源電圧が約1.6Vより下であるとデバイスの起動は停止されます。動作時および電池が放電している時、VBATピンの電圧が約1.6Vより下に低下すると、デバイスは自動的にシャットダウン・モードになります。この低電圧ロックアウト機能はコンバータの誤動作を防ぐために用いられます。

#### ソフトスタート

デバイスがイネーブルされると、内部の起動サイクルは最初のサイクルであるプリチャージ・フェーズを開始します。プリチャージ時、出力キャパシタが入力電圧に近い値に充電されるまで整流スイッチはオンになっています。整流スイッチはそのフェーズの間電流制限されています。この機能により、出力短絡状態での出力電流も制限されます。出力キャパシタを入力電圧まで充電した後、デバイスはスイッチングを開始します。出力電圧がその標準値に達するまで、昇圧スイッチの電流制限値は起動時に電池から大きなピーク電流が流れるのを回避するためその標準値の40%に制限されています。出力電圧に達するとレギュレータはコントロールを開始し、スイッチの電流制限値は100%の値に設定されます。

#### パワー・セーブ・モードと外部同期

SYNCピンは種々の動作モードを選択するのに使用できます。パワー・セーブをイネーブルにするには、SYNCピンを"L"レベルに設定しなければなりません。パワー・セーブ・モードは軽負荷時の効率を改善するのに使用されます。パワー・セーブ・モードでは、コンバータは出力電圧が設定スレッショルド電圧より下になった時にのみ動作します。コンバータは1つまたはいくつかのパルスにより出力電圧を増加させ、出力電圧が設定スレッショルド電圧を越えると再びパワー・セーブ・モードになります。このパワー・セーブ・モードはSYNCをVBATに接続することによりディスエーブルにすることができます。

デューティ比が30%から70%の外部クロック信号をSYNC ピンに供給する事によりコンバータは供給されたクロック周波 数に同期して動作します。外部クロック周波数は内部クロック 周波数の標準値の約±20%の範囲内である必要が有ります。数 値の詳細はデータシートの電気的特性を参照してください。

#### ロー・バッテリー検出回路 - LBI/LBO

ロー・バッテリー検出回路は、通常、電池電圧を管理し、電池電圧がユーザー設定のスレッショルド電圧より下に低下した時エラー・フラグを生成するのに使用されます。この機能はデバイスがイネーブルの場合にのみアクティブです。デバイスがディスエーブルの場合、LBOピンはハイ・インピーダンスです。その切り替わりのスレッショルド電圧はLBIで500mVです。正常動作時、LBIに印加される電圧がスレッショルドより上の場合LBOはハイ・インピーダンスです。LBIの電圧が500mVより下に

低下した時アクティブの"L"レベルになります。

検出が切り替わる電池電圧はLBIピンに接続される抵抗デバイダによりプログラムすることができます。抵抗デバイダは電池電圧を500mVの電圧レベルに分圧し、次にその電圧はLBIスレッショルド電圧と比較されます。LBIピンには10mVのヒステリシスが設定されています。LBIスレッショルドのプログラミングの詳細については"アプリケーション情報"の項を参照してください。ロー・バッテリー検出回路を使用しない場合は、LBIピンはGND(またはVBAT)に接続しなければならず、一方LBOピンは未接続にしておくことができます。LBIピンをフローティングにしてはいけません。

#### 低EMIスイッチ

このデバイスは、コンバータが不連続モードになった時、通常SWノードに現れるリンギングを除去する回路を内蔵しています。不連続モードではインダクタに流れる電流はゼロまで減少し、整流PMOSスイッチは出力キャパシタから電池に戻ってくる逆電流を防止するためオフになります。半導体とインダクタの寄生成分に貯えられている残留エネルギーにより、SWピンにリンギングが生じます。内蔵のアンチリンギング・スイッチがこの電圧をVBATにクランプするため、リンギングが減少します。

# アプリケーション情報

#### 設計手順

TPS6103x DC/DCコンバータは、標準端子電圧が1.8Vから5.5Vで2セルから3セルまでのニッカド、ニッケル水素電池を電源とするシステム向けの製品です。このコンバータは、また、標準電圧が2.5Vから4.2Vの1セルのリチウム・イオンまたはリチウム・ポリマーを電源とするシステムにも使用することができます。さらに、2セルから3セルの1次および2次のアルカリ電池もTPS6103xが使われるシステムに電源を供給することができます。

#### 出力電圧のプログラミング

TPS61030 DC/DCコンバータの出力電圧は外付けの抵抗デバイダにより可変で調整することができます。FBピンの標準電圧値は500mVです。出力電圧の推奨最大値は5.5Vです。抵抗デバイダを流れる電流はFBピンに流れ込む電流の約100倍にします。FBピンに流れ込む電流の標準値は0.01 $\mu$ Aで、R4の端子間電圧は500mVです。この2つの値をもとに、デバイダ電流を $\mu$ Aまたはそれより高く設定するためにはR4の推奨値は500kΩより小さくなければなりません。内部の位相補償回路との関係から、この抵抗値は200kΩ以下でなければなりません。このことから、抵抗R3の値は、必要とされる出力電圧( $V_0$ )により、以下の式(1)を使って計算できます。

$$R3 = R4 \times \left(\frac{V_O}{V_{FB}} - 1\right) = 180k\Omega \times \left(\frac{V_O}{500mV} - 1\right)$$

(1)

例として、3.3Vの出力電圧が必要とされる場合、R3には 1.0M $\Omega$ の抵抗が選択されます。何らかの理由でR4に200k $\Omega$ よりかなり小さい値が選択された場合、R3と並列に容量を付加することを推奨します。必要とされる容量値は以下の式 (2) を使って簡単に計算できます。

$$R_{parR3} = 10pF \times \left(\frac{200k\Omega}{R4} - 1\right)$$

(2)

#### LBI/LBOスレッショルド電圧のプログラミング

抵抗デバイダを流れる電流はLBIピンに流れ込む電流の約100 倍にします。LBIピンに流れ込む電流の標準値は $0.01\mu$ Aで、R2 端の電圧はチップで生成される500mVの値をもつLBI電圧スレッショルドと等しくなります。従って、R2の推奨値は $500k\Omega$ 程度です。このことから、抵抗R1の値は、設定する最小電池電圧 $V_{BAT}$ により、以下の式 (3) を使って計算できます。

R1 = R2 ×

$$\left(\frac{V_{BAT}}{V_{LBI-threshold}} - 1\right)$$

= 390k $\Omega$  ×  $\left(\frac{V_{BAT}}{500mV} - 1\right)$  (3)

ロー・バッテリー・スーパーバイザの出力は、使用されている 電池の電圧がLBIのプログラムされたスレッショルド電圧より 下に低下するとアクティブで"L"レベルになる簡素なオープン・ ドレイン出力です。この出力には推奨値1MΩのプルアップ抵 抗が必要です。LBO出力のプルアップに使用する電源の最大電 圧はDC/DCコンバータの出力電圧を越えてはいけません。使 用しない場合にはLBOピンはフローティングにしておくかまた はGNDに接続します。

### インダクタの選択

昇圧コンバータは変換時にエネルギーを貯えるため通常2つの主要受動部品が必要です。つまり、昇圧インダクタと出力にストレージ・キャパシタが必要となります。昇圧インダクタを選択するには、選択した構成において起こり得るピーク・インダクタ電流を昇圧スイッチの電流制限スレッショルドより下に保持することを推奨します。例えば、TPS6103xのスイッチの電流制限スレッショルドは出力電圧が5Vの時4500mAです。インダクタとスイッチを流れる最大ピーク電流は、出力負荷、入力電圧  $(V_{BAT})$ 、出力電圧  $(V_{OUT})$  に依存します。最大平均インダクタ電流は以下の式(4)を使って概算できます。

$$I_{L} = I_{OUT} \times \frac{V_{OUT}}{V_{BAT} \times 0.8}$$

(4)

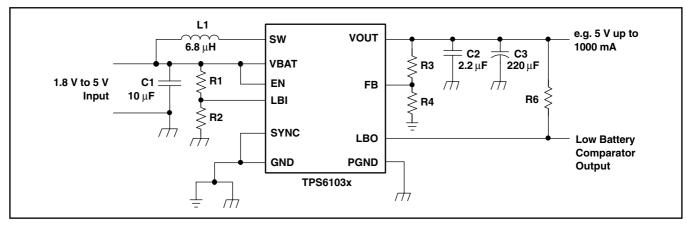

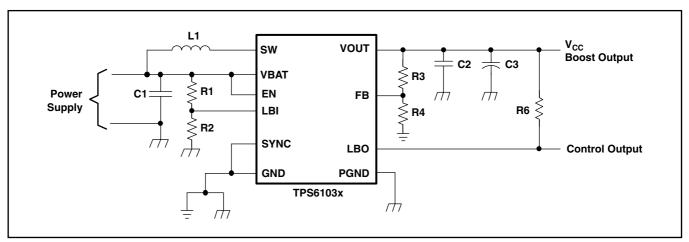

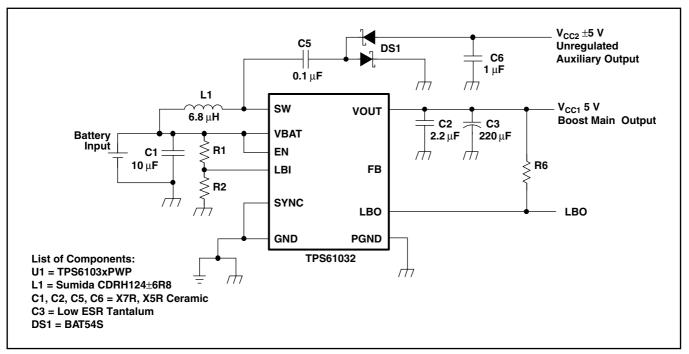

図18. Typical Application Circuit for Adjustable Output Voltage Option

例えば、出力電圧が5.0V、出力電流が1000mAの場合、1.8V の最小入力電圧の時少なくとも3500mAの平均電流がインダクタを流れます。

インダクタを選択する際の2番目のパラメータはインダクタのリップル電流です。通常、望ましくは平均インダクタ電流の20%より小さいリップルで動作することです。リップルが小さいと出力電圧リップルやEMIだけでなくインダクタの磁気ヒステリシス損も低減します。しかし、同じように、負荷変化時のレギュレーション時間が増加します。さらに、インダクタが大きいとシステムの総コストも増大します。これらのパラメータにより以下の式(5)を使ってインダクタの値を計算することができます。

$$L = \frac{V_{BAT} \times (V_{OUT} - V_{BAT})}{\Delta I_{L} \times f \times V_{OUT}}$$

(5)

パラメータf はスイッチング周波数、 $\Delta I_L$ はインダクタのリップル電流、すなわち $10\% \times I_L$ です。この例では、求められたインダクタ値は $5.5\mu H$ です。標準的なアプリケーションでは $6.8\mu H$ のインダクタを推奨します。使用可能な最少インダクタンス値は $2.2\mu H$ です。計算されたインダクタンス値と負荷電流値に応じてより適切なインダクタを選択することができます。負荷過渡応答と回路の損失により、式(4)で概算されるより大きな電流が流れる可能性があることに注意する必要があります。また、磁気ヒステリシス損や銅損により生じるインダクタの損失も回路の総合効率にとって重要なパラメータとなります。

以下の各サプライヤのインダクタ・シリーズ製品がTPS6103x コンバータとともに使用されています。

| ベンダー             | インダクタ・シリーズ名 |  |  |  |

|------------------|-------------|--|--|--|

|                  | CDRH124     |  |  |  |

| Sumida           | CDRH103R    |  |  |  |

|                  | CDRH104R    |  |  |  |

| Wurth Electronik | 7447779     |  |  |  |

| Wurth Electronik | 744771      |  |  |  |

| EPCOS            | B82464G     |  |  |  |

表1. インダクタ・リスト

## キャパシタの選択

#### 入力キャパシタ

レギュレータの過渡動作及び電源回路全体の動作を改善するため少なくとも10μFの入力キャパシタを推奨します。0.1μFのセラミック・キャパシタをセラミック・キャパシタまたはタンタル・キャパシタと並列にICの直近に配置することを推奨します。

#### 出力キャパシタ

出力キャパシタを規定するのに必要な主要パラメータはコン バータの最大許容出力電圧リップルです。このリップルは、 キャパシタの2つのパラメータである、容量とESRで決まります。ESRをゼロと仮定して、規定したリップルに必要とされる最小容量を以下の式(6)を使って計算できます。

$$C_{\min} = \frac{I_{\text{OUT}} \times (V_{\text{OUT}} - V_{\text{BAT}})}{f \times \Delta V \times V_{\text{OUT}}}$$

(6)

パラメータはスイッチング周波数、 $\Delta V$ は最大許容リップルです。

リップル電圧を10mVに選択すると、最小容量 $100\mu$ Fが必要となります。総リップルは出力キャパシタのESRによりこれより大きくなります。このさらなるリップル成分は式(7)を使って計算できます。

$$\Delta V_{\rm ESR} = I_{\rm OUT} \times R_{\rm ESR} \tag{7}$$

80mΩの低ESRのタンタル・キャパシタを使用した結果追加されるリップルは80mVです。総リップルは容量により生じるリップルとキャパシタのESRにより生じるリップルの合計です。この例では、総リップルは90mVです。さらに別のリップルが負荷過渡により生じます。これにより、リップル電圧の要求を満足させるには、上記の計算により求めた値より大きな容量が必要となります。

出力キャパシタはインダクタの充電フェーズ時、十分に負荷に電流を供給できる能力が必要であるということを意味しています。出力容量の適正値は負荷変化時の負荷過渡の速度と負荷電流値に依存します。最小容量の計算結果100μFと負荷過渡を考慮すると、推奨出力容量値は220μF程度となります。経済的理由により、これは通常はタンタル・キャパシタになります。従って、内部位相補償は30mΩ以上のESRをもつ出力キャパシタを使用する事を前提に設計を最適化されています。出力キャパシタの最小値は22μFです(注:リップル電圧や負荷過渡による電圧変動を考慮していない、異常発振しないで動作する為の最低容量です)。

#### 小信号安定性

セラミックのような低いESRの出力キャパシタを使用する場合には、可変出力電圧バージョンを推奨します。ESRの不足はフィードバック・デバイダで補償することができます。一般的に10pF程度のキャパシタをR3に並列にすると低ESRの出力キャパシタで小信号安定性を得るのに役立ちます。より詳細の解析には、式(8)で求められる誤差増幅器とレギュレータの小信号伝達関数を使用することができます。

$$A_{REG} = \frac{d}{V_{FB}} = \frac{5 \times (R3 + R4)}{R4 \times (1 + i \times \omega \times 2.3 \mu s)}$$

(8)

## レイアウトについての考察

すべてのスイッチング電源、特に高ピーク電流及び高スイッチング周波数の場合、レイアウトは設計時の重要なステップとなります。レイアウトが注意深く行われていないと、レギュレータではEMI問題はもとより安定性の問題も生じることがあります。従って、主要な電流パスや電力用グランド・トラックには広く短い配線を使用してください。入力キャパシタ、出力キャパシタ、インダクタはできるだけICの近くに配置しなければなりません。グランド・ノイズの影響を最小限に抑えるため、電力用グランドには共通のグランド・ノードを使用し、制御回

路用グランドにはこれとは別のノードを使用してください。これらのグランド・ノードはICのグランド・ピンの1つに近い場所で接続してください。フィードバック・デバイダはICの制御回路用グランドのピンにできるだけ近い場所に配置しなければなりません。制御回路用グランドを適切に配置するには、配線を短くし、さらに電源グランドの配線から分離することを推奨します。このことにより、電力用グランドの電流と制御回路用グランドの電流の重なり合いにより起こり得るグランド・シフトの問題が避けられます。

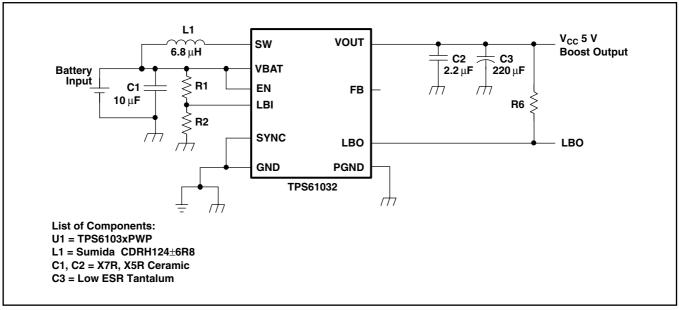

**図19.** Power Supply Solution for Maximum Output Power

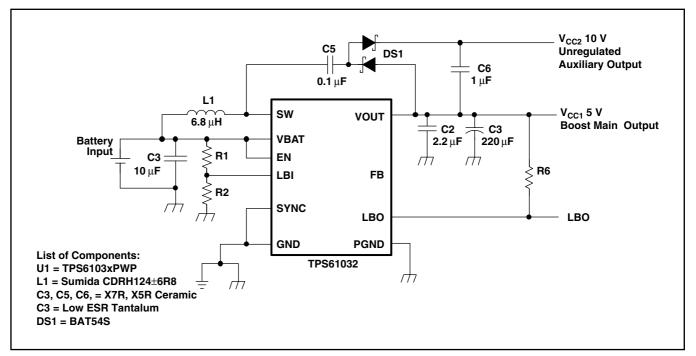

図20. Power Supply Solution With Auxiliary Positive Output Voltage

図21. Power Supply Solution With Auxiliary Negative Output Voltage

## 熱情報

薄型、狭ピッチの表面実装パッケージICを使用する際には一般的に消費電力への特別な注意が必要です。熱結合、エアフロー、追加ヒートシンクと対流面、他の発熱部品の存在といった多くのシステム依存の問題が与えられた部品の許容損失の制限に影響を及ぼします。熱特性を向上させる基本的な3つの方法を以下にあげます。

- PCB設計において基板の熱抵抗を下げることにより許容損失 能力を改善する

- 部品のPCBへの熱結合を改善する

- システムにエアフローを導入する

TPS6103xデバイスの推奨最大接合部温度  $(T_J)$  は125 $\mathbb{C}$ です。PowerPADがはんだ付けされた場合、16ピンTSSOP PowerPADパッケージ (PWP) の熱抵抗 $R_{\theta JA}$ は36.5 $\mathbb{C}$ /W (QFNパッケージのRSAでは38.1 $\mathbb{C}$ /W) です。レギュレータの動作規定は最大問囲温度 $T_A=85\mathbb{C}$ で保証されています。従って、許容損失はPWPパッケージでは約1096mWで、RSAパッケージでは約1050mWです。アプリケーションの最大周囲温度がこれより低ければ、より大きな電力を消費することができます。

$$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \frac{\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}}{\mathsf{R}_{\theta}\mathsf{J}\mathsf{A}} = \frac{125 \ {^{\circ}}\! \mathsf{C} - 85 \ {^{\circ}}\! \mathsf{C}}{36.5 \ {^{\circ}}\! \mathsf{C}/\mathsf{W}}$$

# パッケージ・オプション

## パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| TPS61030PWP      | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61030PWPG4    | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61030PWPR     | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61030PWPRG4   | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61030RSAR     | ACTIVE                | QFN             | RSA                | 16   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61030RSARG4   | ACTIVE                | QFN             | RSA                | 16   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61031PWP      | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61031PWPG4    | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61031PWPR     | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61031PWPRG4   | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61031RSAR     | ACTIVE                | QFN             | RSA                | 16   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61031RSARG4   | ACTIVE                | QFN             | RSA                | 16   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61032PWP      | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61032PWPG4    | ACTIVE                | HTSSOP          | PWP                | 16   | 90             | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61032PWPR     | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61032PWPRG4   | ACTIVE                | HTSSOP          | PWP                | 16   | 2000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61032RSAR     | ACTIVE                | QFN             | RSA                | 16   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS61032RSARG4   | ACTIVE                | QFN             | RSA                | 16   | 3000           | Green (RoHS & no Sb/Br)    | CUNIPDAU         | Level-2-260C-1 YEAR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE:製品デバイスが新規設計用に推奨されています。

LIFEBUY:TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free"(鉛フリー)は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green (RoHS & no Sb/Br):**TIにおける "Green" は、"Pb-Free"(RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質 な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

$^{(3)}$  MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

TIは、いかなる場合においても、かかる情報により発生した損害について、TIがお客様に1年間に販売した本書記載の問題となった TIパーツの購入価格の合計金額を超える責任は負いかねます。

# パッケージ・マテリアル情報

## テープおよびリール・ボックス情報

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPS61030PWPR | HTSSOP          | PWP                | 16   | 2000 | 330.0                    | 12.4                     | 6.8     | 5.4     | 1.6     | 8.0        | 12.0      | Q1               |

| TPS61030RSAR | QFN             | RSA                | 16   | 3000 | 330.0                    | 12.4                     | 4.3     | 4.3     | 1.5     | 8.0        | 12.0      | Q2               |

| TPS61031PWPR | HTSSOP          | PWP                | 16   | 2000 | 330.0                    | 12.4                     | 6.8     | 5.4     | 1.6     | 8.0        | 12.0      | Q1               |

| TPS61031RSAR | QFN             | RSA                | 16   | 3000 | 330.0                    | 12.4                     | 4.3     | 4.3     | 1.5     | 8.0        | 12.0      | Q2               |

| TPS61032PWPR | HTSSOP          | PWP                | 16   | 2000 | 330.0                    | 12.4                     | 6.8     | 5.4     | 1.6     | 8.0        | 12.0      | Q1               |

| TPS61032RSAR | QFN             | RSA                | 16   | 3000 | 330.0                    | 12.4                     | 4.3     | 4.3     | 1.5     | 8.0        | 12.0      | Q2               |

# パッケージ・マテリアル情報

#### \*All dimensions are nominal

| Device       | PackageType | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|-------------|-----------------|------|------|-------------|------------|-------------|

| TPS61030PWPR | HTSSOP      | PWP             | 16   | 2000 | 346.0       | 346.0      | 29.0        |

| TPS61030RSAR | QFN         | RSA             | 16   | 3000 | 340.5       | 333.0      | 20.6        |

| TPS61031PWPR | HTSSOP      | PWP             | 16   | 2000 | 346.0       | 346.0      | 29.0        |

| TPS61031RSAR | QFN         | RSA             | 16   | 3000 | 340.5       | 333.0      | 20.6        |

| TPS61032PWPR | HTSSOP      | PWP             | 16   | 2000 | 346.0       | 346.0      | 29.0        |

| TPS61032RSAR | QFN         | RSA             | 16   | 3000 | 340.5       | 333.0      | 20.6        |

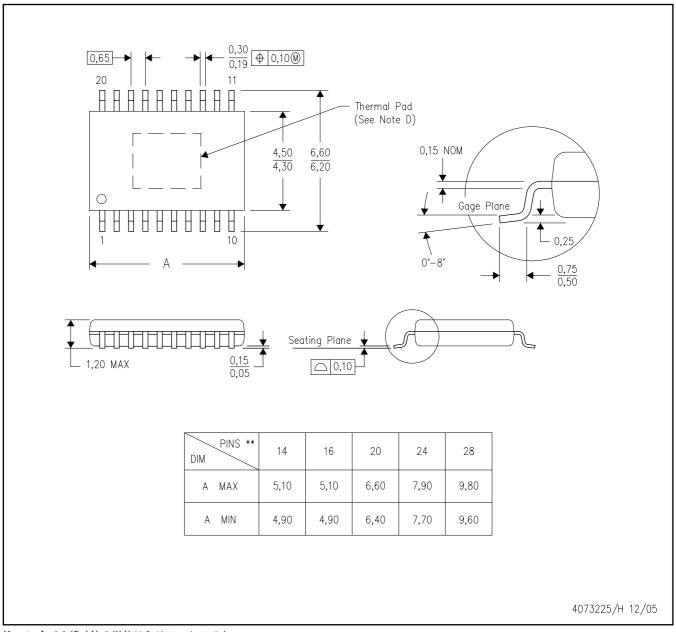

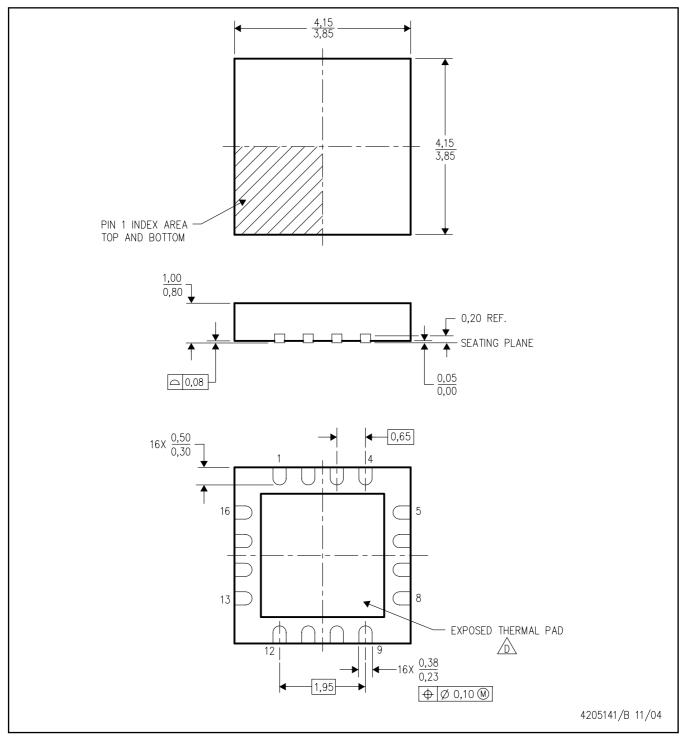

#### PWP (R-PDSO-G\*\*)

20 PIN SHOWN

- 注:A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

- C. ボディの寸法には、0,15を超えるモールド・フラッシュや突起は含まれません。 D. このパッケージは、基板上のサーマル・パッドに半田付けされるように設計されています。推奨基板レイアウトについては、 テクニカル・ブリーフ『PowerPAD Thermally Enhanced Package』(TI文献番号SLMA002)を参照してください。 これらのドキュメントは、ホームページwww.ti.comで入手できます。 E. JEDEC MO-153に準拠します。

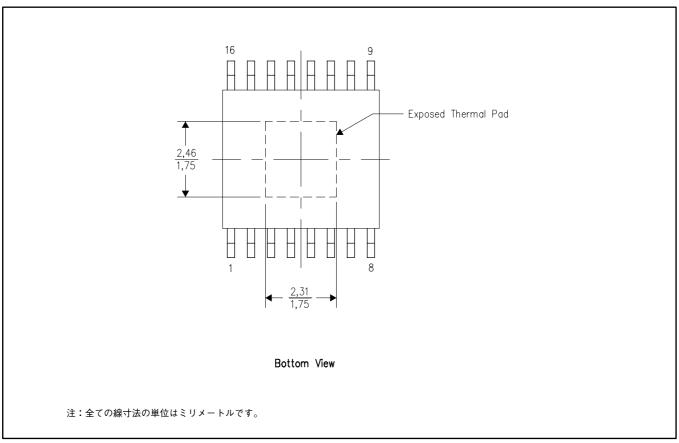

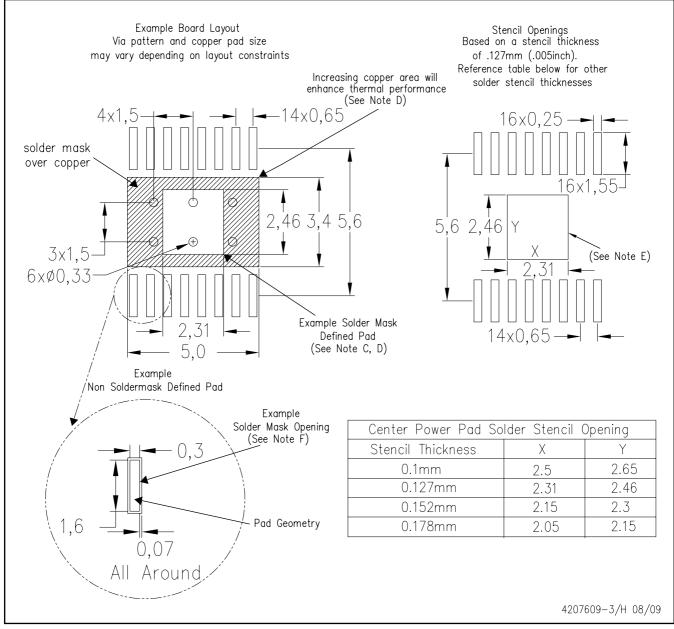

# サーマルパッド・メカニカル・データ

#### PWP (R-PDSO-G16)

## 熱的特性の情報

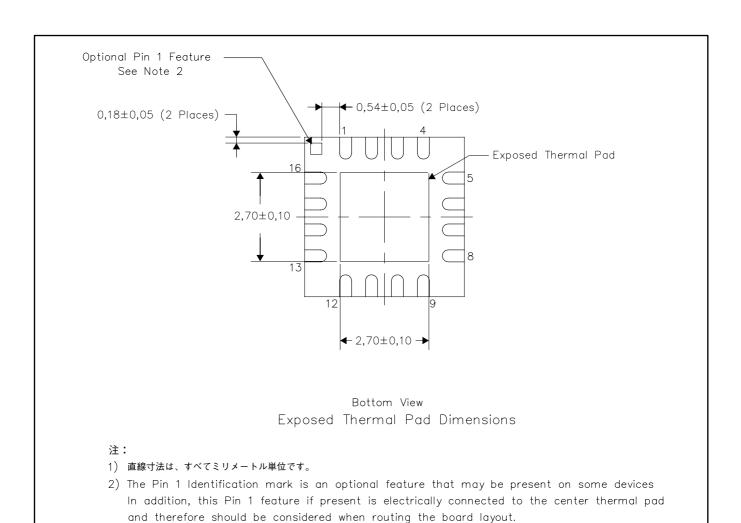

このPowerPADTMパッケージは外部のヒートシンクに直接接続できるよう設計された露出したサーマル・パッドをもっています。サーマル・パッドはプリント回路基板 (PCB) に直接はんだ付けされなければなりません。はんだ付けの後、PCBはヒートシンクとして使用できます。さらに、サーマル・ビアを使用することにより、サーマル・パッドはデバイスの電気回路図に示されている銅プレーンに直接接続するか、あるいは、PCBに設計された特別なヒートシンク構造に接続することができます。この設計により、集積回路 (IC) からの熱移動が最適化されます。

PowerPAD<sup>TM</sup>パッケージの追加情報及びその熱放散能力の利用法についてはテクニカル・ブリーフ "PowerPAD<sup>TM</sup> Thermally Enhanced Package" TI文献番号SLMA002とアプリケーション・ブリーフ "PowerPAD<sup>TM</sup> Made Easy" TI文献番号SLMA004を参照してください。両方の文献ともホームページwww.ti.comで入手できます。

このパッケージの露出サーマル・パッドの寸法は以下の図に 示されています。

サーマル・パッド寸法図

#### PWP (R-PDSO-G16) PowerPAD™

- 注:A. 全ての線寸法の単位はミリメートルです。

- B. 図は予告なく変更することがあります。

C. カスタマは中央のはんだマスク規定パッドを変更しないよう回路ボードの製作図面に注釈をつけなければなりません。

D. 本パッケージは、サーマルパッドを基板に半田付けするように設計されています。具体的な熱的特性資料、ヴィア条件、推奨基板レイアウトについては、テクニカル・ブリーフ「PowerPAD熱特性強化パッケージ」テキサス・インスツルメンツ文献番号SLMA002、 SLMA004および製品データシートも参照願います。これらの文献はwww.tij.co.jp、www.ti.com < http://www.ti.com > で入手できます。 代替設計には、IPC-7351規格を推奨します。

- E. 台形壁面やラウンドコーナーにレーザー・カッティング・アパーチャを行うと、ペーストのリリースが容易になります。推奨のステン シル設計については、基板組立元に問合せ願います。ステンシルの設計例は、50%容積金属負荷半田ペーストに基づいています。 ステンシル設計の検討については、IPC7525規格を参照願います。

- F. 信号パッドの間および周辺の半田マスク公差については、基板製造元に問合せ願います。

- 注:A. 全ての線寸法の単位はミリメートルです。寸法および許容誤差はASME Y14.5M-1994によります。

- B. 図は予告なく変更することがあります。

- C. クゥアド・フラットパック・ノーリード(QFN)パッケージ構造。

- E. JEDEC MO-220に準拠します。

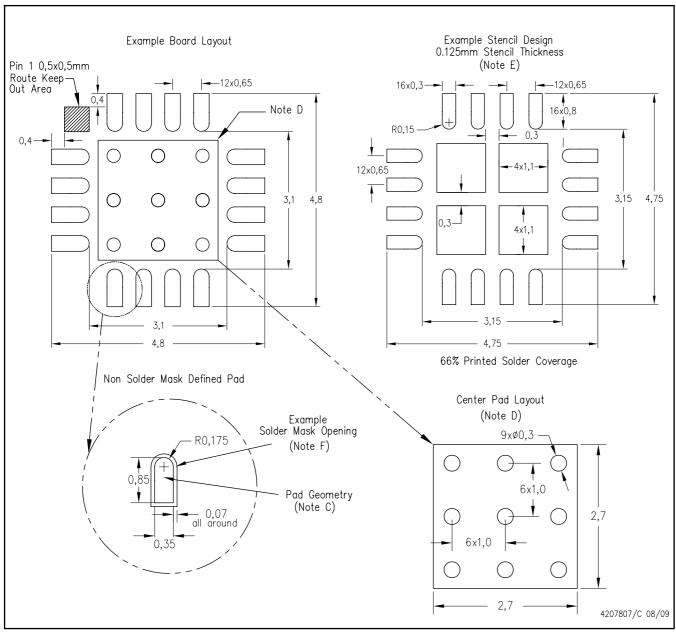

#### サーマルパッド・メカニカル・データ

## RGT (S-PVQFN-N16)

#### 熱的特性の情報

本パッケージは、外付けヒートシンクに直接取り付けられるように設計した、露出サーマルパッドを組み込んでいます。サーマルパッドは、プリント基板 (PCB) に直接半田付けする必要があります。半田付けをした後は、PCBがヒートシンクとして使用できます。さらに、サーマル・ビアを使用すると、サーマルパッドはデバイスの電気的図面に示す適当な銅面、あるいはその代わりとして、PCBに設計された特殊なヒートシンク構

造物に直接取り付けられます。この設計により、集積回路(IC)からの熱伝導が最適化されます。

クゥアド・フラットパック・ノーリード (QFN) パッケージおよびその利点に関する情報は、アプリケーション・レポート「クゥアド・フラットパック・ノーリード・ロジック・パッケージ」、テキサス・インスツルメンツ文献番号SCBA017を参照願います。本文献はwww.ti.comで入手できます。

本パッケージの露出サーマルパッドの寸法を下図に示します。

露出サーマルパッドの寸法

## ランド・パターン

#### RSA (S-PVQFN-N16)

- 注:A. 直線寸法はすべてミリメートル単位です。

- B. 本図は予告なしに変更することがあります。

- C. 代替設計には、IPC-7351規格を推奨します。

- D. 本パッケージは、サーマルパッドを基板に半田付けするように設計されています。具体的な熱的特性情報、ヴィア条件、および 推奨基板レイアウトについては、アプリケーション・ノート「クゥアド・フラットパック・パッケージ」テキサス・インスツルメンツ 文献番号SCBA017、SLUA271、および製品データシートも参照してください。これらの文献はwww.tij.co.jpもしくは www.ti.com < http://www.ti.com> で入手できます。

- E. 台形壁面やラウンドコーナーにレーザー・カッティング・アパーチャを行うと、ペーストのリリースが容易になります。 推奨のステンシル設計については、基板組立元に問合せてください。ステンシル設計の検討については、IPC7525規格を参照して ください。

- F. 信号パッド間の最小半田マスク・ウェブ公差については、基板製造元に問合せてください。

(SLUS534D)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上