ADC128S102-SEP JAJSLJ3A - DECEMBER 2021 - REVISED APRIL 2022

# ADC128S102-SEP 放射線耐性、8 チャネル、50kSPS~1MSPS 12 ビット ADC

# 1 特長

- 放射線耐性:

- シングル・イベント・ラッチアップ (SEL) 耐性:LET  $= 43 MeV - cm^2/mg (125^{\circ}C)$

- LET = 43MeV-cm<sup>2</sup>/mg まで、SEFI (Single-Event Functional Interrupt) 特性を評価済み

- 30krad(Si) まで、吸収線量 (TID) 特性を評価済み

- 宇宙用強化プラスチック (宇宙用 EP):

- ASTM E595 アウトガス仕様に適合

- VID (Vendor Item Drawing) V62/22608

- 軍用温度範囲:-55℃~125℃

- 単一の製造、アセンブリ、テスト施設

- 金ボンド・ワイヤ、NiPdAu リード仕上げ

- ウェハー・ロットをトレース可能

- 長い製品ライフ・サイクル

- 長期にわたる製品変更通知

- 広い電源電圧範囲:

- VA:2.7V~5.25V

- $V_D: 2.7V \sim V_A$

- SPI<sup>™</sup>、QSPI<sup>™</sup>、MICROWIRE<sup>®</sup>、DSP 互換

- 変換レート:50kSPS~1MSPS

- DNL:+1.8LSB~-0.99LSB (最大値)

- INL:+1.6LSB~-1.6LSB (最大値)

- 消費電力:

- 3V 電源:2.7mW (標準値)

- 5V 電源:11mW (標準値)

# 2 アプリケーション

- 衛星用電源システム (EPS)

- コマンドとデータの処理 (C&DH)

- 光学画像処理のペイロード

- 電圧、電流、温度の監視

- アクセラレータ

# 3 概要

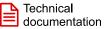

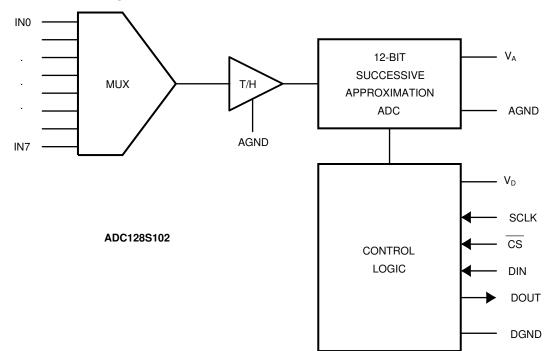

ADC128S102-SEP は、50kSPS~1MSPS の変換スル ープット・レートに対応した低消費電力、8 チャネル、 CMOS、12 ビット A/D コンバータ (ADC) です。 本コンバ ータは逐次比較型 (SAR) のアーキテクチャを採用してお り、トラック・アンド・ホールド回路を内蔵しています。INO~ IN7 の入力で最大 8 つの入力信号を受け取るように構成 できます。

出力のシリアル・データはストレート・バイナリで、SPI、 QSPI、MICROWIRE などいくつかの標準に加えて、多く の一般的な DSP シリアル・インターフェイスと互換性があ ります。

ADC128S102-SEP は、独立したアナログ電源とデジタル 電源で動作できます。アナログ電源 (VA) は 2.7V~ 5.25V、デジタル電源 (V<sub>D</sub>) は 2.7V~V<sub>A</sub> に対応できま す。3V 電源または 5V 電源による通常動作の消費電力 は、それぞれ 2.3mW、10.7mW です。パワー・ダウン機 能により、消費電力は 3V 電源で 16.5µW、5V 電源で 30µW に低減されます。

#### 製品情報(1)

| 部品番号           | パッケージ      | 本体サイズ (公称)      |

|----------------|------------|-----------------|

| ADC128S102-SEP | TSSOP (16) | 5.00mm × 4.40mm |

利用可能なパッケージについては、このデータシートの末尾にあ (1)る注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 | 特長1                                   |

|---|---------------------------------------|

| 2 | アプリケーション1                             |

| 3 | 概要1                                   |

| 4 | Revision History2                     |

| 5 | Pin Configuration and Functions       |

| 6 | Specifications4                       |

|   | 6.1 Absolute Maximum Ratings4         |

|   | 6.2 ESD Ratings 4                     |

|   | 6.3 Recommended Operating Conditions4 |

|   | 6.4 Thermal Information5              |

|   | 6.5 Electrical Characteristics        |

|   | 6.6 Timing Requirements8              |

|   | 6.7 Switching Characteristics         |

|   | 6.8 Timing Diagrams9                  |

|   | 6.9 Typical Characteristics10         |

| 7 | Detailed Description15                |

|   | 7.1 Overview15                        |

|   | 7.2 Functional Block Diagram15        |

|   | 7.3 Feature Description15             |

|   | 7.4 Device Functional Modes17         |

| 7.5 Programming                                       | . 18 |

|-------------------------------------------------------|------|

| 8 Application and Implementation                      | . 20 |

| 8.1 Application Information                           |      |

| 8.2 Typical Application                               |      |

| 9 Power Supply Recommendations                        |      |

| 9.1 Power-Supply Sequence                             |      |

| 9.2 Power Management                                  |      |

| 9.3 Power-Supply Noise Considerations                 |      |

| 10 Layout                                             |      |

| 10.1 Layout Guidelines                                |      |

| 10.2 Layout Example                                   |      |

| 11 Device and Documentation Support                   |      |

| 11.1 Receiving Notification of Documentation Updates. |      |

| <b>11.2</b> サポート・リソース                                 |      |

| 11.3 Trademarks                                       |      |

| 11.4 Electrostatic Discharge Caution                  |      |

| 11.5 Glossary                                         |      |

| 12 Mechanical, Packaging, and Orderable               |      |

| Information                                           | .24  |

| 12.1 Engineering Samples                              |      |

| g                                                     |      |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| C | hanges from Revision * (December 2021) to Revision A (April 2022) | Page |

|---|-------------------------------------------------------------------|------|

| • | ドキュメントのステータスを事前情報から量産データに変更                                       | 1    |

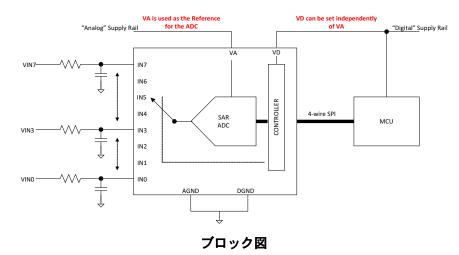

# **5** Pin Configuration and Functions

## 図 5-1. PW Package, 16-Pin TSSOP (Top View)

#### 表 5-1. Pin Functions

| PIN |                | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                      |  |

|-----|----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME           | ITPE   | DESCRIPTION                                                                                                                                                                                                                                                      |  |

| 1   | CS             | IN     | Chip select. On the falling edge of $\overline{CS}$ , a conversion process begins. Conversions continue as long as $\overline{CS}$ is held low.                                                                                                                  |  |

| 2   | VA             | Supply | Positive analog supply pin. This voltage is also used as the reference voltage. Connect this pin to a quiet 2.7-V to 5.25-V source and bypass this pin to GND with $1-\mu F$ and $0.1-\mu F$ monolithic ceramic capacitors located within 1 cm of the power pin. |  |

| 3   | AGND           | Supply | The ground return for the analog supply and signals.                                                                                                                                                                                                             |  |

| 4   | IN0            | IN     | Analog input. This signal can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                               |  |

| 5   | IN1            | IN     | Analog input. This signal can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                               |  |

| 6   | IN2            | IN     | Analog input. This signal can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                               |  |

| 7   | IN3            | IN     | Analog input. This signal can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                               |  |

| 8   | IN4            | IN     | Analog input. This signal can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                               |  |

| 9   | IN5            | IN     | Analog input. This signal can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                               |  |

| 10  | IN6            | IN     | Analog input. This signal can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                               |  |

| 11  | IN7            | IN     | Analog input. This signals can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                              |  |

| 12  | DGND           | Supply | The ground return for the digital supply and signals.                                                                                                                                                                                                            |  |

| 13  | V <sub>D</sub> | Supply | Positive digital supply pin. Connect this pin to a 2.7-V to $V_A$ supply, and bypass this pin to GND with a 0.1- $\mu$ F monolithic ceramic capacitor located within 1 cm of the power pin.                                                                      |  |

| 14  | DIN            | IN     | Digital data input. The control register is loaded through this pin on rising edges of the SCLK pin.                                                                                                                                                             |  |

| 15  | DOUT           | OUT    | Digital data output. The output samples are clocked out of this pin on the falling edges of the SCLK pin.                                                                                                                                                        |  |

| 16  | SCLK           | IN     | Digital clock input. The specified performance range of frequencies for this input is 0.8 MHz to 16 MHz. This clock directly controls the conversion and readout processes.                                                                                      |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                         | MIN        | MAX                  | UNIT |

|-------------------------------------------------------------------------|------------|----------------------|------|

| Analog supply voltage (V <sub>A</sub> )                                 | -0.3       | 6.5                  | V    |

| Digital supply voltage (V <sub>D</sub> ) <sup>(2)</sup>                 | -0.3       | V <sub>A</sub> + 0.3 | V    |

| Voltage on analog input pins to AGND <sup>(2)</sup>                     | AGND – 0.3 | V <sub>A</sub> + 0.3 | V    |

| Voltage on digital input and digital output pins to DGND <sup>(2)</sup> | DGND – 0.3 | V <sub>D</sub> + 0.3 | V    |

| DGND to AGND                                                            | -0.3       | 0.3                  | V    |

| Input current at any pin                                                | -10        | 10                   | mA   |

| Package input current                                                   | -20        | 20                   | mA   |

| Power-dissipation at T <sub>A</sub> = 25°C                              |            | See <sup>(3)</sup>   |      |

| Junction temperature, T <sub>J</sub>                                    |            | 150                  | °C   |

| Storage temperature, T <sub>stg</sub>                                   | -65        | 150                  | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) The maximum voltage is not to exceed 6.5 V

(3) The absolute maximum junction temperature ( $T_Jmax$ ) for this device is 150°C. The maximum allowable power dissipation is dictated by TJmax, the junction-to-ambient thermal resistance ( $\theta_{JA}$ ), and the ambient temperature ( $T_A$ ), and can be calculated using the formula  $P_DMAX = (T_Jmax - T_A)/\theta_{JA}$ . The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided.

### 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>          | ±2000 | M    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                     | TEST CONDITIONS        | MIN | NOM | MAX            | UNIT |

|-----------------|-------------------------------|------------------------|-----|-----|----------------|------|

| VA              | Analog power supply           | V <sub>A</sub> to AGND | 2.7 | ·   | 5.25           | V    |

| V <sub>D</sub>  | Digital power supply          | V <sub>D</sub> to DGND | 2.7 | ·   | V <sub>A</sub> | V    |

| V <sub>IN</sub> | Digital input voltage         |                        | 0   | ·   | V <sub>A</sub> | V    |

| FSR             | Full-scale analog input range |                        | 0   | ·   | V <sub>A</sub> | V    |

|                 | Clock frequency               |                        | 0.8 |     | 16             | MHz  |

| T <sub>A</sub>  | Ambient temperature           |                        | -55 | 25  | 125            | °C   |

#### 6.4 Thermal Information

|                       |                                              | ADC128S102-SEP |      |

|-----------------------|----------------------------------------------|----------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP)     | UNIT |

|                       |                                              | 16 PINS        |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 110            | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 42             | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 56             | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 5              | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 55             | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### **6.5 Electrical Characteristics**

at AGND = DGND = 0 V,  $f_{SCLK}$  = 0.8 MHz to 16 MHz,  $f_{SAMPLE}$  = 50 kSPS to 1 MSPS, and  $C_L$  = 50 pF (unless otherwise noted); minimum and maximum values at  $T_A$  = -55°C to +125°C; typical values at  $T_A$  = 25°C

|                  | PARAMETER                          | TEST CONDITIONS                                                                  | MIN   | TYP  | MAX | UNIT       |

|------------------|------------------------------------|----------------------------------------------------------------------------------|-------|------|-----|------------|

| ANALOG           | INPUTS                             |                                                                                  |       |      |     |            |

| DCL              | Input leakage current              |                                                                                  | -1    |      | 1   | μA         |

| <b>`</b>         | 1                                  | Track mode                                                                       |       | 33   |     | - 5        |

| 2 <sub>IN</sub>  | Input capacitance <sup>(1)</sup>   | Hold mode                                                                        |       | 3    |     | pF         |

| DC PERF          | ORMANCE                            |                                                                                  |       |      |     |            |

|                  | Resolution                         | No missing codes                                                                 |       | 12   |     | Bits       |

|                  |                                    | $V_A = V_D = 3 V$                                                                |       | 0.5  | 1.8 |            |

| ONL              | Differential poplingerity          | $v_A = v_D = 3 v$                                                                | -0.99 | -0.3 |     | LSB        |

|                  | Differential nonlinearity          | $V_A = V_D = 5 V$                                                                |       | 0.9  | 1.7 | LOD        |

|                  |                                    | $v_A = v_D = 3 v$                                                                | -0.99 | -0.5 |     |            |

| NL               |                                    | $V_A = V_D = 3 V$                                                                | -1.6  | ±0.6 | 1.6 | LSB        |

| INL              | Integral nonlinearity              | $V_A = V_D = 5 V$                                                                | -1.5  | ±0.9 | 1.5 | LOD        |

| ,                | Innut effect error                 | $V_A = V_D = 3 V$                                                                | -2.3  | 0.8  | 2.3 |            |

| V <sub>OFF</sub> | Input offset error                 | $V_A = V_D = 5 V$                                                                | -2.3  | 1.1  | 2.3 | LSB        |

|                  | Offerstermentels                   | $V_A = V_D = 3 V$                                                                | -1.5  | ±0.1 | 1.5 |            |

| DEM              | Offset error match                 | $V_A = V_D = 5 V$                                                                | -1.5  | ±0.3 | 1.5 | LSE        |

| -0-5             | <b>F</b>                           | $V_A = V_D = 3 V$                                                                | -2.1  | 0.8  | 2.1 | 1.05       |

| SE               | Full-scale error                   | $V_A = V_D = 5 V$                                                                | -2.1  | 0.3  | 2.1 | LSE        |

|                  | E                                  | $V_A = V_D = 3 V$                                                                | -1.6  | ±0.1 | 1.6 | 1.05       |

| SEM              | Full-scale error match             | $V_A = V_D = 5 V$                                                                | -1.6  | ±0.3 | 1.6 | LSE        |

| AC PERF          | ORMANCE                            | 1                                                                                |       |      |     |            |

|                  |                                    | $V_A = V_D = 3 V$                                                                |       | 6.8  |     |            |

| PBW              | Full-power bandwidth               | $V_A = V_D = 5 V$                                                                |       | 10   |     | MHz        |

|                  |                                    | V <sub>A</sub> = V <sub>D</sub> = 3 V,<br>f <sub>IN</sub> = 40.2 kHz, -0.02 dBFS | 68    | 72   |     | -10        |

| SINAD            | Signal-to-noise + distortion ratio | $V_A = V_D = 5 V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , -0.02 dBFS                  | 68    | 72   |     | dB         |

|                  | Circul to point ratio              | V <sub>A</sub> = V <sub>D</sub> = 3 V,<br>f <sub>IN</sub> = 40.2 kHz, -0.02 dBFS | 68.5  | 72   |     | dD         |

| SNR              | Signal-to-noise ratio              | $V_A = V_D = 5 V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , -0.02 dBFS                  | 68    | 72   |     | dB         |

| ГНD              | Total harmonic distortion          | $V_A = V_D = 3 V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$            |       | -86  | -72 | dB         |

|                  |                                    | $V_A = V_D = 5 V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , -0.02 dBFS                  |       | -87  | -72 | чD         |

| SFDR             | Spurious free dynamic reaso        | $V_A = V_D = 3 V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$            | 75    | 91   |     | ٩D         |

| אטיינ            | Spurious-free dynamic range        | $V_A = V_D = 5 V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , -0.02 dBFS                  | 75    | 90   |     | dB         |

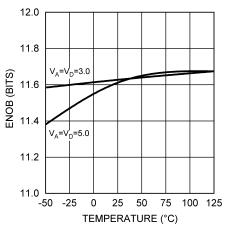

| ENOB             | Effective number of bits           | $V_A = V_D = 3 V,$<br>$f_{IN} = 40.2 \text{ kHz}, -0.02 \text{ dBFS}$            | 11.1  | 11.6 |     | Bits       |

|                  |                                    | $V_A = V_D = 5 V$ ,<br>$f_{IN} = 40.2 \text{ kHz}$ , -0.02 dBFS                  | 11    | 11.6 |     | DIIS       |

| 80               | Channel to observe instation       | $V_A = V_D = 3 V,$<br>$f_{IN} = 20 \text{ kHz}, -0.02 \text{ dBFS}$              |       | 84   |     | <b>٦</b> D |

| SO               | Channel-to-channel isolation       | $V_A = V_D = 5 V$ ,<br>f <sub>IN</sub> = 20 kHz, -0.02 dBFS                      |       | 85   |     | dB         |

# 6.5 Electrical Characteristics (continued)

at AGND = DGND = 0 V,  $f_{SCLK}$  = 0.8 MHz to 16 MHz,  $f_{SAMPLE}$  = 50 kSPS to 1 MSPS, and  $C_L$  = 50 pF (unless otherwise noted); minimum and maximum values at  $T_A$  = -55°C to +125°C; typical values at  $T_A$  = 25°C

|                                 | PARAMETER                                         | TEST CONDITIONS                                                                                                   | MIN TYP              | MAX  | UNIT |

|---------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------------|------|------|

|                                 | Intermodulation distortion,                       | V <sub>A</sub> = V <sub>D</sub> = 3 V,<br>f <sub>IN</sub> = 19.5 kHz, –0.02 dBFS                                  | -93                  | -77  |      |

| IMD                             | second order terms                                | V <sub>A</sub> = V <sub>D</sub> = 5 V,<br>f <sub>IN</sub> = 19.5 kHz, –0.02 dBFS                                  | -93                  | -77  | dB   |

| ND                              | Intermodulation distortion,                       | V <sub>A</sub> = V <sub>D</sub> = 3 V,<br>f <sub>IN</sub> = 19.5 kHz, -0.02 dBFS                                  | -91                  | -70  | uВ   |

|                                 | third order terms                                 | V <sub>A</sub> = V <sub>D</sub> = 5 V,<br>f <sub>IN</sub> = 19.5 kHz, –0.02 dBFS                                  | -91                  | -70  |      |

| DIGITAL                         | INPUTS                                            | · ·                                                                                                               |                      |      |      |

|                                 | Input high logic lovel                            | $V_{A} = V_{D} = 2.7 \text{ V to } 3.6 \text{ V}$                                                                 | 2.1                  |      | V    |

| V <sub>IH</sub>                 | Input high logic level                            | $V_{A} = V_{D} = 4.75 \text{ V} \text{ to } 5.25 \text{ V}$                                                       | 2.4                  |      | v    |

| VIL                             | Input low logic level                             | V <sub>A</sub> = V <sub>D</sub> = 2.7 V to 5.25 V                                                                 |                      | 0.8  | V    |

|                                 | Input current                                     | $V_{IN} = 0 V \text{ or } V_D$                                                                                    | ±0.01                | ±2   | μA   |

|                                 | Digital input capacitance <sup>(1)</sup>          |                                                                                                                   |                      | 3.5  | pF   |

| DIGITAL                         | OUTPUTS                                           |                                                                                                                   |                      | I    |      |

|                                 | Output format                                     |                                                                                                                   | Straight binary      |      |      |

| V <sub>OH</sub>                 | Output high logic level                           | I <sub>SOURCE</sub> = 200 μA,<br>V <sub>A</sub> = V <sub>D</sub> = 2.7 V to 5.25 V                                | V <sub>D</sub> - 0.5 |      | V    |

| V <sub>OL</sub>                 | Output low logic level                            | $I_{SOURCE} = 200 \ \mu A \text{ to } 1 \ \text{mA},$<br>$V_A = V_D = 2.7 \ \text{V} \text{ to } 5.25 \ \text{V}$ |                      | 0.4  | V    |

|                                 | Hiigh-impedance output leakage current            | V <sub>A</sub> = V <sub>D</sub> = 2.7 V to 5.25 V                                                                 | ±0.01                | ±1   | μA   |

|                                 | Hiigh-impedance output capacitance <sup>(1)</sup> |                                                                                                                   |                      | 3.5  | pF   |

| POWER                           | SUPPLY                                            |                                                                                                                   |                      |      |      |

|                                 | Total supply current,                             | $V_A = V_D = 2.7 V \text{ to } 3.6 V$<br>$f_{SAMPLE} = 1 \text{ MSPS}, f_{IN} = 40 \text{ kHz}$                   | 0.9                  | 1.5  |      |

|                                 | normal mode (CS low)                              | $V_A = V_D = 4.75 V \text{ to } 5.25 V$<br>$f_{SAMPLE} = 1 \text{ MSPS}, f_{IN} = 40 \text{ kHz}$                 | 2.2                  | 3.2  | mA   |

| I <sub>A</sub> + I <sub>D</sub> | Total supply current,                             | V <sub>A</sub> = V <sub>D</sub> = 2.7 V to 3.6 V<br>f <sub>SAMPLE</sub> = 0 kSPS                                  | 5.5                  | 50   |      |

|                                 | shutdown mode (CS high)                           | V <sub>A</sub> = V <sub>D</sub> = 4.75 V to 5.25 V<br>f <sub>SAMPLE</sub> = 0 kSPS                                | 6                    | 70   | μA   |

| P <sub>C</sub>                  | Power consumption,                                | $V_A = V_D = 3 V$<br>$f_{SAMPLE} = 1 MSPS$ , $f_{IN} = 40 \text{ kHz}$                                            | 2.7                  | 4.5  | mW   |

|                                 | normal mode (CS low)                              | $V_A = V_D = 5 V$<br>$f_{SAMPLE} = 1 MSPS, f_{IN} = 40 \text{ kHz}$                                               | 11                   | 15.5 | 1117 |

| С                               | Power consumption,                                | V <sub>A</sub> = V <sub>D</sub> = 3 V<br>f <sub>SAMPLE</sub> = 0 kSPS                                             | 16.5                 | 150  | μW   |

|                                 | shutdown mode (CS high)                           | V <sub>A</sub> = V <sub>D</sub> = 5 V<br>f <sub>SAMPLE</sub> = 0 kSPS                                             | 30                   | 350  | μvv  |

(1) This parameter is specified by design and/or characterization and is not tested in production.

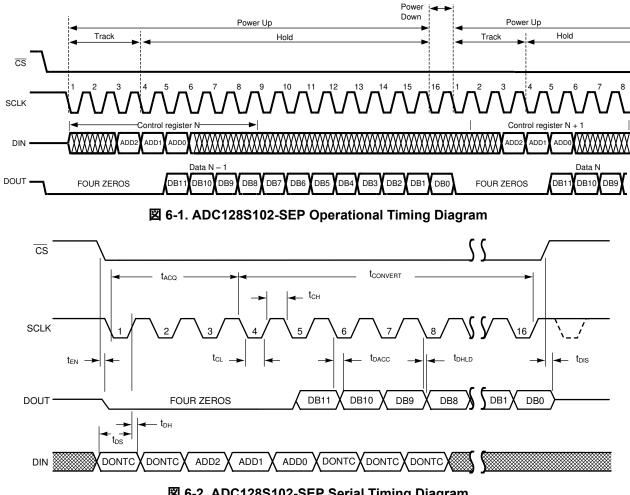

#### 6.6 Timing Requirements

at  $V_A = V_D = 2.7$  V to 5.25 V, AGND = DGND = 0 V,  $f_{SCLK} = 0.8$  MHz to 16 MHz,  $f_{SAMPLE} = 50$  kSPS to 1 MSPS, and  $C_L = 50$  pF (unless otherwise noted); minimum and maximum values at  $T_A = -55$ °C to +125°C; typical values at  $T_A = 25$ °C.

|                      |                                     |                                                         | MIN | TYP                     | MAX | UNIT |

|----------------------|-------------------------------------|---------------------------------------------------------|-----|-------------------------|-----|------|

| CONVERS              | SION CYCLE                          |                                                         |     |                         |     |      |

| f <sub>SCLK</sub>    | Serial clock frequency              | $V_{A} = V_{D} = 2.7 \text{ V to } 5.25 \text{ V}$      | 0.8 |                         | 16  | MHz  |

|                      | Serial clock duty cycle             | $V_{A} = V_{D} = 2.7 \text{ V to } 5.25 \text{ V}$      | 40% |                         | 60% |      |

| f <sub>S</sub>       | Sample rate in continuous mode      | $V_{A} = V_{D} = 2.7 \text{ V to } 5.25 \text{ V}$      | 50  |                         |     | kSPS |

| t <sub>CONVERT</sub> | Conversion (hold) time              | $V_{A} = V_{D} = 2.7 \text{ V to } 5.25 \text{ V}$      |     |                         | 13  | SCLK |

| t <sub>ACQ</sub>     | Acquisition (track) time            | $V_{A} = V_{D} = 2.7 \text{ V to } 5.25 \text{ V}$      |     |                         | 3   | SCLK |

| t <sub>CYCLE</sub>   | Throughput time                     | $(t_{CONV} + t_{ACQ})$ at $V_A = V_D = 2.7 V$ to 5.25 V |     |                         | 16  | SCLK |

| SPI INTER            | RFACE TIMINGS                       | •                                                       |     |                         |     |      |

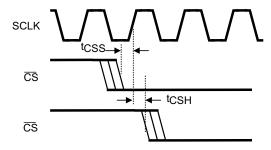

| t <sub>CSH</sub>     | CS hold time after SCLK rising edg  | е                                                       | 10  | 2                       |     | ns   |

| t <sub>CSS</sub>     | CS setup time prior to SCLK rising  | edge                                                    | 10  | 4.5                     |     | ns   |

| t <sub>DS</sub>      | DIN setup time prior to SCLK rising | l edge                                                  | 10  |                         |     | ns   |

| t <sub>DH</sub>      | DIN hold time after SCLK rising ed  | ge                                                      | 10  |                         |     | ns   |

| t <sub>CH</sub>      | SCLK high time                      |                                                         | C   | ).4 x t <sub>SCLK</sub> |     | ns   |

| t <sub>CL</sub>      | SCLK low time                       |                                                         | C   | ).4 x t <sub>SCLK</sub> |     | ns   |

### 6.7 Switching Characteristics

at  $V_A = V_D = 2.7$  V to 5.25 V, AGND = DGND = 0 V,  $f_{SCLK} = 0.8$  MHz to 16 MHz,  $f_{SAMPLE} = 50$  kSPS to 1 MSPS, and  $C_L = 50$  pF (unless otherwise noted); minimum and maximum values at  $T_A = -55^{\circ}$ C to  $+125^{\circ}$ C; typical values at  $T_A = 25^{\circ}$ C.

|                       | PARAMETER                                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |  |

|-----------------------|------------------------------------------|-----------------|-----|-----|-----|------|--|--|

| SPI INTERFACE TIMINGS |                                          |                 |     |     |     |      |  |  |

| t <sub>EN</sub>       | CS falling edge to DOUT enabled          |                 |     | 5   | 30  | ns   |  |  |

| t <sub>DACC</sub>     | DOUT access time after SCLK falling edge |                 |     | 17  | 27  | ns   |  |  |

| t <sub>DHLD</sub>     | DOUT hold time after SCLK falling edge   |                 | 7   |     |     | ns   |  |  |

| t                     | CS rising edge to DOUT high-impedance    | DOUT falling    |     | 2.4 | 20  | ns   |  |  |

| t <sub>DIS</sub>      | Consing edge to DOOT high-impedance      | DOUT rising     |     | 0.9 | 20  | ns   |  |  |

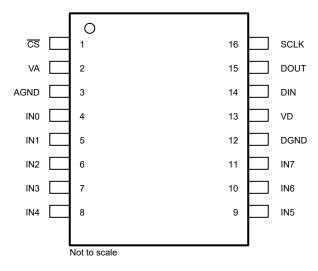

# 6.8 Timing Diagrams

6-2. ADC128S102-SEP Serial Timing Diagram

☑ 6-3. SCLK and CS Timing Parameters

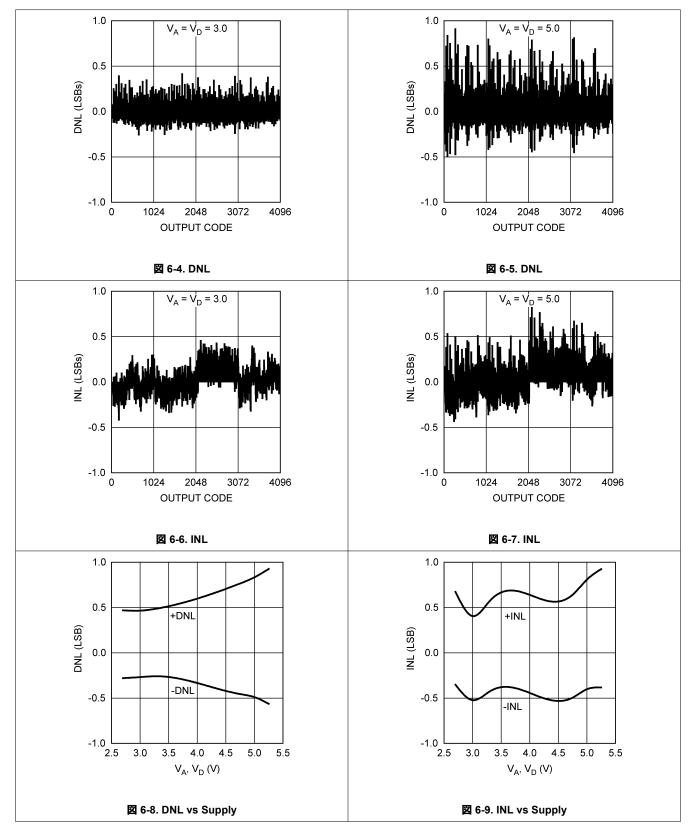

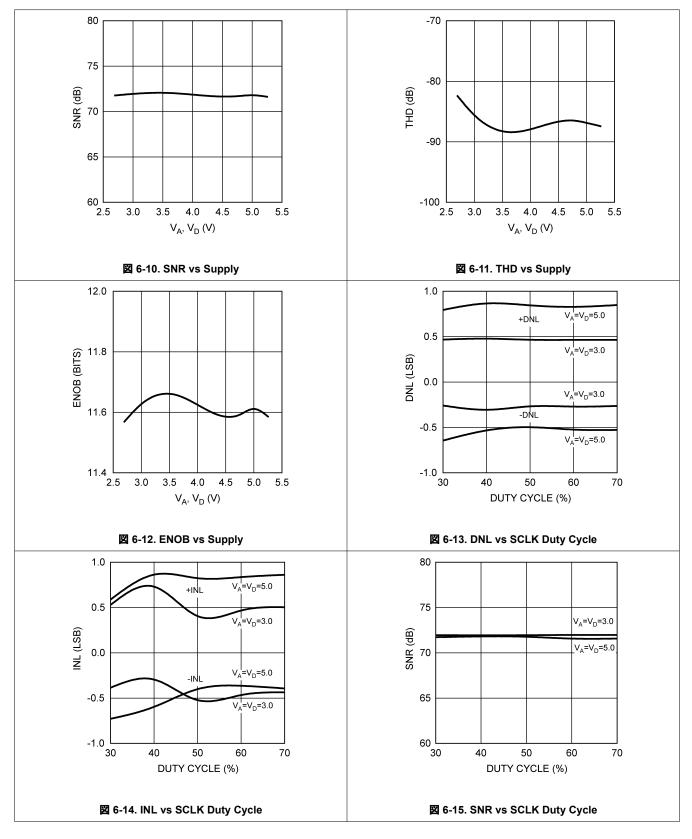

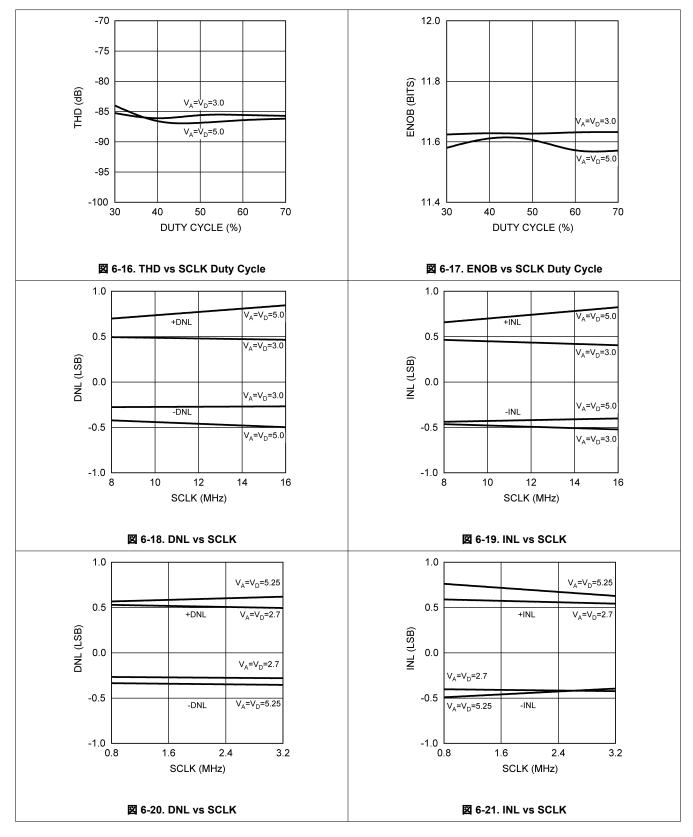

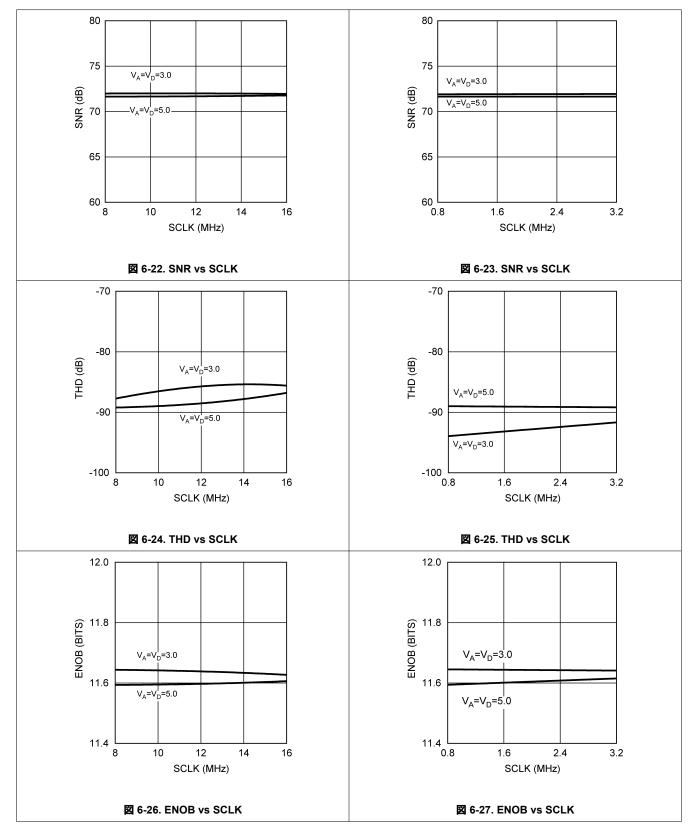

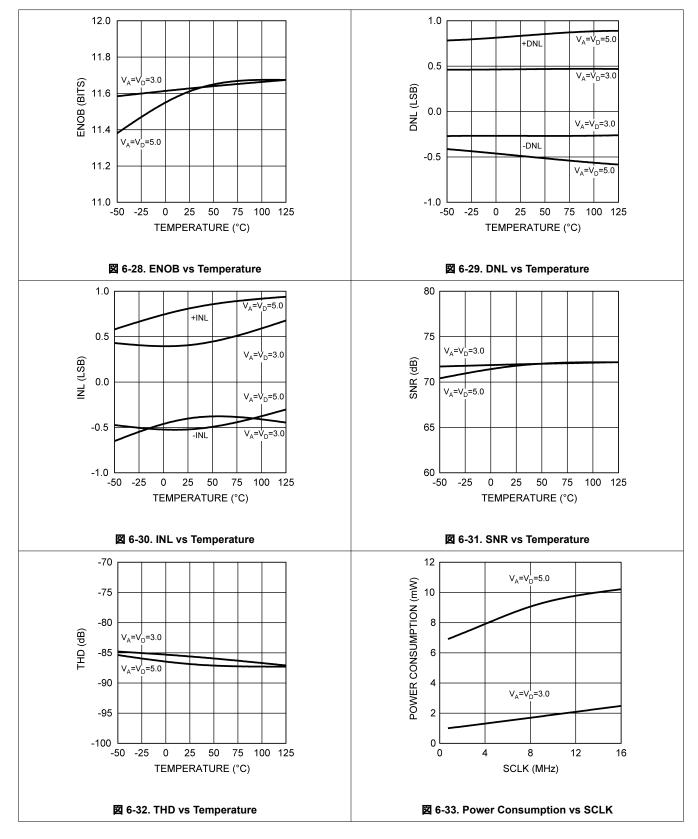

### **6.9 Typical Characteristics**

# 7 Detailed Description

### 7.1 Overview

The ADC128S102-SEP is a small, eight-channel, multiplexed, 12-bit, successive-approximation register analogto-digital converter (SAR ADC) designed around a charge redistribution digital-to-analog converter (DAC). In addition to having 8 input channels, the ADC128S102-SEP can operate at sampling rates up to 1 MSPS.

The device provides an SPI-compatible serial interface.

#### 7.2 Functional Block Diagram

# 7.3 Feature Description

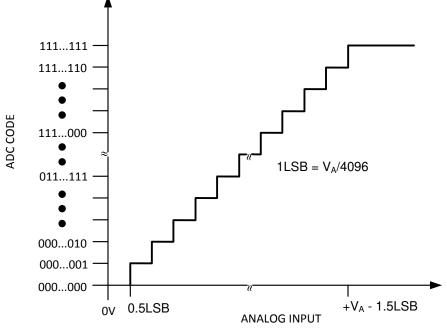

#### 7.3.1 ADC128S102-SEP Transfer Function

The output format of the ADC128S102-SEP is straight binary. Code transitions occur midway between successive integer LSB values. The LSB width for the ADC128S102-SEP is  $V_A$  / 4096.  $\boxtimes$  7-1 illustrates the ideal transfer characteristic. The transition from an output code of 0000 0000 0000 to a code of 0000 0000 0001 is at 1/2 LSB, or a voltage of  $V_A$  / 8192. Other code transitions occur at steps of one LSB.

図 7-1. Ideal Transfer Characteristic

#### 7.3.2 Analog Inputs

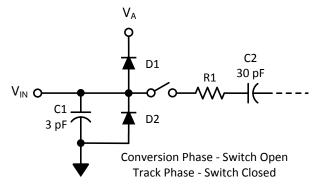

⊠ 7-2 shows an equivalent circuit for one of the input channels of the ADC128S102-SEP. Diodes D1 and D2 provide ESD protection for the analog inputs. The operating range for the analog inputs is 0 V to  $V_A$ . Going beyond this range causes the ESD diodes to conduct and results in erratic operation.

Capacitor C1 in  $\boxtimes$  7-2 has a typical value of 3 pF and is mainly the package pin capacitance. Resistor R1 is the ON-resistance of the multiplexer and track-and-hold switch and is typically 500  $\Omega$ . Capacitor C2 is the ADC128S102-SEP sampling capacitor, and is typically 30 pF. The ADC128S102-SEP delivers best performance when driven by a low-impedance source (less than 100  $\Omega$ ). This source is especially important when using the ADC128S102-SEP to sample dynamic signals. Also important when sampling dynamic signals is a band-pass or low-pass filter, which reduces harmonics and noise in the input. These filters are often referred to as antialiasing filters.

#### 7.3.3 Digital Inputs and Outputs

The digital inputs of the ADC128S102-SEP (SCLK,  $\overline{CS}$ , and DIN) have an operating range of 0 V to V<sub>A</sub>. The inputs are not prone to latch-up and can be asserted before the digital supply (V<sub>D</sub>) without any risk. The digital output (DOUT) operating range is controlled by V<sub>D</sub>. The output high voltage is V<sub>D</sub> – 0.5 V (minimum) when the output low voltage is 0.4 V (maximum).

#### 7.3.4 Radiation Environments

Careful consideration must be given to environmental conditions when using a product in a radiation environment.

#### 7.3.4.1 Total Ionizing Dose

Testing and qualification of these products is done on a wafer level according to *MIL-STD-883G*, *Test Method 1019.7*. Testing is done according to condition A and the extended room temperature anneal test described in section 3.11 for application environment dose rates less than 51.61 rad(Si)/s. Wafer level TID data are available with lot shipments.

#### 7.3.4.2 Single Event Latch-Up

One-time single event latch-up (SEL) was preformed according to EIA/JEDEC Standard, EIA/JEDEC57. The linear energy transfer threshold (LET<sub>th</sub>) shown in the # section is the maximum LET tested. A test report is available upon request.

#### 7.4 Device Functional Modes

#### 7.4.1 ADC128S102-SEP Operation

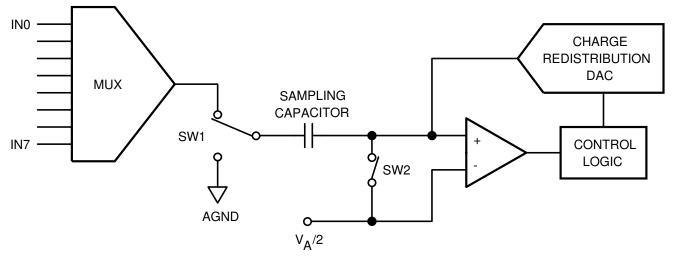

Simplified schematics of the ADC128S102-SEP in both track and hold operation are provided in  $\boxtimes$  7-3 and  $\boxtimes$  7-4, respectively. In  $\boxtimes$  7-3, the ADC128S102-SEP is in track mode: switch SW1 connects the sampling capacitor to one of eight analog input channels through the multiplexer, and SW2 balances the comparator inputs. The ADC128S102-SEP is in this state for the first three SCLK cycles after  $\overline{CS}$  is brought low.

図 7-3. ADC128S102-SEP in Track Mode

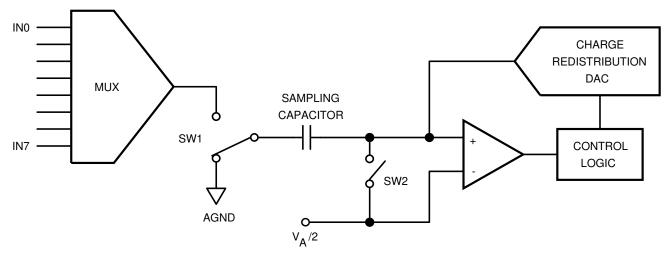

$\boxtimes$  7-4 shows the ADC128S102-SEP in hold mode: switch SW1 connects the sampling capacitor to ground, maintaining the sampled voltage, and switch SW2 unbalances the comparator. The control logic then instructs the charge-redistribution DAC to add or subtract fixed amounts of charge to or from the sampling capacitor until the comparator is balanced. When the comparator is balanced, the digital word supplied to the DAC is the digital representation of the analog input voltage. The ADC128S102-SEP is in this state for the last 13 SCLK cycles after  $\overline{CS}$  is brought low.

図 7-4. ADC128S102-SEP in Hold Mode

### 7.5 Programming

#### 7.5.1 Serial Interface

An operational timing diagram and a serial interface timing diagram for the ADC128S102-SEP are illustrated in the *Timing Diagrams* section.  $\overline{CS}$ , chip select, initiates conversions and frames the serial data transfers. SCLK (serial clock) controls both the conversion process and the timing of serial data. DOUT is the serial data output pin, where a conversion result is sent as a serial data stream, MSB first. Data to be written to the control register are placed on DIN, the serial data input pin. New data are written to DIN with each conversion.

A serial frame is initiated on the falling edge of  $\overline{CS}$  and ends on the rising edge of  $\overline{CS}$ . Each frame must contain an integer multiple of 16 rising SCLK edges. The ADC DOUT pin is in a high-impedance state when  $\overline{CS}$  is high and is active when  $\overline{CS}$  is low.  $\overline{CS}$  is asynchronous and therefore functions as an output enable. Similarly, SCLK is internally gated off when  $\overline{CS}$  is brought high.

During the first three SCLK cycles, the ADC is in track mode, acquiring the input voltage. For the next 13 SCLK cycles the conversion is accomplished and the data are clocked out. SCLK falling edges 1 through 4 clock out leading zeros and falling edges 5 through 16 clock out the conversion result, MSB first. If there is more than one conversion in a frame (continuous conversion mode), the ADC re-enters track mode on the SCLK falling edge after the N × 16th SCLK rising edge and re-enters the hold/convert mode on the N × 16 + 4th SCLK falling edge. *N* is an integer value.

The ADC128S102-SEP enters track mode under three different conditions. In  $\boxtimes$  6-1,  $\overline{CS}$  goes low with SCLK high and the ADC enters track mode on the first SCLK falling edge. In the second condition,  $\overline{CS}$  goes low with SCLK low. Under this condition, the ADC automatically enters track mode and the  $\overline{CS}$  falling edge is taken as the first SCLK falling edge. In the third condition,  $\overline{CS}$  and SCLK go low simultaneously and the ADC enters track mode. Although there is no timing restriction with respect to the falling edges of  $\overline{CS}$  and SCLK, see  $\boxtimes$  6-3 for setup and hold time requirements for the  $\overline{CS}$  falling edge with respect to the SCLK rising edge.

During each conversion, data are clocked into a control register through the DIN pin on the first eight SCLK rising edges after the fall of  $\overline{CS}$ . As given in  $\frac{1}{8}$  7-1,  $\frac{1}{8}$  7-2, and  $\frac{1}{8}$  7-3, the control register is loaded with data indicating the input channel to be converted on the subsequent conversion.

Although the ADC128S102-SEP can acquire the input signal to full resolution in the first conversion immediately following power up, the first conversion result after power up is that of a randomly selected channel. Therefore, incorporate a dummy conversion to set the required channel to be used on the subsequent conversion.

#### 表 7-1. Control Register Bits

| BIT 7 (MSB) | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| DONTC       | DONTC | ADD2  | ADD1  | ADD0  | DONTC | DONTC | DONTC |

| BIT           | SYMBOL | DESCRIPTION                                                                                               |

|---------------|--------|-----------------------------------------------------------------------------------------------------------|

| 7, 6, 2, 1, 0 | DONTC  | Don't care. The values of these bits do not affect the device.                                            |

| 5             | ADD2   | These three bits determine which input channel is sampled and converted at the next conversion cycle. The |

| 4             | ADD1   | mapping between codes and channels is given in 表 7-3.                                                     |

| 3             | ADD0   |                                                                                                           |

#### 表 7-2. Control Register Bit Descriptions

| ADD0 0 1 | INPUT CHANNEL<br>INO |

|----------|----------------------|

| 0        | INO                  |

| 1        |                      |

|          | IN1                  |

| 0        | IN2                  |

| 1        | IN3                  |

| 0        | IN4                  |

| 1        | IN5                  |

| 0        | IN6                  |

| 1        | IN7                  |

|          | 1                    |

#### 表 7-3. Input Channel Selection

### 8 Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 8.1 Application Information

The ADC128S102-SEP is a low-power, eight-channel, 12-bit ADC with specified performance specifications from 50 kSPS to 1 MSPS. The ADC128S102-SEP can be used at sample rates below 50 kSPS by powering the device down (deasserting  $\overline{CS}$ ) in between conversions. The *Electrical Characteristics* table highlights the clock frequency where ADC performance is specified. There is no limitation on periods of time for shutdown between conversions.

#### 8.2 Typical Application

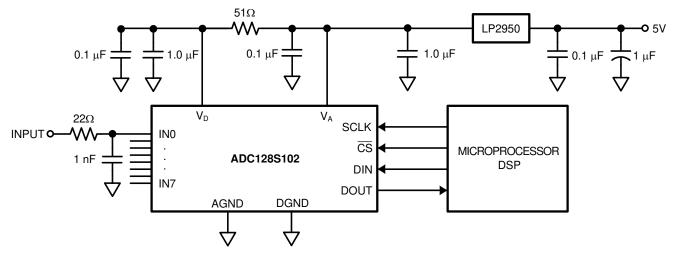

⊠ 8-1 shows a typical application block diagram. The split analog and digital supply pins are both powered in this example by the Texas Instruments' LP2950-N low-dropout voltage regulator. The analog supply is bypassed with a capacitor network located close to the ADC128S102-SEP. The digital supply is separated from the analog supply by an isolation resistor and bypassed with additional capacitors. The ADC128S102-SEP uses the analog supply ( $V_A$ ) as its reference voltage; thus,  $V_A$  must be kept as clean as possible. Because of the low power requirements of the ADC128S102-SEP, a precision reference can also be used as a power supply.

図 8-1. Typical Application Circuit

#### 8.2.1 Design Requirements

A positive-supply-only data acquisition (DAQ) system is capable of digitizing up to eight single-ended input signals ranging from 0 V to 5 V with BW = 10 kHz and a throughput up to 500 kSPS. The ADC128S102-SEP must interface to an MCU whose supply is set at 5 V. To interface with an MCU that operates at 3.3 V or lower,  $V_A$  and  $V_D$  must be separated and care must be taken to ensure that  $V_A$  is powered before  $V_D$ .

#### 8.2.2 Detailed Design Procedure

The signal range requirement forces the design to use a 5-V analog supply at V<sub>A</sub>, the analog supply. This requirement stems from the fact that V<sub>A</sub> is also a reference potential for the ADC. If the requirement of interfacing to the MCU changes to 3.3 V, the V<sub>D</sub> supply voltage must also change to 3.3 V. The maximum sampling rate of the ADC128S102-SEP when all channels (eight) are enabled is  $f_S = f_{SCLK} / (16 \times 8)$ .

Faster sampling rates can be achieved when fewer channels are sampled. A single channel can be sampled at the maximum rate of  $f_S$  (single) =  $f_{SCLK}$  / 16.

The  $V_A$  and  $V_D$  pins are separated by a 51- $\Omega$  resistor to minimize digital noise from corrupting the analog reference input. If additional filtering is required, the resistor can be replaced by a ferrite bead, thus achieving a second-order filter response. Further noise consideration can be provided to the SPI interface, especially when the controller MCU is capable of producing fast rising edges on the digital bus signals. Inserting small resistances in the digital signal path can help reduce ground bounce, and thus improve overall noise performance of the system. Care must be taken when the signal source is capable of producing voltages beyond  $V_A$ . In such instances, the internal ESD diodes can start conducting. The ESD diodes are not intended as input signal clamps. To provide the desired clamping action, use Schottky diodes.

#### 8.2.3 Application Curve

図 8-2. ENOB vs Temperature

## 9 Power Supply Recommendations

There are three major power supply concerns with this product: power-supply sequencing, power management, and the effect of digital supply noise on the analog supply.

#### 9.1 Power-Supply Sequence

The ADC128S102-SEP is a dual-supply device. The two supply pins share ESD resources, so care must be exercised to ensure that power is applied in the correct sequence. To avoid turning on the ESD diodes, the digital supply ( $V_D$ ) cannot exceed the analog supply ( $V_A$ ) by more than 300 mV. Therefore,  $V_A$  must ramp up before or concurrently with  $V_D$ .

#### 9.2 Power Management

The ADC128S102-SEP is fully powered up when  $\overline{CS}$  is low and is fully powered down when  $\overline{CS}$  is high, with one exception. If operating in continuous conversion mode, the ADC128S102-SEP automatically enters power-down mode between the 16th SCLK falling edge of a conversion and the 1st SCLK falling edge of the subsequent conversion (see  $\boxtimes$  6-1).

In continuous conversion mode, the ADC128S102-SEP can perform multiple conversions back to back. Each conversion requires 16 SCLK cycles and the ADC128S102-SEP performs conversions continuously as long as  $\overline{CS}$  is held low. Continuous mode offers maximum throughput.

In burst mode, throughput can be traded off for power consumption by performing fewer conversions per unit time. In other words, more time is spent in power-down mode and less time is spent in normal mode. By using this technique, very low sample rates can be achieved while still using an SCLK frequency within the electrical specifications. To calculate the power consumption ( $P_C$ ), simply multiply the fraction of time spent in normal mode ( $t_N$ ) by the normal mode power consumption ( $P_N$ ), as shown in  $\neq 1$ , and add the fraction of time spent in shutdown mode ( $t_S$ ) multiplied by the shutdown mode power consumption ( $P_S$ ).

$$P_{C} = \frac{t_{N}}{t_{N} + t_{S}} \times P_{N} + \frac{t_{S}}{t_{N} + t_{S}} \times P_{S}$$

<sup>(1)</sup>

### 9.3 Power-Supply Noise Considerations

The charging of any output load capacitance requires current from the digital supply, V<sub>D</sub>. The current pulses required from the supply to charge the output capacitance cause voltage variations on the digital supply. If these variations are large enough, they can degrade SNR and SINAD performance of the ADC. Furthermore, if the analog and digital supplies are tied directly together, the noise on the digital supply is coupled directly into the analog supply, causing greater performance degradation than noise alone causes on the digital supply. Similarly, discharging the output capacitance when the digital output goes from a logic high to a logic low dumps current into the die substrate, which is resistive. Load discharge currents cause *ground bounce* noise in the substrate that degrades noise performance if that current is large enough. The larger the output capacitance, the more current flows through the die substrate and the greater the noise coupled into the analog channel.

The first solution to keeping digital noise out of the analog supply is to decouple the analog and digital supplies from each other or use separate supplies for them. To keep noise out of the digital supply, keep the output load capacitance as small as practical. If the load capacitance is greater than 50 pF, use a 100- $\Omega$  series resistor at the ADC output, located as close to the ADC output pin as practical. This resistor limits the charge and discharge current of the output capacitance and improves noise performance. Because the series resistor and the load capacitance form a low-frequency pole, verify signal integrity when the series resistor is added.

# 10 Layout

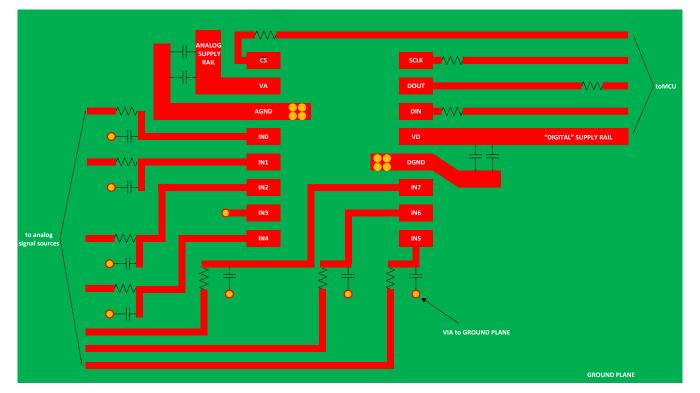

#### **10.1 Layout Guidelines**

Capacitive coupling between the noisy digital circuitry and the sensitive analog circuitry can lead to poor performance. The solution is to keep the analog circuitry separated from the digital circuitry and the clock line as short as possible.

Digital circuits create substantial supply and ground current transients. The logic noise generated can have significant impact upon system noise performance. To avoid performance degradation of the ADC128S102-SEP resulting from supply noise, do not use the same supply for the ADC128S102-SEP that is used for digital logic.

Generally, analog and digital lines cross each other at 90° to avoid crosstalk. However, to maximize accuracy in high-resolution systems, avoid crossing analog and digital lines altogether. Clock lines must be kept as short as possible and isolated from *all* other lines, including other digital lines. In addition, the clock line must be treated as a transmission line and be properly terminated.

Isolate the analog input from noisy signal traces to avoid coupling of spurious signals into the input. Any external component (for example, a filter capacitor) connected between the converter input pins and ground or to the reference input pin and ground must be connected to a very clean point in the ground plane.

Use a single, uniform ground plane and split power planes. The power planes must be located within the same board layer. Place all analog circuitry (input amplifiers, filters, reference components, and so forth) over the analog power plane. Place all digital circuitry and I/O lines over the digital power plane. Furthermore, all components in the reference circuitry and the input signal chain that are connected to ground must be connected together with short traces and enter the analog ground plane at a single, quiet point.

## 10.2 Layout Example

# 11 Device and Documentation Support

#### **11.1 Receiving Notification of Documentation Updates**

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

## 11.2 サポート・リソース

TI E2E<sup>™</sup> サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接 得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得るこ とができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 11.3 Trademarks

SPI<sup>™</sup> and QSPI<sup>™</sup> are trademarks of Motorola, Inc.. TI E2E<sup>™</sup> is a trademark of Texas Instruments. MICROWIRE<sup>®</sup> is a registered trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

#### **11.4 Electrostatic Discharge Caution**

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 11.5 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

#### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

#### **12.1 Engineering Samples**

Engineering samples are available for order and are identified by *MPR* in the orderable device name (see *Packaging Information* at the end of this document). Engineering (MPR) samples meet the performance specifications of the data sheet at room temperature only and have not received the full space production flow or testing. Engineering samples may be QCI rejects that failed tests that do not impact the performance at room temperature, such as radiation or reliability testing.

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|-------------------------------|----------------------|--------------|-------------------------|---------|

| ADC128S102PWTSEP | ACTIVE        | TSSOP        | PW                 | 16   | 250            | RoHS & Green    | NIPDAU                        | Level-2-260C-1 YEAR  | -55 to 125   | 128S102                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

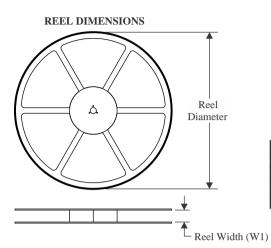

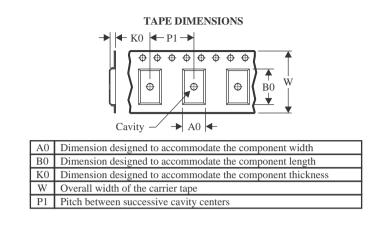

# TAPE AND REEL INFORMATION

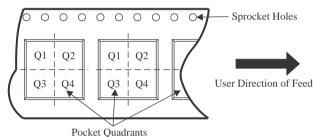

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |       |                    |    |     |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-------|--------------------|----|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | -     | Package<br>Drawing |    | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| ADC128S102PWTSEP            | TSSOP | PW                 | 16 | 250 | 178.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com

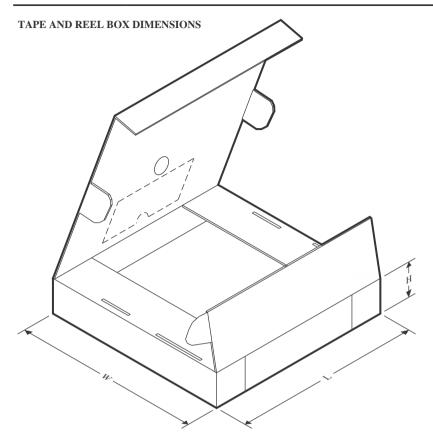

# PACKAGE MATERIALS INFORMATION

12-Dec-2023

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| ADC128S102PWTSEP | TSSOP        | PW              | 16   | 250 | 208.0       | 191.0      | 35.0        |

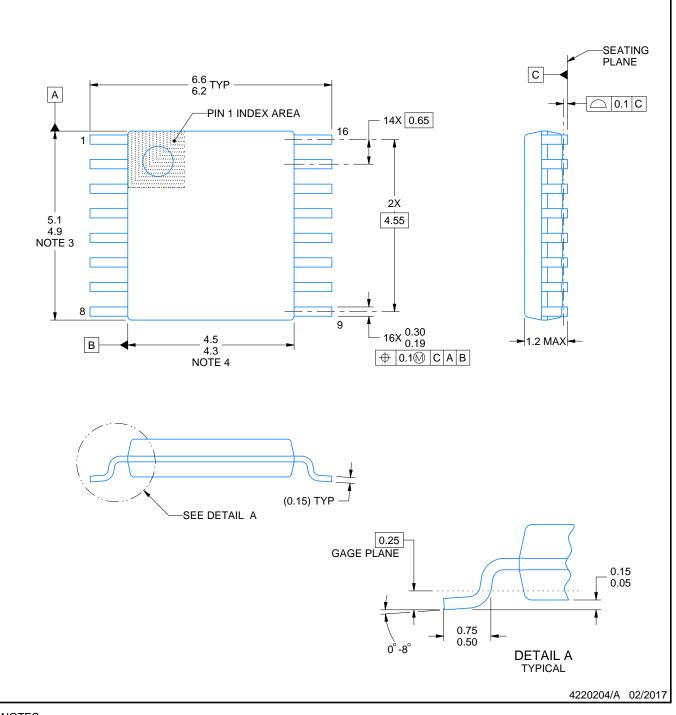

# **PW0016A**

# **PACKAGE OUTLINE**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

# PW0016A

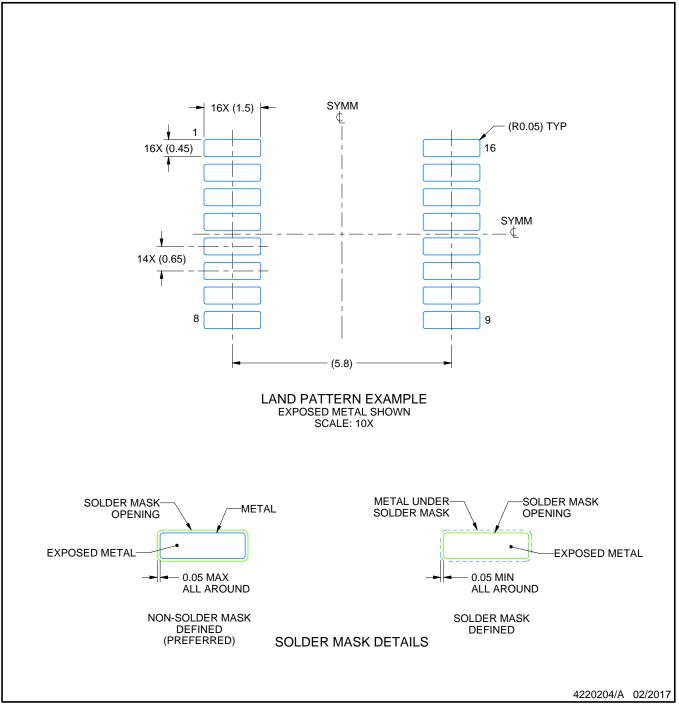

# **EXAMPLE BOARD LAYOUT**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# PW0016A

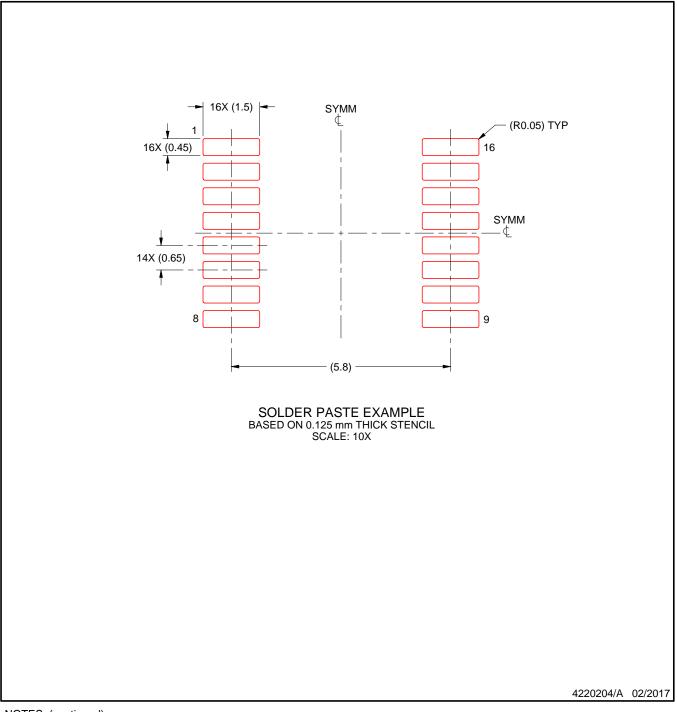

# **EXAMPLE STENCIL DESIGN**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

9. Board assembly site may have different recommendations for stencil design.

<sup>8.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要なお知らせと免責事項

TIは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや 設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供してお り、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的に かかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプ リケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載す ることは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを 自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供され ています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありま せん。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated