ADS125H01 JAJSHL9A – JUNE 2019 – REVISED JANUARY 2021

# ADS125H01 ±20V 入力、40 kSPS、24 ビット、デルタ・シグマ ADC

# 1 特長

- ±20V 入力、24 ビット・デルタ・シグマ ADC

- データ・レートをプログラム可能:2.5SPS~40kSPS

- 高電圧、入力インピーダンス 1GΩ の PGA:

- 差動入力範囲:最大 ±20V

- 差動入力範囲:最大 ±15.5V

- プログラム可能な減衰およびゲイン:

- 0.125~128

- 高性能 ADC:

- $J \prec z : 45 \text{nV}_{RMS} (f \prec z) = 128, 20 \text{SPS})$

- CMRR:105dB

- 50Hz および 60Hz 除去比:95dB

- オフセットのドリフト:10nV/℃

- ゲイン・ドリフト: 1ppm/℃

- INL:2ppm

- 搭載機能および診断能力

- オシレータ内蔵

- 信号および基準電圧モニタ

- 巡回冗長検査 (CRC)

- 電源:

- AVDD:4.75V∼5.25V

- DVDD:2.7V~5.25V

- HVDD:±5V~±18V

- 動作温度:-40℃~+125℃

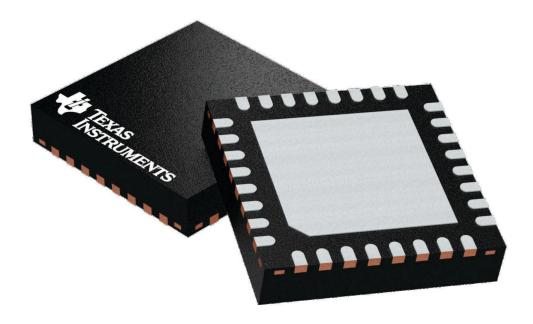

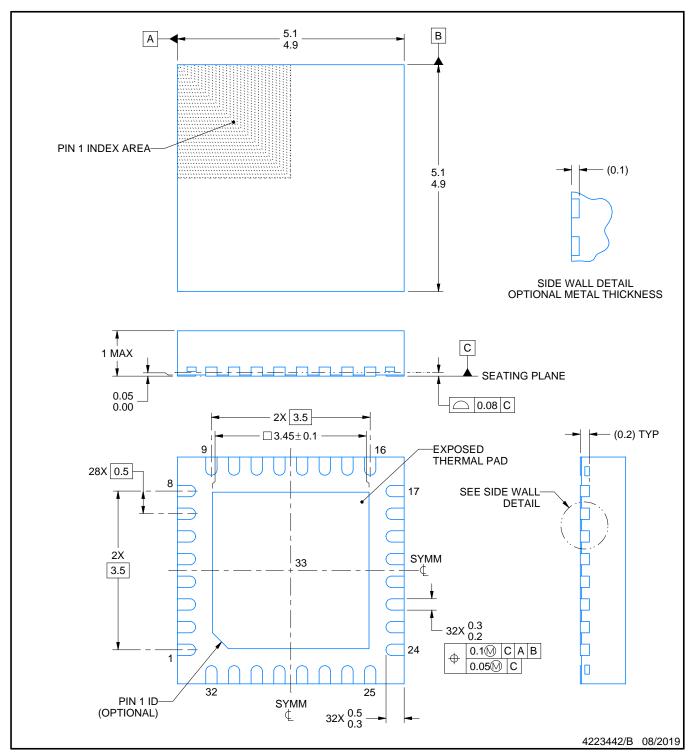

- 5mm × 5mm VQFN パッケージ

### 2 アプリケーション

- PLC アナログ入力モジュール

- 電圧 (±10V または 0V~5V)

- 電流 (4mA~20mA、シャント使用)

- データ・アクイジション (DAQ)

- 高い同相電圧入力

- ハイサイド電流測定

- バッテリ試験装置

## 3 概要

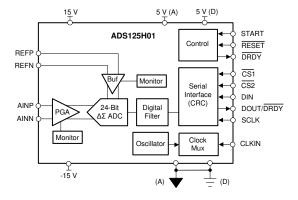

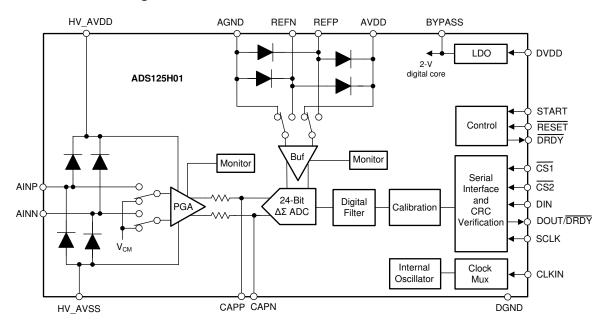

ADS125H01 は ±20V 入力、24 ビットのデルタ・シグマ (ΔΣ) アナログ/デジタル・コンバータ (ADC) であり、低ノイズ・プログラマブル・ゲイン・アンプ (PGA)、クロック発振器、信号およびリファレンス・アウトオブレンジ・モニタを搭載しています。

広い入力範囲の ±18V 電源 PGA と ADC を 1 つのパッケージに統合しているため、ディスクリート・ソリューションよりも基板面積を最大 50% 削減できます。

ゲインを 0.125~128 の範囲でプログラム可能 (±20 V~±20mV の等価な入力範囲に対応) なので、外部アッテネータや外部ゲイン段が不要です。入力インピーダンスが1GΩ 以上であるため、センサの負荷による誤差を低減できます。また、低ノイズ・低ドリフトであるため、高い同相電圧の影響を受ける歪みゲージ・ブリッジや熱電対センサに直接接続できます。

デジタル・フィルタは、2.5SPS~40kSPS の広い範囲にわたってプログラム可能です。50SPS 以下または 60SPS 以下のデータ・レートについて、50Hz および 60Hz のライン・サイクル・ノイズを減衰させることにより、測定誤差を低減できます。ほとんどのデータ・レートでは、フィルタはレイテンシなしの変換データを提供し、外部チャネルのシーケンシング時に高いデータ・スループットを実現します。

ADS125H01 は 5mm × 5mm VQFN パッケージで供給 され、-40℃~+125℃の温度範囲で仕様が規定されてい ます。

## デバイス情報(1)

| 部品番号      | パッケージ     | 本体サイズ (公称)      |

|-----------|-----------|-----------------|

| ADS125H01 | VQFN (32) | 5.00mm × 5.00mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

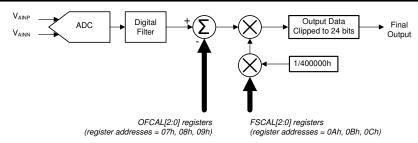

機能ブロック図

## **Table of Contents**

| <b>1</b> 特長 1                         | 9.4 Device Functional Modes               | 31              |

|---------------------------------------|-------------------------------------------|-----------------|

| <b>2</b> アプリケーション1                    |                                           | 37              |

| 3 概要1                                 |                                           | 44              |

| 4 Revision History                    | 46 4 11 41 11 1 4 41                      | <mark>56</mark> |

| 5 Device Comparison Table             |                                           | <mark>56</mark> |

| 6 Pin Configuration and Functions4    | 40 0 T!   A!:4:                           | <mark>57</mark> |

| 7 Specifications6                     |                                           | 61              |

| 7.1 Absolute Maximum Ratings          |                                           | 61              |

| 7.2 ESD Ratings6                      |                                           | 61              |

| 7.3 Recommended Operating Conditions  |                                           | 61              |

| 7.4 Thermal Information               | 40                                        | 62              |

| 7.5 Electrical Characteristics        | 40.41 10.11                               | 62              |

| 7.6 Timing Requirements               | 40.01 avant Evanania                      | 62              |

| 7.7 Switching Characteristics10       | 40 Davidas and Davidas antatian Occurrent | 64              |

| 7.8 Timing Diagrams10                 |                                           | 64              |

| 7.9 Typical Characteristics12         |                                           | 64              |

| 8 Parameter Measurement Information18 |                                           | 64              |

| 8.1 Noise Performance18               |                                           | 64              |

| 9 Detailed Description20              | ) 13.5 静電気放電に関する注意事項                      | 64              |

| 9.1 Overview                          |                                           |                 |

| 9.2 Functional Block Diagram21        | / / / / / / / / / / / / / / / / / /       |                 |

| 9.3 Feature Description22             |                                           | 64              |

| •                                     |                                           |                 |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

####

# **5 Device Comparison Table**

| FEATURE            | ADS125H01 | ADS125H02 |

|--------------------|-----------|-----------|

| Resolution         | 24 bits   | 24 bits   |

| Data rate          | 40 kSPS   | 40 kSPS   |

| Analog input pins  | 2         | 3         |

| Voltage reference  | _         | Yes       |

| Temperature sensor | _         | Yes       |

| Auto-zero mode     | _         | Yes       |

| Sinc2 filter mode  | _         | Yes       |

| GPIO pins          | _         | 4         |

| Current sources    | _         | 2         |

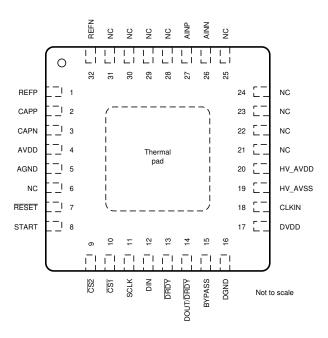

# **6 Pin Configuration and Functions**

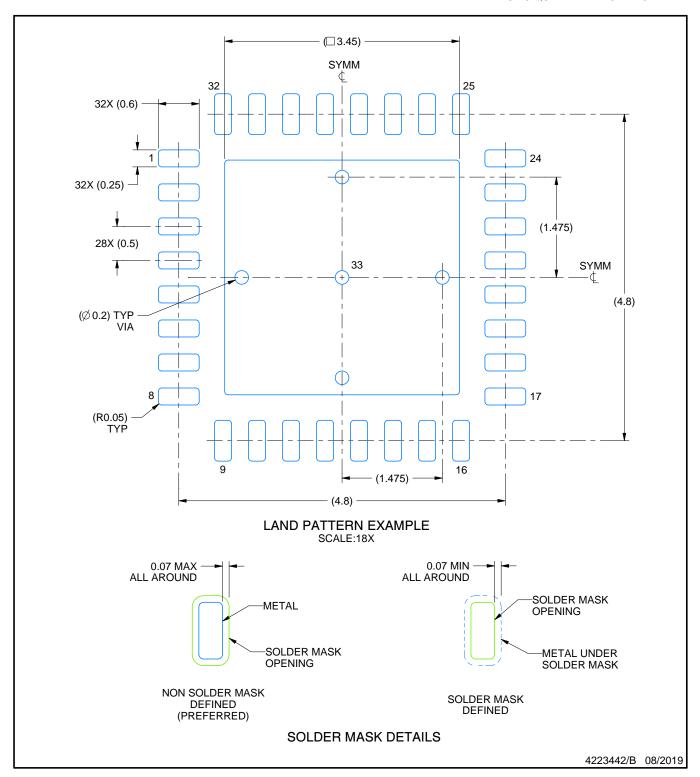

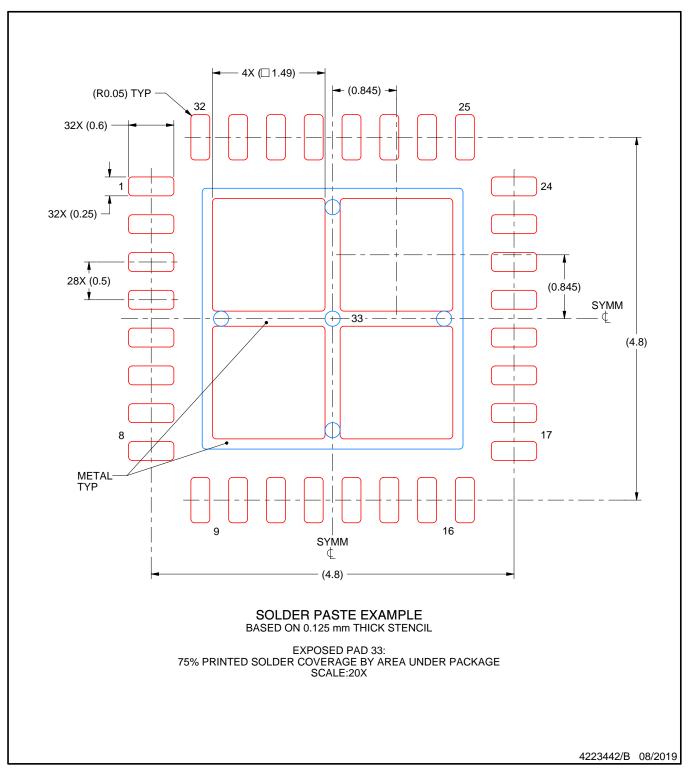

図 6-1. RHB Package, 32-Pin VQFN, Top View

表 6-1. Pin Functions

| NO.     | NAME      | I/O            | DESCRIPTION                                                             |

|---------|-----------|----------------|-------------------------------------------------------------------------|

| 1       | REFP      | Analog input   | Positive reference input                                                |

| 2       | CAPP      | Analog output  | PGA output P; connect a 1-nF C0G dielectric capacitor from CAPP to CAPN |

| 3       | CAPN      | Analog output  | PGA output N; connect a 1-nF C0G dielectric capacitor from CAPP to CAPN |

| 4       | AVDD      | Analog         | Low-voltage analog power supply                                         |

| 5       | AGND      | Analog         | Analog ground; connect to the ADC ground plane                          |

| 6       | NC        | _              | No connection; electrically float or tie to AGND                        |

| 7       | RESET     | Digital input  | Reset; active low                                                       |

| 8       | START     | Digital input  | Conversion start, active high                                           |

| 9       | CS2       | Digital input  | Serial interface chip-select 2 to select the PGA for communication      |

| 10      | CS1       | Digital input  | Serial interface chip-select 1 to select the ADC for communication      |

| 11      | SCLK      | Digital input  | Serial interface shift clock                                            |

| 12      | DIN       | Digital input  | Serial interface data input                                             |

| 13      | DRDY      | Digital output | Data ready; active low                                                  |

| 14      | DOUT/DRDY | Digital output | Serial interface data output or data-ready output, active low           |

| 15      | BYPASS    | Analog output  | 2-V subregulator output; connect a 1-µF capacitor to DGND               |

| 16      | DGND      | Digital        | Digital ground; connect to the ADC ground plane                         |

| 17      | DVDD      | Digital        | Digital power supply                                                    |

| 18      | CLKIN     | Digital input  | External clock input; connect to DGND for internal oscillator operation |

| 19      | HV_AVSS   | Analog         | High-voltage negative analog power supply                               |

| 20      | HV_AVDD   | Analog         | High-voltage positive analog power supply                               |

| 21 – 25 | NC        | _              | No connection; electrically float or tie to AGND                        |

| 26      | AINN      | Analog input   | Negative analog input                                                   |

| 27      | AINP      | Analog input   | Positive analog input                                                   |

# 表 6-1. Pin Functions (continued)

| NO.          | NAME | I/O          | DESCRIPTION                                                                                           |

|--------------|------|--------------|-------------------------------------------------------------------------------------------------------|

| 28 – 31      | NC   | _            | No connection; electrically float or tie to AGND                                                      |

| Thermal padE |      | Analog input | Negative reference input                                                                              |

|              |      | _            | Exposed thermal pad; connect to DGND; see the recommended PCB land pattern at the end of the document |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

see (1)

|                       |                                                            | MIN           | MAX           | UNIT |

|-----------------------|------------------------------------------------------------|---------------|---------------|------|

|                       | HV_AVDD to HV_AVSS                                         | -0.3          | 38            |      |

|                       | HV_AVSS to AGND                                            | -19           | 0.3           |      |

| Power-supply voltage  | AVDD to AGND                                               | -0.3          | 6             | V    |

|                       | DVDD to DGND                                               | -0.3          | 6             |      |

|                       | AGND to DGND                                               | -0.1          | 0.1           |      |

| Analog input voltage  | AINP, AINN                                                 | HV_AVSS - 0.3 | HV_AVDD + 0.3 | V    |

| Analog input voltage  | REFP, REFN                                                 | AGND - 0.3    | AVDD + 0.3    | v    |

| Digital input voltage | CS1, CS2, SCLK, DIN, START, RESET, CLKIN, DRDY, DOUT/ DRDY | DGND - 0.3    | DVDD + 0.3    | V    |

| Input current         | Continuous <sup>(2)</sup>                                  | -10           | 10            | mA   |

| Temperature           | Junction, T <sub>J</sub>                                   |               | 150           | °C   |

| Temperature           | Storage, T <sub>stg</sub>                                  | SS to AGND    |               |      |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Input and output pins are diode-clamped to the internal power supplies. Limit the input current to 10 mA in the event the analog input voltage exceeds HV\_AVDD + 0.3 V or HV\_AVSS 0.3 V, or if the reference input exceeds AVDD + 0.3 V or AGND 0.3 V, or if the digital input voltage exceeds DVDD + 0.3 V or DGND 0.3 V.

# 7.2 ESD Ratings

|                    |                          |                                                                                | VALUE | UNIT     |

|--------------------|--------------------------|--------------------------------------------------------------------------------|-------|----------|

| V                  | Electrostatic discharge  | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V        |

| V <sub>(ESD)</sub> | Lieotrostatic discriarge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | <b>v</b> |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)

|                     |                                                 |                                     | MIN                                 | NOM                      | MAX                       | UNIT  |

|---------------------|-------------------------------------------------|-------------------------------------|-------------------------------------|--------------------------|---------------------------|-------|

| POWER               | SUPPLY                                          |                                     |                                     |                          |                           |       |

|                     |                                                 | HV_AVDD to HV_AVSS                  | 10                                  |                          | 36                        |       |

|                     | High-voltage analog power supplies              | HV_AVSS to AGND                     | -18                                 |                          | 0                         | V     |

|                     |                                                 | HV_AVDD to AGND <sup>(1)</sup>      | 5                                   |                          | 36                        |       |

|                     | Low-voltage analog power supply                 | AVDD to AGND                        | 4.75                                | 5                        | 5.25                      | V     |

|                     | Digital power supply                            | DVDD to DGND                        | 2.7                                 |                          | 5.25                      | V     |

| SIGNAL              | INPUTS                                          | 1                                   |                                     |                          |                           |       |

| V <sub>(AINx)</sub> | Absolute input voltage                          |                                     | See the PGA Operating Range section |                          |                           |       |

| V <sub>IN</sub>     | Differential input voltage range <sup>(2)</sup> | $V_{IN} = V_{AINP} - V_{AINN}$      | -20                                 | ±V <sub>REF</sub> / Gain | 20                        | V     |

| VOLTAC              | SE REFERENCE INPUTS                             | 1                                   |                                     |                          |                           |       |

| V <sub>REF</sub>    | Reference voltage input                         | $V_{REF} = V_{(REFP)} - V_{(REFN)}$ | 0.9                                 |                          | AVDD                      | V     |

| V <sub>(REFN)</sub> | Negative reference voltage                      |                                     | AGND - 0.05                         |                          | V <sub>(REFP)</sub> – 0.9 | V     |

| V <sub>(REFP)</sub> | Positive reference voltage                      |                                     | V <sub>(REFN)</sub> + 0.9           |                          | AVDD + 0.05               | V     |

| DIGITAL             | INPUTS                                          |                                     |                                     |                          |                           |       |

|                     | Input voltage                                   |                                     | DGND                                |                          | DVDD                      | V     |

| EXTERN              | NAL CLOCK <sup>(3)</sup>                        | 1                                   |                                     |                          |                           |       |

| £                   | Fraguency                                       | f <sub>DATA</sub> ≤ 25.6 kSPS       | 1                                   | 7.3728                   | 8                         | MHz   |

| f <sub>CLK</sub>    | Frequency                                       | f <sub>DATA</sub> = 40 kSPS         | 1                                   | 10.24                    | 10.75                     | IVIHZ |

|                     | Duty cycle                                      |                                     | 40%                                 |                          | 60%                       |       |

| TEMPE               | RATURE RANGE                                    | 1                                   |                                     |                          |                           |       |

| T <sub>A</sub>      | Operating ambient temperature                   |                                     | -45                                 |                          | 125                       | °C    |

- (1) HV\_AVDD can be connected to AVDD if AVDD ≥ 5 V.

- (2) The full available differential input voltage range is limited under certain conditions. See the *PGA Operating Range* section for details.

- (3) Data rates scale with clock frequency.

### 7.4 Thermal Information

|                       |                                              | ADS125H01  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN) | UNIT |

|                       |                                              | 32 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 35.2       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 19.0       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 15.8       | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 15.7       | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 8.0        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

minimum and maximum specifications apply from  $T_A = -40^{\circ}C$  to +125°C; typical specifications are at  $T_A = 25^{\circ}C$ ; all specifications are at HV\_AVDD = 15 V, HV\_AVSS = -15 V, AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 2.5$  V,  $f_{CLK} = 7.3728$  MHz, data rate = 20 SPS, and gain = 1 (unless otherwise noted)

|                   | PARAMETER                                   | TEST CONDITIONS                                         | MIN              | TYP                        | MAX              | UNIT               |

|-------------------|---------------------------------------------|---------------------------------------------------------|------------------|----------------------------|------------------|--------------------|

| ANALOG            | INPUTS                                      |                                                         |                  |                            |                  |                    |

|                   | Absolute input current                      | $V_{(AINx)} = 0 \text{ V}, T_A \le 105^{\circ}\text{C}$ | -15              | ±0.5                       | 15               | nA                 |

|                   | Absolute input current drift                |                                                         |                  | 20                         |                  | pA/°C              |

|                   | Differential input current                  | V <sub>IN</sub> = 2.5 V                                 |                  | ±0.1                       |                  | nA                 |

|                   | Differential input current drift            | V <sub>IN</sub> = 2.5 V                                 |                  | 10                         |                  | pA/°C              |

|                   | Differential input impedance                |                                                         | 1                | 20                         |                  | GΩ                 |

| PGA               |                                             |                                                         |                  |                            |                  |                    |

|                   | Gain settings                               |                                                         | 0.125, 0.1875, 0 | .25, 0.5, 1, 2, 4, 8,      | 16, 32, 64,128   | V/V                |

|                   | Antialias filter frequency                  |                                                         |                  | 230                        |                  | kHz                |

| PERFOR            | MANCE                                       |                                                         |                  |                            |                  |                    |

|                   | Resolution                                  | No missing codes                                        | 24               |                            |                  | Bits               |

| e <sub>n</sub>    | Noise performance                           | -                                                       | Se               | e the <i>Noise Perforn</i> | nance section    |                    |

| f <sub>DATA</sub> | Data rate                                   |                                                         | 2.5              |                            | 40000            | SPS                |

|                   |                                             | Gain = 0.125 to 32                                      |                  | 2                          | 10               |                    |

| INL               | Integral nonlinearity                       | Gain = 64, 128                                          |                  | 4                          | 12               | ppm <sub>FSR</sub> |

| V <sub>OS</sub>   | Offset error <sup>(4)</sup>                 | T <sub>A</sub> = 25°C                                   | -30 - 300 / Gain | ±10 + 100 / Gain           | 30 + 300 / Gain  | μV                 |

|                   |                                             | Gain = 0.125 to 8                                       |                  | 150 / Gain                 | 700 / Gain       | -                  |

|                   | Offset error drift                          | Gain = 16 to 128                                        |                  | 10                         | 50               | nV/°C              |

| GE                | Gain error <sup>(4)</sup>                   | T <sub>A</sub> = 25°C, all gains                        | -0.7%            | ±0.1%                      | 0.7%             |                    |

|                   | Gain drift                                  | All gains                                               |                  | 1                          | 4                | ppm/°C             |

| NMRR              | Normal-mode rejection ratio <sup>(1)</sup>  |                                                         | See the 50-H     | z and 60-Hz Norma          | I-Mode Rejection | section            |

|                   |                                             | Data rate = 20 SPS                                      |                  | 130                        |                  |                    |

| CMRR              | Common-mode rejection ratio <sup>(2)</sup>  | Data rate = 400 SPS                                     | 90               | 105                        |                  | dB                 |

|                   |                                             | HV_AVDD, HV_AVSS                                        |                  | 2                          | 20               |                    |

| PSRR              | Power-supply rejection ratio <sup>(3)</sup> | AVDD                                                    |                  | 20                         | 60               | μV/V               |

|                   |                                             | DVDD                                                    |                  | 5                          | 30               | ·                  |

| VOLTAGE           | E REFERENCE INPUTS                          |                                                         |                  |                            |                  |                    |

|                   | Absolute input current                      |                                                         |                  | ±250                       |                  | nA                 |

|                   | Input current vs reference voltage          |                                                         |                  | 15                         |                  | nA/V               |

|                   | Input current drift                         |                                                         |                  | 0.2                        |                  | nA/°C              |

|                   | Effective input impedance                   | Differential                                            |                  | 30                         |                  | ΜΩ                 |

| PGA MOI           | NITORS                                      |                                                         |                  |                            |                  |                    |

|                   | Input and output low threshold              |                                                         |                  | HV_AVSS + 2                |                  | V                  |

|                   | Input and output high threshold             |                                                         |                  | <br>HV_AVDD – 2            |                  | V                  |

| REFERE            | NCE MONITOR                                 |                                                         |                  |                            |                  |                    |

|                   | Low voltage threshold                       |                                                         |                  | 0.4                        | 0.6              | V                  |

| INTERNA           | AL OSCILLATOR                               | <u> </u>                                                |                  |                            |                  |                    |

|                   |                                             | f <sub>DATA</sub> ≤ 25.6 kSPS                           | -2.5%            | ±0.5%                      | 2.5%             |                    |

|                   | Accuracy                                    | f <sub>DATA</sub> = 40 kSPS                             | -3.5%            | ±0.5%                      | 3.5%             |                    |

### 7.5 Electrical Characteristics (continued)

minimum and maximum specifications apply from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are at  $T_A = 25^{\circ}\text{C}$ ; all specifications are at HV\_AVDD = 15 V, HV\_AVSS = -15 V, AVDD = 5 V, DVDD = 3.3 V,  $V_{REF} = 2.5$  V,  $f_{CLK} = 7.3728$  MHz, data rate = 20 SPS, and gain = 1 (unless otherwise noted)

|                                                | PARAMETER                       | TEST CONDITIONS               | MIN        | TYP         | MAX        | UNIT |

|------------------------------------------------|---------------------------------|-------------------------------|------------|-------------|------------|------|

| DIGITAL II                                     | NPUTS/OUTPUTS                   |                               |            |             |            |      |

| V                                              | Llimb level cutout valtage      | I <sub>OH</sub> = 1 mA        | 0.8 × DVDD |             |            |      |

| V <sub>OH</sub>                                | High-level output voltage       | I <sub>OH</sub> = 8 mA        |            | 0.75 × DVDD |            | V    |

| V                                              | Lew level output veltage        | I <sub>OL</sub> = -1 mA       |            |             | 0.2 × DVDD | V    |

| V <sub>OL</sub>                                | Low-level output voltage        | I <sub>OL</sub> = -8 mA       |            | 0.2 × DVDD  |            | V    |

| V <sub>IH</sub>                                | High-level input voltage        |                               | 0.7 × DVDD |             | DVDD       | V    |

| V <sub>IL</sub>                                | Low-level input voltage         |                               |            |             | 0.3 × DVDD | V    |

|                                                | Input hysteresis                |                               |            | 0.1         |            | V    |

|                                                | Input leakage                   |                               | -10        |             | 10         | μA   |

| POWER S                                        | UPPLY                           |                               |            |             | ,          |      |

| I <sub>HV_AVDD</sub> ,<br>I <sub>HV_AVSS</sub> | HV_AVDD, HV_AVSS supply current |                               |            | 1.1         | 1.8        | mA   |

|                                                | AVDD supply current             | f <sub>DATA</sub> ≤ 25.6 kSPS |            | 2.8         | 4.6        | mA   |

| I <sub>AVDD</sub>                              | AVDD supply current             | f <sub>DATA</sub> = 40 kSPS   |            | 3.6         |            | IIIA |

| 1                                              | DVDD cumply current             | Internal oscillator active    |            | 0.5         | 0.7        | mA   |

| I <sub>DVDD</sub>                              | DVDD supply current             | f <sub>DATA</sub> = 40 kSPS   |            | 0.7         | 1          | IIIA |

| P <sub>D</sub>                                 | Power dissipation               |                               |            | 49          | 79         | mW   |

- (1) Normal-mode rejection ratio performance is dependent on the digital filter configuration.

- (2) Common-mode rejection ratio is specified at  $f_{IN}$  = 50 Hz and 60 Hz.

- (3) Power-supply rejection ratio is specified at DC.

- (4) Offset and gain errors are reduced to the level of noise by calibration.

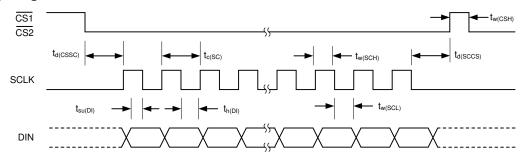

## 7.6 Timing Requirements

over operating ambient temperature range and DVDD = 2.7 V to 5.25 V (unless otherwise noted)

|                                           |                                                                                                                           | MIN | MAX | UNIT               |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------|

| SERIAL INTER                              | FACE                                                                                                                      |     | '   |                    |

| t <sub>d(CSSC)</sub>                      | Delay time, first SCLK rising edge after CS1 or CS2 falling edge                                                          | 50  |     | ns                 |

| t <sub>su(DI)</sub>                       | Setup time, DIN valid before SCLK falling edge                                                                            | 25  |     | ns                 |

| t <sub>h(DI)</sub>                        | Hold time, DIN valid after SCLK falling edge                                                                              | 25  |     | ns                 |

| t <sub>c(SC)</sub>                        | SCLK period                                                                                                               | 97  |     | ns                 |

| t <sub>w(SCH)</sub> , t <sub>w(SCL)</sub> | Pulse duration, SCLK high or low                                                                                          | 40  |     | ns                 |

| t <sub>d(SCCS)</sub>                      | Delay time, last SCLK falling edge before CS1 or CS2 rising edge                                                          | 50  |     | ns                 |

| t <sub>w(CSH)</sub>                       | Pulse duration, CS1 or CS2 high to reset interface                                                                        | 25  |     | ns                 |

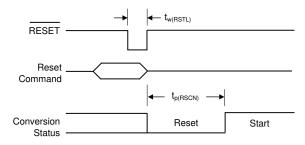

| RESET                                     |                                                                                                                           |     | '   |                    |

| t <sub>w(RSTL)</sub>                      | Pulse duration, RESET low                                                                                                 | 4   |     | 1/f <sub>CLK</sub> |

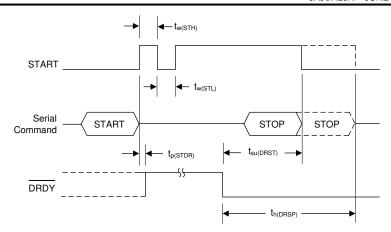

| CONVERSION                                | CONTROL                                                                                                                   |     | '   |                    |

| t <sub>w(STH)</sub>                       | Pulse duration, START high                                                                                                | 4   |     | 1/f <sub>CLK</sub> |

| t <sub>w(STL)</sub>                       | Pulse duration, START low                                                                                                 | 4   |     | 1/f <sub>CLK</sub> |

| t <sub>su(STDR)</sub>                     | Setup time, START low or STOP command before DRDY falling edge to stop the next conversion (continuous-conversion mode)   |     | 100 | 1/f <sub>CLK</sub> |

| t <sub>h(DRSP)</sub>                      | Hold time, START low or STOP command after DRDY falling edge to continue the next conversion (continuous-conversion mode) | 150 |     | 1/f <sub>CLK</sub> |

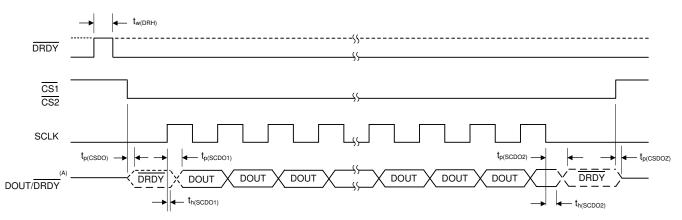

# 7.7 Switching Characteristics

over operating ambient temperature range and DVDD = 2.7 V to 5.25 V, and DOUT/ $\overline{DRDY}$  load = 20 pF || 100 k $\Omega$  to DGND (unless otherwise noted)

| PARAMETER TEST CONDITIONS MIN TYP MAX U |                                                                                 |  |     |                 |     |                    |  |

|-----------------------------------------|---------------------------------------------------------------------------------|--|-----|-----------------|-----|--------------------|--|

| SERIAL IN                               | NTERFACE                                                                        |  |     |                 |     |                    |  |

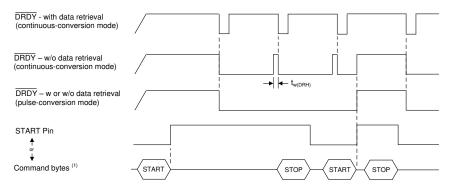

| t <sub>w(DRH)</sub>                     | Pulse duration, DRDY high                                                       |  | 16  |                 |     | 1/f <sub>CLK</sub> |  |

| t <sub>p(CSDO)</sub>                    | Propagation delay time, CS1 or CS2 falling edge to DOUT/DRDY driven             |  | 0   |                 | 50  | ns                 |  |

| t <sub>p(SCDO1)</sub>                   | Propagation delay time, SCLK rising edge to valid DOUT/DRDY                     |  |     |                 | 40  | ns                 |  |

| t <sub>h(SCDO1)</sub>                   | Hold time, SCLK rising edge to invalid DOUT/DRDY                                |  | 0   |                 |     | ns                 |  |

| t <sub>h(SCDO2)</sub>                   | Hold time, last SCLK falling edge to invalid DOUT/DRDY data output function     |  | 15  |                 |     | ns                 |  |

| t <sub>p(SCDO2)</sub>                   | Propagation delay time, last SCLK falling edge to DOUT/DRDY data-ready function |  |     |                 | 110 | ns                 |  |

| t <sub>p(CSDOZ)</sub>                   | Propagation delay time, CST or CS2 rising edge to DOUT/DRDY high impedance      |  |     |                 | 50  | ns                 |  |

| RESET                                   |                                                                                 |  |     |                 |     |                    |  |

| t <sub>p(RSCN)</sub>                    | Propagation delay time, RESET rising edge or RESET command to conversion start  |  | 512 |                 |     | 1/f <sub>CLK</sub> |  |

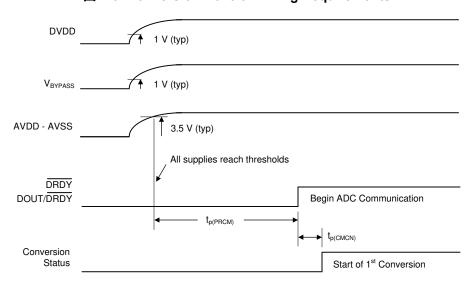

| t <sub>p(PRCM)</sub>                    | Propagation delay time, power-on threshold voltage to ADC communication         |  |     | 2 <sup>16</sup> |     | 1/f <sub>CLK</sub> |  |

| t <sub>p(CMCN)</sub>                    | Propagation delay time, ADC communication to conversion start                   |  | 512 |                 |     | 1/f <sub>CLK</sub> |  |

| CONVERS                                 | SION CONTROL                                                                    |  | •   |                 |     |                    |  |

| $t_{p(STDR)}$                           | Propagation delay time, START pin high or START command to DRDY high            |  |     |                 | 2   | 1/f <sub>CLK</sub> |  |

# 7.8 Timing Diagrams

図 7-1. Serial Interface Timing Requirements

A.  $\overline{DRDY}$  indicates the data-ready function in the interval between  $\overline{CS1}$  low and the first SCLK rising edge, and in the interval between the last SCLK falling edge of the command to  $\overline{CS1}$  high. DOUT indicates the data output function during the data read operation.

### 図 7-2. Serial Interface Switching Characteristics

図 7-3. Conversion Control Timing Requirements

図 7-4. Power-Up Characteristics

図 7-5. RESET Pin and Reset Command Timing Requirements

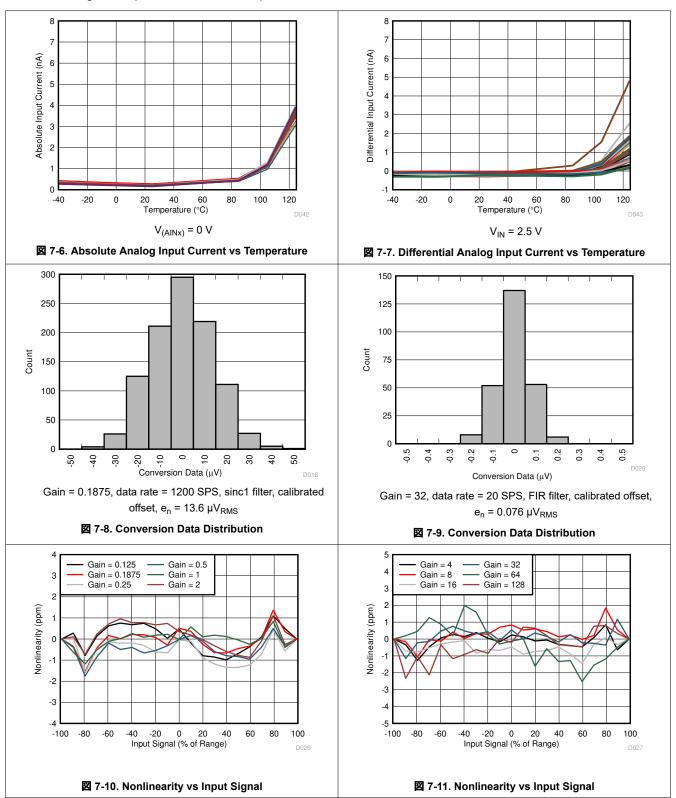

# 7.9 Typical Characteristics

at  $T_A$  = 25°C, HV\_AVDD = 15 V, HV\_AVSS = -15 V, AVDD = 5 V, DVDD = 3.3 V,  $V_{REF}$  = 2.5 V,  $f_{CLK}$  = 7.3728 MHz, data rate = 20 SPS, and gain = 1 (unless otherwise noted)

### 表 7-1. Table of Graphs

|                                     | ax 1 1. Tubic of Graphis                                                                                                                                                                                    |                                                          |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Analog Input Current                | Absolute Input Current vs Temperature, $V_{(AINX)} = 0 \text{ V}$<br>Differential Input Current vs Temperature, $V_{IN} = 2.5 \text{ V}$                                                                    | ⊠ 7-6<br>⊠ 7-7                                           |

| Noise                               | Distribution (Gain = 0.1875, Data Rate = 1.2 kSPS) Distribution (Gain = 32, Data Rate = 20 SPS)                                                                                                             | ⊠ 7-8<br>⊠ 7-9                                           |

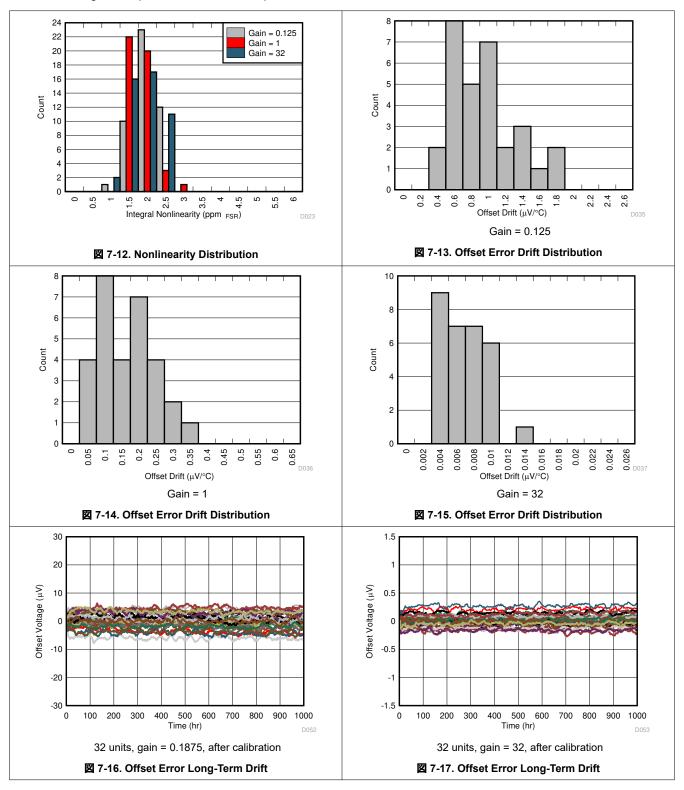

| Nonlinearity                        | vs Input Voltage (Gain = 0.125 to 2)<br>vs Input Voltage (Gain = 4 to 128)<br>Distribution (Gain = 0.125, 1, 32)                                                                                            | 図 7-10<br>図 7-11<br>図 7-12                               |

| Offset Error                        | Drift Distribution (Gain = 0.125) Drift Distribution (Gain = 1) Drift Distribution (Gain = 32) Long-Term Drift (Gain = 0.1875) Long-Term Drift (Gain = 32)                                                  | 図 7-13<br>図 7-14<br>図 7-15<br>図 7-16<br>図 7-17           |

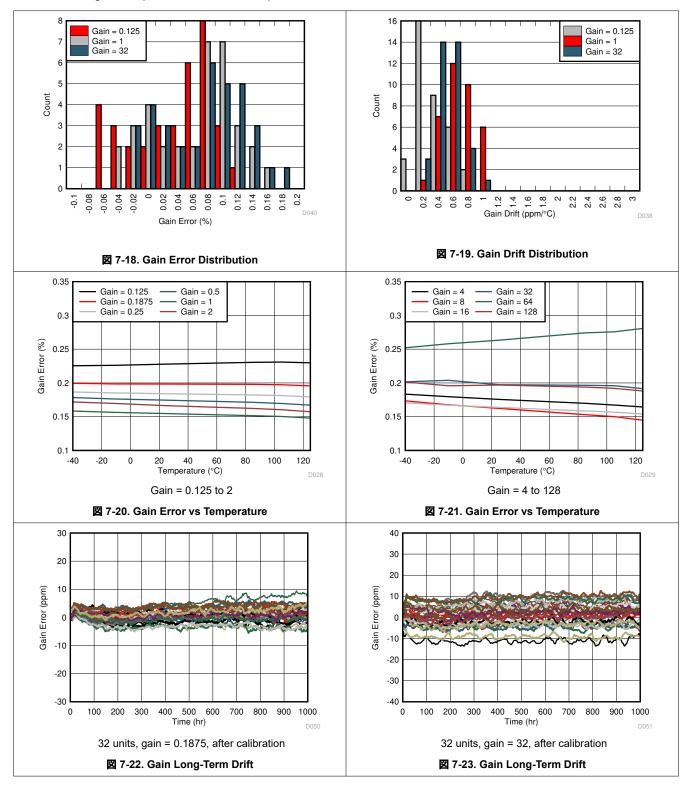

| Gain Error                          | Distribution (Gain = 0.125, 1, 32) Drift Distribution (Gain = 0.125, 1, 32) vs Temperature (Gain = 0.125 to 2) vs Temperature (Gain = 4 to 128) Long-Term Drift (Gain = 0.1875) Long-Term Drift (Gain = 32) | 図 7-18<br>図 7-19<br>図 7-20<br>図 7-21<br>図 7-22<br>図 7-23 |

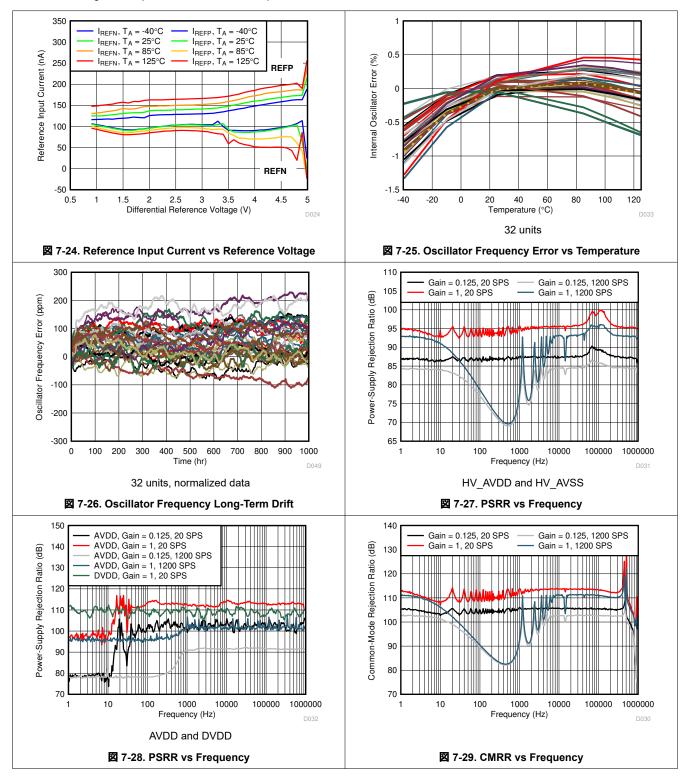

| Reference Input Current             | vs Reference Voltage (T <sub>A</sub> = -40°C, 25°C, 85°C, 125°C)                                                                                                                                            | 図 7-24                                                   |

| Oscillator Frequency Error          | vs Temperature<br>Long-Term Drift                                                                                                                                                                           | 図 7-25<br>図 7-26                                         |

| Power-Supply Rejection Ratio (PSRR) | vs Frequency (HV_AVDD and HV_AVSS) vs Frequency (AVDD and DVDD)                                                                                                                                             | 図 7-27<br>図 7-28                                         |

| Common-Mode Rejection Ratio (CMRR)  | vs Frequency                                                                                                                                                                                                | 図 7-29                                                   |

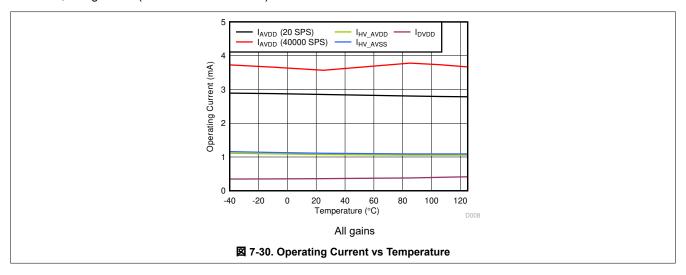

| Operating Current                   | vs Temperature                                                                                                                                                                                              | 図 7-30                                                   |

## 7.9 Typical Characteristics

### **8 Parameter Measurement Information**

### **8.1 Noise Performance**

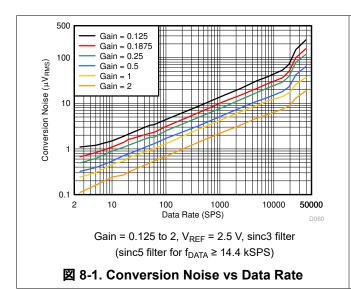

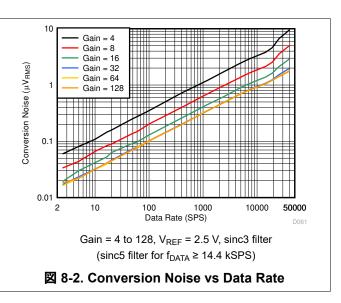

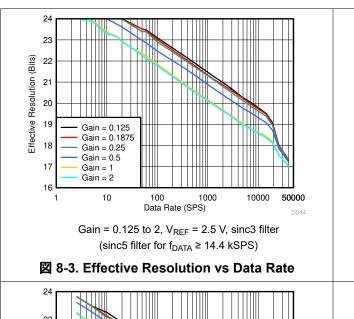

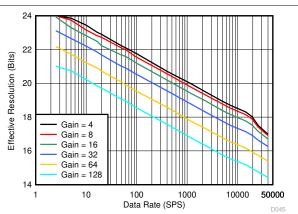

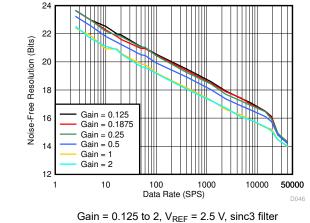

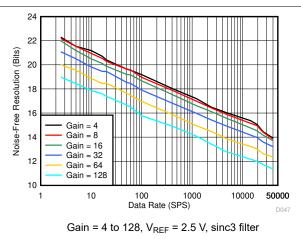

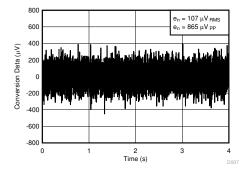

Noise performance depends on the device configuration: data rate, input gain, and digital filter mode. Two significant factors affecting noise performance are data rate and input gain. Decreasing the data rate lowers the noise because the measurement bandwidth is reduced. Increasing the gain reduces noise (when noise is treated as an input-referred quantity) because the noise of the PGA is lower than that of the ADC. Noise performance also depends on the digital filter mode. As the digital filter order is increased, the bandwidth decreases, which results in lower noise.

Peak-to-peak noise performance is typically 6.6 times the RMS value. Relative to the noise in the sinc3 filter mode, noise typically increases 30% in the finite-impulse response (FIR) and sinc1 filter mode because of the increased bandwidth of the sinc1 and FIR modes. Noise typically decreases 6% in the sinc4 filter mode because of the decreased bandwidth of the sinc4 filter mode.

The noise data are the standard deviation of the ADC data scaled in microvolts. The data are acquired with inputs shorted and based on consecutive ADC readings for a period of ten seconds or 8192 data points, whichever occurs first. Because of the statistical nature of noise, repeated measurements may yield higher or lower noise results.

ADC noise performance can also be expressed as *effective resolution* and *noise-free resolution* (bits). Effective resolution is based on the RMS value of the noise data and noise-free resolution is based on the peak-to-peak noise data; therefore, the noise-free resolution is the resolution with no code flicker.  $\Rightarrow$  1 is used to compute effective resolution based on the noise values plots of  $\Rightarrow$  8-1 and  $\Rightarrow$  8-2.

Effective Resolution or Noise-Free Resolution (Bits) =

$$3.32 \log (FSR / e_n)$$

(1)

where:

- FSR = Full-scale range = 2 V<sub>REF</sub> / Gain

- e<sub>n</sub> = Input-referred noise (RMS value for effective resolution, peak-to-peak value for noise-free resolution)

For example, using full-scale range =  $\pm 13.3$  V, data rate = 20 SPS, and sinc3 filter mode, the RMS noise value (from  $\boxtimes$  8-1) is 2.1  $\mu$ V. The effective resolution is: 3.32 log (26.6 V / 2.1  $\mu$ V) = 23.6 bits.

Gain = 4 to 128, V<sub>REF</sub> = 2.5 V, sinc3 filter mode (sinc5 filter for f<sub>DATA</sub> ≥ 14.4 kSPS)

### 図 8-4. Effective Resolution vs Data Rate

(sinc5 filter for f<sub>DATA</sub> ≥ 14.4 kSPS)

図 8-6. Noise-Free Resolution vs Data Rate

## 9 Detailed Description

### 9.1 Overview

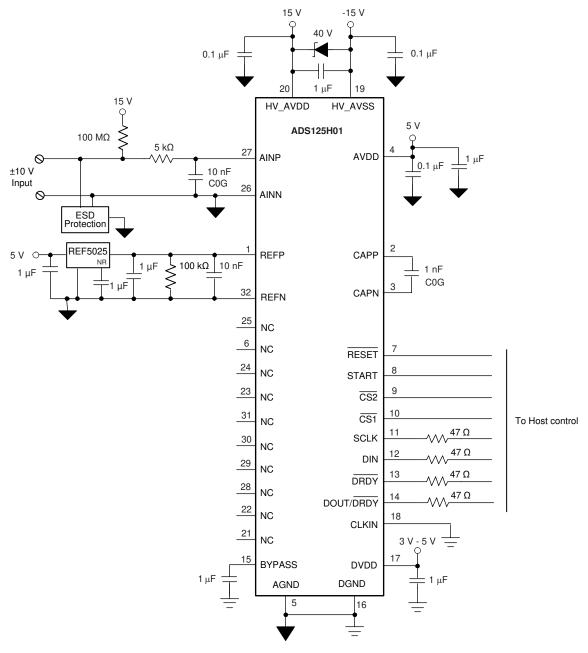

The ADS125H01 is a  $\pm 20$ -V signal input, 40-kSPS, 24-bit, delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converter (ADC). The ADC provides a compact one-chip measurement solution for a wide range of input voltages, including typical current and voltage inputs of industrial programmable logic controllers (PLCs), such as  $\pm 10$ -V and 4-mA to 20-mA transmitters (using an external shunt resistor). The ADC provides the resolution necessary for direct interface to low-level sensors such as strain-gauge sensors and thermocouples.

The device features a programmable gain amplifier (PGA) with an attenuation range from 0.125 to 0.5 and a gain range from 1 to 128. The combination of attenuation and gain provide an overall input voltage range of  $\pm 20$  V to  $\pm 20$  mV (when  $V_{REF} = 2.5$  V). The PGA is low-noise and low-drift with high input impedance, and includes internal monitors for detection of overload conditions.

In summary, the ADC features:

- 24-bit resolution

- Low-noise, 1-GΩ input impedance PGA

- Selectable attenuation and gain: overall full-scale range from ±20 mV to ±20 V

- Internal or external clock operation

- PGA and voltage reference monitors

- SPI-compatible serial interface with cyclic redundancy check (CRC) error check

Analog inputs (AINP and AINN) connect to the PGA via an input switch. The switch selects between the input signal and an internal test voltage ( $V_{CM}$ ). Internal diodes protect the analog and reference inputs from ESD events.

The PGA is a high-impedance, differential-input and differential-output amplifier providing both gain and attenuation modes. In attenuation mode, the input voltage is reduced to the range of the ADC. In gain mode, the input voltage is amplified to the range of the ADC. The PGA output connects to the CAPP and CAPN pins. The ADC antialias filter is provided by the combination of the internal PGA output resistors and the external capacitor connected to these pins.

The PGA is monitored for signal overload conditions. Status bits in the STATUS1 register indicate possible PGA overload conditions.

The  $\Delta\Sigma$  modulator measures the input voltage relative to the reference voltage to produce a 24-bit conversion result. The input range of the ADC is  $\pm V_{REF}$  / Gain, where gain is programmable from 0.125 to 128.

The reference voltage is either external (pins REFP, REFN) or the AVDD power supply. The reference input includes a monitor to detect low voltage conditions. The status is reflected in the conversion data STATUS byte.

The digital filter averages and decimates the modulator data to provide the output conversion result. For data rates ≤ 7.2 kSPS, the digital filter provides programmable sinc orders allowing optimization of conversion latency, conversion noise, and line-cycle rejection. The finite-impulse response (FIR) filter mode provides no-latency conversion data with simultaneous rejection of 50-Hz and 60-Hz interference at data rates of 20 SPS or less.

User-programmable offset- and gain-calibration registers correct the conversion data to provide the final conversion result.

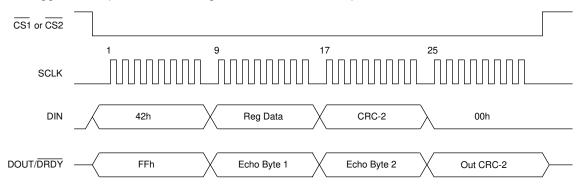

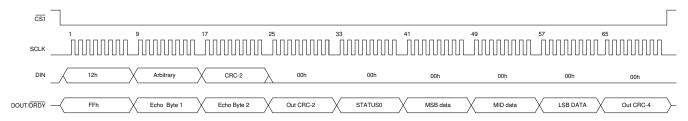

The SPI-compatible serial interface is used to read the conversion data and for device configuration. SPI I/O communication is validated by CRC error checking. The serial interface consists of the following signals:  $\overline{CS1}$ ,  $\overline{CS2}$ , SCLK, DIN, and DOUT/ $\overline{DRDY}$  (see the *Chip-Select Pins* ( $\overline{CS1}$  and  $\overline{CS2}$ ) section for details). The dual-function DOUT/ $\overline{DRDY}$  pin combines the functions of the serial data output and data-ready indication into one pin.  $\overline{DRDY}$  is the data-ready output signal.

Clock operation is either by the internal oscillator or by an external clock source. The external clock is automatically detected by the ADC. The nominal clock frequency is 7.3728 MHz (10.24 MHz for  $f_{DATA} = 40$  kSPS).

www.tij.co.jp

Conversions are controlled by the START pin or by the START command. Conversions are programmable for either continuous or one-shot (pulse) mode of operation.

The ADC is reset at power-on, or manually reset by the RESET input or by the RESET command.

The HV AVDD and HV AVSS power supplies allow either bipolar or unipolar configuration (bipolar: ±5 V to ±18 V, unipolar: 10 V to 36 V). The 5-V analog supply (AVDD) powers the ADC. The digital I/Os are powered by DVDD (3-V to 5-V range). An internal 2-V subregulator powers the ADC digital core from the DVDD supply. An external bypass capacitor is required at the subregulator output (BYPASS pin).

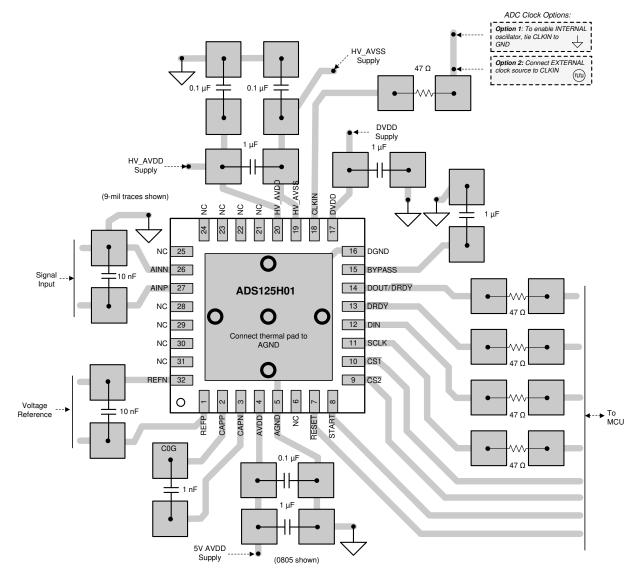

### 9.2 Functional Block Diagram

### 9.3 Feature Description

### 9.3.1 Input Voltage Range

式 2 defines the full-scale input voltage range of the ADC. 表 9-1 lists the input voltage range corresponding to the attenuation and gain setting when operating with a 2.5-V reference voltage. The input voltage range is limited under certain operating conditions due to the required headroom of the PGA and the ADC. See the *PGA Operating Range* section for details.

Input Voltage Range = ± V<sub>REF</sub> / Gain

(2)

表 9-1. Input Voltage Range

| GAIN[2:0] BITS <sup>(1)</sup> | GAIN   | INPUT VOLTAGE RANGE |                  |  |

|-------------------------------|--------|---------------------|------------------|--|

| GAIN[2.0] BITS                | GAIN   | DIFFERENTIAL        | SINGLE-ENDED     |  |

| 0000                          | 0.125  | ±20 V               | 0 V to ±15.5 V   |  |

| 0001                          | 0.1875 | ±13.3 V             | 0 V to ±13.3 V   |  |

| 0010                          | 0.25   | ±10 V               | 0 V to ±10 V     |  |

| 0011                          | 0.5    | ±5 V                | 0 V to ±5 V      |  |

| 0100                          | 1      | ±2.5 V              | 0 V to ±2.5 V    |  |

| 0101                          | 2      | ±1.25 V             | 0 V to ±1.25 V   |  |

| 0110                          | 4      | ±0.625 V            | 0 V to ±0.625 V  |  |

| 0111                          | 8      | ±0.312 V            | 0 V to ±0.312 V  |  |

| 1000                          | 16     | ±0.156 V            | 0 V to ±0.156 V  |  |

| 1001                          | 32     | ±0.0781 V           | 0 V to ±0.0781 V |  |

| 1010                          | 64     | ±0.0391 V           | 0 V to ±0.0391 V |  |

| 1011                          | 128    | ±0.0195 V           | 0 V to ±0.0195 V |  |

<sup>(1)</sup> Reference voltage = 2.5 V and HV power supply = ±18 V.

### 9.3.2 Analog Inputs (AINP, AINN)

### 9.3.2.1 ESD Diodes

ESD diodes are used to protect the ADC inputs from possible ESD events occurring during the manufacturing process and during printed circuit board (PCB) assembly when manufactured in an ESD-controlled environment. For system-level ESD protection, consider the use of external ESD protection devices for pins that are exposed to possible ESD, including the analog inputs.

If an analog input is driven below  $HV\_AVSS - 0.3 V$ , or above  $HV\_AVDD + 0.3 V$ , the internal ESD protection diodes can conduct. If this condition is possible, current can flow through the inputs and flow out from the  $HV\_AVDD$  or  $HV\_AVSS$  pins. Use external clamp diodes, series resistors, or both to limit the input current to the specified value.

### 9.3.2.2 Input Switch

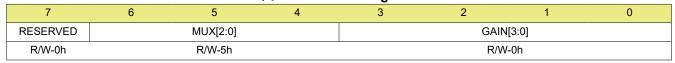

The input switch selects between an internal test voltage and the external input signal. The internal test voltage  $(V_{CM})$  is the mid-point of the HV\_AVDD and HV\_AVSS power-supply voltage. The internal voltage is used to verify the offset and noise of the ADC measurement path. The input switch is programmed by the MUX[2:0] bits of the MODE4 register (address = 10h). 表 9-2 lists the input switch settings.

表 9-2. Input Switch Settings

| MUX[2:0] BITS OF<br>REGISTER MODE4 (10h) | INPUT SELECTION                                     |  |

|------------------------------------------|-----------------------------------------------------|--|

| 000                                      | AINP to AINN                                        |  |

| 101                                      | V <sub>CM</sub> : (HV_AVDD + HV_AVSS) / 2 (default) |  |

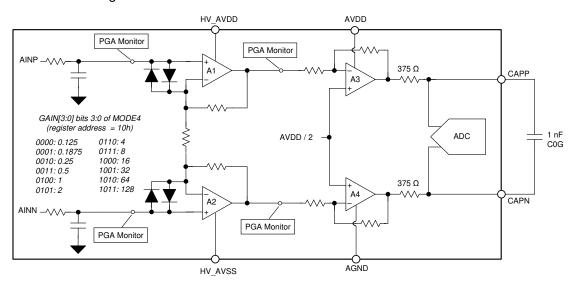

### 9.3.3 Programmable Gain Amplifier (PGA)

The PGA is a low-noise, programmable gain (attenuation), CMOS differential-input, differential-output amplifier. The PGA operates in gain or attenuation mode depending on the selected gain. Typically, the PGA is programmed for gain when the expected input signal voltage is  $\leq V_{REF}$  and is programmed for attenuation when the expected input signal voltage is  $\geq V_{REF}$ .

###

図 9-1. PGA Block Diagram

The signal inputs are RC filtered to reduce sensitivity to radio frequency interference (RFI) and electromagnetic interference (EMI). The first PGA stage is a high input-impedance, noninverting differential amplifier (amplifiers A1 and A2) and provides gain. Inverse-parallel connected diodes across the inputs of A1 and A2 clamp the amplifier input voltage if they are driven out-of-range. If the amplifier is out-of-range, the diodes can conduct, resulting in current flow through the analog input pins. High dV/dt input signals, such as those generated from the switching of a multiplexer, can lead to transient turn-on of the clamp diodes. In some cases, an RC filter at the PGA inputs may be necessary to limit the dV/dt of the signal to prevent the clamp diodes from turning on.

The second stage (amplifiers A3 and A4) is an inverting, differential amplifier. This stage provides attenuation of high-amplitude signal levels. The common-mode voltage of this stage is AVDD / 2. The second stage drives the modulator input of the ADC and is also connected to the CAPP and CAPN pins. An external 1-nF capacitor filters the modulator input sample pulses and also provides the antialias filter for the ADC. Place the capacitor close to the pins using short, direct traces. Avoid running clock traces or other digital traces underneath or in the vicinity of these pins. Gain is programmed by the GAIN[3:0] bits of the MODE 4 register.

Monitors verify the voltage headroom of the PGA input and output nodes. See the *PGA Monitors* section for details.

### 9.3.3.1 PGA Operating Range

The absolute input voltage range of the PGA must not be exceeded in order to maintain linear operation. The maximum and minimum absolute input voltage is determined by the PGA gain setting, the maximum differential input voltage ( $V_{IN}$ ), and the minimum value of the high-voltage power supply. The absolute voltage is the combined differential and common-mode voltages. Maintain the absolute input voltage ( $V_{AINx}$ ) within the range as shown in  $\neq 3$ , otherwise incorrect conversion data can result.

$$HV_AVSS + 2.5 V + V_{IN} \times (Gain - 1) / 2 < V_{(AINx)} < HV_AVDD - 2.5 V - V_{IN} \times (Gain - 1) / 2$$

(3)

#### where:

- Gain = PGA gain. For gain < 1, use value = 1

- V<sub>(AINx)</sub> = Absolute input voltage

- V<sub>IN</sub> = V<sub>AINP</sub> V<sub>AINN</sub> = Maximum expected differential input voltage

Additionally, the *differential input signal* is limited in two conditions. The first condition is when the reference voltage exceeds AVDD - 1 V (nominally  $V_{REF} > 4$  V). In this case, the differential input signal is limited to:  $V_{IN} = \pm (AVDD - 1 \text{ V})$  / Gain, instead of the ideal  $V_{IN} = \pm V_{REF}$  / Gain. The second condition applies to gains of 0.125 and 0.1875. In this case, the differential input signal range is limited to:  $V_{IN} = \pm 20$  V, regardless of the reference voltage value.

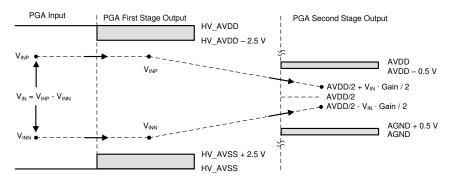

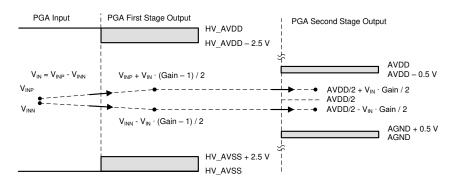

☑ 9-2 and ☑ 9-3 show the relationship between the PGA input voltage and the PGA output voltage. In attenuation mode, the first PGA stage is configured as a unity-gain follower. The second PGA stage attenuates the differential input voltage and shifts the signal common-mode voltage to AVDD / 2 to drive the ADC input.

In gain mode, the first PGA stage amplifies the differential signal. The second PGA stage is configured as a unity-gain follower with level-shift.  $\boxtimes$  9-2 and  $\boxtimes$  9-3 show the corresponding output voltage of the PGA stages that must have operating voltage headroom.

図 9-2. PGA Attenuation Mode

図 9-3. PGA Gain Mode

Submit Document Feedback

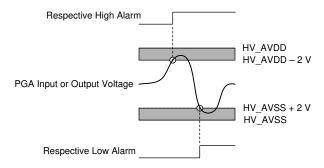

#### 9.3.3.2 PGA Monitors

The PGA requires operating voltage headroom at the input and output nodes. The operating headroom must be maintained; otherwise the conversion data may not be valid. Use the internal PGA monitors to detect PGA out-of-range conditions. The PGA has four monitors (two monitors for the input and two monitors for the output) with high and low thresholds for each, for a total of eight possible alarms. The status of each PGA monitor is read in the STATUS1 register. The PGA monitoring points are illustrated in  $\boxtimes$  9-1.  $\boxtimes$  9-4 shows the operation of the high and low thresholds of each of the four PGA monitors.

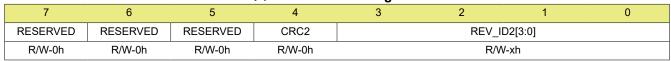

図 9-4. PGA Monitor Thresholds

Detect PGA out-of-range operating conditions by polling the STAT12 bit (bit 4 of the STATUS conversion byte or STATUS0 register). The STAT12 bit is the logical OR of all PGA error flags with the CRC2 error flag. When the STAT12 bit asserts, poll the STATUS1 and STATUS2 registers (address 11h and 12h) to determine the source of the STAT12 error. The PGA out-of-range flags latch in the STATUS1 register and remain latched after the overload condition is removed. Read the STATUS1 register to clear the PGA out-of-range bits (clear-on-read operation). The PGA overload flags *and* the CRC2 flag must be reset in order for the STAT12 bit to clear. See the STATUS1 register for a description of the PGA overload bits.

The PGA monitors are analog comparators that respond to transient out-of-range conditions.

### 9.3.4 Reference Voltage

A reference voltage is required for operation. An internal reference voltage switch selects between the external reference and the AVDD power supply voltage (default). Program the reference switch using the RMUX[3:0] bits to select the reference (see the REF register for details).

Apply the reference voltage to the REFP and REFN pins. The reference inputs are differential defined by:  $V_{REF} = (V_{(REFP)} - V_{(REFN)})$ , where  $V_{(REFP)}$  and  $V_{(REFN)}$  are the positive and negative absolute reference voltages. Follow the specified absolute and differential operating conditions. Use a 10-nF or larger bypass capacitor across the reference input pins to filter noise. The reference input current can lead to a voltage error if large reference impedances are present. If a reference impedance is present, the reference voltage may have an error.

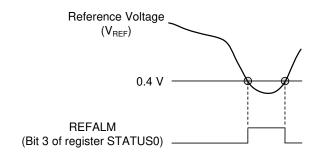

### 9.3.4.1 Reference Monitor

The reference monitor detects a low or missing reference voltage. As illustrated in  $\boxtimes$  9-5, when the differential reference voltage is  $\leq$  0.4 V (typical), the REFALM bit is set in the STATUS0 register. The alarm is read-only and resets at the next conversion after the fault condition is cleared. To implement the reference monitor, place a 100-k $\Omega$  resistor across the reference inputs. If either positive or negative reference inputs become disconnected, the reference inputs are differentially biased to 0 V, thereby triggering the low reference alarm. Poll bit 3 (REFALM) of the STATUS0 register to determine if the reference alarm has triggered.

図 9-5. Reference Monitor Operation

#### 9.3.5 ADC Modulator

The modulator is an inherently stable, fourth-order, 2 + 2 pipelined  $\Delta\Sigma$  modulator. The modulator samples the analog input voltage at a high sample rate ( $f_{MOD} = f_{CLK} / 8$ ) and converts the analog input to a 1's-density bit stream that is processed by the digital filter.

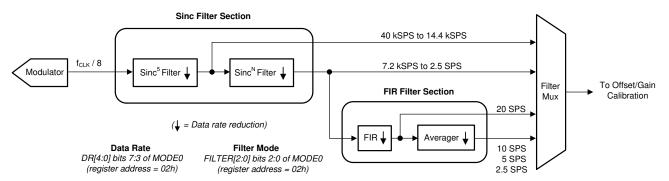

### 9.3.6 Digital Filter

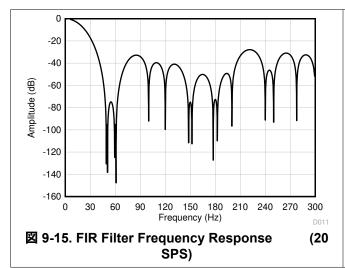

The digital filter has two operating modes, as shown in  $\boxtimes$  9-6:  $\sin(x) / x$  (sinc) mode and finite impulse response (FIR) mode. The sinc mode provides data rates of 2.5 SPS to 40 kSPS, and selectable sinc1, sinc3, and sinc4 filter orders for  $f_{DATA} \le 7.2$  kSPS. The FIR filter provides single-cycle settled conversions and simultaneous rejection of 50-Hz and 60-Hz signal interference frequencies with data rates of 2.5 SPS to 20 SPS.

図 9-6. Digital Filter Block Diagram

#### 9.3.6.1 Sinc Filter Mode

The sinc filter consists of a variable-decimation sinc5 filter followed by a variable-decimation, variable-order sinc filter. The sinc5 filter averages and down-samples the modulator data ( $f_{CLK}$  / 8) to provide 40 kSPS, 25.6 kSPS, 19.2 kSPS, and 14.4 kSPS data rates by using decimation ratios of 32, 36, 48, and 64. These data rates bypass the second filter stage and as a result are sinc5 output only. The second stage receives data at 14.4 kSPS and performs additional filtering and decimation to provide data rates of 7.2 kSPS to 2.5 SPS. The second stage has programmable sinc order. The data rate is programmed by the DR[4:0] bits and the filter mode is programmed by the FILTER[2:0] bits of the MODE0 register.

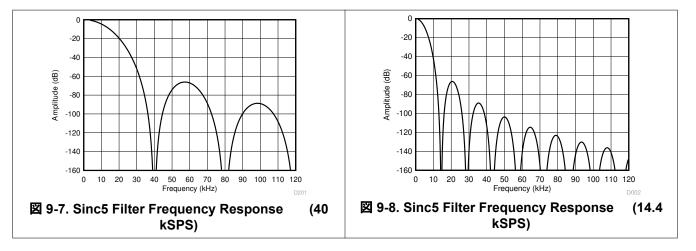

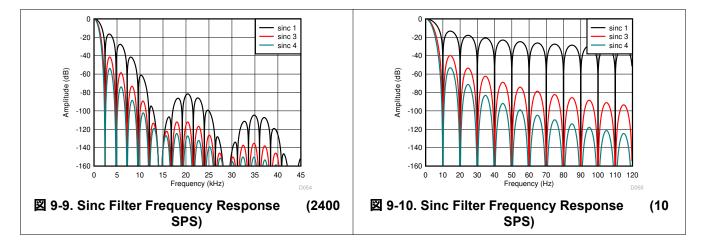

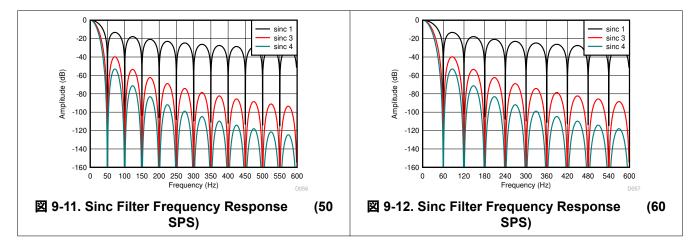

### 9.3.6.1.1 Sinc Filter Frequency Response

As shown in  $\boxtimes$  9-7 and  $\boxtimes$  9-8, the first-stage sinc5 filter has frequency response nulls occurring at N × f<sub>DATA</sub> (where N = 1, 2, 3, and so on). At the null frequencies, the filter has zero gain.

The second stage filter superimposes additional nulls to the nulls produced by the first stage. The first of the nulls occurs at the output data rate with additional nulls occurring at data rate multiples.

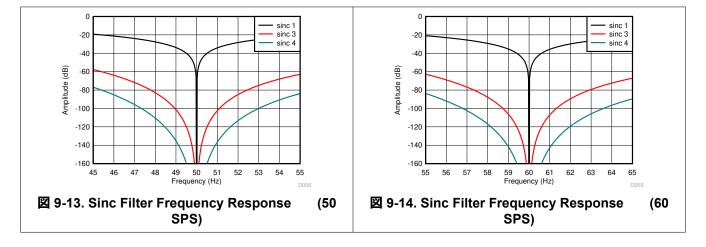

$\boxtimes$  9-11 and  $\boxtimes$  9-12 show the frequency response of data rates 50 SPS and 60 SPS. 50-Hz or 60-Hz rejection is increased by increasing the order of the sinc filter.

The sinc filter has an overall low-pass response that rolls off high-frequency components of the signal. The filter bandwidth depends on the output data rate and the filter order. The *system* bandwidth is the combined bandwidths of the digital filter, the PGA antialias filter, and external signal filters. 表 9-3 lists the -3-dB bandwidth of the sinc filter.

-3-dB BANDWIDTH (Hz) **DATA RATE (SPS)** SINC1 SINC3 SINC4 SINC5 2.5 1.10 0.65 0.58 5 2.23 1.33 1.15 10 4.43 2.62 2.28 7.38 16.6 4.37 3.80 20 8.85 5.25 4.63 22.1 13.1 11.4 50 60 26.6 15.7 13.7 100 44.3 26.2 22.8 400 177 105 91.0 273 1200 525 314 2400 1015 623 544 4800 1798 1214 1077 7200 2310 1750 1590 14400 \_ 2940 19200 3920 25600 5227 40000 8167

表 9-3. Sinc Filter Bandwidth

#### 9.3.6.2 FIR Filter

The finite impulse response (FIR) filter provides simultaneous rejection of 50-Hz and 60-Hz line cycle frequencies and related harmonics at data rates of 2.5 SPS, 5 SPS, 10 SPS, and 20 SPS. The conversion latency of the FIR filter is a single cycle; see  $\frac{1}{8}$  9-6 for detailed latency values. As illustrated in  $\frac{1}{8}$  9-6, the FIR filter section receives data from the second-stage sinc filter. The FIR filter section decimates the data to yield the output data rate of 20 SPS. A variable averaging filter (sinc1) yields 10 SPS, 5 SPS, and 2.5 SPS.

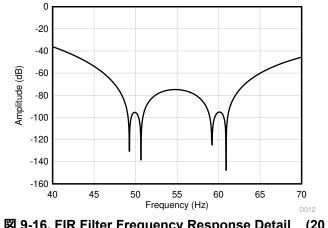

As shown in 🗵 9-15 and 🗵 9-16, the frequency response has nulls that are positioned near 50 Hz and 60 Hz.

図 9-16. FIR Filter Frequency Response Detail (20 SPS)

Similar to the response of the sinc filter, the overall FIR filter frequency has a low-pass response that rolls off high frequencies. The signal bandwidth depends on the output data rate. 表 9-4 lists the -3-dB filter bandwidth of the FIR filter. The total system bandwidth is the combined response of the digital filter, the PGA antialias filter, and external filters.

表 9-4. FIR Filter Bandwidth

| DATA RATE (SPS) | –3-dB BANDWIDTH (Hz) |  |

|-----------------|----------------------|--|

| 2.5             | 1.2                  |  |

| 5               | 2.4                  |  |

| 10              | 4.7                  |  |

| 20              | 13                   |  |

### 9.3.6.3 50-Hz and 60-Hz Normal-Mode Rejection

To reduce the effects of 50-Hz and 60-Hz interference, optimize the filter mode and data rate selection, and the accuracy of the ADC clock to provide the required 50-Hz and 60-Hz rejection.  $\frac{1}{2}$  9-5 summarizes the 50-Hz and 60-Hz noise rejection versus filter mode and data rate. The table values are based on a 2% and 6% tolerance of the 50-Hz and 60-Hz input frequencies relative to the ADC clock frequency. Common-mode noise is also rejected at 50 Hz and 60 Hz.

表 9-5. 50-Hz and 60-Hz Normal-Mode Rejection

|                 | DIGITAL FILTER AMPLITUDE (dB) |             |             |             |             |  |

|-----------------|-------------------------------|-------------|-------------|-------------|-------------|--|

| DATA RATE (SPS) | FILTER TYPE                   | 50 Hz (±2%) | 50 Hz (±6%) | 60 Hz (±2%) | 60 Hz (±6%) |  |

| 2.5             | FIR                           | -113        | -88         | -99         | -80         |  |

| 2.5             | Sinc1                         | -36         | -40         | -37         | -37         |  |

| 2.5             | Sinc3                         | -108        | -120        | -111        | -111        |  |

| 2.5             | Sinc4                         | -144        | -160        | -148        | -148        |  |

| 5               | FIR                           | -111        | -77         | -95         | -76         |  |

| 5               | Sinc1                         | -34         | -30         | -34         | -30         |  |

| 5               | Sinc3                         | -102        | -90         | -102        | -90         |  |

| 5               | Sinc4                         | -136        | -120        | -136        | -120        |  |

| 10              | FIR                           | -111        | -73         | -94         | -68         |  |

| 10              | Sinc1                         | -34         | -25         | -34         | -25         |  |

| 10              | Sinc3                         | -102        | <b>–</b> 75 | -102        | <b>–</b> 75 |  |

| 10              | Sinc4                         | -136        | -100        | -136        | -100        |  |

| 16.6            | Sinc1                         | -34         | -24         | -21         | -21         |  |

| 16.6            | Sinc3                         | -102        | -72         | -63         | -63         |  |

| 16.6            | Sinc4                         | -136        | -96         | -84         | -84         |  |

| 20              | FIR                           | <b>-95</b>  | -66         | -94         | -66         |  |

| 20              | Sinc1                         | -18         | -18         | -34         | -24         |  |

| 20              | Sinc3                         | -54         | -54         | -102        | -72         |  |

| 20              | Sinc4                         | -72         | -72         | -136        | -96         |  |

| 50              | Sinc1                         | -34         | -24         | -15         | -15         |  |

| 50              | Sinc3                         | -102        | -72         | -45         | -45         |  |

| 50              | Sinc4                         | -136        | -96         | -60         | -60         |  |

| 60              | Sinc1                         | -13         | -12         | -34         | -24         |  |

| 60              | Sinc3                         | -40         | -36         | -102        | -72         |  |

| 60              | Sinc4                         | -53         | -48         | -136        | -96         |  |

Submit Document Feedback

### 9.4 Device Functional Modes

#### 9.4.1 Conversion Control

The START pin or the START command controls the conversions. If using commands to control conversions, keep the START pin low to avoid contention between pin control and command control. Commands take effect on the 32nd falling SCLK edge. See the *Switching Characteristics* table for details on conversion-control timing.

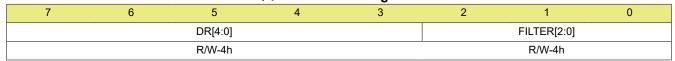

The ADC has two conversion-control operating modes: continuous-conversion mode and pulse-conversion mode. The continuous-conversion mode performs conversions indefinitely until conversions are stopped. Pulse-conversion mode performs one conversion and then stops. The CONVRT (bit 4 of the MODE1 register) programs the conversion mode.

### 9.4.1.1 Continuous-Conversion Mode

This conversion mode performs continuous conversions until the conversion process is stopped. To start conversions, take the START pin high or send the START command.  $\overline{DRDY}$  is driven high when the conversion is started.  $\overline{DRDY}$  is driven low when the conversion data are ready. Conversion data are available to read at that time. Take the START pin low or send a STOP command to stop conversions. When conversions are stopped, any conversion in progress runs to completion. To restart a conversion that is in progress, toggle the START pin low-then-high or send a new START command.

#### 9.4.1.2 Pulse-Conversion Mode

In pulse-conversion mode, the ADC performs one conversion when the START pin is taken high or when the START command is sent. When the conversion completes, further conversions stop automatically. The  $\overline{\text{DRDY}}$  output is driven high to indicate the conversion is actively in progress and is driven low when the conversion data are ready. Conversion data are available to read at that time. To restart a conversion in progress, toggle the START pin low-then-high or send a new START command. Driving START low or sending the STOP command does not interrupt the current conversion.

### 9.4.1.3 Conversion Latency

The digital filter averages data from the modulator to produce the conversion result. The internal stages of the digital filter must be settled to provide fully settled output data. The order and the decimation ratio of the digital filter determine the amount of data averaged that, in turn, affects the latency of the conversion result. The FIR and sinc1 filter modes are zero latency because the ADC provides the conversion result in one conversion cycle. Latency time is an important consideration for overall data throughput in multiplexed applications.

$\pm$  9-6 lists the conversion latency values of the ADC. Conversion latency is defined as the time from the start of the first conversion by taking the START pin high or sending the START command to the time of the first conversion data. The ADC is designed to provide fully settled data under this condition. The conversion latency values listed in  $\pm$  9-6 include the programmable start-conversion delay that delays the digital filter start. After the first conversion in continuous-conversion mode, the periods of the following conversions are equal to 1 /  $f_{DATA}$ .

表 9-6. Conversion Latency Time

| DATA RATE | CONVERSION LATENCY TIME (t <sub>(STDR)</sub> <sup>(1)</sup> , ms) |       |       |       |       |  |  |

|-----------|-------------------------------------------------------------------|-------|-------|-------|-------|--|--|

| (SPS)     | SINC1                                                             | SINC3 | SINC4 | SINC5 | FIR   |  |  |

| 2.5       | 400.4                                                             | 1,200 | 1,600 | _     | 402.2 |  |  |

| 5         | 200.4                                                             | 600.4 | 800.4 | _     | 202.2 |  |  |

| 10        | 100.4                                                             | 300.4 | 400.4 | _     | 102.2 |  |  |

| 16.6      | 60.43                                                             | 180.4 | 240.4 | _     | _     |  |  |

| 20        | 50.43                                                             | 150.4 | 200.4 | _     | 52.22 |  |  |

| 50        | 20.43                                                             | 60.43 | 80.43 | _     | _     |  |  |

| 60        | 17.09                                                             | 50.43 | 67.09 | _     | _     |  |  |

| 100       | 10.43                                                             | 30.43 | 40.43 | _     | _     |  |  |

| 400       | 2.925                                                             | 7.925 | 10.43 | _     | _     |  |  |

| 1200      | 1.258                                                             | 2.925 | 3.758 | _     | _     |  |  |

| 2400      | 0.841                                                             | 1.675 | 2.091 | _     | _     |  |  |

| 4800      | 0.633                                                             | 1.050 | 1.258 | _     | _     |  |  |

| 7200      | 0.564                                                             | 0.841 | 0.980 | _     | _     |  |  |

| 14400     | _                                                                 | _     | _     | 0.423 | _     |  |  |

| 19200     | _                                                                 | _     | _     | 0.336 | _     |  |  |

| 25600     | _                                                                 | _     | _     | 0.271 | _     |  |  |

| 40000     | _                                                                 | _     | _     | 0.179 | _     |  |  |

(1) Conversion-start time delay = 50 µs (36 µs at f<sub>CLK</sub> = 10.24 MHz) using DELAY[3:0] = 0001). Conversion latency scales with f<sub>CLK</sub>.

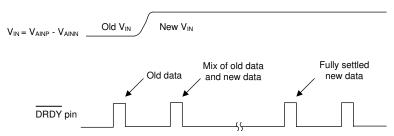

As shown in  $\boxtimes$  9-17, if the input-step change occurs during an active conversion, the conversion data are a mix of old and new data. After an input-step change, the number of conversion periods required to provide fully settled output data are determined dividing the conversion latency time by the conversion period plus one additional conversion period.

図 9-17. Input Change During Conversions

#### 9.4.1.4 Start-Conversion Delay

At the start of a conversion, the ADC provides a programmable delay time to allow for PGA settling and to provide a delay time for the possible effects of settling of external components (such as multiplexers and R-C filters). The default value is  $50~\mu s$  ( $f_{CLK} = 7.3728~MHz$ ) to provide settling time for the PGA antialiasing filter after an input step change. Use additional delay time as needed to provide settling time for the settling effects of external components. As an alternative to this parameter, delay the start of conversion manually after an input change. See  $\frac{1}{8}$  9-27 for start-conversion delay values.

#### 9.4.2 Clock Mode

The ADC is operated with an external clock or with the internal oscillator. For external clock operation, apply the clock signal to the CLKIN pin. The ADC detects the presence of the external clock and selects the clock automatically. Read the CLOCK bit in the STATUS0 register to verify the clock mode. As described in 表 9-7, the clock frequency depends on the data rate used. Be sure the external clock is free of overshoot and glitches. A source-termination resistor placed at the clock buffer often helps reduce overshoot.

To operate the ADC by the internal oscillator, connect CLKIN to DGND. Be aware of the accuracy of the internal oscillator as described in the *Electrical Characteristics*. The internal oscillator begins operating immediately at device power-on.

表 9-7. External Clock Frequency

| CLOCK FREQUENCY | DATA RATE           |

|-----------------|---------------------|

| 7.3728 MHz      | 2.5 SPS – 25.6 kSPS |

| 10.24 MHz       | 40 kSPS             |

#### 9.4.3 Reset

The ADC is reset in three ways: automatic at power-on, manually via the RESET pin, or manually by the RESET command.

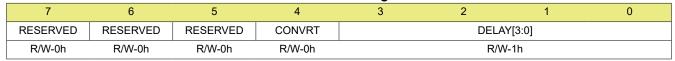

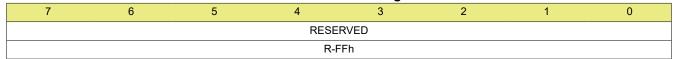

At reset, the serial interface, conversion-control logic, digital filter, and register map values are reset. The RESET bit of the STATUS0 register is set after a reset occurs. Clear the bit to detect the next device reset. If the START pin is high after reset, the ADC immediately begins conversions after reset.

#### 9.4.3.1 Power-On Reset

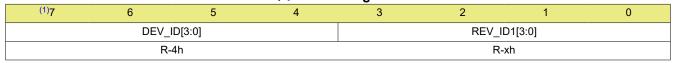

After the supply voltages cross the respective reset thresholds at power-up, the ADC is reset and after  $2^{16}$  f<sub>CLK</sub> cycles the ADC is ready for communication. Until this time,  $\overline{DRDY}$  is held low.  $\overline{DRDY}$  is then driven high to indicate when ADC communication can begin. The conversion cycle starts 512 f<sub>CLK</sub> cycles after  $\overline{DRDY}$  asserts high if START is high. See  $\boxtimes$  7-4 for power-on reset behavior.