Texas Instruments

BQ24160, BQ24160A, BQ24161, BQ24161B, BQ24163, BQ24168 JAJSOY8H - NOVEMBER 2011 - REVISED JULY 2022

# BQ2416xx パワー・パス管理および I<sup>2</sup>C インターフェイス搭載、2.5A、デュア ル入力、シングル・セルのスイッチ・モード・リチウムイオン・バッテリ・ チャージャ

# 1 特長

- 独立のパワー・パス制御機能を搭載した、高効率のス イッチ・モード・チャージャ

- - 深放電されたバッテリまたはバッテリなしで、システムをただちに起動

- MaxLife<sup>™</sup> テクノロジーと互換性があり、BQ27530と 組み合わせれば、より高速な充電が可能

- 最大 2.5A の充電に対応するデュアル入力、FET 内 蔵のチャージャ

- 入力定格 20V で過電圧保護 (OVP) を搭載

- 最大 1.5A の USB 入力について 6.5V

- 最大 2.5Aの IN 入力 (BQ24160、 BQ24160A、BQ24161、BQ24163) について 10.5V

- 最大 2.5A の IN 入力 (BQ24168) で 6.5V

- 安全で高精度のバッテリ管理機能

- 1%のバッテリ・レギュレーション精度

- 10%の充電電流精度

- I<sup>2</sup>C インターフェイスを使用して充電パラメータをプログ ラム

- 電圧ベースの NTC 監視入力

- JEITA 互換 (BQ24160、BQ24160A、 BQ24161B、BQ24163、BQ24168)

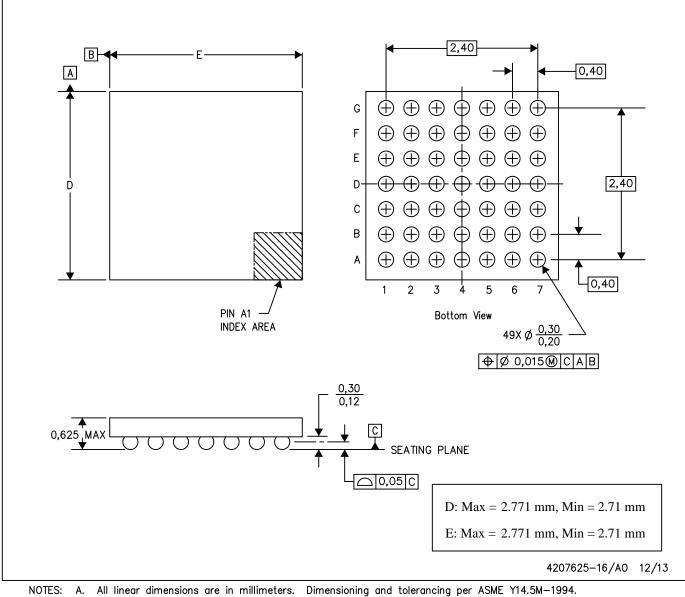

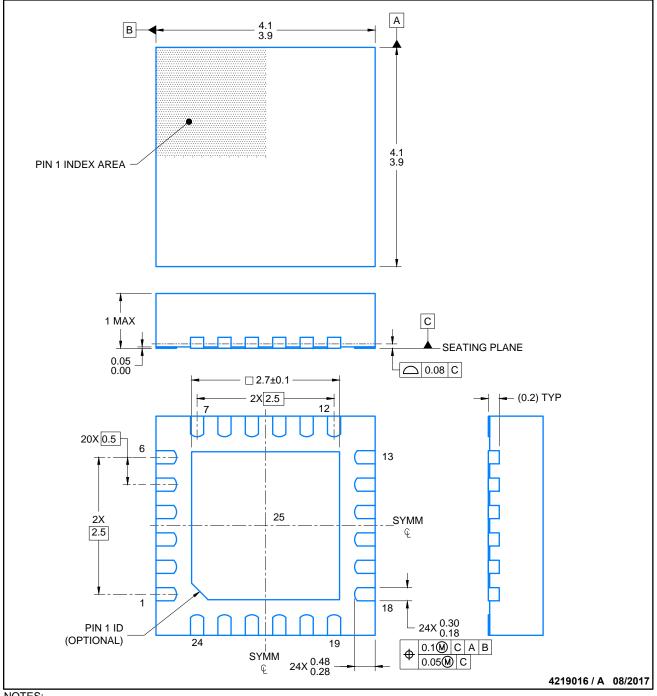

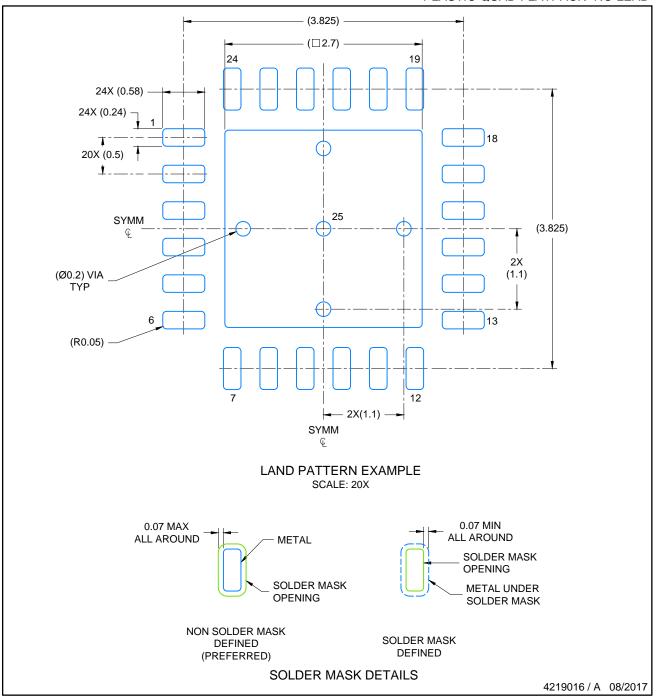

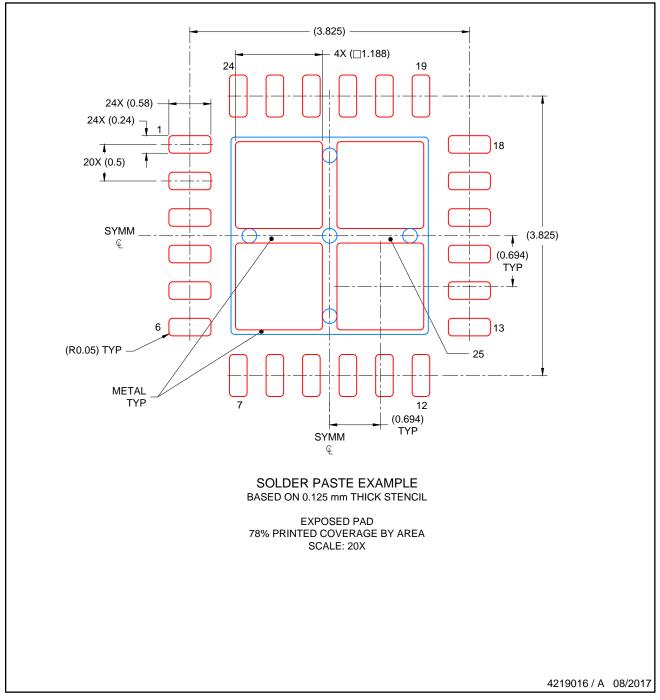

- 2.8mm × 2.8mm の小型 49 ボール WCSP または 4mm × 4mm の VQFN-24 パッケージで供給

# 2 アプリケーション

- ハンドヘルド製品

- ポータブル・メディア・プレーヤ

- 携帯機器

- ネットブックおよびポータブル・インターネット・デバイス

# 3 概要

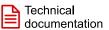

BQ24160、BQ24160A、BQ24161、BQ24161B、 BQ24163、BQ24168は、スペースに制約があり、大容量 バッテリを使用するポータブル・アプリケーションを対象と した、高集積のシングル・セル・リチウムイオン・バッテリ・チ ャージャおよびシステム・パワー・パス管理デバイスです。 シングル・セル・チャージャにはデュアル入力があり、USB ポート、またはより大電力の入力電源 (AC アダプタまたは ワイヤレス充電入力)で動作でき、多様なソリューションを 実現できます。2つの入力は互いに完全に絶縁されてお り、J<sup>2</sup>C インターフェイスを使用して簡単に選択できます。

電力パス管理機能により、BQ2416xx は高効率の DC-DC コンバータからシステムに電力を供給するとともに、バ ッテリを同時に独立して充電できます。パワー・パス管理ア ーキテクチャにより、バッテリ・パックに欠陥がある、または 存在しない場合でもシステムを動作させ、バッテリが完全 に放電した、または存在しない状態でもシステムを即座に オンできます。

| 部品番号     | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |  |  |  |  |  |  |

|----------|----------------------|-----------------|--|--|--|--|--|--|

| BQ2416xx | VQFN (24)            | 4.00mm × 4.00mm |  |  |  |  |  |  |

| DQZTIOAA | DSBGA (49)           | 2.80mm × 2.80mm |  |  |  |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

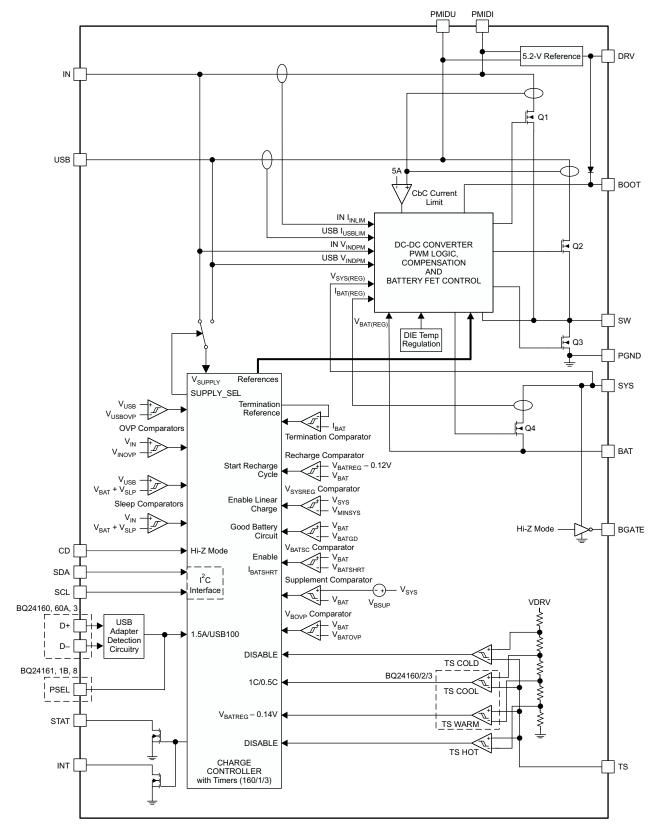

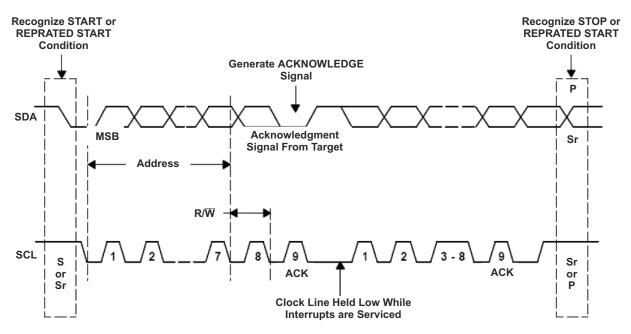

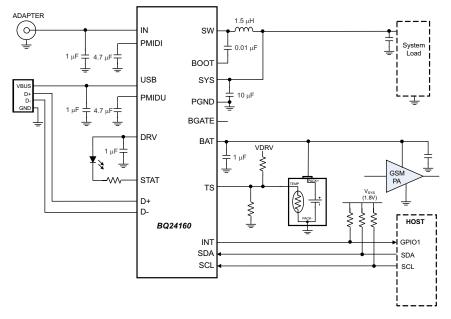

アプリケーション回路図

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

- - -

| 1 | 特長                                   | . 1 |

|---|--------------------------------------|-----|

| 2 | アプリケーション                             | 1   |

| 3 | 概要                                   | . 1 |

| 4 | Revision History                     | . 2 |

| 5 | Device Comparison Table              | 4   |

|   | Pin Configuration and Functions      |     |

| 7 | Specifications                       | . 7 |

|   | 7.1 Absolute Maximum Ratings         | . 7 |

|   | 7.2 Handling Ratings                 |     |

|   | 7.3 Recommended Operating Conditions |     |

|   | 7.4 Thermal Information              |     |

|   | 7.5 Electrical Characteristics       |     |

|   | 7.6 Typical Characteristics          |     |

| 8 | Detailed Description                 |     |

|   | 8.1 Overview                         | 13  |

|   | 8.2 Functional Block Diagram         |     |

|   | 8.3 Feature Description              | 15  |

|   | 8.4 Device Functional Modes          | 26  |

| 8.5 Programming                                     | 27                |

|-----------------------------------------------------|-------------------|

| 8.6 Register Maps                                   | 29                |

| 9 Application and Implementation                    |                   |

| 9.1 Application Information                         |                   |

| 9.2 Typical Application                             |                   |

| 10 Power Supply Recommendations                     | 38                |

| 10.1 Requirements for SYS Output                    | 38                |

| 10.2 Requirements for Charging                      | 38                |

| 11 Layout                                           | 39                |

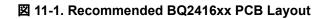

| 11.1 Layout Guidelines                              | 39                |

| 11.2 Layout Example                                 | 40                |

| 12 Device and Documentation Support                 | 41                |

| 12.1 Device Support                                 | 41                |

| 12.2 Receiving Notification of Documentation Update | s <mark>41</mark> |

| 12.3 サポート・リソース                                      | 41                |

| 12.4 Trademarks                                     |                   |

| 12.5 Electrostatic Discharge Caution                | 41                |

| 12.6 Glossary                                       | 41                |

|                                                     |                   |

## 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Cł | hanges from Revision G (November 2015) to Revision H (July 2022) | Page |

|----|------------------------------------------------------------------|------|

| •  | Changed I <sub>TERM</sub> specification                          | 8    |

| CI | Changes from Revision F (July 2014) to Revision G (November 2015) |    |  |  |  |  |

|----|-------------------------------------------------------------------|----|--|--|--|--|

| •  | Deleted hyperlink to unpublished application note SI UA727        | 26 |  |  |  |  |

| C | hanges from Revision E (November 2013) to Revision F (January 2014)                               | Page |

|---|---------------------------------------------------------------------------------------------------|------|

| • | 「取り扱い定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクシ                                          | /ョン、 |

|   | 「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、                                         | 、「メカ |

|   | ニカル、パッケージ、および注文情報」セクションを追加                                                                        | 1    |

| • | Changed the Ordering Information table to the Device Comparison Table                             | 4    |

| • | Changed to V <sub>BAD SOURCE</sub> include values for "During Bad Source Detection"               | 8    |

|   | Changed the Functional Block Diagram. Changed the device numbers above D+/D- and PSEL             |      |

| • | Changed the PWM Controller in Charge Mode section to include the soft-start function              | 15   |

|   | Changed the Battery Charging Process section. New text added starting with "The BQ2416xx monitors |      |

|   | charging current."                                                                                | 16   |

| • | Changed the Input Source Connected section                      | 17 |

|---|-----------------------------------------------------------------|----|

| • | Changed the Input Source Connected section                      | 19 |

|   | Added the Reverse Boost (Boost Back) Prevention Circuit section |    |

|   |                                                                 |    |

#### Changes from Revision D (November 2012) to Revision E (November 2013)

- 特長を追加: MaxLife テクノロジーと互換性があり、BQ27530と組み合わせれば、より高速な充電が可能......1

- データシート全体にわたって次のように変更:データシート全体にわたって QFN-24 パッケージを VQFN-24 パッケージに変更......1

#### Changes from Revision C (October 2012) to Revision D (November 2012)

Page

Page

| С | hanges from Revision B (September 2012) to Revision C (October 2012) Page                                                                                                                                       |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • | Changed the Ordering Information table to include BQ24160A4                                                                                                                                                     |

| С | hanges from Revision A (March 2012) to Revision B (September 2012) Page                                                                                                                                         |

| • | Changed the Ordering Information table to include BQ24161B4                                                                                                                                                     |

| • | Changed text From: "battery FET (Q6)" To: "battery FET (Q4)" in the Battery Only Connected section                                                                                                              |

| • | Changed From: V <sub>WARM</sub> < V <sub>TS</sub> < V <sub>HOT</sub> To: V <sub>WARM</sub> > V <sub>TS</sub> > V <sub>HOT</sub> , and Changed From: V <sub>COLD</sub> < V <sub>TS</sub> < V <sub>COOL</sub> To: |

|   | V <sub>COLD</sub> > V <sub>TS</sub> > V <sub>COOL</sub> in the External NTC Monitoring (TS) section                                                                                                             |

| • | Changed 🗵 11-1                                                                                                                                                                                                  |

| С | hanges from Revision * (November 2011) to Revision A (March 2012) Page                                                                                                                                          |

| • | Changed the USB Pin numbers in the YFF pachkage for bq24160/3 From: A5-A6 To: A5-A74                                                                                                                            |

| • | Changed V <sub>BATREG</sub> - Voltage regulation accuracy                                                                                                                                                       |

| • | Changed 🗵 9-1                                                                                                                                                                                                   |

| • | Changed 🗵 9-2                                                                                                                                                                                                   |

# **5** Device Comparison Table

| PART NUMBER <sup>(1)</sup> (2) | USB OVP | IN OVP | USB DETECTION             | TIMERS<br>(Safety and<br>Watchdog) | NTC<br>MONITORING | V <sub>BATSHRT</sub> /<br>I <sub>BATSHRT</sub> | V <sub>MINSYS</sub> |

|--------------------------------|---------|--------|---------------------------|------------------------------------|-------------------|------------------------------------------------|---------------------|

| BQ24160                        | 6.5V    | 10.5V  | D+/D-                     | Yes                                | JEITA             | 3.0V<br>50mA                                   | 3.5V                |

| BQ24160A                       | 6.5V    | 10.5V  | D+/D-                     | No                                 | JEITA             | 3.0V<br>50mA                                   | 3.5V                |

| BQ24161                        | 6.5V    | 10.5V  | PSEL (0=1.5A,<br>1=100mA) | Yes                                | Standard          | 2.0V<br>50mA                                   | 3.5V                |

| BQ24161B                       | 6.5V    | 10.5V  | PSEL (0=1.5A,<br>1=500mA) | Yes                                | JEITA             | 3.0V<br>50mA                                   | 3.5V                |

| BQ24163                        | 6.5V    | 10.5V  | D+/D-                     | Yes                                | JEITA             | 2.0V<br>50mA                                   | 3.2V                |

| BQ24168                        | 6.5V    | 6.5V   | PSEL (0=1.5A,<br>1=100mA) | No                                 | JEITA             | 2.0V<br>50mA                                   | 3.5V                |

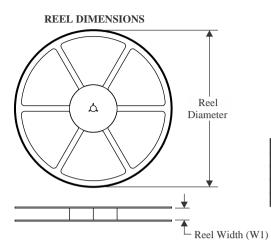

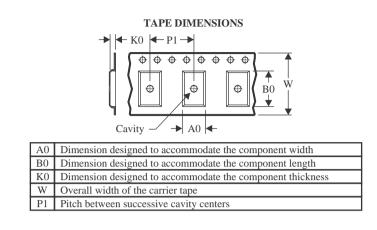

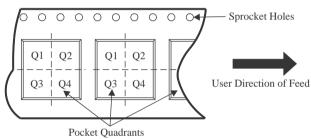

(1) Each of the above are available in as YFF and RGE packages with the following options:

R - tabed and reeled in quantities of 3,000 devices per reel.

T - taped and reeled in quantities of 250 devices per reel.

(2) This product is RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and is suitable for use in specified lead-free soldering processes. In addition, this product uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

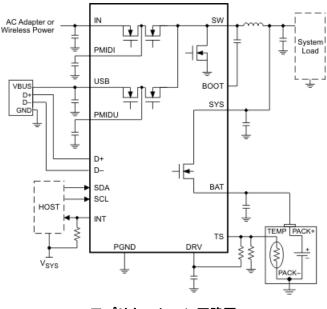

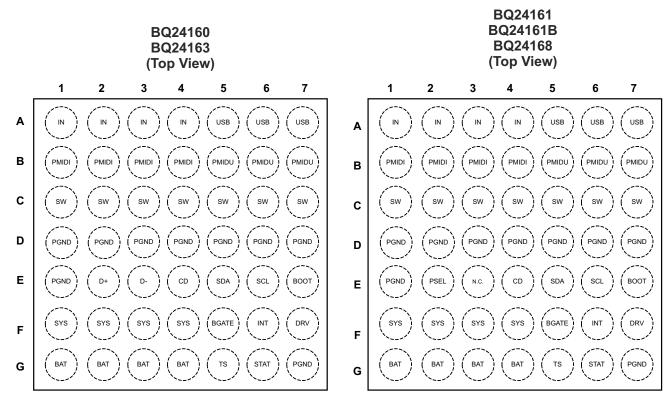

# **6** Pin Configuration and Functions

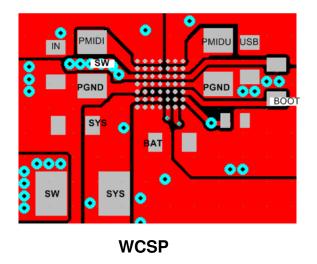

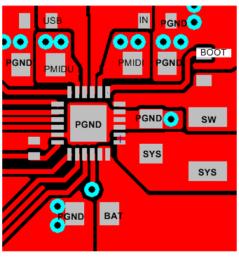

図 6-2. YFF Package WCSP 49 Pins Top View

#### 表 6-1. Pin Functions

| PIN   |                   |                  |                       |                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|-------|-------------------|------------------|-----------------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME  | NO.<br>BQ24160, 3 |                  | NO.<br>BQ24161, 1B, 8 |                  | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|       | YFF               | RGE              | YFF                   | RGE              |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| BAT   | G1-G4             | 11, 12           | G1-G4                 | 11, 12           | I/O | Battery Connection – Connect to the positive terminal of the battery. Additionally, bypass BAT to GND with at least a 1- $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| BGATE | F5                | 10               | F5                    | 10               | 0   | <b>External Discharge MOSFET Gate Connection –</b> BGATE drives an external P-Channel MOSFET to provide a very low-resistance discharge path. Connect BGATE to the gate of the external MOSFET. BGATE is low during high impedance mode and when no input is connected.                                                                                                                                                                                                      |  |  |  |

| BOOT  | E7                | 19               | E7                    | 19               | I   | <b>High Side MOSFET Gate Driver Supply –</b> Connect a 0.01-µF ceramic capacitor (voltage rating > 10 V) from BOOT to SW to supply the gate drive for the high side MOSFETs.                                                                                                                                                                                                                                                                                                 |  |  |  |

| CD    | E4                | 24               | E4                    | 24               | I   | IC Hardware Chip Disable Input – Drive CD high to place the BQ2416xx in high-z mode. Drive CD low for normal operation. Do not leave CD unconnected.                                                                                                                                                                                                                                                                                                                         |  |  |  |

| D+    | E2                | 2                | _                     | —                | I   | D+ and D- Connections for USB Input Adapter Detection - When a charge cycle is initiated                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| D-    | E3                | 1                | _                     | _                | I   | by the USB input, and a short is detected between D+ and D–, the USB input current limit is set<br>o 1.5 A. If a short is not detected, the USB100 mode is selected. The D+/D– detection has no<br>offect on the IN input.                                                                                                                                                                                                                                                   |  |  |  |

| DRV   | F7                | 6                | F7                    | 6                | 0   | <b>Gate Drive Supply</b> – DRV is the bias supply for the gate drive of the internal MOSFETs.<br>Bypass DRV to PGND with a 1- $\mu$ F ceramic capacitor. DRV may be used to drive external loads up to 10 mA. DRV is active whenever the input is connected and V <sub>SUPPLY</sub> > V <sub>UVLO</sub> and V <sub>SUPPLY</sub> > (V <sub>BAT</sub> + V <sub>SLP</sub> )                                                                                                     |  |  |  |

| IN    | A1- A4            | 21               | A1- A4                | 21               | I   | <b>Input power supply</b> – IN is connected to the external DC supply (AC adapter or alternate power source). Bypass IN to PGND with at least a 1-µF ceramic capacitor.                                                                                                                                                                                                                                                                                                      |  |  |  |

| INT   | F6                | 7                | F6                    | 7                | 0   | <b>Status Output –</b> INT is an open-drain output that signals charging status and fault interrupts.<br>NT pulls low during charging. INT is high impedance when charging is complete or the charger<br>s disabled. When a fault occurs, a 128-μs pulse is sent out as an interrupt for the host. INT is<br>enabled/disabled using the EN_STAT bit in the control register. Connect INT to a logic rail<br>hrough a 100-kΩ resistor to communicate with the host processor. |  |  |  |

| PGND  | D1-D7,<br>E1, G7  | 5, 15,<br>16, 17 | D1-D7,<br>E1, G7      | 5, 15,<br>16, 17 | —   | <b>Ground terminal –</b> Connect to the thermal pad (for VQFN only) and the ground plane of the circuit.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

DIN

#### 表 6-1. Pin Functions (continued)

| PIN            |                   |        |                       |       |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|----------------|-------------------|--------|-----------------------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME           | NO.<br>BQ24160, 3 |        | NO.<br>BQ24161, 1B, 8 |       | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                | YFF               | RGE    | YFF                   | RGE   | 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| PMIDI          | B1-B4             | 20     | B1-B4                 | 20    | 0   | <b>Reverse Blocking MOSFET and High Side MOSFET Connection Point for High Power</b><br><b>Input –</b> Bypass PMIDI to GND with at least a 4.7-μF ceramic capacitor. Use caution when<br>connecting an external load to PMIDI. The PMIDI output is not current limited. Any short on<br>PMIDI will damage the IC.                                                                                                                                                                                                               |  |  |  |

| PMIDU          | B5-B7             | 23     | B5-B7                 | 23    | 0   | Reverse Blocking MOSFET and High Side MOSFET Connection Point for USB Input – Bypass PMIDU to GND with at least a 4.7- $\mu$ F ceramic capacitor. Use caution when connecting an external load to PMIDU. The PMIDU output is not current limited. Any short on PMIDU will damage the IC.                                                                                                                                                                                                                                       |  |  |  |

| PSEL           | _                 | _      | E2                    | 2     |     | <b>JSB Source Detection Input –</b> Drive PSEL high to indicate that a USB source is connected to he USB input. When PSEL is high, the IC starts up with a 100 mA (BQ24161/8) or 500 mA BQ24161B) input current limit for USB. Drive PSEL low to indicate that an AC Adapter is connected to the USB input. When PSEL is low, the IC starts up with a 1.5 A input current limit or USB. PSEL has no effect on the IN input. Do not leave PSEL unconnected.                                                                     |  |  |  |

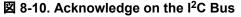

| SCL            | E6                | 3      | E6                    | 3     | 1   | I <sup>2</sup> C Interface Clock – Connect SCL to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| SDA            | E5                | 4      | E5                    | 4     | I/O | I <sup>2</sup> C Interface Data – Connect SDA to the logic rail through a 10-kΩ resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| STAT           | G6                | 8      | G6                    | 8     | 0   | <b>Status Output</b> – STAT is an open-drain output that signals charging status and fault interrupts.<br>STAT pulls low during charging. STAT is high impedance when charging is complete or the charger is disabled. When a fault occurs, a 128-µs pulse is sent out as an interrupt for the host.<br>STAT is enabled /disabled using the EN_STAT bit in the control register. Pull STAT up to a logic rail thruogh an LED for visual indication or through a 10-k $\Omega$ resistor to communicate with the host processor. |  |  |  |

| SW             | C1-C7             | 18     | C1-C7                 | 18    | 0   | Inductor Connection – Connect to the switched side of the external inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| SYS            | F1-F4             | 13, 14 | F1-F4                 | 13,14 | I   | System Voltage Sense and Charger FET Connection – Connect SYS to the system output at the output bulk capacitors. Bypass SYS locally with at least 10 $\mu$ F. A 47- $\mu$ F bypass capacitor is recommended for optimal transient response.                                                                                                                                                                                                                                                                                   |  |  |  |

| TS             | G5                | 9      | G5                    | 9     | I   | <b>Battery Pack NTC Monitor –</b> Connect TS to the center tap of a resistor divider from DRV to GND. The NTC is connected from TS to GND. The TS function provides 4 thresholds for JEITA compatibility (160, 161B, 163, 168 only). TS faults are reported by the I <sup>2</sup> C interface. See the <i>NTC Monitor</i> section for more details on operation and selecting the resistor values. Connect TS to DRV to disable the TS function.                                                                               |  |  |  |

| USB            | A5-A7             | 22     | A5-A7                 | 22    | I   | <b>USB Input Power Supply –</b> USB is connected to the external DC supply (AC adapter or USB port). Bypass USB to PGND with at least a 1-µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| Thermal<br>Pad | -                 | Pad    | _                     | Pad   | -   | There is an internal electrical connection between the exposed thermal pad and the PGND pin of the device. The thermal pad must be connected to the same potential as the PGND pin on the printed circuit board. Do not use the thermal pad as the primary ground input for the device. PGND pin must be connected to ground at all times.                                                                                                                                                                                     |  |  |  |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                      |                                                                 | MIN  | MAX | UNIT |

|--------------------------------------|-----------------------------------------------------------------|------|-----|------|

|                                      | IN, USB                                                         | -2   | 20  | V    |

| Pin voltage range (with              | PMIDI, PMIDU, BOOT                                              | -0.3 | 20  | V    |

| respect to VSS)                      | SW                                                              | -0.7 | 12  | V    |

|                                      | SDA, SCL, SYS, BAT, STAT, BGATE, DRV, TS, D+, D–, INT, PSEL, CD | -0.3 | 7   | V    |

| BOOT to SW                           |                                                                 | -0.3 | 7   | V    |

| Output ourrent (continuous)          | SW                                                              | 4.5  |     | А    |

| Output current (continuous)          | SYS, BAT                                                        | 3.5  |     | А    |

| Input current (continuous)           | IN                                                              | 2.75 |     | А    |

| input current (continuous)           | USB                                                             | 1.75 |     | А    |

| Output cink ourrant                  | STAT                                                            | 10   | 7   | mA   |

| Output sink current                  | INT                                                             | 1    |     | mA   |

| Operating free-air temperatur        | e range                                                         | -40  | 85  | °C   |

| Junction temperature, T <sub>J</sub> |                                                                 | -40  | 125 | °C   |

| Lead temperature (soldering,         | 10 s)                                                           | 300  |     | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

## 7.2 Handling Ratings

|                                            |                                                                                                |                                                                             | MIN | MAX | UNIT |

|--------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|------|

| T <sub>stg</sub>                           | T <sub>stg</sub> Storage temperature range                                                     |                                                                             | -65 | 150 | °C   |

| V <sub>(ESD)</sub> Electrostatic discharge | Electrostatic discharge                                                                        | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> |     | 2   | kV   |

|                                            | Charged device model (CDM), per JEDEC specification JESD22-C101, all $\ensuremath{pins}^{(2)}$ |                                                                             | 500 | V   |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                          | MIN | MAX | UNIT |

|------------------|------------------------------------------|-----|-----|------|

|                  | IN voltage range                         | 4.2 | 18  |      |

| V <sub>IN</sub>  | IN operating voltage range (BQ24160/1/3) | 4.2 | 10  | V    |

|                  | IN operating voltage range (BQ24168)     | 4.2 | 6   |      |

| V                | USB voltage range                        | 4.2 | 18  | V    |

| V <sub>USB</sub> | USB operating range                      | 4.2 | 6   | v    |

| I <sub>IN</sub>  | Input current, IN input                  |     | 2.5 | А    |

| I <sub>USB</sub> | Input current USB input                  |     | 1.5 | А    |

| I <sub>SYS</sub> | Output Current from SW, DC               |     | 3   | А    |

| 1                | Charging                                 |     | 2.5 | А    |

| IBAT             | Discharging, using internal battery FET  |     | 2.5 | А    |

| TJ               | Operating junction temperature range     | 0   | 125 | °C   |

## 7.4 Thermal Information

|                    | THERMAL METRIC <sup>(1)</sup>                | B             | BQ2416xx      |      |  |  |

|--------------------|----------------------------------------------|---------------|---------------|------|--|--|

|                    |                                              | 49 PINS (YFF) | 24 PINS (RGE) | UNIT |  |  |

| θ <sub>JA</sub>    | Junction-to-ambient thermal resistance       | 49.8          | 32.6          | °C/W |  |  |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 0.2           | 30.5          | °C/W |  |  |

| θ <sub>JB</sub>    | Junction-to-board thermal resistance         | 1.1           | 3.3           | °C/W |  |  |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter   | 1.1           | 0.4           | °C/W |  |  |

| Ψјв                | Junction-to-board characterization parameter | 6.6           | 9.3           | °C/W |  |  |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance | n/a           | 2.6           | °C/W |  |  |

(1) For more information about traditional and new thermal metrics, see *The IC Package Thermal Metrics Application Report*.

# 7.5 Electrical Characteristics

Circuit of  $\boxtimes$  9-1, V<sub>SUPPLY</sub> = V<sub>USB</sub> or V<sub>IN</sub> (whichever is supplying the IC), V<sub>UVLO</sub> < V<sub>SUPPLY</sub> < V<sub>OVP</sub> and V<sub>SUPPLY</sub> > V<sub>BAT</sub>+V<sub>SLP</sub>, T<sub>J</sub> = -40°C - 125°C and T<sub>J</sub> = 25°C for typical values (unless otherwise noted)

|                           | PARAMETER                                                               | TEST CONDITIONS                                                                                            |                                                   | MIN                           | TYP                           | МАХ                            | UNIT     |

|---------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------|-------------------------------|--------------------------------|----------|

| INPUT CURR                | RENTS                                                                   |                                                                                                            |                                                   |                               |                               |                                |          |

| ISUPPLY                   | Supply current for control (V <sub>IN</sub> or V <sub>USB</sub> )       | $V_{UVLO} < V_{SUPPLY} < V_{OVP}$ and $V_{SUPPLY} > V_{BAT} + V_{SLP}$                                     | PWM switching<br>PWM NOT switching                |                               | 15                            | 5                              | mA       |

| SUFFEI                    |                                                                         | 0°C < T <sub>1</sub> < 85°C, High-Z Mode                                                                   | · · · · · · · · · · · · · · · · · · ·             |                               |                               | 175                            | μA       |

| IBATLEAK                  | Leakage current from BAT to the Supply                                  | 0°C < T <sub>J</sub> < 85°C, V <sub>BAT</sub> = 4.2V, V <sub>USE</sub>                                     | <sub>B</sub> = V <sub>IN</sub> = 0V               |                               |                               | 5                              | μΑ       |

| I <sub>BAT_HIZ</sub>      | Battery discharge current in High Impedance mode,<br>(BAT, SW, SYS)     | 0°C< T <sub>J</sub> < 85°C, V <sub>BAT</sub> = 4.2V, V <sub>SUP</sub><br>SCL, SDA = 0 V or 1.8V, High-Z Mo |                                                   |                               |                               | 55                             | μA       |

| POWER-PAT                 | H MANAGEMENT                                                            |                                                                                                            |                                                   |                               |                               |                                |          |

|                           |                                                                         |                                                                                                            | BQ24160, 1, 1B, 8                                 | 3.60                          | 3.7                           | 3.82                           |          |

| V <sub>SYS(REG)</sub>     | System regulation voltage                                               | Charge Enabled, V <sub>BAT</sub> < V <sub>MINSYS</sub>                                                     | BQ24163                                           | 3.3                           | 3.4                           | 3.5                            | V        |

| * 515(REG)                |                                                                         | Battery FET turned off (Charge Dis<br>Charging Terminated)                                                 | abled, TS Fault or                                | V <sub>BATREG</sub><br>+ 1.5% | V <sub>BATREG</sub><br>+ 3.0% | V <sub>BATREG</sub><br>+ 4.17% | v        |

|                           |                                                                         | Charge enabled, V <sub>BAT</sub> < V <sub>MINSYS</sub> ,                                                   | BQ24160, 1, 1B, 8                                 | 3.4                           | 3.5                           | 3.62                           | V        |

| V <sub>MINSYS</sub>       | Minimum system regulation voltage                                       | Input current limit or VINDPM active                                                                       | BQ24163                                           | 3.1                           | 3.2                           | 3.3                            | V        |

| V <sub>BSUP1</sub>        | Enter supplement mode threshold                                         | V <sub>BAT</sub> > 2.5V                                                                                    |                                                   |                               | V <sub>BAT</sub><br>–30mV     |                                | V        |

| V <sub>BSUP2</sub>        | Exit supplement mode threshold                                          | V <sub>BAT</sub> > 2.5V                                                                                    |                                                   |                               | V <sub>BAT</sub><br>–10mV     |                                | V        |

| ILIM(discharge)           | Current limit, discharge or supplement mode                             | Current monitored in internal FET only.                                                                    |                                                   |                               | 7                             |                                | А        |

| t <sub>DGL(SC1)</sub>     | Deglitch time, SYS short circuit during discharge or<br>supplement mode | Measured from $(V_{BAT} - V_{SYS})$ = 300mV to BAT high-impedance                                          |                                                   |                               | 250                           |                                | μs       |

| t <sub>REC(SC1)</sub>     | Recovery time, SYS short circuit during discharge or supplement mode    |                                                                                                            |                                                   |                               | 60                            |                                | ms       |

|                           | Battery range for BGATE and supplement mode operation                   |                                                                                                            |                                                   | 2.5                           |                               | 4.5                            | V        |

| BATTERY CH                | HARGER                                                                  |                                                                                                            |                                                   |                               |                               |                                |          |

|                           | LA LA MARTIN                                                            | Measured from BAT to SYS,                                                                                  | YFF pkg                                           |                               | 37                            | 57                             | <u> </u> |

| R <sub>ON(BAT-SYS)</sub>  | Internal battery charger MOSFET on-resistance                           | V <sub>BAT</sub> = 4.2V                                                                                    | RGE pkg                                           |                               | 50                            | 70                             | mΩ       |

|                           | Charge Voltage                                                          | Operating in voltage regulation, Pro                                                                       | ogrammable range                                  | 3.5                           |                               | 4.44                           | V        |

| VBATREG                   | Voltage regulation accuracy                                             |                                                                                                            |                                                   | -1%                           |                               | 1%                             |          |

|                           | Fast charge current range                                               | V <sub>BATSHRT</sub> ≤ V <sub>BAT</sub> < V <sub>BAT(REG)</sub> progra                                     | ammable range                                     | 550                           |                               | 2500                           | mA       |

| CHARGE                    | Fast charge current accuracy                                            | 0°C to 125°C                                                                                               |                                                   | -10%                          |                               | +10%                           |          |

| V                         | Battery short circuit threshold                                         | 100mV Hysteresis                                                                                           | BQ24161, 3, 8                                     | 1.9                           | 2.0                           | 2.1                            | V        |

| VBATSHRT                  |                                                                         |                                                                                                            | BQ24160, 1B                                       | 2.9                           | 3.0                           | 3.1                            | v        |

| IBATSHRT                  | Battery short circuit current                                           | V <sub>BAT</sub> < V <sub>BATSHRT</sub>                                                                    |                                                   |                               | 50                            |                                | mA       |

| t <sub>DGL(BATSHRT)</sub> | Deglitch time for battery short circuit to fastcharge transition        |                                                                                                            |                                                   |                               | 32                            |                                | ms       |

|                           |                                                                         | I <sub>TERM</sub> = 50mA                                                                                   |                                                   | -40%                          |                               | +40%                           |          |

| ITERM                     | Termination charge current accuracy                                     | I <sub>TERM</sub> = 100mA                                                                                  |                                                   | -20%                          |                               | +20%                           |          |

|                           |                                                                         | I <sub>TERM</sub> ≥ 150mA                                                                                  |                                                   | -15%                          |                               | +15%                           |          |

| t <sub>DGL(TERM)</sub>    | Deglitch time for charge termination                                    | Both rising and falling, 2mV overdri                                                                       | ive, t <sub>RISE,</sub> t <sub>FALL</sub> = 100ns |                               | 32                            |                                | ms       |

# 7.5 Electrical Characteristics (continued)

Circuit of  $\boxtimes$  9-1, V<sub>SUPPLY</sub> = V<sub>USB</sub> or V<sub>IN</sub> (whichever is supplying the IC), V<sub>UVLO</sub> < V<sub>SUPPLY</sub> < V<sub>OVP</sub> and V<sub>SUPPLY</sub> > V<sub>BAT</sub>+V<sub>SLP</sub>, T<sub>J</sub> = -40°C - 125°C and T<sub>J</sub> = 25°C for typical values (unless otherwise noted)

|                        | PARAMETER                                                                     | TEST CONDI                                                                                                                                               | TIONS                        | MIN                 | TYP                            | MAX     | UNIT      |

|------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------|--------------------------------|---------|-----------|

| V <sub>RCH</sub>       | Recharge threshold voltage                                                    | Below V <sub>BATREG</sub>                                                                                                                                |                              |                     | 120                            |         | mV        |

| DGL(RCH)               | Deglitch time                                                                 | VBAT falling below VRCH, tFALL=                                                                                                                          | =100ns                       |                     | 32                             |         | ms        |

| <b>V</b> DETECT        | Battery detection threshold                                                   | During battery detection source cy                                                                                                                       | /cle                         |                     | 3.3                            |         | V         |

|                        |                                                                               | During battery detection sink cycle                                                                                                                      | e                            |                     | 3.0                            |         |           |

| DETECT                 | Battery detection current before charge done (sink current)                   | Termination enabled (EN_TERM = 1)                                                                                                                        |                              |                     | 2.5                            |         | mA        |

| DETECT                 | Battery detection time                                                        | Termination enabled (EN_TERM =                                                                                                                           | = 1)                         |                     | 250                            |         | ms        |

| VIH                    | PSEL, CD Input high logic level                                               |                                                                                                                                                          |                              | 1.3                 |                                |         | V         |

| V <sub>IL</sub>        | PSEL, CD Input low logic level                                                |                                                                                                                                                          |                              |                     |                                | 0.4     | V         |

|                        | RENT LIMITING                                                                 |                                                                                                                                                          |                              |                     |                                |         |           |

|                        |                                                                               |                                                                                                                                                          | I <sub>USBLIM</sub> = USB100 | 90                  | 95                             | 100     |           |

|                        |                                                                               |                                                                                                                                                          | I <sub>USBLIM</sub> = USB500 | 450                 | 475                            | 500     |           |

|                        | Input current limit threshold (USB input)                                     | USB charge mode, V <sub>USB</sub> = 5V,                                                                                                                  | I <sub>USBLIM</sub> = USB150 | 135                 | 142.5                          | 150     |           |

| I <sub>IN_USB</sub>    |                                                                               | DC Current pulled from SW                                                                                                                                | I <sub>USBLIM</sub> = USB900 | 800                 | 850                            | 900     | mA        |

|                        |                                                                               |                                                                                                                                                          | I <sub>USBLIM</sub> = USB800 | 700                 | 750                            | 800     |           |

|                        |                                                                               |                                                                                                                                                          | I <sub>USBLIM</sub> = 1.5A   | 1250                | 1400                           | 1500    |           |

|                        |                                                                               | IN charge mode, V <sub>IN</sub> = 5V,                                                                                                                    | I <sub>INLIM</sub> = 1.5A    | 1.35                | 1.5                            | 1.65    |           |

| I <sub>IN_IN</sub>     | Input current limit threshold (IN input)                                      | DC Current pulled from SW                                                                                                                                |                              | 2.3                 | 2.5                            | 2.8     | А         |

| V                      | Input based DPM threshold range                                               | Chargo modo, programmable via                                                                                                                            | $I_{\rm INLIM} = 2.5A$       |                     | 2.5                            | 4.76    | V         |

| V <sub>IN_DPM</sub>    | Input based DPM threshold range                                               | Charge mode, programmable via                                                                                                                            | I-C, both inputs             | 4.2                 |                                |         | v         |

|                        | V <sub>IN_DPM</sub> threshold accuracy                                        |                                                                                                                                                          |                              | -2                  |                                | +2%     |           |

|                        | REGULATOR                                                                     |                                                                                                                                                          |                              |                     |                                |         |           |

| V <sub>DRV</sub>       | Internal bias regulator voltage                                               | V <sub>SUPPLY</sub> > 5.45V                                                                                                                              |                              | 5                   | 5.2                            | 5.45    | V         |

| I <sub>DRV</sub>       | DRV output current                                                            |                                                                                                                                                          |                              | 10                  |                                |         | mA        |

| V <sub>DO_DRV</sub>    | DRV Dropout voltage (V <sub>SUPPLY</sub> – V <sub>DRV</sub> )                 | I <sub>SUPPLY</sub> = 1A, V <sub>SUPPLY</sub> = 5V, I <sub>DRV</sub> =                                                                                   | = 10mA                       |                     |                                | 450     | mV        |

| STATUS OUT             | TPUT ( STAT, INT)                                                             | Т                                                                                                                                                        |                              |                     |                                |         |           |

| V <sub>OL</sub>        | Low-level output saturation voltage                                           | I <sub>O</sub> = 10mA, sink current                                                                                                                      |                              |                     |                                | 0.4     | V         |

| l <sub>IH</sub>        | High-level leakage current                                                    | $V_{STAT} = V_{INT} = 5V$                                                                                                                                |                              |                     |                                | 1       | μA        |

| PROTECTIO              | N                                                                             |                                                                                                                                                          |                              |                     |                                |         |           |

| V <sub>UVLO</sub>      | IC active threshold voltage                                                   | V <sub>IN</sub> rising                                                                                                                                   |                              | 3.6                 | 3.8                            | 4       | V         |

| V <sub>UVLO_HYS</sub>  | IC active hysteresis                                                          | $V_{\text{IN}}$ falling from above $V_{\text{UVLO}}$                                                                                                     |                              | 120                 | 150                            |         | mV        |

| V <sub>SLP</sub>       | Sleep-mode entry threshold, V <sub>SUPPLY</sub> -V <sub>BAT</sub>             | 2.0V ≤V <sub>BAT</sub> ≤V <sub>BATREG</sub> , V <sub>IN</sub> falling                                                                                    |                              | 0                   | 40                             | 100     | mV        |

| V <sub>SLP_EXIT</sub>  | Sleep-mode exit hysteresis                                                    | 2.0V ≤V <sub>BAT</sub> ≤V <sub>BATREG</sub>                                                                                                              |                              | 40                  | 100                            | 175     | mV        |

|                        | Deglitch time for supply rising above V <sub>SLP</sub> +V <sub>SLP_EXIT</sub> | Rising voltage, 2mV over drive, t <sub>R</sub>                                                                                                           | <sub>ISE</sub> = 100ns       |                     | 30                             |         | ms        |

|                        |                                                                               | After Bad Source Detection comp                                                                                                                          | letes                        |                     | V <sub>IN_DPM</sub><br>– 80 mV |         | V         |

| VBAD_SOURCE            | Bad source detection threshold                                                | During Bad Source Detection                                                                                                                              |                              |                     | V <sub>IN_DPM</sub><br>+ 80 mV |         | V         |

| t <sub>DGL(BSD)</sub>  | Deglitch on bad source detection                                              |                                                                                                                                                          |                              |                     | 32                             |         | ms        |

|                        |                                                                               | USB, V <sub>USB</sub> Rising                                                                                                                             |                              | 6.3                 | 6.5                            | 6.7     |           |

| V <sub>OVP</sub>       | Input supply OVP threshold voltage                                            | IN, V <sub>IN</sub> Rising (BQ24160/1/1B/3)                                                                                                              |                              | 10.3                | 10.5                           | 10.7    | v         |

|                        |                                                                               | IN, V <sub>IN</sub> Rising (BQ24168)                                                                                                                     |                              | 6.3                 | 6.5                            | 6.7     |           |

| V <sub>OVP(HYS)</sub>  | V <sub>OVP</sub> hysteresis                                                   | Supply falling from V <sub>OVP</sub>                                                                                                                     |                              |                     | 100                            |         | mV        |

|                        |                                                                               |                                                                                                                                                          |                              | 1.025 ×             | 1.05 ×                         | 1.075 × |           |

| VBOVP                  | Battery OVP threshold voltage                                                 | V <sub>BAT</sub> threshold over V <sub>OREG</sub> to turn                                                                                                | off charger during charge    | V <sub>BATREG</sub> | VBATREG                        | VBATREG | V<br>% of |

|                        | V <sub>BOVP</sub> hysteresis                                                  | Lower limit for V <sub>BAT</sub> falling from above V <sub>BOVP</sub>                                                                                    |                              |                     | 1                              |         | VBATREG   |

| t <sub>DGL(BOVP)</sub> | Battery OVP deglitch                                                          | BOVP fault shown in register once t <sub>DGL(BOVP)</sub> expires.<br>Buck converter shut down immediately when V <sub>BAT</sub> ><br>V <sub>BATOVP</sub> |                              |                     | 1                              |         | ms        |

| VBATUVLO               | Battery undervoltage lockout threshold                                        | V <sub>BAT</sub> rising, 100mV hysteresis                                                                                                                |                              |                     | 2.5                            |         | V         |

| LIMIT                  | Cycle-by-cycle current limit                                                  | V <sub>SYS</sub> shorted                                                                                                                                 |                              | 4.1                 | 4.9                            | 5.6     | А         |

| T <sub>SHTDWN</sub>    | Thermal trip                                                                  |                                                                                                                                                          |                              |                     | 165                            |         | °C        |

|                        | Thermal hysteresis                                                            |                                                                                                                                                          |                              |                     | 10                             |         |           |

|                        |                                                                               | 1                                                                                                                                                        |                              |                     |                                |         |           |

| T <sub>REG</sub>       | Thermal regulation threshold                                                  | Charge current begins to cut off                                                                                                                         |                              |                     | 120                            |         | °C        |

# 7.5 Electrical Characteristics (continued)

Circuit of  $\boxtimes$  9-1, V<sub>SUPPLY</sub> = V<sub>USB</sub> or V<sub>IN</sub> (whichever is supplying the IC), V<sub>UVLO</sub> < V<sub>SUPPLY</sub> < V<sub>OVP</sub> and V<sub>SUPPLY</sub> > V<sub>BAT</sub>+V<sub>SLP</sub>, T<sub>J</sub> = -40°C - 125°C and T<sub>J</sub> = 25°C for typical values (unless otherwise noted)

|                         | PARAMETER                                          | TEST CONDITIONS                                           | MIN   | TYP  | MAX  | UNIT              |  |

|-------------------------|----------------------------------------------------|-----------------------------------------------------------|-------|------|------|-------------------|--|

| PWM                     |                                                    |                                                           |       |      |      |                   |  |

|                         | Internal top reverse blocking MOSFET on-resistance | I <sub>IN_LIMIT</sub> = 500mA, Measured from USB to PMIDU |       | 95   | 175  | mΩ                |  |

|                         |                                                    | I <sub>IN_LIMIT</sub> = 500mA, Measured from IN to PMIDI  |       | 45   | 80   | 11152             |  |

|                         | Internal top N-channel Switching MOSFET on-        | Measured from PMIDU to SW                                 |       | 100  | 175  | mΩ                |  |

|                         | resistance                                         | Measured from PMIDI to SW                                 |       | 65   | 110  | 11152             |  |

|                         | Internal bottom N-channel MOSFET on-resistance     | Measured from SW to PGND                                  |       | 65   | 115  | mΩ                |  |

| f <sub>OSC</sub>        | Oscillator frequency                               |                                                           | 1.35  | 1.50 | 1.65 | MHz               |  |

| D <sub>MAX</sub>        | Maximum duty cycle                                 |                                                           |       | 95%  |      |                   |  |

| D <sub>MIN</sub>        | Minimum duty cycle                                 |                                                           | 0%    |      |      |                   |  |

| BATTERY-PA              | ACK NTC MONITOR                                    | 1                                                         | -     |      | I    |                   |  |

| V <sub>HOT</sub>        | High temperature threshold                         | V <sub>TS</sub> falling                                   | 29.7  | 30   | 30.5 | 0/1/              |  |

| V <sub>HYS(HOT)</sub>   | Hysteresis on high threshold                       | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |  |

| VWARM                   | High temperature threshold                         | V <sub>TS</sub> falling                                   | 37.9  | 38.3 | 39.6 |                   |  |

| V <sub>HYS(WARM)</sub>  | Hysteresis on high threshold                       | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |  |

| V <sub>COOL</sub>       | Low temperature threshold                          | V <sub>TS</sub> falling                                   | 56    | 56.5 | 56.9 |                   |  |

| V <sub>HYS(COOL)</sub>  | Hysteresis on low threshold                        | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |  |

| V <sub>COLD</sub>       | Low temperature threshold                          | V <sub>TS</sub> falling                                   | 59.5  | 60   | 60.4 |                   |  |

| V <sub>HYS(COLD)</sub>  | Hysteresis on low threshold                        | V <sub>TS</sub> rising                                    |       | 1    |      | %V <sub>DRV</sub> |  |

| TSOFF                   | TS Disable threshold                               | V <sub>TS</sub> rising, 2%V <sub>DRV</sub> hysteresis     | 70    |      | 73   | %V <sub>DRV</sub> |  |

| t <sub>DGL(TS)</sub>    | Deglitch time on TS change                         |                                                           |       | 50   |      | ms                |  |

|                         | CTION (bq24160)                                    |                                                           |       |      |      |                   |  |

| V <sub>D+_SRC</sub>     | D+ Voltage Source                                  |                                                           | 0.5   | 0.6  | 0.7  | V                 |  |

| ID+_SRC                 | D+ Connection Check Current Source                 |                                                           | 7     |      | 14   | μA                |  |

| I <sub>DSINK</sub>      | D- Current Sink                                    |                                                           | 50    | 100  | 150  | μA                |  |

| I <sub>D_LKG</sub>      |                                                    | D–, switch open                                           | -1    |      | 1    | μA                |  |

| -                       | Leakage Current into D+/D-                         | D+, switch open                                           | -1    |      | 1    | μA                |  |

| V <sub>D+ LOW</sub>     | D+ Low Comparator Threshold                        |                                                           | 0.8   |      |      | V                 |  |

| V <sub>DLOWdatref</sub> | D- Low Comparator Threshold                        |                                                           | 250   |      | 400  | mV                |  |

| R <sub>DDWN</sub>       | D- Pulldown for Connection Check                   |                                                           | 14.25 |      | 24.8 | kΩ                |  |

| BATGD OPE               | RATION                                             |                                                           |       |      |      |                   |  |

| VBATGD                  | Good Battery threshold                             |                                                           | 3.6   | 3.8  | 3.9  | V                 |  |

|                         | Deglitch for good battery threshold                | V <sub>BAT</sub> rising to HIGH-Z mode, DEFAULT Mode Only |       | 32   |      | ms                |  |

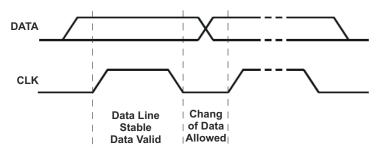

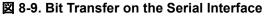

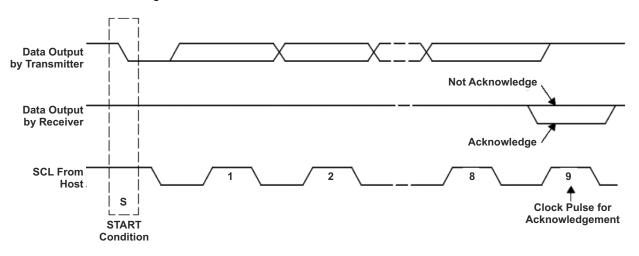

| I <sup>2</sup> C COMPAT |                                                    |                                                           |       |      |      |                   |  |

| VIH                     | Input low threshold level                          | V <sub>PULL-UP</sub> = 1.8V, SDA and SCL                  | 1.3   |      |      | V                 |  |

| VIL                     | Input low threshold level                          | V <sub>PULL-UP</sub> = 1.8V, SDA and SCL                  |       |      | 0.4  | V                 |  |

| V <sub>OL</sub>         | Output low threshold level                         | I <sub>L</sub> = 10mA, sink current                       |       |      | 0.4  | V                 |  |

| IBIAS                   | High-Level leakage current                         | V <sub>PULL-UP</sub> = 1.8V, SDA and SCL                  |       | 1    |      | μA                |  |

|                         | -                                                  |                                                           |       |      |      | -                 |  |

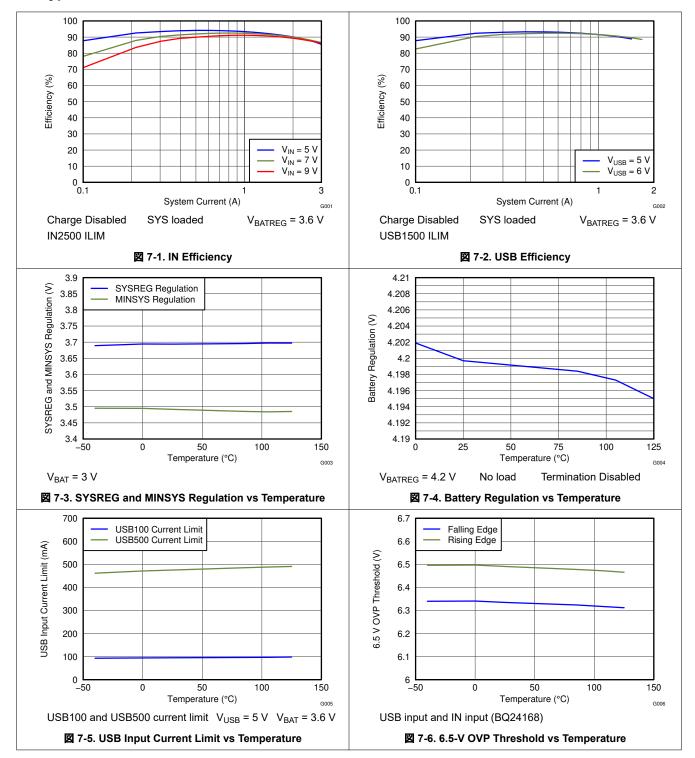

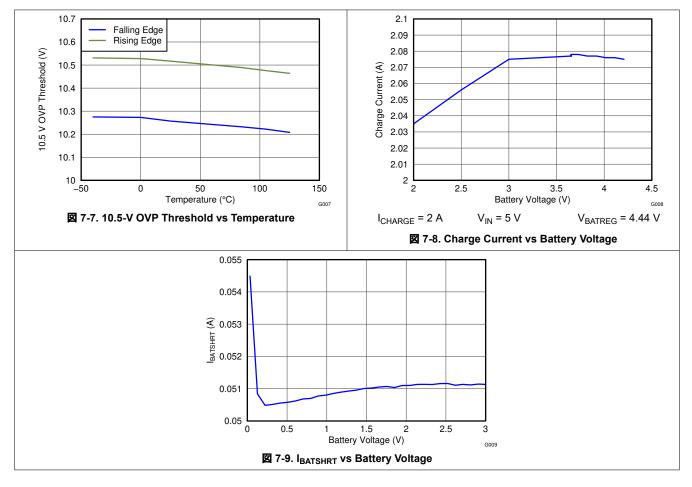

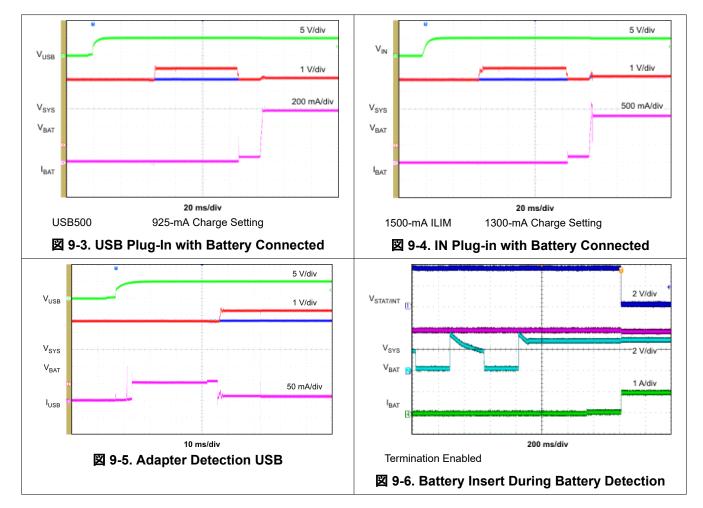

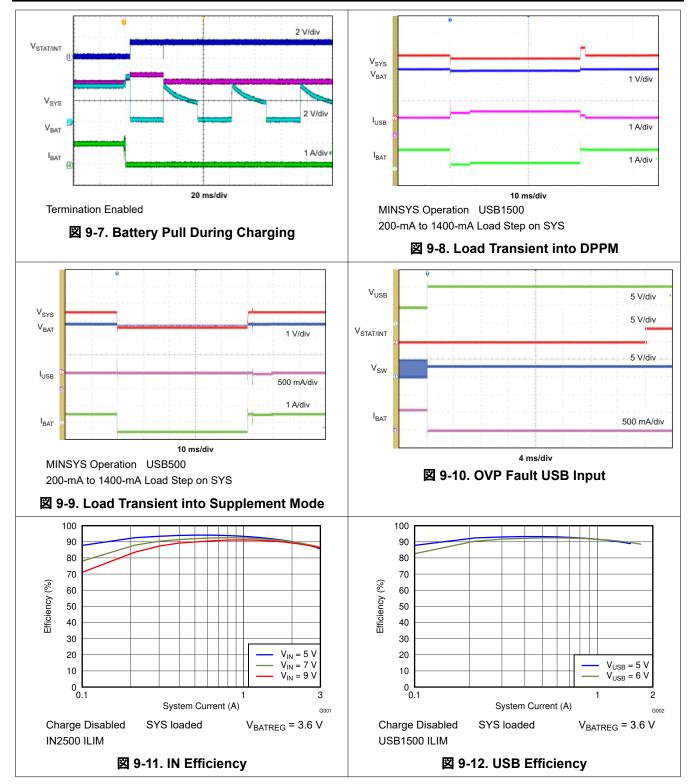

## 7.6 Typical Characteristics

## 7.6 Typical Characteristics (continued)

# 8 Detailed Description

## 8.1 Overview

The BQ24160/BQ24160A/BQ24161/BQ24161B/BQ24163/BQ24168 devices are highly integrated single-cell Lilon battery chargers and system power path management devices targeted for space-limited, portable applications with high-capacity batteries. The dual-input, single-cell charger operates from either a USB port or alternate power source (that is, wall adapter or wireless power input) for a versatile solution.

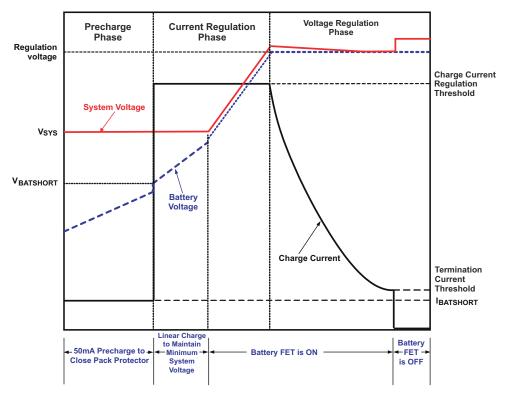

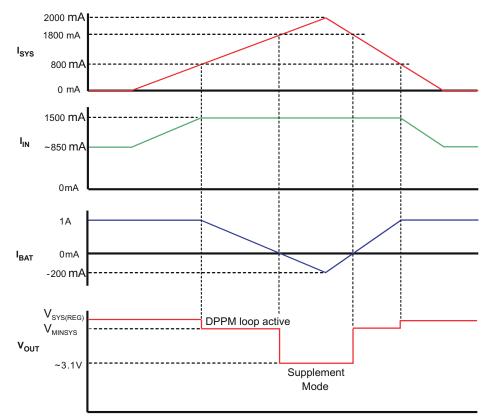

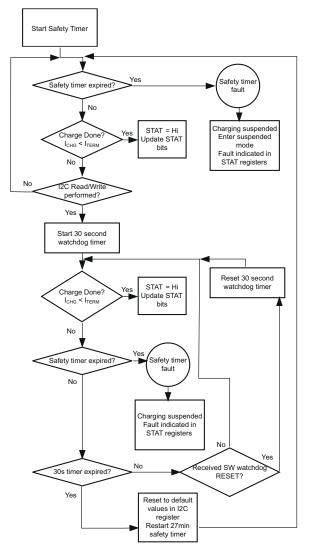

The power path management feature allows the BQ2416xx to power the system from a high-efficiency DC-DC converter while simultaneously and independently charging the battery. The charger monitors the battery current at all times and reduces the charge current when the system load requires current above the input current limit. This allows proper charge termination and enables the system to run with a defective or absent battery pack. Additionally, this enables instant system turnon even with a totally discharged battery or no battery. The power-path management architecture also permits the battery to supplement the system current requirements when the adapter cannot deliver the peak system currents. This enables the use of a smaller adapter. The 2.5-A current capability allows for GSM phone calls as soon as the adapter is plugged in regardless of the battery voltage. The charge parameters are programmable using the l<sup>2</sup>C interface.

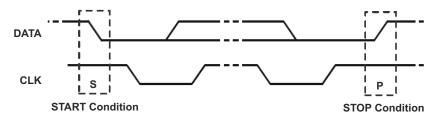

#### 8.2 Functional Block Diagram

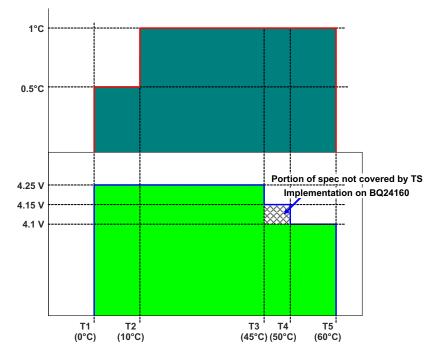

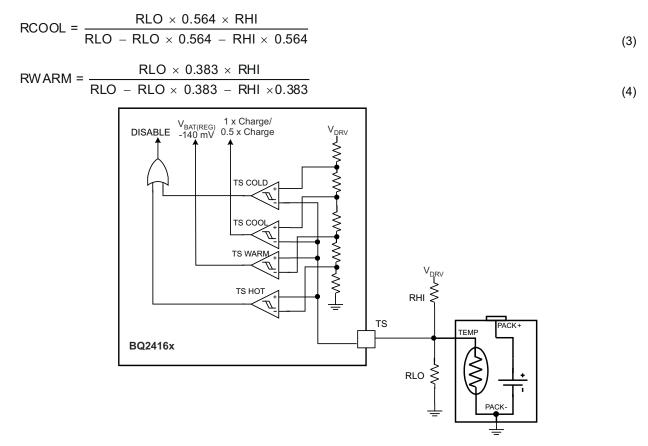

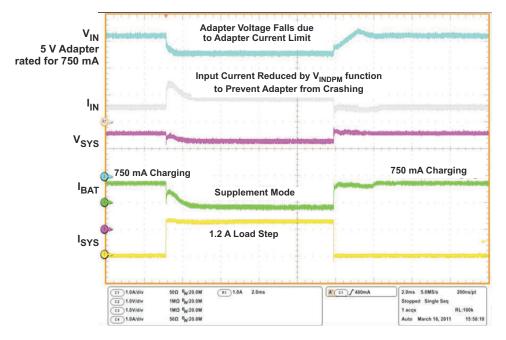

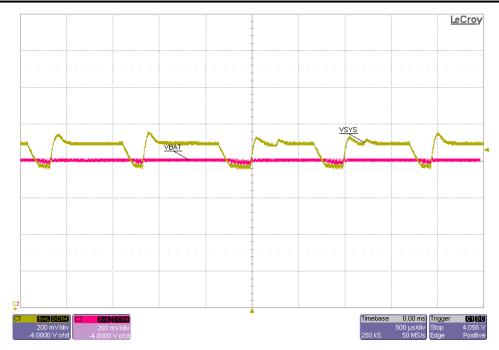

## 8.3 Feature Description