bq25570

JAJSGQ0G -MARCH 2013-REVISED MARCH 2019

# bq25570 エネルギー・ハーベスト駆動アプリケーション用の ナノパワー昇圧充電器および降圧コンバータ

# 特長

#### 超低消費電力のDC-DC昇圧充電器

- コールド・スタート電圧: V<sub>IN</sub> ≥ 600mV

- 最小100mVのVINでエネルギー・ハーベストを継

- 入力電圧のレギュレーションにより、高インピーダン ス入力源の過度の電圧低下を防止

- 全動作モードの静止電流:488nA(標準値)

- シップ・モードのバッテリ電流:5nA未満

#### エネルギー・ストレージ

- 充電可能なリチウムイオン・バッテリ、薄膜バッテリ、 スーパーキャパシタ、従来型コンデンサにエネル ギーを蓄積可能

#### バッテリの充電と保護

- 内部で設定済みの低電圧レベル

- ユーザーがプログラム可能な過電圧レベル

#### バッテリ・グッド出力フラグ

- プログラム可能なスレッショルドとヒステリシス

- 接続されたマイクロコントローラに電力消失を未然 に警告

- システム負荷のイネーブル/ディセーブルに使用可

#### プログラム可能な降圧レギュレート出力

- 最大93%の高効率

- 最大110mAのピーク出力電流をサポート(標準 値)

# プログラム可能な最大電力点追従(MPPT)

ソーラー・パネル、サーマルおよび圧電発電器など の各種エネルギー・ハーベスタからエネルギーを 最適抽出

# 2 アプリケーション

- エネルギー・ハーベスト

- ソーラー充電器

- 熱電発電器(TEG)によるハーベスト

- ワイヤレス・センサ・ネットワーク(WSN)

- 低消費電力のワイヤレス・モニタ

- 環境モニタ

- 橋梁および構造健全性モニタ(SHM)

- スマート・ビルディング制御

- ポータブルおよびウェアラブル健康管理機器

- エンターテインメント・システムのリモート制御

# 3 概要

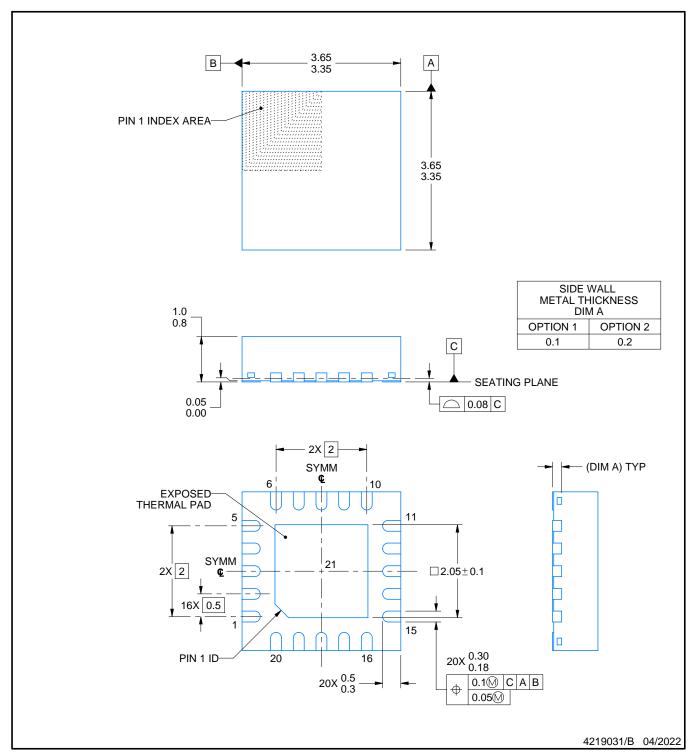

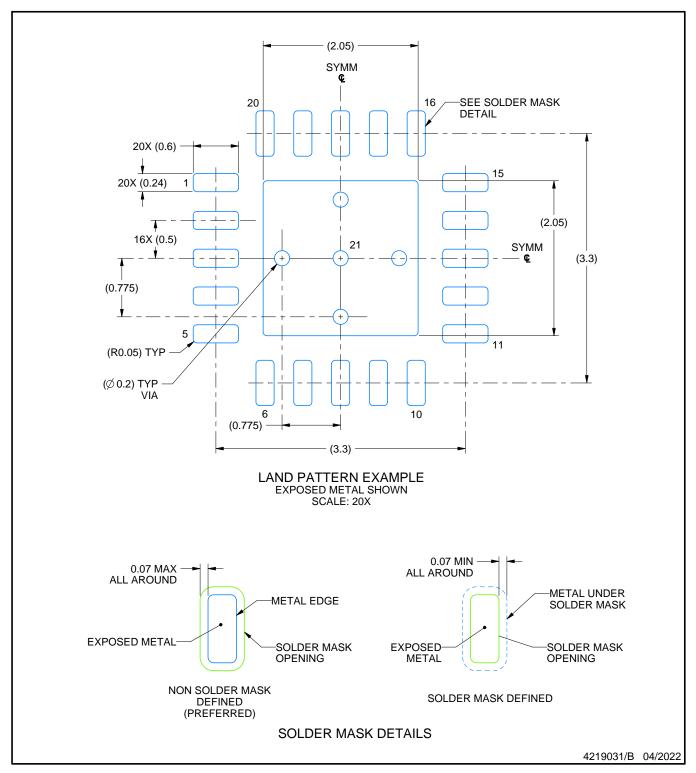

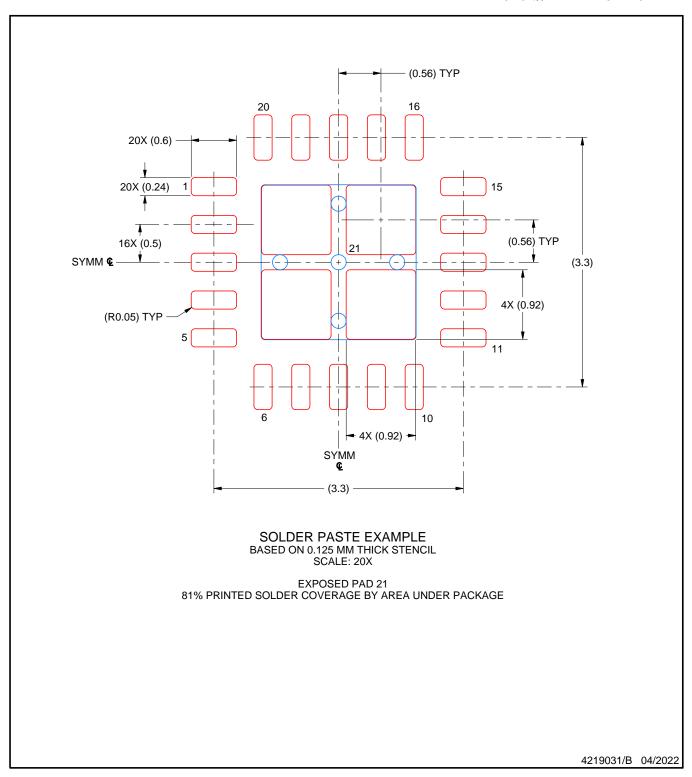

bq25570デバイスは、光電池(ソーラーパネル)または熱 電発電器(TEG)などの高インピーダンス出力の各種DC 源から、それらの出力電圧を過度に低下させないでマイク ロワット(µW)からミリワット(mW)級の電力を効率的に抽出 することに特化して設計されています。バッテリ管理機能 により、この抽出された昇圧電力によって充電可能バッテ リが過充電されず、システム負荷による安全制限を超えて 過放電もされないことが保証されます。 bg25570は、高効 率の昇圧充電器に加えて、高効率のナノパワー降圧コン バータを内蔵しており、電力や運用に関する要求が厳し いワイヤレス・センサ・ネットワーク(WSN)などのシステム向 けに第2の電源レールを提供します。bg25570のすべての 機能が、小型(3.5mm x 3.5mm)の20ピンQFNパッケージ (RGR)に搭載されています。

#### 製品情報(1)

| 型番      | パッケージ     | 本体サイズ(公称)     |

|---------|-----------|---------------|

| bq25570 | VQFN (20) | 3.50mm×3.50mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

# 代表的なアプリケーション回路図

#### 充電器の効率と入力電圧との関係

| `h- |

|-----|

|     |

|     |

| 1 | 特長1                                  | 8 Application and Implementation | 22 |

|---|--------------------------------------|----------------------------------|----|

| 2 | アプリケーション1                            | 8.1 Application Information      |    |

| 3 | 概要1                                  | 8.2 Typical Applications         |    |

| 4 | 改訂履歴2                                | 9 Power Supply Recommendations   | 34 |

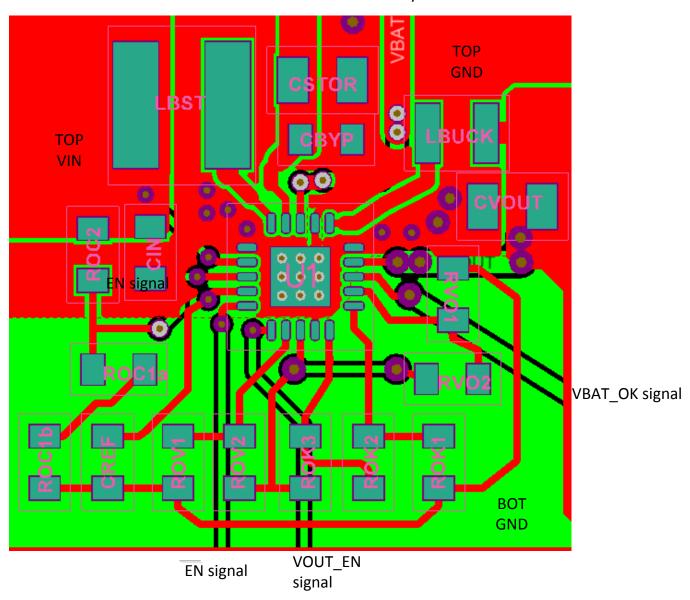

| 5 | Pin Configuration and Functions 4    | 10 Layout                        | 34 |

| 6 | Specifications5                      | 10.1 Layout Guidelines           | 34 |

| • | 6.1 Absolute Maximum Ratings         | 10.2 Layout Example              | 35 |

|   | 6.2 ESD Ratings5                     | 10.3 Thermal Considerations      | 36 |

|   | 6.3 Recommended Operating Conditions | 11 デバイスおよびドキュメントのサポート            | 37 |

|   | 6.4 Thermal Information              | 11.1 デバイス・サポート                   | 37 |

|   | 6.5 Electrical Characteristics       | 11.2 ドキュメントのサポート                 | 37 |

|   | 6.6 Electrical Characteristics       | 11.3 ドキュメントの更新通知を受け取る方法          | 37 |

|   | 6.7 Typical Characteristics9         | 11.4 コミュニティ・リソース                 | 37 |

| 7 | Detailed Description 13              | 11.5 商標                          | 37 |

|   | 7.1 Overview                         | 11.6 静電気放電に関する注意事項               | 37 |

|   | 7.2 Functional Block Diagram         | 11.7 Glossary                    | 37 |

|   | 7.3 Feature Description              | 12 メカニカル、パッケージ、および注文情報           | 37 |

|   | 7.4 Device Functional Modes          |                                  |    |

#### 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

Revision C (December 2013) から Revision D に変更

#

# Changed the Test Condition for P<sub>IN(CS)</sub> in the *Electrical Characteristics* 6 Changed the values for P<sub>IN(CS)</sub> in the *Electrical Characteristics* From: TYP = 5 To: TYP = 15 6 Changed CBYP = 0.1 µF To: CBYP = 0.01 µF in *Detailed Design Procedure* 25 Changed CBYP = 0.1 µF To: CBYP = 0.01 µF in *Detailed Design Procedure* 28

#

#

**Page**

| Re | evision B (September 2013) から Revision C に変更                                                                            | Page           |

|----|-------------------------------------------------------------------------------------------------------------------------|----------------|

| •  | 「特長」の「最小120mVの入力ソースでエネルギー・ハーベストを継続」を「最小100mVの入力ソースでエネルギー・ハーベストを継続」に変更                                                   |                |

| •  | 「特長」の「最大98%の高効率」を「最大93%の高効率」に変更                                                                                         |                |

| •  | 「概要」のテキストを「最小120mVのV <sub>IN</sub> でエネルギー・ハーベストを継続できます」から「最小100mVのV <sub>IN</sub> でエネルギー・ハーベストを継続できます」に変更               |                |

| •  | Changed Peak Input Power n the Absolute Maximum Ratings table From: MAX = 400 mW To: MAX = 510 mW                       | 5              |

| •  | Changed VIN(DC) in the Recommended Operating Conditions table From: MIN = 0.12 V MAX = 4 V To: MIN = 0.1 V MAX = 5.1 V  | 5              |

| •  | Changed VIN(DC) in the Electrical Characteristics table From: MIN = 120 mV MAX = 4000 mV To: MIN = 100 mV MAX = 5100 mV | 6              |

| •  | Changed PIN in the Electrical Characteristics table From: MAX = 400 mW To: MAX = 510 mW                                 | 6              |

| •  | Added VDELTA, VBAT_OV - VIN(DC to the ELECTRICAL CHARACTERISTICS table                                                  | <mark>7</mark> |

| •  | Changed VOUT_EN(H) From: VSTOR - 0.2 To: VSTOR - 0.4 in the ELECTRICAL CHARACTERISTICS table                            | 7              |

| Re | evision A (September 2013) から Revision B に変更                                                                            | Page           |

| •  | Changed values in the <i>Thermal Information</i> table                                                                  | 6              |

| 20 | <b>113</b> 年 <b>3</b> 月発行のものから更新                                                                                        | Page           |

| •  | Changed the data sheet from a Product Brief to Production data                                                          | 4              |

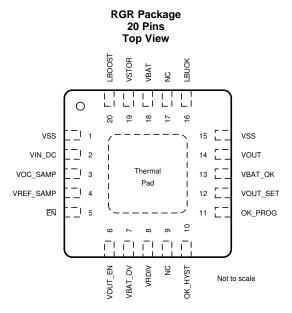

# 5 Pin Configuration and Functions

# **Pin Functions**

| NAME NO.  |    |     | DECORIDEION                                                                                                                                                                                                    |

|-----------|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           |    | 1/0 | DESCRIPTION                                                                                                                                                                                                    |

| EN        | 5  | 1   | Active low digital programming input for enabling/disabling the IC. Connect to GND to enable the IC.                                                                                                           |

| LBOOST    | 20 | I/O | Inductor connection for the boost charger switching node. Connect a 22 µH inductor between this pin and pin 2 (VIN_DC).                                                                                        |

| LBUCK     | 16 | I/O | Inductor connection for the buck converter switching node. Connect at least a 4.7 µH inductor between this pin and pin 14 (VOUT).                                                                              |

| NC        | 9  | I   | Connect to ground using the IC's PowerPAD™.                                                                                                                                                                    |

| NC        | 17 | 1   | Connect to ground using the IC's PowerPAD.                                                                                                                                                                     |

| OK_HYST   | 10 | I   | Connect to the mid-point of external resistor divider between VRDIV and GND for setting the VBAT_OK hystersis threshold. If not used, connect this pin to GND.                                                 |

| OK_PROG   | 11 | I   | Connect to the mid-point of external resistor divider between VRDIV and GND for setting the VBAT_OK threshold. If not used, connect this pin to GND.                                                           |

| VBAT      | 18 | I/O | Connect a rechargeable storage element with at least 100uF of equivalent capacitance between this pin and either VSS pin.                                                                                      |

| VBAT_OK   | 13 | 0   | Digital output for battery good indicator. Internally referenced to the VSTOR voltage. Leave floating if not used.                                                                                             |

| VBAT_OV   | 7  | I   | Connect to the mid-point of external resistor divider between VRDIV and GND for setting the VBAT overvoltage threshold.                                                                                        |

| VIN_DC    | 2  | I   | DC voltage input from energy harvesting source. Connect at least a 4.7 µF capacitor as close as possible between this pin and pin 1.                                                                           |

| VOC_SAMP  | 3  | I   | Sampling pin for MPPT network. Connect to VSTOR to sample at 80% of input source open circuit voltage. Connect to GND for 50% or connect to the mid-point of external resistor divider between VIN_DC and GND. |

| VOUT      | 14 | 0   | Buck converter output. Connect at least 22 μF output capacitor between this pin and pin 15 (VSS).                                                                                                              |

| VOUT_EN   | 6  | I   | Active high digital programming input for enabling/disabling the buck converter. Connect to VSTOR to enable the buck converter.                                                                                |

| VOUT_SET  | 12 | I   | Connect to the mid-point of external resistor divider between VRDIV and GND for setting the VOUT regulation set point.                                                                                         |

| VREF_SAMP | 4  | ı   | Connect a 0.01-µF low-leakage capacitor from this pin to GND to store the voltage to which VIN_DC will be regulated. This voltage is provided by the MPPT sample circuit.                                      |

| VRDIV     | 8  | 0   | Connect high side of resistor divider networks to this biasing voltage.                                                                                                                                        |

| VSS       | 1  | I   | Power ground for the boost charger.                                                                                                                                                                            |

| VSS       | 15 | _   | Power ground for the buck converter and analog/signal ground for the resistor dividers and VREF_SAMP capacitor.                                                                                                |

| VSTOR     | 19 | 0   | Connection for the output of the boost charger. Connect at least a 4.7 µF capacitor in parallel with a 0.1 µF capacitor as close as possible to between this pin and pin 1 (VSS).                              |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                    |                                                                                                                                                | MIN  | MAX | UNIT |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|

| Input voltage      | VIN_DC, VOC_SAMP, VREF_SAMP, VBAT_OV, VRDIV, OK_HYST, OK_PROG, VBAT_OK, VBAT, VSTOR, LBOOST, EN, VOUT_EN, VOUT_SET, LBUCK, VOUT <sup>(2)</sup> | -0.3 | 5.5 | V    |

| Peak Input Power,  | PIN_PK                                                                                                                                         |      | 510 | mW   |

| Operating junction | temperature, $T_J$                                                                                                                             | -40  | 125 | °C   |

| Storage temperatu  | re, T <sub>stg</sub>                                                                                                                           | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|   |       |                         |                                                                                | VALUE | UNIT |

|---|-------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|   |       |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V | (ESD) | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

|                                                          |                                                                                  | MIN | NOM | MAX | UNIT       |

|----------------------------------------------------------|----------------------------------------------------------------------------------|-----|-----|-----|------------|

| VIN(DC)                                                  | DC input voltage into VIN_DC <sup>(1)</sup>                                      | 0.1 |     | 5.1 | V          |

| VBAT, VOUT                                               | Voltage range <sup>(2)</sup>                                                     | 2   |     | 5.5 | <b>V</b>   |

| CIN                                                      | Capacitance on VIN_DC pin                                                        | 4.7 |     |     | μF         |

| CSTOR                                                    | Capacitance on VSTOR pin                                                         | 4.7 |     |     | μF         |

| COUT                                                     | Capacitance on VOUT pin                                                          | 10  | 22  |     | μF         |

| CBAT                                                     | Capacitance or battery with at least the same equivalent capacitance on VBAT pin | 100 |     |     | μF         |

| CREF                                                     | Capacitance on VREF_SAMP that stores the samped VIN reference                    | 9   | 10  | 11  | nF         |

| R <sub>OC1</sub> + R <sub>OC2</sub>                      | Total resistance for setting for MPPT reference if needed                        | 18  | 20  | 22  | $\Omega$ M |

| R <sub>OK 1</sub> + R <sub>OK 2</sub> + R <sub>OK3</sub> | Total resistance for setting VBAT_OK threshold voltage.                          | 11  | 13  | 15  | $\Omega$ M |

| R <sub>OUT1</sub> + R <sub>OUT2</sub>                    | Total resistance for setting VOUT threshold voltage.                             | 11  | 13  | 15  | $\Omega$ M |

| R <sub>OV1</sub> + R <sub>OV2</sub>                      | Total resistance for setting VBAT_OV voltage.                                    | 11  | 13  | 15  | ΜΩ         |

| L1                                                       | Inductance on LBOOST pin                                                         | 22  |     |     | μΗ         |

| L2                                                       | Inductance on LBUCK pin                                                          | 4.7 | 10  |     | μΗ         |

| T <sub>A</sub>                                           | Operating free air ambient temperature                                           | -40 |     | 85  | °C         |

| T <sub>J</sub>                                           | Operating junction temperature                                                   | -40 |     | 105 | °C         |

<sup>(1)</sup> Maximum input power ≤ 400 mW. Cold start has been completed

<sup>(2)</sup> All voltage values are with respect to V<sub>SS</sub>/ground terminal.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

VBAT\_OV setting must be higher than VIN\_DC

#### 6.4 Thermal Information

|                      |                                              | bq25570 |      |

|----------------------|----------------------------------------------|---------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGR     | UNIT |

|                      |                                              | 20 PINS |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 34.6    |      |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 49.0    |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 12.5    | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.5     | C/VV |

| ΨЈВ                  | Junction-to-board characterization parameter | 12.6    |      |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 1.0     |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

Over recommended temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of  $V_{STOR}$  = 4.2 V,  $V_{OUT}$  = 1.8 V. External components,  $C_{IN}$  = 4.7  $\mu$ F, L1 = 22  $\mu$ H,  $C_{STOR}$  = 4.7  $\mu$ F, L2 = 10  $\mu$ H,  $C_{OUT}$  = 22  $\mu$ F

|                           | PARAMETER                                                                                                        | TEST CONDITIONS                                                                                            | MIN   | TYP  | MAX  | UNIT |

|---------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| BOOST CHARGE              | R                                                                                                                |                                                                                                            |       |      |      |      |

| V <sub>IN(DC)</sub>       | DC input voltage into VIN_DC                                                                                     | Cold-start completed                                                                                       | 100   |      | 5100 | mV   |

| I <sub>CHG(CBC_LIM)</sub> | Cycle-by-cycle current limit of charger                                                                          | 0.5V < V <sub>IN</sub> < 4.0 V; VSTOR<br>= 4.2 V                                                           |       | 230  | 285  | mA   |

| P <sub>IN</sub>           | Input power range for normal charging                                                                            | VBAT_OV > VSTOR > VSTOR_CHGEN                                                                              | 0.005 |      | 510  | mW   |

| V <sub>IN(CS)</sub>       | Minimum input voltage for cold start circuit to start charging VSTOR                                             | VBAT < VBAT_UV; VSTOR<br>= 0 V; 0°C < T <sub>A</sub> < 85°C                                                |       | 600  | 700  | mV   |

| VSTOR <sub>(CHGEN)</sub>  | Voltage on VSTOR when cold start operation ends and normal charger operation commences                           |                                                                                                            | 1.6   | 1.73 | 1.9  | ٧    |

| P <sub>IN(CS)</sub>       | Minimum cold-start input power for VSTOR to reach VSTOR <sub>(CHGEN)</sub> and allow normal charging to commence | VSTOR < VSTOR <sub>(CHGEN)</sub> VIN_DC clamped to V <sub>IN(CS)</sub> by cold start circuit VBAT = 100 µF |       | 15   |      | μW   |

| t <sub>BAT_HOT_PLUG</sub> | Time for which switch between VSTOR and VBAT closes when battery is hot plugged into VBAT                        | Battery resistance = 300 $\Omega$ , Battery voltage = 3.3V                                                 |       | 50   |      | ms   |

| QUIESCENT CUR             | RRENTS                                                                                                           |                                                                                                            |       |      |      |      |

|                           | EN = 0, VOUT_EN = 1 - Full operating                                                                             | VIN_DC = 0V; VSTOR = 2.1V; T <sub>J</sub> = 25°C                                                           |       | 488  | 700  | l    |

|                           | mode                                                                                                             | VIN_DC = 0V; VSTOR = 2.1V; -40°C < T <sub>J</sub> < 85°C                                                   |       |      | 900  |      |

|                           | $\overline{\text{EN}} = 0$ , VOUT_EN = 0 - Partial standby                                                       | VIN_DC = 0V; VSTOR = 2.1V; T <sub>J</sub> = 25°C                                                           |       | 445  | 615  |      |

| $I_Q$                     | mode                                                                                                             | VIN_DC = 0V; VSTOR = 2.1V; -40°C < T <sub>J</sub> < 85°C                                                   |       |      | 815  | nA   |

|                           |                                                                                                                  | VBAT = 2.1 V; T <sub>J</sub> = 25°C;<br>VSTOR = VIN_DC = 0 V                                               |       | 1    | 5    |      |

|                           | EN = 1, VOUT_EN = x - Ship mode                                                                                  | VBAT = 2.1 V; -40°C < T <sub>J</sub> < 85°C; VSTOR = VIN_DC = 0 V                                          |       |      | 30   | ı    |

| MOSFET RESIST             | ANCES                                                                                                            |                                                                                                            |       |      |      |      |

| R <sub>DS(ON)-BAT</sub>   | ON resistance of switch between VBAT and VSTOR                                                                   | VBAT = 4.2 V                                                                                               |       | 0.95 | 1.50 | Ω    |

# **Electrical Characteristics (continued)**

Over recommended temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of  $V_{STOR}$  = 4.2 V,  $V_{OUT}$  = 1.8 V. External components,  $C_{IN}$  = 4.7  $\mu$ F, L1 = 22  $\mu$ H,  $C_{STOR}$  = 4.7  $\mu$ F, L2 = 10  $\mu$ H,  $C_{OUT}$  = 22  $\mu$ F

|                          | PARAMETER                                                                           | TEST CONDITIONS                                 | MIN              | TYP  | MAX                      | UNIT |

|--------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------|------------------|------|--------------------------|------|

|                          | Charger low side switch ON resistance                                               |                                                 |                  | 0.70 | 0.90                     |      |

| _                        | Charger high side switch ON resistance                                              | VBAT = 4.2 V                                    |                  | 2.30 | 3.00                     |      |

| R <sub>DS(ON)_CHG</sub>  | Charger low side switch ON resistance                                               | VP.47                                           |                  | 0.80 | 1.00                     | Ω    |

|                          | Charger high side switch ON resistance                                              | VBAT = 2.1 V                                    |                  | 3.70 | 4.80                     |      |

|                          | Buck low side switch ON resistance                                                  | \/DAT                                           |                  | 0.80 | 1.00                     |      |

|                          | Buck high side switch ON resistance                                                 | VBAT = 4.2 V                                    |                  | 1.60 | 2.00                     |      |

| R <sub>DS(ON)_BUCK</sub> | Buck low side switch ON resistance                                                  | \/DAT 0.4\/                                     |                  | 1.00 | 1.20                     | Ω    |

|                          | Buck high side switch ON resistance                                                 | VBAT = 2.1 V                                    |                  | 2.40 | 2.90                     |      |

| f <sub>SW_CHG</sub>      | Maximum charger switching frequency                                                 |                                                 |                  | 1    |                          | MHz  |

| f <sub>SW_BUCK</sub>     | Maximum buck switching frequency                                                    |                                                 |                  | 500  |                          | kHz  |

| T <sub>TEMP_SD</sub>     | Junction temperature when charging is discontinued                                  | VBAT_OV > VSTOR > 1.8V                          |                  | 125  |                          | С    |

| BATTERY MANAGE           | MENT                                                                                |                                                 |                  |      |                          |      |

| VBAT_OV                  | Programmable voltage range for overvoltage threshold                                | VBAT increasing                                 | 2.2              |      | 5.5                      | V    |

| VBAT_OV_HYST             | Battery over-voltage hysteresis (internal)                                          | VBAT decreasing;<br>VBAT_OV = 5.25V             |                  | 24   | 55                       | mV   |

| VDELTA                   | VBAT_OV - VIN(DC)                                                                   | Main boost charger on;<br>MPPT not sampling VOC | 400              |      |                          | mV   |

| VBAT_UV                  | Under-voltage threshold                                                             | VBAT decreasing                                 | 1.91             | 1.95 | 2.0                      | V    |

| VBAT_UV_HYST             | Battery under-voltage hysteresis (internal)                                         | VBAT increasing                                 |                  | 15   | 32                       | mV   |

| VBAT_OK_HYST             | Programmable voltage range of digital signal indicating VSTOR (=VBAT) is OK         | VBAT increasing                                 | VBAT_UV          |      | VBAT_OV                  | ٧    |

| VBAT_OK_PROG             | Programmable voltage range of digital signal indicating VSTOR (=VBAT) is OK         | VBAT decreasing                                 | VBAT_UV          |      | VBAT_OK<br>_HYST -<br>50 | mV   |

| VBAT_ACCURACY            | Overall Accuracy for threshold values VBAT_OV, VBAT_OK                              | Selected resistors are 0.1% tolerance           | -2%              |      | 2%                       |      |

| VBAT_OK(H)               | VBAT_OK (High) threshold voltage                                                    | Load = 10 µA                                    |                  |      | VSTOR –<br>200           | mV   |

| VBAT_OK(L)               | VBAT_OK (Low) threshold voltage                                                     | Load = 10 µA                                    |                  |      | 100                      | mV   |

| <b>ENABLE THRESHO</b>    | LDS                                                                                 |                                                 |                  |      |                          |      |

| EN(H)                    | Voltage for $\overline{\text{EN}}$ high setting. Relative to VBAT.                  | VBAT = 4.2V                                     | VBAT –<br>0.2    |      |                          | ٧    |

| EN(L)                    | Voltage for EN low setting                                                          | VBAT = 4.2V                                     |                  |      | 0.3                      | V    |

| VOUT_EN(H)               | Voltage for VOUT_EN High setting.                                                   | VSTOR = 4.2V                                    | VSTOR -<br>0.4   |      |                          | V    |

| VOUT_EN(L)               | Voltage for VOUT_EN Low setting.                                                    | VSTOR = 4.2V                                    |                  |      | 0.3                      | V    |

| BIAS and MPPT CO         | NTROL STAGE                                                                         |                                                 |                  |      |                          |      |

| VOC_SAMPLE               | Time period between two MPPT samples                                                |                                                 |                  | 16   |                          | S    |

| VOC_STLG                 | Settling time for MPPT sample measurement of VIN_DC open circuit voltage            | Device not switching                            |                  | 256  |                          | ms   |

| VIN_REG                  | Regulation of VIN_DC during charging                                                | 0.5 V < VIN < 4 V; IIN(DC)<br>= 10 mA           |                  |      | 10%                      |      |

| MPPT_80                  | Voltage on VOC_SAMP to set MPPT threshold to 0.80 of open circuit voltage of VIN_DC |                                                 | VSTOR -<br>0.015 |      |                          | V    |

# **Electrical Characteristics (continued)**

Over recommended temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of  $V_{STOR}$  = 4.2 V,  $V_{OUT}$  = 1.8 V. External components,  $C_{IN}$  = 4.7  $\mu$ F, L1 = 22  $\mu$ H,  $C_{STOR}$  = 4.7  $\mu$ F, L2 = 10  $\mu$ H,  $C_{OUT}$  = 22  $\mu$ F

| PARAMETER |                                                                                     | TEST CONDITIONS     | MIN   | TYP  | MAX   | UNIT |

|-----------|-------------------------------------------------------------------------------------|---------------------|-------|------|-------|------|

| MPPT_50   | Voltage on VOC_SAMP to set MPPT threshold to 0.50 of open circuit voltage of VIN_DC |                     |       |      | 15    | mV   |

| VBIAS     | Internal reference for the programmable voltage thresholds                          | VSTOR ≥ VSTOR_CHGEN | 1.205 | 1.21 | 1.217 | V    |

#### 6.6 Electrical Characteristics

Over recommended ambient temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of VSTOR = 4.2 V,  $V_{OUT}$  = 1.8 V. External components,  $C_{IN}$  = 4.7  $\mu$ F, L1 = 22  $\mu$ H, CSTOR = 4.7  $\mu$ F, L2 = 10  $\mu$ H,  $C_{OUT}$  = 22  $\mu$ F

|                         | PARAMETER                                                                                  | TEST CONDITIONS                                                                                                                                       | MIN | TYP   | MAX                           | UNIT |

|-------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------------------------|------|

| BUCK CONVERTER          |                                                                                            |                                                                                                                                                       |     |       |                               |      |

|                         | Output regulation (excluding resistor tolerance error)                                     | I <sub>OUT</sub> = 10 mA;<br>1.3 V < V <sub>OUT</sub> < 3.3 V                                                                                         | -2% |       | 2%                            |      |

| VOUT                    | Output line regulation                                                                     | $\begin{split} I_{OUT} &= 10 \text{ mA;} \\ VSTOR &= 2.1 \text{ V to } 5.5 \text{ V,} \\ C_{OUT} &= 22  \mu\text{F} \end{split}$                      |     | 0.09  |                               | %/V  |

|                         | Output load regulation                                                                     | $I_{OUT}$ = 100 μA to 95 mA,<br>VSTOR = 3.6 V, $C_{OUT}$ = 22<br>μF                                                                                   |     | -0.01 |                               | %/mA |

|                         | Output ripple                                                                              | $\begin{aligned} & \text{VSTOR} = 4.2 \text{V}, \ \text{I}_{\text{OUT}} = 1 \ \text{mA}, \\ & \text{C}_{\text{OUT}} = 22 \ \mu\text{F} \end{aligned}$ |     | 30    |                               | mVpp |

|                         | Programmable voltage range for output voltage threshold                                    |                                                                                                                                                       | 1.3 |       | VSTOR –<br>0.2 <sup>(1)</sup> | V    |

| IOUT                    | Output Current                                                                             | VSTOR = 3.3V; V <sub>OUT</sub> = 1.8 V                                                                                                                | 93  | 110   |                               | mA   |

| t <sub>START-STBY</sub> | Startup time with $\overline{\text{EN}}$ low and VOUT_EN transition to high (Standby Mode) | C <sub>OUT</sub> = 22 μF                                                                                                                              |     | 250   |                               | μS   |

| t <sub>START-SHIP</sub> | Startup time with VOUT_EN high and EN transition from high to low (Ship Mode)              | C <sub>OUT</sub> = 22 μF                                                                                                                              |     | 100   |                               | ms   |

| I-BUCK(CBC-LIM)         | Cycle-by-cycle current limit of buck converter                                             | 2.4 V < VSTOR < 5.5 V;<br>1.3 V < V <sub>OUT</sub> < 3.3 V                                                                                            | 160 | 185   | 205                           | mA   |

<sup>(1)</sup> The dropout voltage can be computed as the maximum output current times the buck high side resistance.

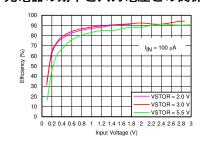

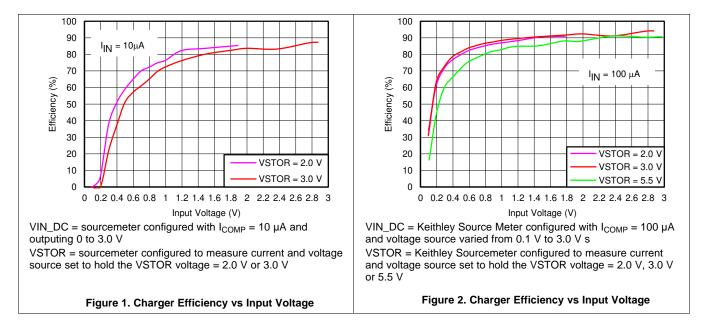

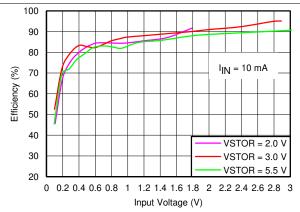

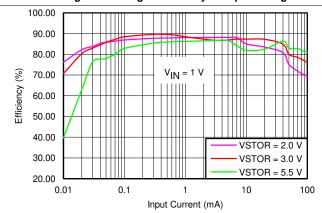

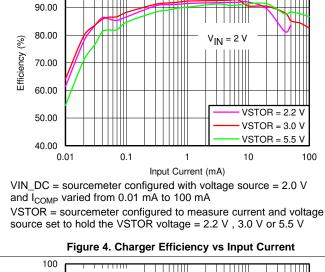

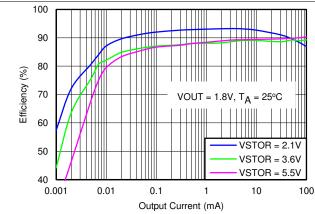

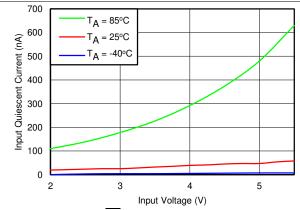

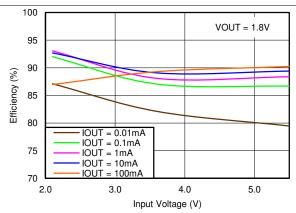

#### 6.7 Typical Characteristics

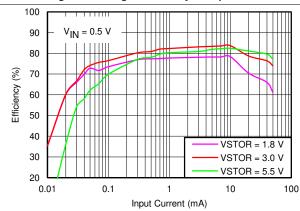

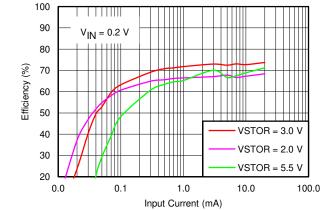

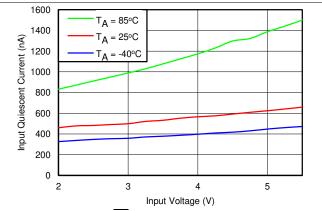

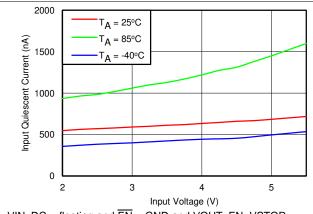

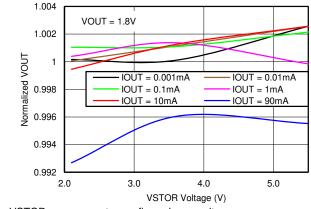

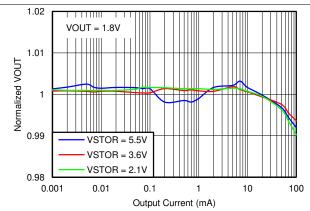

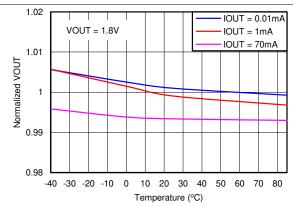

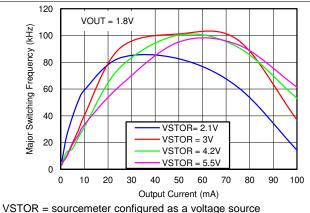

Unless otherwise noted, graphs were taken using Figure 24 with CIN =  $4.7\mu$ F, L1 = Coilcraft 22 $\mu$ H LPS4018, CSTOR =  $4.7\mu$ F, L2 = Toko 10  $\mu$ H DFE252012C, COUT = 22 $\mu$ F, VBAT\_OV=4.2V, VOUT=1.8V

**Table 1. Table of Graphs**

|                                               |                     |                                                            | FIGURE    |

|-----------------------------------------------|---------------------|------------------------------------------------------------|-----------|

|                                               |                     | IN= 10 μA                                                  | Figure 1  |

|                                               | vs. Input Voltage   | IN= 100 μA                                                 | Figure 2  |

|                                               |                     | IIN = 10 mA                                                | Figure 3  |

| Charger Efficiency (η) <sup>(1)</sup>         |                     | VIN = 2.0 V                                                | Figure 4  |

|                                               | Land Company        | VIN = 1.0 V                                                | Figure 5  |

|                                               | vs. Input Current   | VIN = 0.5 V                                                | Figure 6  |

|                                               |                     | VIN = 0.2 V                                                | Figure 7  |

| VSTOR Quiescent Current                       | vs. VSTOR Voltage   | EN = 1, VOUT_EN = X (Ship Mode)                            | Figure 8  |

| VSTOR Quiescent Current                       | vs. vsTOR voltage   | $\overline{\text{EN}} = 0$ , VOUT_EN = 0 (Standby Mode)    | Figure 9  |

| VBAT Quiescent Current                        | vs. VBAT Voltage    | AT Voltage $\overline{EN} = 0$ , VOUT_EN = 1 (Active Mode) |           |

| Duck Efficiency (v)                           |                     | vs. Output Current                                         | Figure 11 |

| Buck Efficiency (η)                           |                     | vs. Input Voltage                                          | Figure 12 |

|                                               |                     | vs. Output Current                                         | Figure 13 |

| Normalized Buck Output Voltage                |                     | vs. Input Voltage                                          | Figure 14 |

|                                               |                     | vs. Temperature                                            | Figure 15 |

| Buck Maximum Output Current vs. Input Voltage | VOUT = 1.8V - 100mV |                                                            | Figure 16 |

| Duels Major Cuitabing Francisco               |                     | vs. Output Current                                         | Figure 17 |

| Buck Major Switching Frequency                |                     | vs. Input Voltage                                          | Figure 18 |

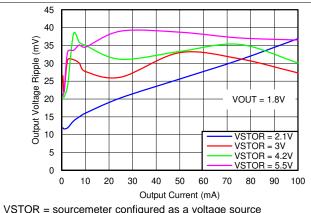

| Buok Output Binnla                            |                     | vs.Output Current                                          | Figure 19 |

| Buck Output Ripple                            |                     | vs. Input Voltage                                          | Figure 20 |

<sup>(1)</sup> See SLUA691 for an explanation on how to take these measurements. Because the MPPT feature cannot be disabled on the bq25570, these measurements need to be taken in the middle of the 16 s sampling period.

VIN\_DC = sourcemeter configured with I $_{\rm COMP}$  = 10 mA and voltage source varied from 0.1 V to 3.0 V

VSTOR = sourcemeter configured to measure current and voltage source set to hold the VSTOR voltage = 2.0 V, 3.0 V or 5.5 V

Figure 3. Charger Efficiency vs Input Voltage

$VIN\_DC$  = sourcemeter configured with voltage source = 1.0 V and  $I_{COMP}$  varied from 0.01 mA to 100 mA

VSTOR = sourcemeter configured to measure current and voltage source set to hold the VSTOR voltage = 2.0 V, 3.0 V or 5.5 V

Figure 5. Charger Efficiency vs Input Current

100.00

VIN\_DC = sourcemeter configured with voltage source = 0.5 V and  $I_{\text{COMP}}$  varied from 0.01 mA to 100 mA

VSTOR = sourcemeter configured to measure current and voltage source set to hold the VSTOR voltage = 1.8 V, 3.0 V or 5.5 V

Figure 6. Charger Efficiency vs Input Current

VIN\_DC = souremeter configured with voltage source = 0.2 V and  $I_{COMP}$  varied from 0.01 mA to 100 mA

VSTOR = sourcemeter configured to measure current and voltage source set to hold the VSTOR voltage = 2.0 V, 3.0 V or 5.5 V

Figure 7. Charger Efficiency vs Input Current

$VIN_DC = floating and \overline{EN} = VOUT_EN = GND$

VSTOR = sourcemeter configured to measure current and voltage source varied from 2.0 V or 5.5 V  $\,$

Figure 8. VSTOR Quiescent Current vs VSTOR Voltage: Standby Mode

VIN\_DC = floating and  $\overline{\text{EN}}$  = GND and VOUT\_EN=VSTOR VSTOR= sourcemeter configured to measure current and voltage source varied from 2.0 V or 5.5 V

Figure 9. VSTOR Quiescent Current vs VSTOR Voltage:

Active Mode

VSTOR = sourcemeter configured as a voltage source, measuring current

OUT = sourcemeter configured to sink current with VCOMP>V(OUT)

Figure 11. Buck Efficiency vs Output Current

$VIN_DC = floating and \overline{EN} = VSTOR$

VSTOR = sourcemeter configured to measure current and voltage source varied from 2.0 V or 5.5 V  $\,$

Figure 10. VBAT Quiescent Current vs VBAT Voltage: Ship Mode

VSTOR = sourcemeter configured as a voltage source, measuring current

OUT = sourcemeter configured sink current with VCOMP>V(OUT)

VSTOR = sourcemeter configured as a voltage source OUT = sourcemeter configured to sink current with VCOMP>V(OUT) and measuring voltage

Figure 13. Normalized Buck Output Voltage vs Input Voltage

VSTOR = sourcemeter configured as a voltage source OUT = sourcemeter configured to sink current with VCOMP>V(OUT) and measuring voltage

Figure 14. Normalized Buck Output Voltage vs Output Current

VSTOR = sourcemeter configured as a voltage source OUT = sourcemeter configured to sink current with VCOMP>V(OUT) and measuring voltage Thermal stream for temperature variation

170  $T_A = 85^{\circ}C$ VOUT = 1.8V - 100 mV 160  $T_A = 25^{\circ}C$ 150  $T_A = 0$ °C (mA) 140  $T_A = -40^{\circ}C$ **Output Current** 130 120 110 100 90 80 2 VSTOR Voltage (V)

VSTOR = sourcemeter configured as a voltage source OUT = sourcemeter configured to increasingly sink current with VCOMP>V(OUT) until V(OUT) < VOUT - 100 mV Thermal stream for temperature variation

Figure 15. Normalized Buck Output Voltage vs Temperature

OUT = sourcemeter configured to sink current with VCOMP>V(OUT) and measuring voltage

Oscilloscope used to measure switching frequency at LBOOST

Figure 16. Buck Maximum Output Current vs Input Voltage

VSTOR = sourcemeter configured as a voltage source

OUT = sourcemeter configured to sink current with

VCOMP>V(OUT) and measuring voltage

Oscilloscope used to measure switching frequency at LBOOST

Figure 17. Buck Major Switching Frequency vs Output

Current

Figure 18. Buck Major Switching Frequency vs Input Voltage

OUT = sourcemeter configured as a voltage source

OUT = sourcemeter configured to sink current with

VCOMP>V(OUT) and measuring voltage

Oscilloscope used to measure voltage ripple at OUT

Figure 19. Buck Output Voltage Ripple vs Output Current

VSTOR = sourcemeter configured as a voltage source OUT = sourcemeter configured to sink current with VCOMP>V(OUT) and measuring voltage Oscilloscope used to measure voltage ripple at OUT

Figure 20. Buck Output Voltage Ripple vs Input Voltage

# 7 Detailed Description

#### 7.1 Overview

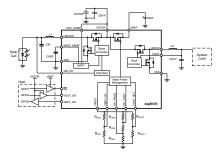

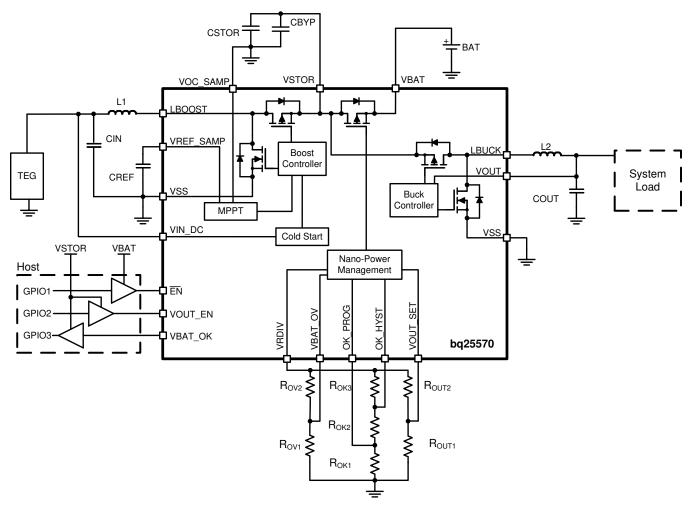

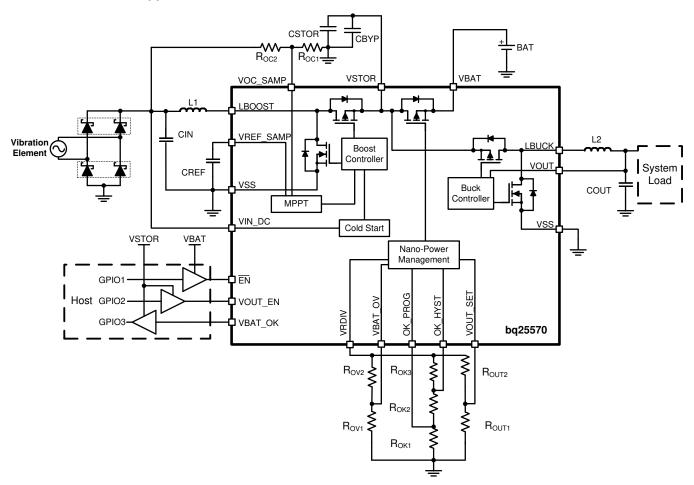

The bq25570 device is a highly integrated energy harvesting Nano-Power management solution that is well suited for meeting the special needs of ultra low-power applications. The product is specifically designed to efficiently acquire and manage the microwatts ( $\mu$ W) to milliwatts (mW) of power generated from a variety of DC sources like photovoltaic (solar) or thermal electric generators. targeted toward products and systems, such as wireless sensor networks (WSN) which have stringent power and operational demands.

The main boost charger is powered from the boost output, VSTOR. Once the VSTOR voltage is above VSTOR\_CHGEN (1.8 V typical), for example, after a partially discharged battery is attached to VBAT, the boost charger can effectively extract power from low voltage output harvesters such as TEGs or single or dual cell solar panels outputting voltages down to VIN(DC) (100 mV minimum). When starting from VSTOR = VBAT < 100 mV, the cold start circuit needs at least VIN(CS), 600 mV typical, to charge VSTOR up to 1.8 V.

The bq25570 also implements a programmable maximum power point tracking sampling network to optimize the transfer of power into the device. The fraction of open circuit voltage that is sampled and held can be controlled by pulling VOC\_SAMP high or low (80% or 50% respectively) or by using external resistors. This sampled voltage is maintained via internal sampling circuitry and held with an external capacitor (CREF) on the VREF\_SAMP pin. For example, solar cells typically operate with a maximum power point (MPP) of 80% of their open circuit voltage. Connecting VOC\_SAMP to VSTOR sets the MPPT threshold to 80% and results in the IC regulating the voltage on the solar cell to ensure that the VIN\_DC voltage does not fail below the voltage on CREF which equals 80% of the solar panel's open circuit voltage. Alternatively, an external reference voltage can be provided by a MCU to produce a more complex MPPT algorithm.

The bq25570 is designed with the flexibility to support a variety of energy storage elements. The availability of the sources from which harvesters extract their energy can often be sporadic or time-varying. Systems will typically need some type of energy storage element, such as a re-chargeable battery, super capacitor, or conventional capacitor. The storage element provides constant power to the system. The storage element also allows the system to handle any peak currents that can not directly come from the input source. To prevent damage to a customer's storage element, both maximum and minimum voltages are monitored against the internally set under-voltage (UV) and user programmable over-voltage (OV) levels.

To further assist users in the strict management of their energy budgets, the bq25570 toggles the battery good (VBAT\_OK) flag to signal an attached microprocessor when the voltage on an energy storage battery or capacitor has dropped below a pre-set critical level. This should trigger the reduction of load currents to prevent the system from entering an under voltage condition. There is also independent enable signals to allow the system to control when to run the regulated output or even put the whole IC into an ultra-low quiescent current sleep state.

In addition to the boost charging front end, the bq25570 provides the system with an externally programmable regulated supply via the buck converter. The regulated output has been optimized to provide high efficiency across low output currents (< 10  $\mu$ A) to high currents (<110 mA).

All the capabilities of bg25570 are packed into a small foot-print 20-lead 3.5-mm x 3.5-mm QFN package (RGR).

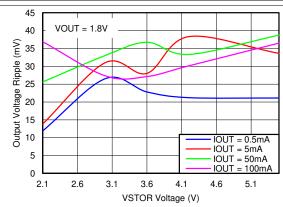

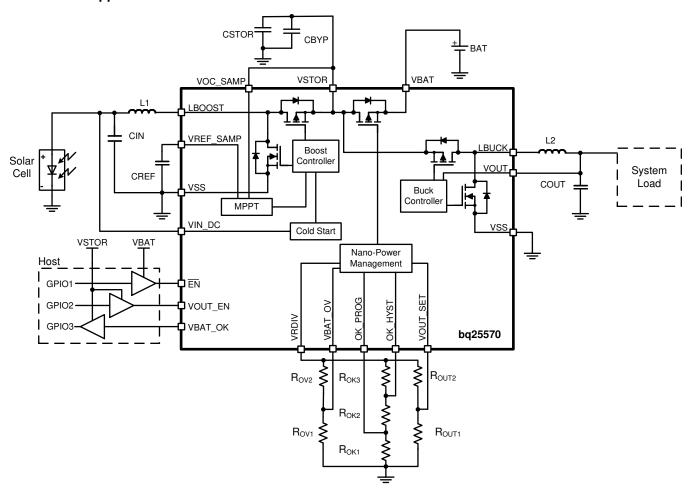

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Maximum Power Point Tracking

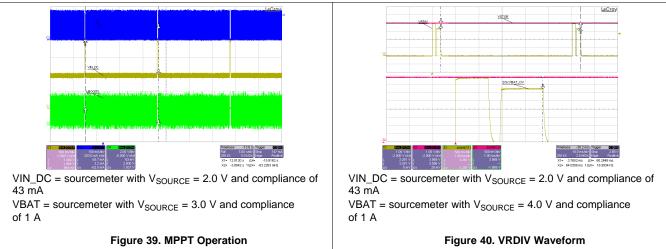

Maximum power point tracking (MPPT) is implemented in order to maximize the power extracted from an energy harvester source. The boost charger indirectly modulates the input impedance of the main boost charger by regulating the charger's input voltage, as sensed by the VIN\_DC pin, to the sampled reference voltage, as stored on the VREF\_SAMP pin. The MPPT circuit obtains a new reference voltage every 16 s (typical) by periodically disabling the charger for 256 ms (typical) and sampling a fraction of the open-circuit voltage (VOC). For solar harvesters, the maximum power point is typically 70%-80% and for thermoelectric harvesters, the MPPT is typically 50%. Tying VOC\_SAMP to VSTOR internally sets the MPPT regulation point to 80% of VOC. Tying VOC\_SAMP to GND internally sets the MPPT regulation point to 50% of VOC. If input source does not have either 80% or 50% of VOC as its MPP point, the exact ratio for MPPT can be optimized to meet the needs of the input source being used by connecting external resistors  $R_{\rm OC1}$  and  $R_{\rm OC2}$  between VRDIV and GND with midpoint at VOC\_SAMP.

The reference voltage is set by the following expression:

$$VREF\_SAMP = VIN\_DC(OpenCircuit) \left( \frac{R_{OC1}}{R_{OC1} + R_{OC2}} \right)$$

(1)

#### Feature Description (continued)

#### 7.3.2 Battery Undervoltage Protection

To prevent rechargeable batteries from being deeply discharged and damaged, and to prevent completely depleting charge from a capacitive storage element, the boost charger has an internally set undervoltage (VBAT\_UV) threshold plus an internal hysteresis voltage (VBAT\_UV\_HYST). The VBAT\_UV threshold voltage when the battery voltage is decreasing is internally set to 1.95V (typical). The undervoltage threshold when battery voltage is increasing is given by VBAT\_UV plus VBAT\_UV\_HYST. For the VBAT\_UV feature to function properly, the system load should be connected to the VSTOR pin while the storage element should be connected to the VBAT pin. Once the VSTOR pin voltage goes above VBAT\_UV plus VBAT\_UV\_HYST threshold, the VSTOR pin and the VBAT pins are effectively shorted through an internal PMOS FET. The switch remains closed until the VSTOR pin voltage falls below the VBAT\_UV threshold. The VBAT\_UV threshold should be considered a fail safe to the system and the system load should be removed or reduced based on the VBAT\_OK threshold which should be set above the VBAT\_UV threshold.

#### 7.3.3 Battery Overvoltage Protection

To prevent rechargeable batteries from being exposed to excessive charging voltages and to prevent over charging a capacitive storage element, the over-voltage (VBAT\_OV) threshold level must be set using external resistors. This is also the voltage value to which the charger will regulate the VSTOR/VBAT pin when the input has sufficient power. The VBAT\_OV threshold when the battery voltage is rising is given by Equation 2:

$$VBAT_OV = \frac{3}{2}VBIAS\left(1 + \frac{R_{OV2}}{R_{OV1}}\right)$$

(2)

The sum of the resistors is recommended to be no higher than 13 M $\Omega$  that is,  $R_{OV1}+R_{OV2}=13$  M $\Omega$ . Spreadsheet SLUC484 provides help on sizing and selecting the resistors. The overvoltage threshold when battery voltage is decreasing is given by VBAT\_OV minus VBAT\_OV\_HYST. Once the voltage at the battery exceeds VBAT\_OV threshold, the boost charger is disabled. The charger will start again once the battery voltage drops by VBAT\_OV\_HYST. When there is excessive input energy, the VBAT pin voltage will ripple between the VBAT\_OV and the VBAT\_OV\_HYST levels.

#### **CAUTION**

If VIN\_DC is higher than VSTOR and VSTOR is equal to VBAT\_OV, the input VIN\_DC is pulled to ground through a small resistance to stop further charging of the attached battery or capacitor. It is critical that if this case is expected, the impedance of the source attached to VIN\_DC be higher than 20  $\Omega$  and not a low impedance source.

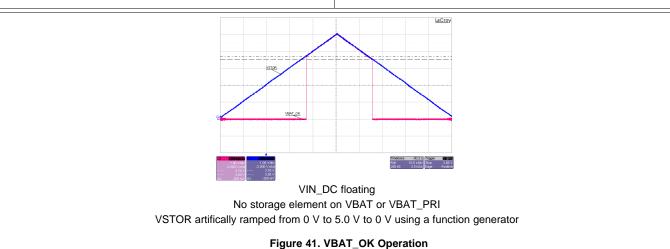

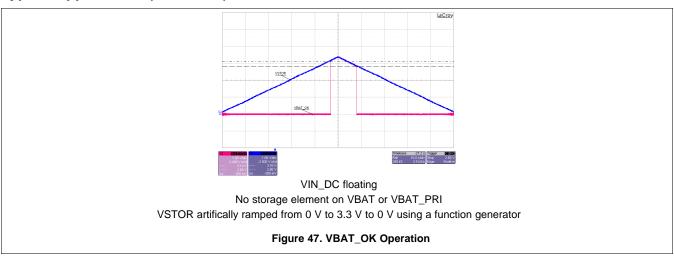

#### 7.3.4 Battery Voltage within Operating Range (VBAT\_OK Output)

The charger allows the user to set a programmable voltage independent of the overvoltage and undervoltage settings to indicate whether the VSTOR voltage (and therefore the VBAT voltage when the PFET between the two pins is turned on) is at an acceptable level. When the battery voltage is decreasing the threshold is set by Equation 3:

VBAT\_OK\_PROG = VBIAS

$$\left(1 + \frac{R_{OK2}}{R_{OK1}}\right)$$

(3)

When the battery voltage is increasing, the threshold is set by Equation 4:

$$VBAT_OK_HYST = VBIAS \left(1 + \frac{R_{OK2} + R_{OK3}}{R_{OK1}}\right)$$

(4)

The sum of the resistors is recommend to be no higher than approximately i.e.,  $R_{OK1}+R_{OK2}+R_{OK3}=13~M\Omega$ . Spreadsheet SLUC484 provides help on sizing and selecting the resistors. The logic high level of this signal is equal to the VSTOR voltage and the logic low level is ground. The logic high level has ~20 K $\Omega$  internally in series to limit the available current in order to prevent MCU damage until the MCU is fully powered. The VBAT\_OK\_PROG threshold must be greater than or equal to the UV threshold.

#### **Feature Description (continued)**

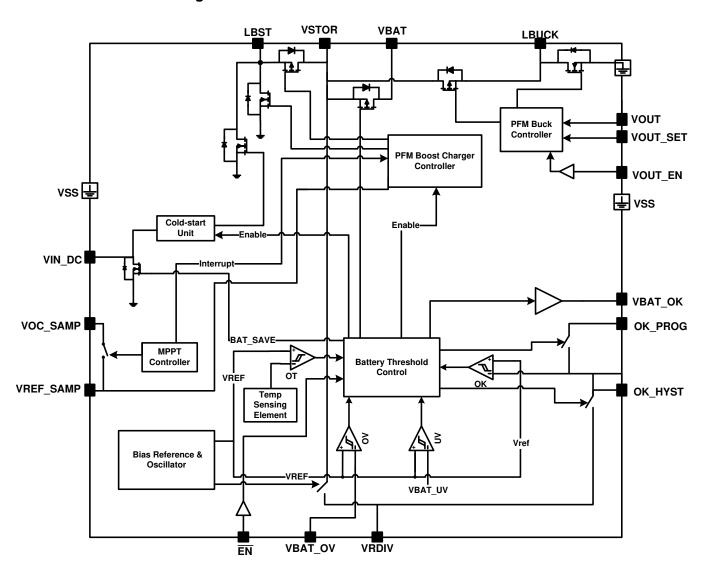

#### 7.3.5 Storage Element / Battery Management

In this section the battery management functionality of the bq25570 integrated circuit (IC) is presented. The IC has internal circuitry to manage the voltage across the storage element and to optimize the charging of the storage element. For successfully extracting energy from the source, two different threshold voltages must be programmed using external resistors, namely battery good threshold (VBAT\_OK) and over voltage (OV) threshold. The two user programmable threshold voltages and the internally set undervoltage threshold determine the IC's region of operation. Figure 21 shows the relative position of the various threshold voltages.

Figure 21. Summary of VSTOR Threshold Voltages

#### 7.3.6 Programming OUT Regulation Voltage

To set the proper output regulation voltage and input voltage power good comparator, the external resistors must be carefully selected.

The OUT regulation voltage is then given by Equation 5:

$$VOUT = VBIAS\left(\frac{R_{OUT2} + R_{OUT1}}{R_{OUT1}}\right)$$

(5)

Note that VBIAS is nominally 1.21 V per the electrical specification table. The sum of the resistors is recommended to be no greater than 13 M $\Omega$ , that is,  $R_{OUT1}$  +  $R_{OUT2}$  = 13 M $\Omega$ . Higher resistors may result in poor output voltage regulation and/or input voltage power good threshold accuracies due to noise pickup via the high impedance pins or reduction of effective resistance due to parasitic resistances created from board assembly residue. See Layout Considerations section for more details. SLUC484 provides help on sizing and selecting the resistors.

# **Feature Description (continued)**

#### 7.3.7 Step Down (Buck) Converter

The buck regulator input power is internally connected to VSTOR and steps the VSTOR voltage down to a lower regulated voltage at the OUT pin. It employs pulse frequency modulation (PFM) control to regulate the voltage close to the desired reference voltage. The voltage regulated at the OUT pin is set by the user programmed resistor divider. The current through the inductor is controlled through internal current sense circuitry. The peak current in the inductor is controlled to maintain high efficiency of the converter across a wide input current range. The converter delivers an output current up to 110mA typical with a peak inductor current of 200 mA. The buck converter is disabled when the voltage on VSTOR drops below the VBAT\_UV condition. The buck converter continues to operate in pass (100% duty cycle) mode, passing the input voltage to the output, as long as VSTOR is greater than VBAT\_UV and less than VOUT.

#### 7.3.8 Nano-Power Management and Efficiency

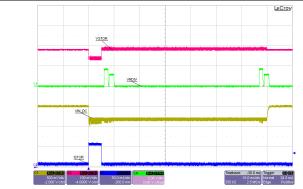

The high efficiency of the bq25570 charger is achieved through the proprietary Nano-Power management circuitry and algorithm. This feature essentially samples and holds the VSTOR voltage to reduce the average quiescent current. That is, the internal circuitry is only active for a short period of time and then off for the remaining period of time at the lowest feasible duty cycle. A portion of this feature can be observed in Figure 28 where the VRDIV node is monitored. Here the VRDIV node provides a connection to the VSTOR voltage (first pulse) and then generates the reference levels for the VBAT\_OV and VBAT\_OK resistor dividers for a short period of time. The divided down values at each pin are compared against VBIAS as part of the hysteretic control. Because this biases a resistor string, the current through these resistors is only active when the Nano-Power management circuitry makes the connection—hence reducing the overall quiescent current due to the resistors. This process repeats every 64 ms.

The efficiency of the bq25570 boost charger is shown for various input power levels in Figure 1 through Figure 7. All efficiency data points were captured by averaging 50 measurements of the input current in between MPPT sampling events. This must be done due to the pulsing currents of the hysteretic, discontinuous mode boost and buck converters. Quiescent currents into VSTOR, VBAT\_SEC and VBAT\_PRI over temperature and voltage are shown at Figure 8 through Figure 9.

#### 7.4 Device Functional Modes

The bq25570 has five functional modes: cold start operation, main boost charger disabled (ship mode), main boost charger enabled, buck converter enabled mode and thermal shutdown. When VSTOR is greater than VSTOR\_CHGEN (1.8 V typical), the bq25570's two enable pins allow for flexibility in controlling the system. The table below summarizes the functionality.

Table 2. Enable Functionality Table when VSTOR > VSTOR\_CHGEN

| EN PIN<br>LOGIC<br>LEVEL | VOUT_EN<br>PIN LOGIC<br>LEVEL | FUNCTIONAL MODE                                                                                                                          |

|--------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0                        | 0                             | Buck standby mode: boost charger and VBAT_OK are enabled. Buck converter is disabled.                                                    |

| 0                        | 1                             | Boost charger, buck converter and VBAT_OK enabled.                                                                                       |

| 1                        | ×                             | Ship mode (lowest leakage state): boost charger, PFET between VSTOR and VBAT is off, buck converter and VBAT_OK indication are disabled. |

The EN high voltage is relative to the VBAT pin voltage. VOUT\_EN high voltage is relative to VSTOR. If it is not desired to control EN, it is recommended that this pin be tied to VSS, or system ground. When EN is low, VOUT\_EN is used to enable and disable the buck converter. The high-level *Functional Block Diagram* highlights most of the major functional blocks inside the bq25570. The cold start circuitry is powered from VIN\_DC. The main boost charger circuitry is powered from VSTOR while the boost power stage is powered from VIN\_DC. Details of entering and exiting each mode are explained below.

# 7.4.1 Main Boost Charger Disabled (Ship Mode) - (VSTOR > VSTOR\_CHGEN and $\overline{EN}$ = HIGH)

When taken high relative to the voltage on VBAT\_SEC, the  $\overline{\text{EN}}$  pin shuts down the IC including the boost charger, buck converter and battery management circuitry. It also turns off the PFET that connects VBAT\_SEC to VSTOR. This can be described as ship mode, because it will put the IC in the lowest leakage state and provides a long storage period without significantly discharging the battery on VBAT. If there is no need to control EN, it is recommended that this pin be tied to VSS, or system ground.

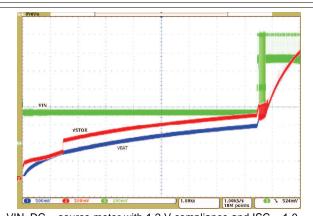

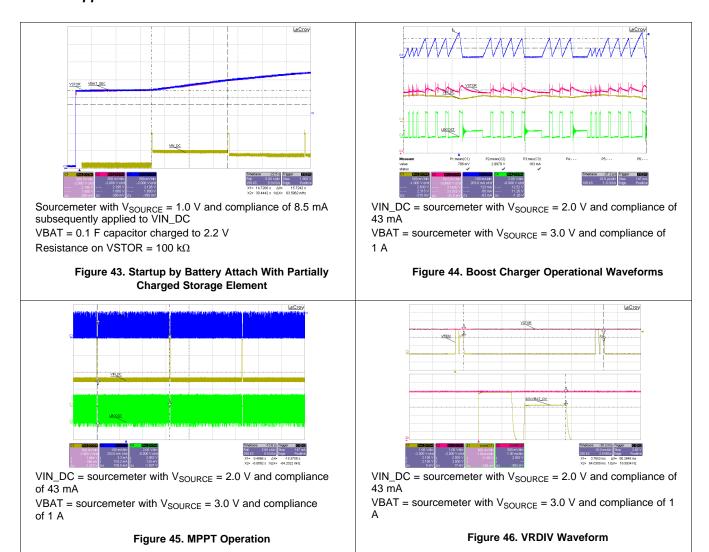

# 7.4.2 Cold-Start Operation (VSTOR < VSTOR\_CHGEN, VIN\_DC > VIN(CS) and PIN > PIN(CS), EN = don't care)

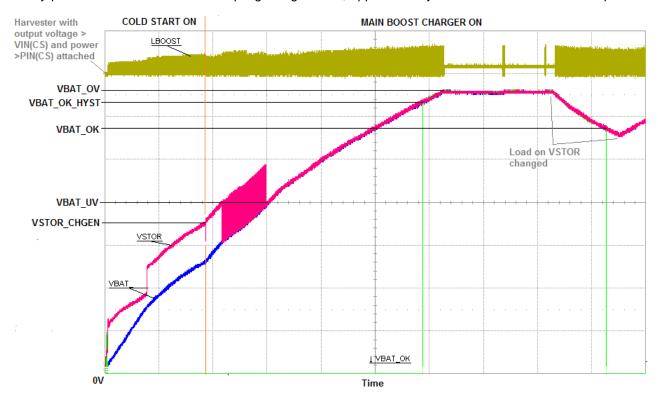

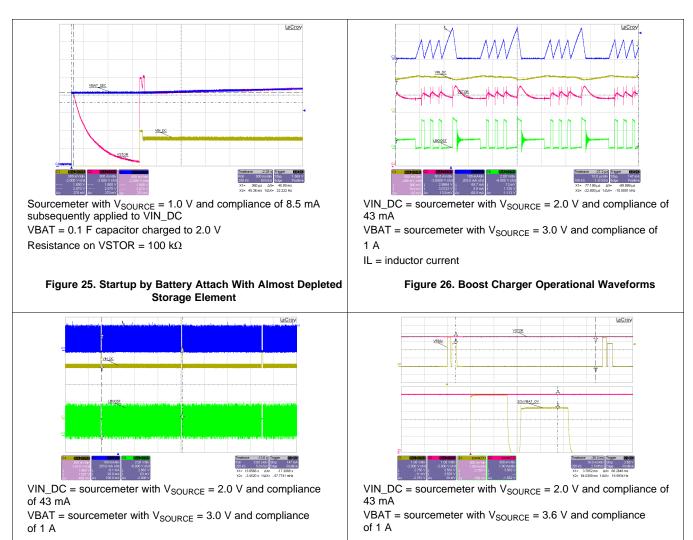

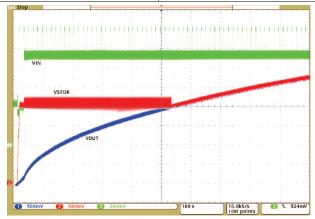

Whenever VSTOR < VSTOR\_CHGEN, VIN\_DC ≥ VIN(CS) and PIN > PIN(CS), the cold-start circuit is on. This could happen when there is not input power at VIN\_DC to prevent the load from discharging the battery or during a large load transient on VSTOR. During cold start, the voltage at VIN\_DC is clamped to VIN(CS) so the energy harvester's output current is critical to providing sufficient cold start input power, PIN(CS) = VIN(CS) X IIN(CS). The cold-start circuit is essentially an unregulated, hysteretic boost converter with lower efficiency compared to the main boost charger. None of the other features, including the EN pin, function during cold start operation. The cold start circuit's goal is to charge VSTOR higher than VSTOR\_CHGEN so that the main boost charger can operate. When a depleted storage element is initially attached to VBAT, as shown in Figure 22 and the harvester can provide a voltage > VIN(CS) and total power at least > PIN(CS), assuming no system load or leakage at VSTOR and VBAT, the cold start circuit can charge VSTOR above VSTOR\_CHGEN. Once the VSTOR voltage reaches the VSTOR CHGEN threshold, the IC

- 1. first performs an initialization pulse on VRDIV to reset the feedback voltages,

- 2. then disables the charger for 32 ms (typical) to allow the VIN\_DC voltage to rise to the harvester's opencircuit voltage which will be used as the input voltage regulation reference voltage until the next MPPT sampling cycle and

- 3. lastly performs its first feedback sampling using VRDIV, approximately 64 ms after the initialization pulse.

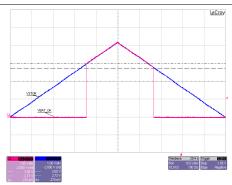

Figure 22. Charger Operation After a Depleted Storage Element is Attached and Harvester Power is Available

The energy harvester must supply sufficient power for the IC to exit cold start. Due to the body diode of the PFET connecting VSTOR and VBAT, the cold start circuit must charge both the capacitor on CSTOR up to the VSTOR\_CHGEN and the storage element connected to VBAT up to VSTOR\_CHGEN less a diode drop. When a rechargeable battery with an open protector is attached, the initial charge time is typically short due to the minimum charge needed to close the battery's protector FETs. When large, discharged super capacitors with high DC leakage currents are attached, the initial charge time can be significant.

When the VSTOR voltage reaches VSTOR\_CHGEN, the main boost charger starts up. When the VSTOR voltage rises to the VBAT\_UV threshold, the PMOS switch between VSTOR and VBAT turns on, which provides additional loading on VSTOR and could result in the VSTOR voltage dropping below both the VBAT\_UV threshold and the VSTOR\_CHGEN voltage, especially if system loads on VSTOR or VBAT are active during this time. Therefore, it is not uncommon for the VSTOR voltage waveform to have incremental pulses (for example, stair steps) as the IC cycles between cold-start and main boost charger operation before eventually maintaing VSTOR above VSTOR\_CHGEN.

The cold start circuit initially clamps VIN\_DC to VIN(CS) = 600 mV typical. If sufficient input power (that is, output current from the harvester clamped to VIN(CS)) is not available, it is possible that the cold start circuit cannot raise the VSTOR voltage above VSTOR\_CHGEN in order for the main boost conveter to start up. It is highly recommended to add an external PFET between the system load and VSTOR. An inverted VBAT\_OK signal provided by VB\_SEC\_ON can be used to drive the gate of this system-isolating, external PFET. See the Energy Harvester Selection applications section for guidance on minimum input power requirements.

# 7.4.3 Main Boost Charger Enabled (VSTOR > VSTOR\_CHGEN and $\overline{EN}$ = LOW)

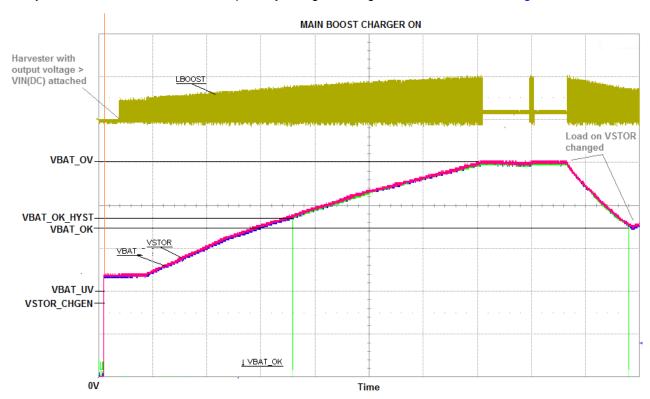

One way to avoid cold start is to attach a partially charged storage element as shown in Figure 23.

Figure 23. Charger Operation after a Partially Charged Storage Element is Attached and Harvester Power is Available

When no input source is attached, the VSTOR node should be discharged to ground before attaching a storage element. Hot-plugging a storage element that is charged (for example, the battery protector PFET is closed) and with the VSTOR node more than 100 mV above ground results in the PFET between VSTOR and VBAT remaining off until an input source is attached.

Assuming the voltages on VSTOR and VBAT are both below 100 mV, when a charged storage element is attached (that is, hot-plugged) to VBAT, the IC

- 1. first turns on the internal PFET between the VSTOR and VBAT pins for t<sub>BAT\_HOT\_PLUG</sub> (45 ms) in order to charge VSTOR to VSTOR\_CHGEN then turns off the PFET to prevent the battery from overdischarge,

- 2. then performs an initialization pulse on VRDIV to reset the feedback voltages,

- 3. then disables the charger for 32 ms (typical) to allow the VIN\_DC voltage to rise to the harvester's opencircuit voltage which will be used as the input voltage regulation reference voltage until the next MPPT sampling cycle and

- 4. lastly performs its first feedback sampling using VRDIV, approximately 64 ms after the initialization pulse.

If the VSTOR pin voltage remains above the internal under voltage threshold (VBAT\_UV) for the additional 64 ms after the VRDIV initialization pulse (following the 45-ms PFET on time), the internal PFET turns back on and the main boost charger begins to charge the storage element assuming there is sufficient power available from the harvester at the VIN\_DC pin. If VSTOR does not reach the VBAT\_UV threshold, then the PFET remains off until the main boost charger can raise the VSTOR voltage to VBAT\_UV. If a system load tied to VSTOR discharges VSTOR below VSTOR\_GEN or below VBAT\_UV during the 32 ms initial MPPT reference voltage measurement or within 110 ms after hot plug, it is recommended to add an external PFET between the system load and VSTOR. An inverted VBAT\_OK signal provided by VB\_SEC\_ONcan be used to drive the gate of this system-isolating, external PFET. Otherwise, the VSTOR voltage waveform will have incremental pulses as the IC turns on and off the internal PFET controlled by VBAT\_UV or cycles between cold-start and main boost charger operation.

Once VSTOR is above VSTOR\_CHGEN but less than VBAT\_V and VIN\_DC > VIN(DC)-MIN = 100 mV, the main boost charger extracts power from its source by employing pulse frequency modulation (PFM) mode of control to regulate the voltage at VIN\_DC close to the desired reference voltage. The reference voltage is set by the MPPT circuitry as described in the features section. Input voltage regulation is obtained by transferring charge from the input to VSTOR only when the input voltage is higher than the voltage on pin VREF\_SAMP. The current through the inductor is controlled through internal current sense circuitry. The peak current in the inductor is incremented internally in three pre-determined levels (~50 mA, ~100 mA and finally I-CHG(CBC\_LIM)) in order to maintain high efficiency of the charger across a wide input current range. When in discontinous mode, the boost charger can transfer up to a maximum of 100 mA average input current with I-CHG(CBC\_LIM) = 230mA typical peak inductor current. The boost charger is disabled when the voltage on VSTOR reaches the user set VBAT\_OV threshold to protect the battery connected at VBAT from overcharging. In order for the battery to charge to VBAT\_OV, the input power must exceed the power needed for the load on VSTOR. See the Energy Harvester Selection applications section for guidance on minimum input power requirements.

Steady state operation for the boost charger is shown in Figure 23. These plots highlight the inductor current, the VSTOR voltage ripple, input voltage regulation and the LBOOST switching node. The cycle-by-cycle minor switching frequency is a function of each the converter's inductor value, peak current limit and voltage levels on each side of each inductor. Once the VSTOR capacitor, CSTOR, droops below a minimum value, the hysteretic switching repeats.

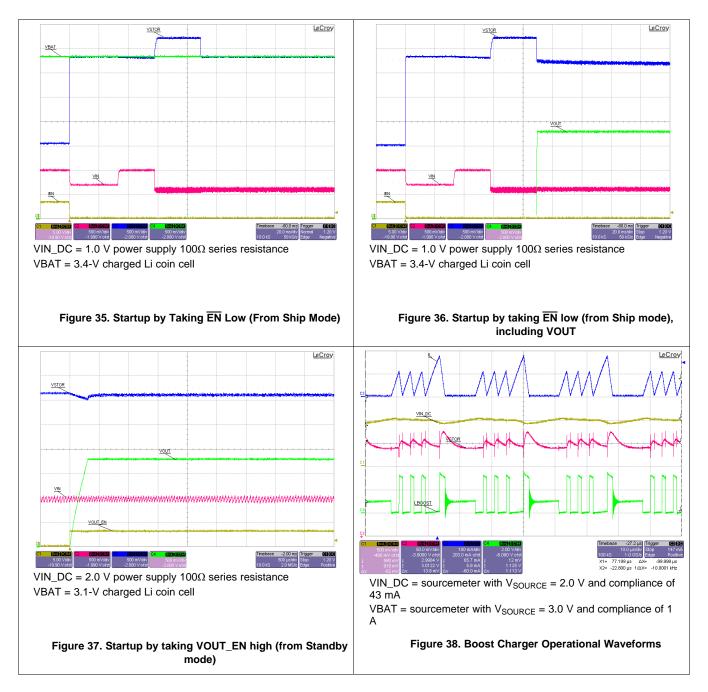

#### 7.4.3.1 Buck Converter Enabled (VSTOR > VBAT UV, EN = LOW and VOUT EN = HIGH)

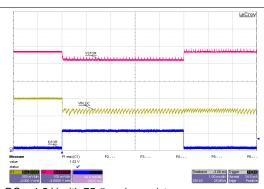

The bq25570 buck converter is hysteretic, peak current, discontinuous mode buck converter as summarized in *Step Down (Buck) Converter*. It has two startup responses: 1) from the ship-mode state (EN transitions from high to low with VOUT\_EN already high), and 2) from the standby state (VOUT\_EN transitions from low to high). The startup response out of ship-mode has the longest time duration due to the internal circuitry being disabled. This response is shown in Figure 35. The startup time takes approximately 100 ms due to the internal Nano-Power management circuitry needing to first complete the 64 ms sample and hold cycle.

Startup from the standby state is shown in Figure 37. This response is much faster due to the internal circuitry being pre-enabled. The startup time from this state is entirely dependent on the size of the output capacitor. The larger the capacitor, the longer it will take to charge during startup. With COUT = 22  $\mu$ F, the startup time is approximately 400  $\mu$ s. The buck converter can startup into a pre-biased output voltage.

The buck converter is disabled when the voltage on VSTOR drops below the VBAT\_UV condition. The buck converter continues to operate in pass (100% duty cycle) mode, passing the input voltage to the output, as long as VSTOR is greater than VBAT\_UV and less than VOUT.

#### 7.4.4 Thermal Shutdown

Rechargeable Li-ion batteries need protection from damage due to operation at elevated temperatures. The application should provide this battery protection and ensure that the ambient temperature is never elevated greater than the expected operational range of 85°C.

The bq25570 uses an integrated temperature sensor to monitor the junction temperature of the device. Once the temperature threshold is exceeded, the boost charger and buck converter are disabled. Once the temperature of the device drops below this threshold, the boost charger and buck converter resume operation. To avoid unstable operation near the overtemperature threshold, a built-in hysteresis of approximately 5°C has been implemented. Care should be taken to not over discharge the battery in this condition since the boost charger is disabled. However, if the supply voltage drops to the VBAT\_UV setting, the switch between VBAT and VSTOR will open and protect the battery even if the device is in thermal shutdown.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

#### 8.1.1 Energy Harvester Selection

The energy harvesting source (for example, solar panel, TEG, vibration element) must provide a minimum level of power for the IC to operate as designed. The IC's minimum input power required to exit cold start can be estimated as

$$PIN > PIN(CS) = VIN(CS) \times IIN(CS) > \frac{\left(I - STR\_ELM\_LEAK_{@1.8V} \times 1.8V\right) + \frac{\left(1.8V\right)^2}{RSTOR(CS)}}{0.05}$$

(6)

where I-STR\_ELM\_LEAK @1.8V is the storage element leakage current at 1.8 V and

RSTOR(CS) is the equivalent resitive load on VSTOR during cold start and 0.05 is an estimate of the worst case efficiency of the cold start circuit.

Once the IC is out of cold start and the system load has been activated (for example, using the VBAT\_OK signal), the energy harvesting element must provide the main boost charger with at least enough power to meet the average system load. Assuming RSTOR(AVG) represents the average resistive load on VSTOR, the simplified equation below gives an estimate of the IC's minimum input power needed during system operation:

$$PIN \times \eta_{EST} > PLOAD = \frac{(VBAT_OV)^2}{RSTOR(AVG)} + VBAT_OV \times I - STR_ELM_LEAK_{@VBAT_OV}$$

(7)

where  $\eta_{EST}$  can be derived from the datasheet efficiency curves for the given input voltage and current and VBAT\_OV. The simplified equation above assumes that, while the harvester is still providing power, the system goes into low power or sleep mode long enough to charge the storage element so that it can power the system when the harvester eventually is down. Refer to SLUC461 for a design example that sizes the energy harvester.

#### 8.1.2 Storage Element Selection

In order for the charge management circuitry to protect the storage element from over-charging or discharging, the storage element must be connected to VBAT pin and the system load tied to the VSTOR pin. Many types of elements can be used, such as capacitors, super capacitors or various battery chemistries. A storage element with 100  $\mu$ F equivalent capacitance is required to filter the pulse currents of the PFM switching charger. The equivalent capacitance of a battery can be computed as computed as

$$C_{EQ} = \frac{2 \times \text{mAHr}_{\text{BAT(CHRGD)}} \times 3600 \text{ s/Hr}}{V_{\text{BAT(CHRGD)}}}$$

(8)

In order for the storage element to be able to charge VSTOR capacitor (CSTOR) within the  $t_{VB\_HOT\_PLUG}$  (50 ms typical) window at hot-plug; therefore preventing the IC from entering cold start, the time constant created by the storage element's series resistance (plus the resistance of the internal PFET switch) and equivalent capacitance must be less than  $t_{VB\_HOT\_PLUG}$ . For example, a battery's resistance can be computed as:

$$R_{BAT} = V_{BAT} / I_{BAT(CONTINUOUS)}$$

from the battery specifications. (9)

The storage element must be sized large enough to provide all of the system load during periods when the harvester is no longer providing power. The harvester is expected to provide at least enough power to fully charge the storage element while the system is in low power or sleep mode. Assuming no load on VSTOR (i.e., the system is in low power or sleep mode), the following equation estimates charge time from voltage VBAT1 to VBAT2 for given input power is:

$$PIN \times \eta_{EST} \times t_{CHRG} = 1/2 \times CEQ \times (VBAT2^2 - VBAT1^2)$$

(10)

# **Application Information (continued)**

Refer to SLUC461 for a design example that sizes the storage element.

Note that if there are large load transients or the storage element has significant impedance then it may be necessary to increase the CSTOR capacitor from the 4.7 µF minimum or add additional capacitance to VBAT in order to prevent a droop in the VSTOR voltage. Refer to Inductor Selection for sizing capacitors.

#### 8.1.3 Inductor Selection

The boost charger and the buck converter each need an appropriately sized inductor for proper operation. The inductor's saturation current should be at least 25% higher than the expected peak inductor currents recommended below if system load transients on VSTOR and/or VOUT are expected. Since this device uses hysteretic control for both the boost charger and buck converter, both are considered naturally stable systems (single order transfer function).

#### 8.1.3.1 Boost Charger Inductor Selection

For the boost charger to operate properly, an inductor of appropriate value must be connected between LBOOST, pin 20, and VIN\_DC, pin 2. The boost charger internal control circuitry is designed to control the switching behavior with a nominal inductance of 22  $\mu$ H  $\pm$  20%. The inductor must have a peak current capability of > 300 mA with a low series resistance (DCR) to maintain high efficiency.

A list of inductors recommended for this device is shown in Table 3.

**Table 3. Boost Charger Inductor Selection**

| INDUCTANCE (µH) | DIMENSIONS (mm) | PART NUMBER  | MANUFACTURER |  |  |  |

|-----------------|-----------------|--------------|--------------|--|--|--|

| 22              | 4.0x4.0x1.7     | LPS4018-223M | Coilcraft    |  |  |  |

| 22              | 3.8x3.8x1.65    | 744031220    | Wuerth       |  |  |  |

#### 8.1.3.2 Buck Converter Inductor Selection