XAS

LMC6482-MIL

JAJSDD7 – JUNE 2017

# LMC6482-MIL CMOSデュアル・レール・ツー・レール入力および出力オペアンプ

#### 1 特長

- 特に記述のない限り標準値

- レール・ツー・レール入力同相電圧範囲(全温度範囲にわたって保証)

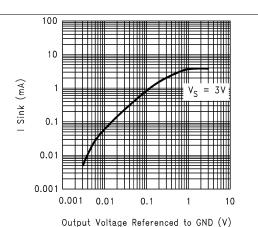

- レール・ツー・レール出力(電源レールの20mV 以内、100kΩ負荷)

- 3V、5V、15Vでの性能を保証

- 非常に優れたCMRRおよびPSRR: 82dB

- 非常に低い入力電流: 20fA

- 高い電圧ゲイン(R L = 500kΩ): 130dB

- 2kΩおよび600Ω負荷について動作を規定

- パワー・グッド出力

- VSSOPパッケージで供給

#### 2 アプリケーション

- データ収集システム

- トランスデューサ・アンプ

- 携帯型分析測定器

- 医療用計測機器

- アクティブ・フィルタ、ピーク検出器、サンプル・アンド・ホールド、pHメータ、電流ソース

- TLC272、TLC277の改良版

#### 3 概要

LMC6482-MILデバイスは、両方の電源レールを超える同相範囲を実現しています。レール・ツー・レール性能と、高いCMRRによる非常に優れた精度から、レール・ツー・レール入力アンプの中でも出色の製品です。このデバイスは、データ収集など大きな入力信号範囲を必要とするシステムに理想的です。また、LMC6482-MILはTLC272やTLC277など同相範囲の限られたアンプを使用する回路のアップグレードとしても優れています。

LMC6482-MILのレール・ツー・レール出力により、低電圧 および単一電源のシステムで最大のダイナミック信号範囲 が保証されます。デバイスの最低600Ωの負荷について、レール・ツー・レール出力が保証されます。低電圧特性と低消費電力が保証されているため、LMC6482-MILはバッテリで動作するシステムに特に適しています。LMC6482-MILは、SOIC-8デバイスのほぼ半分の大きさである、VSSOPパッケージでも供給されます。これらと同じ特長を持つクワッドCMOSオペアンプについては、LMC6484のデータシートを参照してください。

#### 製品情報(1)

| 型番          | パッケージ     | 本体サイズ(公称)     |  |  |  |  |  |  |  |  |

|-------------|-----------|---------------|--|--|--|--|--|--|--|--|

|             | SOIC (8)  | 4.90mm×3.91mm |  |  |  |  |  |  |  |  |

| LMC6482-MIL | VSSOP (8) | 3.00mm×3.00mm |  |  |  |  |  |  |  |  |

|             | PDIP (8)  | 9.81mm×6.35mm |  |  |  |  |  |  |  |  |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

レール・ツー・レール入力

#### レール・ツー・レール出力

## 目次

| 1 | 特長1                                                     |     | 7.2 Functional Block Diagram   | 10             |

|---|---------------------------------------------------------|-----|--------------------------------|----------------|

| 2 | アプリケーション1                                               |     | 7.3 Feature Description        | 10             |

| 3 | 概要1                                                     |     | 7.4 Device Functional Modes    | 17             |

| 4 | 改訂履歴                                                    | •   | Application and Implementation | 18             |

| 5 | Pin Configuration and Functions                         |     | 8.1 Application Information    | 18             |

| 6 | Specifications                                          |     | 8.2 Typical Applications       | 20             |

| • | 6.1 Absolute Maximum Ratings                            | ο.  | Power Supply Recommendations   | 27             |

|   | 6.2 ESD Ratings                                         | 40  | Layout                         | 27             |

|   | 6.3 Recommended Operating Conditions                    |     | 10.1 Layout Guidelines         | 2 <sup>-</sup> |

|   | 6.4 Thermal Information                                 |     | 10.2 Layout Example            | 2 <sup>-</sup> |

|   | 6.5 Electrical Characteristics for V <sup>+</sup> = 5 V | 4.4 | デバイスおよびドキュメントのサポート             | 29             |

|   | 6.6 Electrical Characteristics for V <sup>+</sup> = 3 V |     | 11.1 商標                        | 2              |

|   | 6.7 Typical Characteristics                             |     | 11.2 静電気放電に関する注意事項             | 2              |

| 7 | Detailed Description                                    |     | 11.3 Glossary                  | 2              |

|   | 7.1 Overview                                            | 40  | メカニカル、パッケージ、および注文情報            | 29             |

### 4 改訂履歴

| 日付 | 改訂内容 | 注  |

|----|------|----|

|    | *    | 初版 |

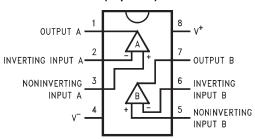

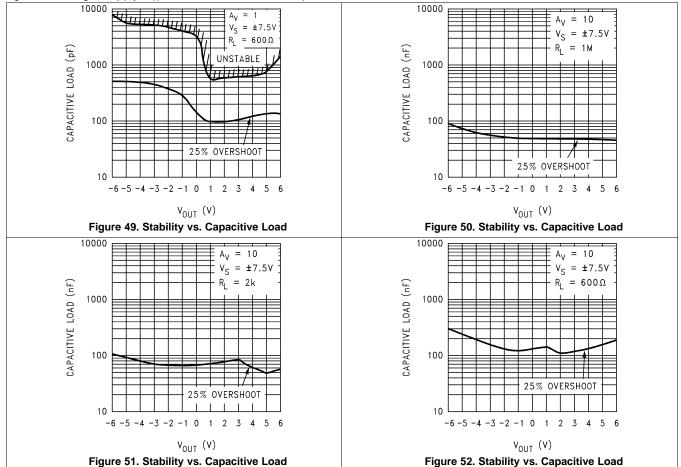

#### Pin Configuration and Functions

#### D, DGK and P Packages 8-Pin SOIC, VSSOP and PDIP (Top View)

#### **Pin Functions**

|     | PIN                  | TVDE | DECORIDATION                       |  |  |  |

|-----|----------------------|------|------------------------------------|--|--|--|

| NO. | NAME                 | TYPE | DESCRIPTION                        |  |  |  |

| 1   | OUTPUT A             | 0    | Output for Amplifier A             |  |  |  |

| 2   | INVERTING INPUT A    | I    | Inverting input for Amplifier A    |  |  |  |

| 3   | NONINVERTING INPUT A | I    | Noninverting input for Amplifier A |  |  |  |

| 4   | V-                   | Р    | Negative supply voltage input      |  |  |  |

| 5   | NONINVERTING INPUT B | I    | Noninverting input for Amplifier B |  |  |  |

| 6   | INVERTING INPUT B    | I    | Inverting input for Amplifier B    |  |  |  |

| 7   | OUTPUT B             | 0    | Output for Amplifier B             |  |  |  |

| 8   | V*                   | Р    | Positive supply voltage input      |  |  |  |

### **Specifications**

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)

|                                                   | M                 | N    | MAX                    | UNIT |

|---------------------------------------------------|-------------------|------|------------------------|------|

| Differential Input Voltage                        |                   |      | ±Supply Voltage        |      |

| Voltage at Input/Output Pin                       | (V <sup>-</sup> ) | -0.3 | (V <sup>+</sup> ) +0.3 | V    |

| Supply Voltage (V <sup>+</sup> - V <sup>-</sup> ) |                   |      | 16                     | V    |

| Current at Input Pin (3)                          | -                 | 5    | 5                      | mA   |

| Current at Output Pin (4) (5)                     | -3                | 80   | 30                     | mA   |

| Current at Power Supply Pin                       |                   |      | 40                     | mA   |

| Lead Temperature (Soldering, 10 sec.)             |                   |      | 260                    | °C   |

| Junction Temperature <sup>(6)</sup>               |                   |      | 150                    | °C   |

| Storage temperature, T <sub>stg</sub>             | -6                | 55   | 150                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

- Limiting input pin current is only necessary for input voltages that exceed absolute maximum input voltage ratings.

- Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of ±30 mA over long term may adversely affect reliability.

- Do not short circuit output to V<sup>+</sup>, when V<sup>+</sup> is greater than 13 V or reliability will be adversely affected.

- The maximum power dissipation is a function of  $T_{J(max)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(max)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly into a PC board.

#### 6.2 ESD Ratings

|                    |                         |                                                        | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                            |          | MIN         | MAX  | UNIT |

|----------------------------|----------|-------------|------|------|

| Supply Voltage             |          | 3           | 15.5 | V    |

| Junction Temperature Range | LMC6482M | <b>-</b> 55 | 125  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.4 Thermal Information

|                 |                                        | LMC6482-MIL | LMC6482-MIL | LMC6482-MIL |      |

|-----------------|----------------------------------------|-------------|-------------|-------------|------|

|                 | THERMAL METRIC <sup>(1)</sup>          | D (SOIC)    | DGK (VSSOP) | P (PDIP)    | UNIT |

|                 |                                        | 8 PINS      | 8 PINS      | 8 PINS      |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 155         | 194         | 90          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Electrical Characteristics for V<sup>+</sup> = 5 V

Unless otherwise specified, all limits specified for  $T_J = 25^{\circ}C$ ,  $V^+ = 5$  V,  $V^- = 0$  V,  $V_{CM} = V_O = V^+/2$  and  $R_L > 1$  M.

| D.                | DAMETED                                     | TEST COMPITIONS                                                                                              |     | T <sub>J</sub> = 25°C |                    | At Tempe | erature Ex         | tremes <sup>(1)</sup> | LINUT        |

|-------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----------------------|--------------------|----------|--------------------|-----------------------|--------------|

| PA                | ARAMETER                                    | TEST CONDITIONS                                                                                              | MIN | TYP <sup>(2)</sup>    | MAX <sup>(3)</sup> | MIN      | TYP <sup>(2)</sup> | MAX <sup>(3)</sup>    | UNIT         |

| DC Elec           | trical Characteris                          | stics                                                                                                        |     |                       |                    |          |                    |                       |              |

| Vos               | Input Offset<br>Voltage                     |                                                                                                              |     | 0.11                  | 3                  |          |                    | 3.8                   | mV           |

| TCV <sub>OS</sub> | Input Offset<br>Voltage<br>Average Drift    |                                                                                                              |     | 1                     |                    |          |                    |                       | μV/°C        |

| I <sub>B</sub>    | Input Current                               | See (4)                                                                                                      |     | 0.02                  |                    |          |                    | 10                    | рА           |

| I <sub>OS</sub>   | Input Offset<br>Current                     | See <sup>(4)</sup>                                                                                           |     | 0.01                  |                    |          |                    | 5                     | рА           |

| C <sub>IN</sub>   | Common-Mode<br>Input<br>Capacitance         |                                                                                                              |     | 3                     |                    |          |                    |                       | pF           |

| R <sub>IN</sub>   | Input<br>Resistance                         |                                                                                                              |     | 10                    |                    |          |                    |                       | $Tera\Omega$ |

| CMDD              | Common-Mode                                 | 0 V ≤ V <sub>CM</sub> ≤ 15 V<br>V <sup>+</sup> = 15 V                                                        | 65  | 82                    |                    | 60       |                    |                       | ٩D           |

| CMRR              | Rejection Ratio                             | 0 V ≤ V <sub>CM</sub> ≤ 5 V<br>V <sup>+</sup> = 5 V                                                          | 65  | 82                    |                    | 60       |                    |                       | dB           |

| +PSRR             | Positive Power<br>Supply<br>Rejection Ratio | $5 \text{ V} \le \text{V}^+ \le 15 \text{ V},$<br>$\text{V}^- = 0 \text{ V}$<br>$\text{V}_0 = 2.5 \text{ V}$ | 65  | 82                    |                    | 60       |                    |                       | dB           |

| -PSRR             | Negative Power<br>Supply<br>Rejection Ratio | $-5 \text{ V} \le \text{V}^- \le -15 \text{ V}, \text{ V}^+ = 0 \text{ V}$<br>$\text{V}_0 = -2.5 \text{ V}$  | 65  | 82                    |                    | 60       |                    |                       | dB           |

<sup>(1)</sup> See Recommended Operating Conditions for operating temperature ranges.

RUMENTS

<sup>(2)</sup> Typical Values represent the most likely parametric norm.

<sup>(3)</sup> All limits are specified by testing or statistical analysis.

<sup>(4)</sup> Ensured limits are dictated by tester limitations and not device performance. Actual performance is reflected in the typical value.

## Electrical Characteristics for $V^* = 5 V$ (continued)

Unless otherwise specified, all limits specified for  $T_1 = 25^{\circ}C$ ,  $V^+ = 5$  V,  $V^- = 0$  V,  $V_{CM} = V_{C} = V^+/2$  and  $R_1 > 1$  M.

|                   |                                          |                                                                                      |          |      | $T_J = 25^{\circ}C$  |                    | At Tempe       | rature Ex          | tremes <sup>(1)</sup> |                    |  |

|-------------------|------------------------------------------|--------------------------------------------------------------------------------------|----------|------|----------------------|--------------------|----------------|--------------------|-----------------------|--------------------|--|

| P                 | PARAMETER                                | TEST CO                                                                              | NDITIONS | MIN  | TYP <sup>(2)</sup>   | MAX <sup>(3)</sup> | MIN            | TYP <sup>(2)</sup> | MAX <sup>(3)</sup>    | UNIT               |  |

| \ /               | Input Common-                            | V <sup>+</sup> = 5 V and 15<br>For CMRR ≥ 50 c                                       |          |      | V <sup>-</sup> - 0.3 | -0.25              |                |                    | 0                     |                    |  |

| V <sub>CM</sub>   | Mode Voltage<br>Range                    |                                                                                      |          |      | V <sup>+</sup> + 0.3 |                    | V <sup>+</sup> |                    |                       | V                  |  |

|                   |                                          | $R_L = 2 k\Omega^{(5)(4)}$                                                           | Sourcing | 120  | 666                  |                    | 60             |                    |                       |                    |  |

| $A_V$             | Large Signal                             |                                                                                      | Sinking  | 35   | 75                   |                    | 18             |                    |                       | V/mV               |  |

| AV                | Voltage Gain                             | $R_L = 600 \ \Omega^{(5)(4)}$                                                        | Sourcing | 50   | 300                  |                    | 25             |                    |                       | V/IIIV             |  |

|                   |                                          |                                                                                      | Sinking  | 15   | 35                   |                    | 8              |                    |                       |                    |  |

| $V_{O}$           | Output Swing                             | $V^{+} = 5 V$                                                                        |          | 4.8  | 4.9                  |                    | 4.7            |                    |                       | V                  |  |

|                   |                                          | $R_L = 2 \text{ k}\Omega \text{ to } V^+/2$                                          |          |      | 0.1                  | 0.18               |                |                    | 0.24                  | •                  |  |

|                   |                                          | V <sup>+</sup> = 5 V                                                                 |          | 4.5  | 4.7                  |                    | 4.24           |                    |                       | V                  |  |

|                   |                                          | $R_L = 600 \Omega \text{ to V}^+$                                                    | /2       |      | 0.3                  | 0.5                |                |                    | 0.65                  | •                  |  |

|                   |                                          | V <sup>+</sup> = 15 V                                                                |          | 14.4 | 14.7                 |                    | 14.2           |                    |                       | V                  |  |

|                   |                                          | $R_L = 2k \Omega \text{ to } V^+/2$                                                  | 2        |      | 0.16                 | 0.32               |                |                    | 0.45                  | •                  |  |

|                   |                                          | $V^{+} = 15 \text{ V}$                                                               | 10       | 13.4 | 14.1                 |                    | 13             |                    |                       | V                  |  |

|                   |                                          | $R_L = 600 \Omega \text{ to V}^+$                                                    | 0.0      |      | 1                    |                    |                | 1.3                | •                     |                    |  |

|                   | Output Short<br>Circuit Current          | Sourcing, $V_0 = 0$                                                                  |          | 16   | 20                   |                    | 10             |                    |                       | A                  |  |

| I <sub>SC</sub>   | V <sup>+</sup> = 5 V                     | Sinking, $V_0 = 5 \ $                                                                | /        | 11   | 15                   |                    | 8              |                    |                       | mA                 |  |

|                   | Output Short                             | Sourcing, V <sub>O</sub> = 0                                                         | V        | 28   | 30                   |                    | 20             |                    |                       |                    |  |

| I <sub>SC</sub>   | Circuit Current<br>V <sup>+</sup> = 15 V | Sinking,<br>$V_O = 12 V^{(6)}$                                                       |          | 30   | 30                   |                    | 22             |                    |                       | mA                 |  |

|                   | 0                                        | Both Amplifiers<br>$V^+ = +5 \text{ V},$<br>$V_O = V^+/2$                            |          |      | 1                    | 1.4                |                |                    | 1.9                   | 1                  |  |

| I <sub>S</sub>    | Supply Current                           | Both Amplifiers<br>$V^+ = 15 \text{ V},$<br>$V_O = V^+/2$                            |          |      | 1.3                  | 1.6                |                |                    | 2                     | mA                 |  |

| AC Ele            | ectrical Characteris                     | stics                                                                                |          |      |                      |                    |                |                    |                       |                    |  |

| SR                | Slew Rate                                | See (7)                                                                              |          | 0.9  | 1.3                  |                    | 0.54           |                    |                       | V/μs               |  |

| GBW               | Gain-Bandwidth<br>Product                | V <sup>+</sup> = 15 V                                                                |          |      | 1.5                  |                    |                |                    |                       | MHz                |  |

| $\phi_{\text{m}}$ | Phase Margin                             |                                                                                      |          |      | 50                   |                    |                |                    |                       | Deg                |  |

| $G_m$             | Gain Margin                              |                                                                                      |          |      | 15                   |                    |                |                    |                       | dB                 |  |

|                   | Amp-to-Amp<br>Isolation                  | See <sup>(8)</sup>                                                                   |          |      | 150                  |                    |                |                    |                       | dB                 |  |

| e <sub>n</sub>    | Input-Referred<br>Voltage Noise          | F = 1 kHz<br>V <sub>cm</sub> = 1 V                                                   |          |      | 37                   |                    |                |                    |                       | nV/√ <del>Hz</del> |  |

| In                | Input-Referred<br>Current Noise          | F = 1 kHz                                                                            |          |      | 0.03                 |                    |                |                    |                       | pA/√Hz             |  |

|                   | Total Harmonic                           | $F = 10 \text{ kHz}, A_V = R_L = 10 \text{ k}\Omega, V_O = 4.1 \text{ V}_{PP}$       | -2       |      | 0.01%                |                    |                |                    |                       |                    |  |

| T.H.D.            | Distortion                               | F = 10 kHz, $A_V = -2$<br>$R_L = 10 k\Omega$ ,<br>$V_O = 8.5 V_{PP}$<br>$V^+ = 10 V$ |          |      | 0.01%                |                    |                |                    |                       |                    |  |

<sup>(6)</sup>

$V^+$  = 15 V,  $V_{CM}$  = 7.5 V and  $R_L$  connected to 7.5 V. For Sourcing tests, 7.5 V  $\leq$   $V_O \leq$  11.5 V. For Sinking tests, 3.5 V  $\leq$   $V_O \leq$  7.5 V. Do not short circuit output to  $V^+$ , when  $V^+$  is greater than 13 V or reliability will be adversely affected. V + = 15V. Connected as Voltage Follower with 10V step input. Number specified is the slower of either the positive or negative slew

Input referred, V<sup>+</sup> = 15 V and R<sub>L</sub> = 100 k $\Omega$  connected to 7.5 V. Each amp excited in turn with 1 kHz to produce V<sub>O</sub> = 12 V<sub>PP</sub>.

## **STRUMENTS**

### 6.6 Electrical Characteristics for $V^+ = 3 V$

Unless otherwise specified, all limits specified for  $T_J = 25^{\circ}C$ ,  $V^+ = 3V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$  and  $R_L > 1M$ .

| PARAMETER         |                                          | TEST CONDITIONS                                                                 |                | T <sub>J</sub> = 25°C | At<br>E            | UNIT |                    |                    |       |

|-------------------|------------------------------------------|---------------------------------------------------------------------------------|----------------|-----------------------|--------------------|------|--------------------|--------------------|-------|

|                   |                                          |                                                                                 | MIN            | TYP <sup>(2)</sup>    | MAX <sup>(3)</sup> | MIN  | TYP <sup>(2)</sup> | MAX <sup>(3)</sup> |       |

| DC Elec           | trical Characteri                        | stics                                                                           |                |                       | ·                  |      |                    |                    | •     |

| Vos               | Input Offset<br>Voltage                  |                                                                                 |                | 0.9                   | 3                  |      |                    | 3.8                | mV    |

| TCV <sub>OS</sub> | Input Offset<br>Voltage<br>Average Drift |                                                                                 |                | 2                     |                    |      |                    |                    | μV/°C |

| I <sub>B</sub>    | Input Bias<br>Current                    |                                                                                 |                | 0.02                  |                    |      |                    |                    | рА    |

| Ios               | Input Offset<br>Current                  |                                                                                 |                | 0.01                  |                    |      |                    |                    | рА    |

| CMRR              | Common<br>Mode<br>Rejection<br>Ratio     | 0 V ≤ V <sub>CM</sub> ≤ 3 V                                                     | 60             | 74                    |                    |      |                    |                    | dB    |

| PSRR              | Power Supply<br>Rejection<br>Ratio       | 3 V ≤ V <sup>+</sup> ≤ 15 V, V <sup>-</sup> = 0 V                               | 60             | 80                    |                    |      |                    |                    | dB    |

|                   | Input                                    | For CMRR ≥ 50 dB                                                                |                | V⁻ <b>-</b> 0.25      | 0                  |      |                    |                    | V     |

| V <sub>CM</sub>   | Common-<br>Mode Voltage<br>Range         |                                                                                 | V <sup>+</sup> | V <sup>+</sup> + 0.25 |                    |      |                    |                    | ٧     |

|                   |                                          | D 21:0 to 1/1/0                                                                 |                | 2.8                   |                    |      |                    |                    | V     |

| .,                | Outrot Coding                            | $R_L = 2 k\Omega$ to $V^+/2$                                                    |                | 0.2                   |                    |      |                    |                    | V     |

| Vo                | Output Swing                             | $R_L = 600 \Omega \text{ to V}^+/2$                                             | 2.5            | 2.7                   |                    |      |                    |                    | V     |

|                   |                                          |                                                                                 |                | 0.37                  | 0.6                |      |                    |                    | V     |

| Is                | Supply Current                           | Both Amplifiers                                                                 |                | 0.825                 | 1.2                |      |                    | 1.6                | mA    |

| AC Elec           | trical Characteri                        | stics                                                                           |                |                       |                    |      |                    |                    |       |

| SR                | Slew Rate                                | See <sup>(4)</sup>                                                              |                | 0.9                   |                    |      |                    |                    | V/μs  |

| GBW               | Gain-<br>Bandwidth<br>Product            |                                                                                 |                | 1                     |                    |      |                    |                    | MHz   |

| T.H.D.            | Total<br>Harmonic<br>Distortion          | $F = 10 \text{ kHz}, A_V = -2$<br>$R_L = 10 \text{ k}Ω, V_O = 2 \text{ V}_{PP}$ |                | 0.01%                 |                    |      |                    |                    |       |

See *Recommended Operating Conditions* for operating temperature ranges. Typical Values represent the most likely parametric norm.

All limits are specified by testing or statistical analysis.

Connected as voltage Follower with 2-V step input. Number specified is the slower of either the positive or negative slew rates.

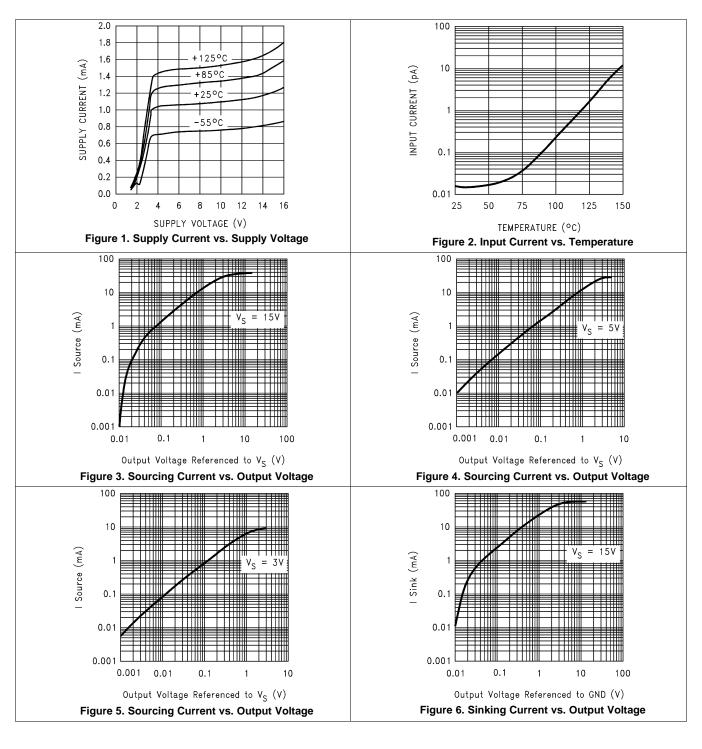

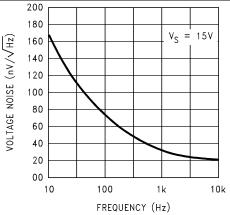

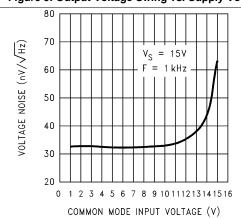

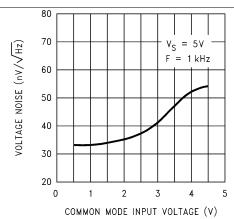

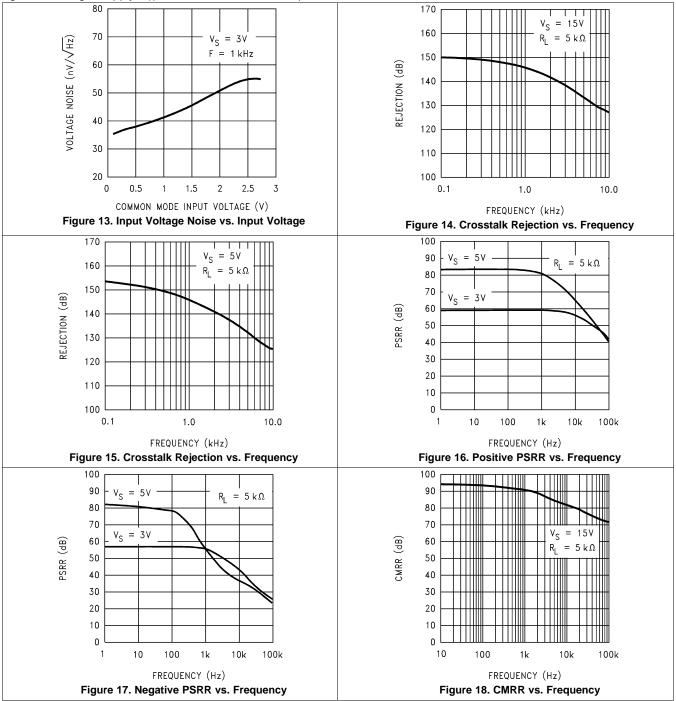

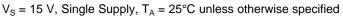

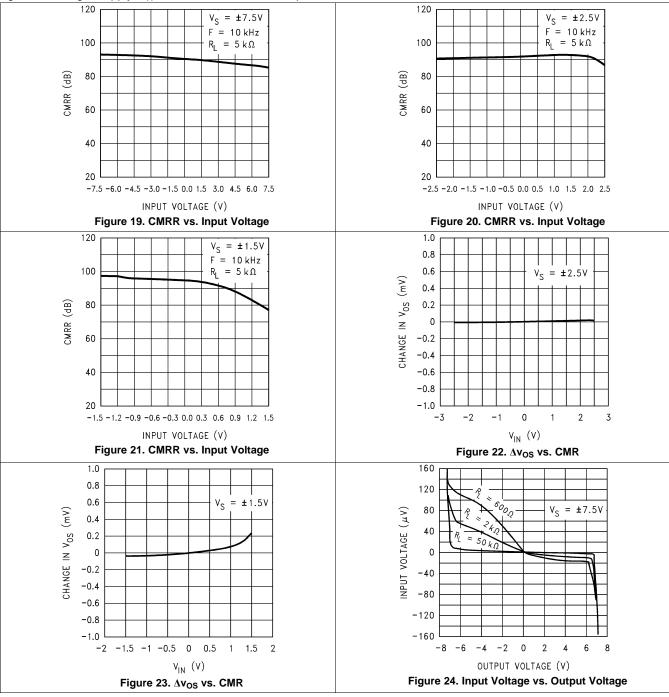

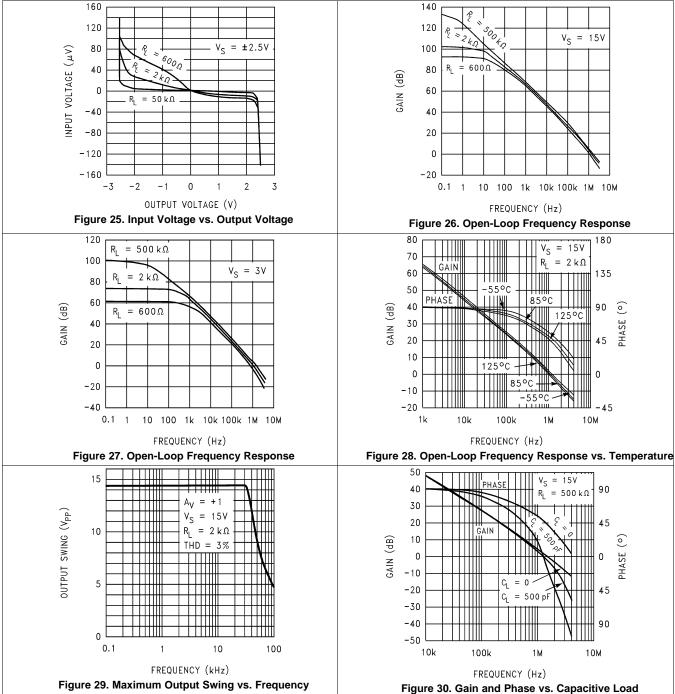

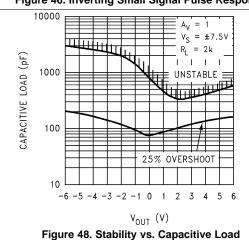

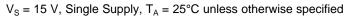

6.7 Typical Characteristics

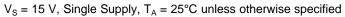

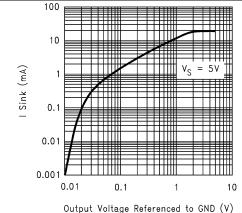

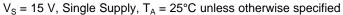

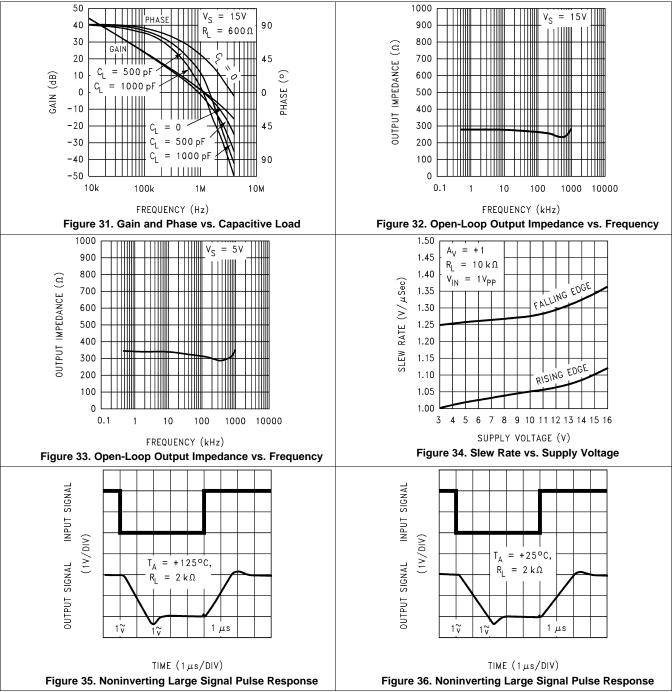

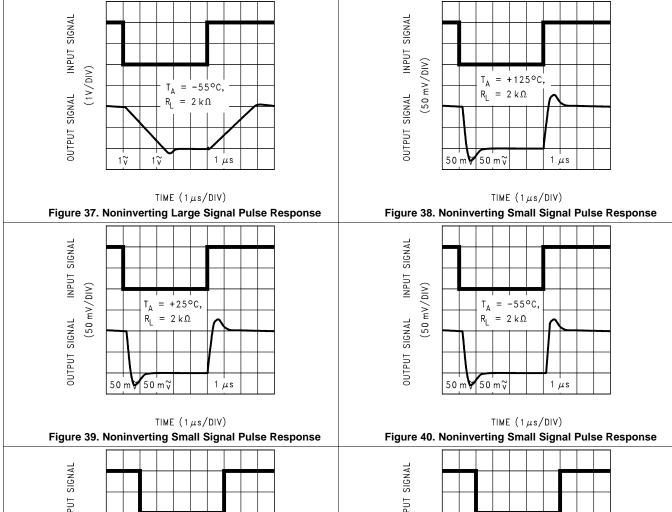

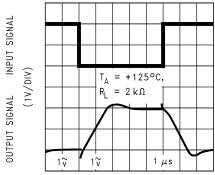

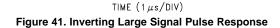

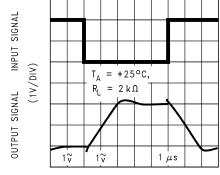

$V_S = 15 \text{ V}$ , Single Supply,  $T_A = 25^{\circ}\text{C}$  unless otherwise specified

#### TEXAS INSTRUMENTS

Figure 7. Sinking Current vs. Output Voltage

Figure 8. Sinking Current vs. Output Voltage

Figure 9. Output Voltage Swing vs. Supply Voltage

Figure 10. Input Voltage Noise vs. Frequency

Figure 11. Input Voltage Noise vs. Input Voltage

Figure 12. Input Voltage Noise vs. Input Voltage

#### TEXAS INSTRUMENTS

## TEXAS INSTRUMENTS

**Typical Characteristics (continued)**

## $V_S = 15 \text{ V}$ , Single Supply, $T_A = 25^{\circ}\text{C}$ unless otherwise specified

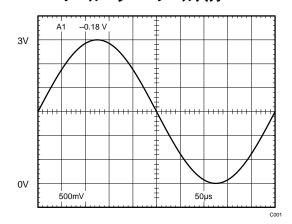

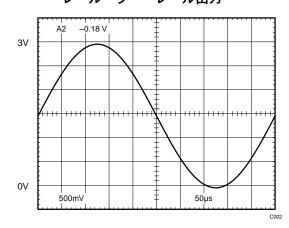

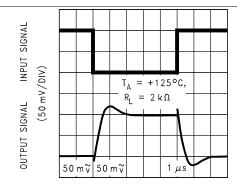

$\label{eq:time_time} \footnotesize \mbox{TIME } (1\,\mu\mbox{s}/\mbox{DIV})$  Figure 42. Inverting Large Signal Pulse Response

## TEXAS INSTRUMENTS

Figure 43. Inverting Large Signal Pulse Response

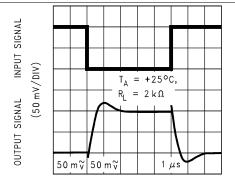

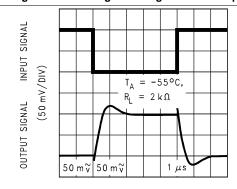

TIME (1  $\mu$ s/DIV) Figure 44. Inverting Small Signal Pulse Response

TIME  $(1 \mu s/DIV)$

$\label{eq:time_time} {\rm TIME}~(1\,\mu{\rm s/DIV})$  Figure 46. Inverting Small Signal Pulse Response

## TEXAS INSTRUMENTS

#### 7 Detailed Description

#### 7.1 Overview

The LMC6482-MIL is a dual CMOS operational amplifier that supports both rail-to-rail inputs and outputs. It may be operated in both dual supply mode and single supply mode.

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Amplifier Topology

The LMC6482-MIL incorporates specially designed wide-compliance range current mirrors and the body effect to extend input common-mode range to each supply rail. Complementary paralleled differential input stages, like the type used in other CMOS and bipolar rail-to-rail input amplifiers, were not used because of their inherent accuracy problems due to CMRR, crossover distortion, and open-loop gain variation.

The LMC6482-MILs input stage design is complemented by an output stage capable of rail-to-rail output swing even when driving a large load. Rail-to-rail output swing is obtained by taking the output directly from the internal integrator instead of an output buffer stage.

#### 7.3.2 Input Common-Mode Voltage Range

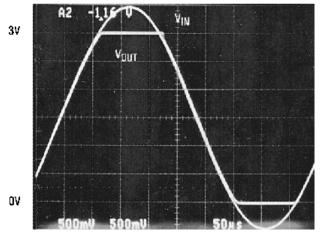

Unlike Bi-FET amplifier designs, the LMC6482-MIL does not exhibit phase inversion when an input voltage exceeds the negative supply voltage. Figure 53 shows an input voltage exceeding both supplies with no resulting phase inversion on the output.

An input voltage signal exceeds the LMC6482-MIL power supply voltages with no output phase inversion.

Figure 53. Input Voltage

The absolute maximum input voltage is 300 mV beyond either supply rail at room temperature. Voltages greatly exceeding this absolute maximum rating, as in Figure 54, can cause excessive current to flow in or out of the input pins possibly affecting reliability.

JAJSDD7-JUNE 2017

#### **Feature Description (continued)**

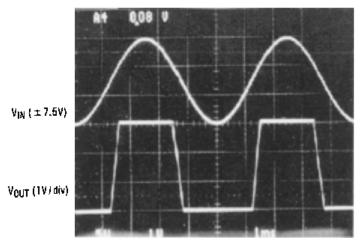

A ±7.5-V input signal greatly exceeds the 3-V supply in Figure 55 causing no phase inversion due to R<sub>I</sub>.

Figure 54. Input Signal

Applications that exceed this rating must externally limit the maximum input current to ±5 mA with an input resistor (R<sub>I</sub>) as shown in Figure 55.

R<sub>I</sub> input current protection for voltages exceeding the supply voltages.

Figure 55. R<sub>I</sub> Input Current Protection for **Voltages Exceeding the Supply Voltages**

#### 7.3.3 Rail-to-Rail Output

The approximated output resistance of the LMC6482-MIL is  $180-\Omega$  sourcing and  $13-0\Omega$  sinking at  $V_S = 3$  V and 110- $\Omega$  sourcing and 80- $\Omega$  sinking at Vs = 5 V. Using the calculated output resistance, maximum output voltage swing can be estimated as a function of load.

#### 7.4 Device Functional Modes

The LMC6482-MIL may be used in applications where each amplifier channel is used independently, or in applications in which the channels are cascaded. See *Typical Applications* for more information.

## TEXAS INSTRUMENTS

#### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

#### 8.1.1 Upgrading Applications

The LMC6484 quads and LMC6482-MIL duals have industry-standard pin outs to retrofit existing applications. System performance can be greatly increased by the features of the LMC6482-MIL. The key benefit of designing in the LMC6482-MIL is increased linear signal range. Most op-amps have limited input common-mode ranges. Signals that exceed this range generate a nonlinear output response that persists long after the input signal returns to the common-mode range.

Linear signal range is vital in applications such as filters where signal peaking can exceed input common-mode ranges resulting in output phase inversion or severe distortion.

#### 8.1.2 Data Acquisition Systems

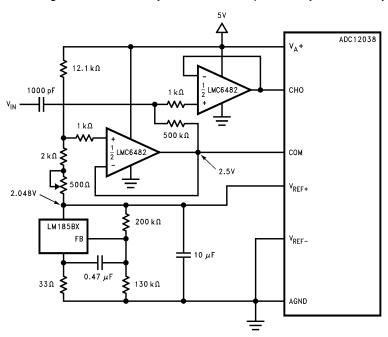

Low power, single supply data acquisition system solutions are provided by buffering the ADC12038 with the LMC6482-MIL (Figure 56). Capable of using the full supply range, the LMC6482-MIL does not require input signals to be scaled down to meet limited common-mode voltage ranges. The LMC4282 CMRR of 82 dB maintains integral linearity of a 12-bit data acquisition system to ±0.325 LSB. Other rail-to-rail input amplifiers with only 50 dB of CMRR will degrade the accuracy of the data acquisition system to only 8 bits.

Operating from the same supply voltage, the LMC6482-MIL buffers the ADC12038 maintaining excellent accuracy.

Figure 56. Buffering the ADC12038 With the LMC6482-MIL

#### Application Information (continued)

#### 8.1.3 Instrumentation Circuits

The LMC6482-MIL has the high input impedance, large common-mode range and high CMRR needed for designing instrumentation circuits. Instrumentation circuits designed with the LMC6482-MIL can reject a larger range of common-mode signals than most in-amps. This makes instrumentation circuits designed with the LMC6482-MIL an excellent choice of noisy or industrial environments. Other applications that benefit from these features include analytic medical instruments, magnetic field detectors, gas detectors, and silicon-based transducers.

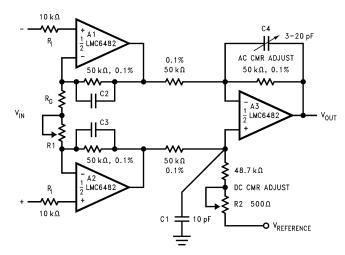

A small valued potentiometer is used in series with R<sub>q</sub> to set the differential gain of the 3-op-amp instrumentation circuit in Figure 57. This combination is used instead of one large valued potentiometer to increase gain trim accuracy and reduce error due to vibration.

Figure 57. Low Power 3-Op-Amp Instrumentation Amplifier

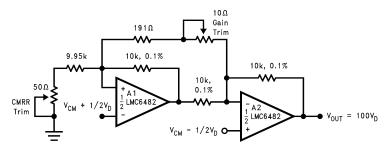

A 2-op-amp instrumentation amplifier designed for a gain of 100 is shown in Figure 58. Low sensitivity trimming is made for offset voltage, CMRR, and gain. Low cost and low power consumption are the main advantages of this 2-op-amp circuit.

Higher frequency and larger common-mode range applications are best facilitated by a 3-op-amp instrumentation amplifier.

Figure 58. Low-Power Two-Op-Amp Instrumentation Amplifier

#### 8.1.4 Spice Macromodel

A spice macromodel is available for the LMC6482-MIL. This model includes accurate simulation of the following:

- Input common-mode voltage range

- Frequency and transient response

- GBW dependence on loading conditions

- Quiescent and dynamic supply current

- Output swing dependence on loading conditions

## TEXAS INSTRUMENTS

#### **Application Information (continued)**

Many more characteristics are listed on the macromodel disk.

Contact your local TI sales office to obtain an operational amplifier spice model library disk.

#### 8.2 Typical Applications

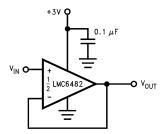

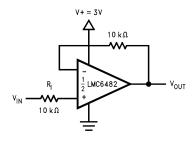

#### 8.2.1 3-V Single Supply Buffer Circuit

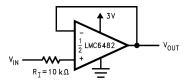

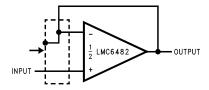

Figure 59. 3-V Single Supply Buffer Circuit

#### 8.2.1.1 Design Requirements

For best performance, ensure that the input voltage swing is between V+ and V-.

Ensure that the input does not exceed the common-mode input range.

To reduce the risk of destabilizing the output, use resistive isolation on the output when driving capacitive loads (see the *Detailed Design Procedure* section).

When large feedback resistors are used, it may be necessary to compensate for parasitic capacitance on the input. See the *Detailed Design Procedure* section.

#### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Capacitive Load Compensation

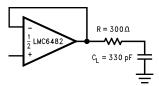

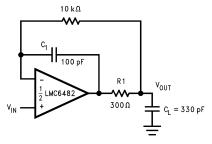

Capacitive load compensation can be accomplished using resistive isolation as shown in Figure 60. This simple technique is useful for isolating the capacitive inputs of multiplexers and A/D converters.

Figure 60. Resistive Isolation of a 330-pF Capacitive Load

#### **Typical Applications (continued)**

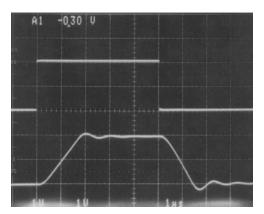

Figure 61. Pulse Response of the LMC6482-MIL Circuit in Figure 60

#### 8.2.1.2.1.1 Capacitive Load Tolerance

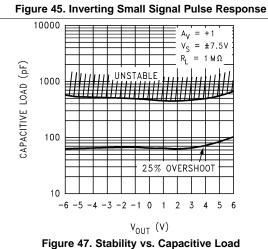

The LMC6482-MIL can typically directly drive a 100-pF load with  $V_S = 15$  V at unity gain without oscillating. The unity gain follower is the most sensitive configuration. Direct capacitive loading reduces the phase margin of opamps. The combination of the output impedance of the op-amp and the capacitive load induces phase lag. This results in either an underdamped pulse response or oscillation.

Improved frequency response is achieved by indirectly driving capacitive loads, as shown in Figure 62.

Compensated to handle a 330pF capacitive load.

Figure 62. LMC6482-MIL Noninverting Amplifier

R1 and C1 serve to counteract the loss of phase margin by feeding forward the high-frequency component of the output signal back to the amplifiers inverting input, thereby preserving phase margin in the overall feedback loop. The values of R1 and C1 are experimentally determined for the desired pulse response. The resulting pulse response is shown in Figure 63.

## TEXAS INSTRUMENTS

#### **Typical Applications (continued)**

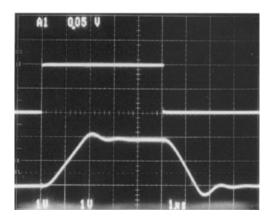

Figure 63. Pulse Response of LMC6482-MIL Circuit in Figure 62

#### 8.2.1.2.1.2 Compensating for Input Capacitance

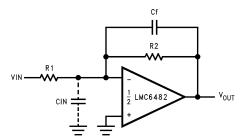

It is quite common to use large values of feedback resistance with amplifiers that have ultralow input current, like the LMC6482-MIL. Large feedback resistors can react with small values of input capacitance due to transducers, photo diodes, and circuits board parasitics to reduce phase margins.

Figure 64. Canceling the Effect of Input Capacitance

The effect of input capacitance can be compensated for by adding a feedback capacitor. The feedback capacitor (as in Figure 64),  $C_f$ , is first estimated by:

$$\frac{1}{2\pi R_1 C_{|N|}} \ge \frac{1}{2\pi R_2 C_f} \tag{1}$$

or

$$R_1 C_{IN} \le R_2 C_f \tag{2}$$

which typically provides significant overcompensation.

Printed-circuit-board stray capacitance may be larger or smaller than that of a bread-board, so the actual optimum value for  $C_f$  may be different. The values of  $C_f$  should be checked on the actual circuit. (Refer to the LMC660 quad CMOS amplifier data sheet for a more detailed discussion.)

#### 8.2.1.2.1.3 Offset Voltage Adjustment

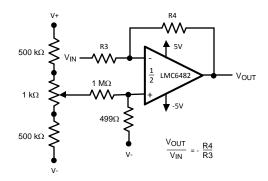

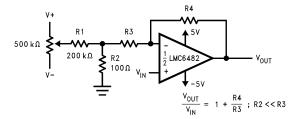

Offset voltage adjustment circuits are illustrated in Figure 65 and Figure 66. Large value resistances and potentiometers are used to reduce power consumption while providing typically  $\pm 2.5$  mV of adjustment range, referred to the input, for both configurations with  $V_S = \pm 5$  V.

#### **Typical Applications (continued)**

**NSTRUMENTS**

Figure 65. Inverting Configuration Offset Voltage Adjustment

Figure 66. Noninverting Configuration Offset Voltage Adjustment

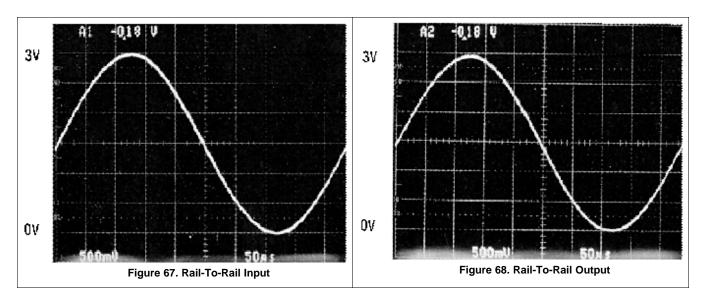

#### 8.2.1.3 Application Curves

#### 8.2.2 Typical Single-Supply Applications

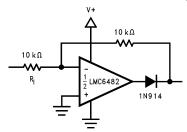

The circuit in Figure 69 uses a single supply to half-wave rectify a sinusoid centered about ground. R<sub>I</sub> limits current into the amplifier caused by the input voltage exceeding the supply voltage. Full-wave rectification is provided by the circuit in Figure 71.

## TEXAS INSTRUMENTS

### **Typical Applications (continued)**

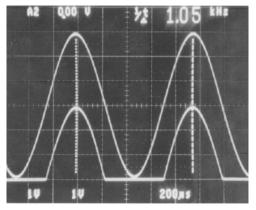

Figure 70. Half-Wave Rectifier Waveform

Typical Applications (continued)

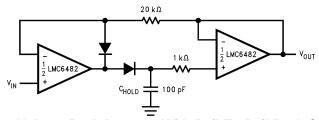

In Figure 75 dielectric absorption and leakage is minimized by using a polystyrene or polyethylene hold capacitor. The droop rate is primarily determined by the value of  $C_H$  and diode leakage current. The ultralow input current of the LMC6482-MIL has a negligible effect on droop.

Figure 71. Full-Wave Rectifier With Input Current Protection (R<sub>I</sub>)

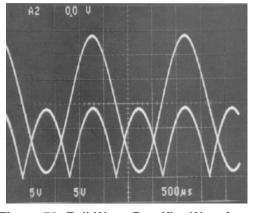

Figure 72. Full-Wave Rectifier Waveform

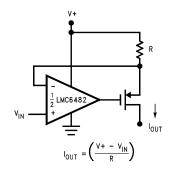

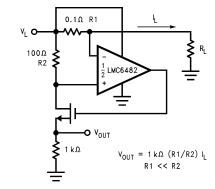

Figure 73. Large Compliance Range Current Source

Figure 74. Positive Supply Current Sense

Figure 75. Low-Voltage Peak Detector With Rail-To-Rail Peak Capture Range

## Instruments

#### **Typical Applications (continued)**

The high CMRR (82 dB) of the LMC6482-MIL allows excellent accuracy throughout the rail-to-rail dynamic capture range of the circuit.

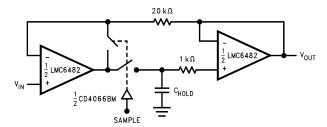

Figure 76. Rail-To-Rail Sample and Hold

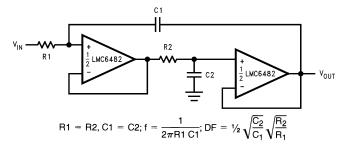

The low-pass filter circuit in Figure 77 can be used as an anti-aliasing filter with the same voltage supply as the A/D converter.

Filter designs can also take advantage of the LMC6482-MIL ultralow input current. The ultralow input current yields negligible offset error even when large value resistors are used. This in turn allows the use of smaller valued capacitors which take less board space and cost less.

Figure 77. Rail-To-Rail Single Supply Low Pass Filter

JAJSDD7-JUNE 2017

#### Power Supply Recommendations

The LMC6482-MIL can be operated over a supply range of 3 V to 15 V. To achieve noise immunity as appropriate to the application, it is important to use good PCB layout practices for power supply rails and planes, as well as using bypass capacitors connected between the power supply pins and ground.

#### Layout

#### 10.1 Layout Guidelines

It is generally recognized that any circuit which must operate with less than 1000 pA of leakage current requires special layout of the PC board. When one wishes to take advantage of the ultralow input current of the LMC6482-MIL, typically less than 20 fA, it is essential to have an excellent layout. Fortunately, the techniques of obtaining low leakages are quite simple. First, the user must not ignore the surface leakage of the PCB, even through it may sometimes appear acceptably low, because under conditions of high humidity or dust or contamination, the surface leakage will be appreciable.

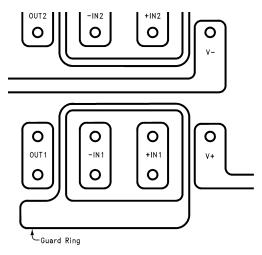

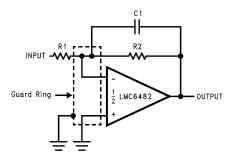

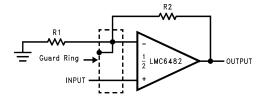

To minimize the effect of any surface leakage, lay out a ring of foil completely surrounding the LM6482s inputs and the terminals of capacitors, diodes, conductors, resistors, relay terminals, and so forth connected to the inputs of the op-amp, as in Figure 78. To have a significant effect, guard rings should be placed on both the top and bottom of the PCB. This PC foil must then be connected to a voltage which is at the same voltage as the amplifier inputs, because no leakage current can flow between two points at the same potential. For example, a PCB trace-to-pad resistance of  $10^{12} \Omega$ , which is normally considered a very large resistance, could leak 5 pA if the trace were a 5-V bus adjacent to the pad of the input. This would cause a 250 times degradation from the actual performance of the LMC6482-MIL. However, if a guard ring is held within 5 mV of the inputs, then even a resistance of  $10^{11} \Omega$  would cause only 0.05 pA of leakage current. See Figure 79 through Figure 81 for typical connections of guard rings for standard op-amp configurations.

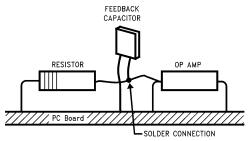

The designer should be aware that when it is inappropriate to lay out a PCB for the sake of just a few circuits, another technique is even better than a guard ring on a PCB: Do not insert the input pin of the amplifier into the PCB at all, but bend it up in the air and use only air as an insulator. Air is an excellent insulator. In this case you may have to forego some of the advantages of PCB construction, but the advantages are sometimes well worth the effort of using point-to-point up-in-the-air wiring. See Figure 82.

#### 10.2 Layout Example

Figure 78. Example of Guard Ring in PCB Layout Typical Connections of Guard Rings

27

#### **Layout Example (continued)**

Figure 79. Inverting Amplifier Typical Connections of Guard Rings

Figure 80. Noninverting Amplifier Typical Connections of Guard Rings

Figure 81. Follower Typical Connections of Guard Rings

(Input pins are lifted out of PCB and soldered directly to components. All other pins connected to PCB.)

Figure 82. Air Wiring

JAJSDD7-JUNE 2017 www.tij.co.jp

### 11 デバイスおよびドキュメントのサポート

#### 11.1 商標

All trademarks are the property of their respective owners.

#### 11.2 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防 上するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

#### 11.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

#### 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスに ついて利用可能な最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もありま す。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

#### PACKAGE OPTION ADDENDUM

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp    | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|------------------|--------------|----------------------|---------|

|                  |        |              |                    |      |                |              | (6)                           |                  |              |                      |         |

| LMC6482AI MDA    | ACTIVE | DIESALE      | Y                  | 0    | 324            | RoHS & Green | Call TI                       | Level-1-NA-UNLIM | -40 to 85    |                      | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供 する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

Copyright © 2020, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社