ΑFI

### LMP91050

2012年1月

# 非分散型赤外線 (NDIR) センシング・アプリケーション向けコンフィギュラブル AFE

#### 概要

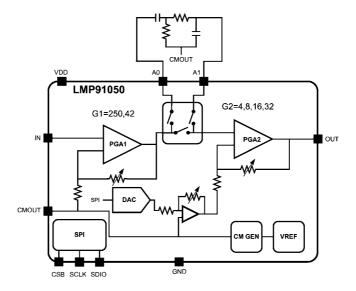

LMP91050 はサーモパイル・センサ向けに最適化されたプログラマブル集積型センサ・アナログ・フロント・エンド (AFE) で、主にNDIR アプリケーションで使用されます。センサとマイクロコントローラの間で完全なシグナルパス・ソリューションとしての役割を果たし、サーモパイル電圧に比例する出力電圧を生成します。LMP91050 のプログラム機能を利用すると、複数のサーモパイル・センサを複数のディスクリート・ソリューションではなく単一の設計によってサポートできます。

LMP91050 は、プログラマブル・ゲイン・アンプ (PGA)、「暗フェーズ」オフセット・キャンセル回路、出力ダイナミック・レンジを広げる可変コモンモード・ジェネレータ (1.15V または2.59V)を備えています。PGA は 167V/V ~ 1,335V/V の低ゲイン範囲と1,002V/V ~ 7,986V/V の高ゲイン範囲に対応しているので、ユーザーはさまざまな感度のサーモパイルを利用できます。また PGA は、低ゲイン・ドリフト (100ppm/  $^{\circ}$ C)、低出力オフセット・ドリフト ( $^{\circ}$ G = 1,005V/V で 1.2mV/ $^{\circ}$ C)、低位相遅延ドリフト (500ns)、低ノイズ ( $^{\circ}$ 0.1  $^{\circ}$ 4 V RMS 0.1 ~ 10Hz) という特徴も備えています。オフセット・キャンセル回路は、第2段の入力に等価の逆オフセットを加えて、出力信号から元のオフセットを削除することにより「暗信号」を補正します。この回路によって、ADC の使用がフルスケールで最適化され、ADC の分解能要件が緩和されます。

LMP91050 では、帯域外ノイズの除去を目的に、専用ピン A0 と A1 を利用して信号フィルタリング (ハイパス、ローパス、またはバンドパス)を追加できます。ユーザーは、オンボードの SPI インタフェースを介してプログラムが可能です。LMP91050 は小型の 10 ピン MSOP パッケージで供給され、-40  $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$  の範囲で動作します。

#### 主な仕様

■ プログラマブル・ゲイン 167V/V ~ 7,986V/V

■ 低ノイズ  $(0.1 \sim 10 \text{Hz})$   $0.1 \,\mu\,\text{V}_{\text{RMS}}$

**■** ゲイン・ドリフト 100ppm/ °C (max)

■ 位相遅延ドリフト 500ns (max)

■ 電源電圧範囲 2.7V ~ 5.5V

### 特長

- プログラマブル・ゲイン・アンプ

- ■「暗信号」オフセット・キャンセル回路

- 外部フィルタリングをサポート

- コモンモード・ジェネレータと8ビットDAC

- 10ピン MSOP パッケージ

### アプリケーション

- NDIR センシング

- デマンド制御換気

- ビルのモニタリング

- CO2 キャビン制御 オートモーティブ

- アルコール検出 -- オートモーティブ

- 産業用安全/セキュリティ機器

- GHG/フレオン検出プラットフォーム

#### ブロック図

Configurable AFE for NDIR

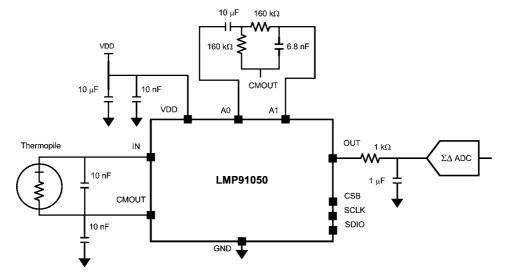

### 代表的なアプリケーション

**Typical NDIR Sensing Application Circuit**

### 製品情報

| Package        | Part Number | Package Marking | Transport Media          | NSC Drawing |

|----------------|-------------|-----------------|--------------------------|-------------|

| 10 Dia         | LMP91050MM  |                 | 1K units tape and reel   |             |

| 10-Pin<br>MSOP | LMP91050MME | <del> </del>    | 250 units tape and reel  | MUB10A      |

|                | LMP91050MMX |                 | 3.5K units tape and reel |             |

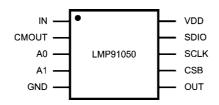

### ピン配置図

### ピン説明

| ピン番号 | 記号    | 種類      | 説明                     |

|------|-------|---------|------------------------|

| 1    | IN    | アナログ入力  | 信号入力                   |

| 2    | CMOUT | アナログ出力  | コモンモード電圧出力             |

| 3    | A0    | アナログ出力  | 第1段の出力                 |

| 4    | A1    | アナログ入力  | 第2段の入力                 |

| 5    | GND   | 電源      | グラウンド                  |

| 6    | OUT   | アナログ出力  | 信号出力。 CMOUT と同電位に対する基準 |

| 7    | CSB   | デジタル入力  | チップ・セレクト、アクティブ Low     |

| 8    | SCLK  | デジタル入力  | インタフェース・クロック           |

| 9    | SDIO  | デジタル入出力 | シリアル・データ入出力            |

| 10   | VDD   | 電源      | 正の電源                   |

### 絶対最大定格 (Note 1)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

ESD 耐圧 (Note 2)

2,500V 人体モデル

250V マシン・モデル 1,250V

帯電デバイス・モデル

電源電圧 (VDD)  $-0.3V \sim 6.0V$

各ピン電圧  $-0.3V \sim VDD + 0.3V$ 各ピンあたりの入力電流 5mA

保存温度範囲 - 65 °C  $\sim$  150 °C

接合部温度 (Note 3) 150 °C

ハンダ付け仕様については、

www.tij.co.jp の製品フォルダと

www.national.com/ms/MS/MS-SOLDERING.pdf を参照

してください。

### 動作定格 (Note 1)

電源電圧  $2.7V \sim 5.5V\,$

接合部温度範囲

$-40\,^{\circ}\text{C} \sim 105\,^{\circ}\text{C}$ (Note 3)

パッケージ熱抵抗 ( $\theta_{JA}$ )

10ピンMSOP 176 °C /W

### 電気的特性 (Note 4)

特記のない限り、以下の仕様は VDD = 3.3V、VCM = 1.15V に対して適用され、**太字**の値は  $T_A = -40$   $\mathbb{C} \sim +85$   $\mathbb{C}$ に対して 適用されます。その他のすべてのリミット値は  $T_A = T_J = +25$   $\mathbb{C}$ に対して適用されます。

| Symbol         | Parameter                                 | Conditions                                                                                   | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units     |

|----------------|-------------------------------------------|----------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|-----------|

| Power Sup      | ply                                       |                                                                                              |                 |                 |                 |           |

| VDD            | Supply Voltage                            |                                                                                              | 2.7             | 3.3             | 5.5             | ٧         |

| IDD            | Supply Current                            | All analog block ON                                                                          | 3.1             | 3.7             | 4.2             | mA        |

|                | Power Down Supply Current                 | All analog block OFF                                                                         | 45              | 85              | 121             | μА        |

| Offset Can     | cellation (Offset DAC)                    |                                                                                              |                 |                 |                 |           |

|                | Resolution                                |                                                                                              |                 | 256             |                 | steps     |

|                | LSB                                       | All gains                                                                                    |                 | 33.8            |                 | mV        |

|                | DNL                                       |                                                                                              | -1              |                 | 2               | LSB       |

|                | Error                                     | Output referred offset error, all gains                                                      |                 | ±100            |                 | mV        |

|                | Offset adjust Range                       | Output referred, all gains                                                                   | 0.2             |                 | VDD -<br>0.2    | ٧         |

|                | DAC settling time                         |                                                                                              |                 | 480             |                 | μs        |

| Programm       | able Gain Amplifier (PGA) 1st             | Stage, R <sub>i</sub> = 10kΩ, C <sub>i</sub> = 15pF                                          |                 |                 |                 | - 1,5,5,5 |

| IBIAS          | Bias Current                              |                                                                                              |                 | 5               | 200             | pA        |

| VINMAX<br>_HGM | Max input signal High gain<br>mode        | Referenced to CMOUT voltage, it refers to the maximum voltage at the IN pin before clipping; |                 | ±2              |                 | mV        |

| VINMAX<br>_LGM | Max input signal Low gain mode            | It includes dark voltage of the thermopile and signal voltage.                               |                 | ±12             |                 | mV        |

| vos            | Input Offset Voltage                      |                                                                                              |                 | -165            |                 | μV        |

| G_HGM          | Gain High gain mode                       |                                                                                              |                 | 250             |                 | V/V       |

| G_LGM          | Gain Low gain mode                        |                                                                                              |                 | 42              |                 | V/V       |

| GE             | Gain Error                                | Both HGM and LGM                                                                             |                 | 2.5             |                 | %         |

| VOUT           | Output Voltage Range                      |                                                                                              | 0.5             |                 | VDD -<br>0.5    | v         |

| PSRR           | Power Supply Rejection Ratio              | DC, 3.3V to 5V supply, Gain = 250V/V                                                         | 90              | 110             |                 | dB        |

| PhDly          | Phase Delay                               | 1mV input step signal, HGM, Vout measured at Vdd/2                                           |                 | 6               |                 | μs        |

| TCPhDly        | Phase Delay variation with<br>Temperature | 1mV input step signal, HGM, Vout measured at Vdd/2,                                          |                 | 416             |                 | ns        |

| SSBW           | Small Signal Bandwidth                    | Vin = 1mVpp, Gain = 250 V/V                                                                  |                 | 18              |                 | kHz       |

| Cin            | Input Capacitance                         |                                                                                              |                 | 100             |                 | pF        |

### **電気的特性** (Note 4) (つづき)

特記のない限り、以下の仕様は VDD = 3.3V、 VCM = 1.15V に対して適用され、**太字**の値は  $T_A=-40$   $^{\circ}$ C  $^{\circ}$ C に対して適用されます。その他のすべてのリミット値は  $T_A=T_J=+25$   $^{\circ}$ C に対して適用されます。

| Symbol                    | Parameter                                          | Conditions                                                                                                    | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units  |

|---------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------|-----------------|-----------------|--------|

| 2=                        | Input-Referred Noise Density                       | Combination of both current and voltage noise, with a 86kΩ source impedance at 5Hz                            |                 | 30              |                 | nV/√Hz |

| Input-Referred Integrated |                                                    | Combination of both current and voltage noise, with a $86k\Omega$ source impedance 0.1Hz to 10Hz              |                 | 0.1             | 0.12            | μVrms  |

| Programm                  | able Gain Amplifier (PGA) 2nd                      |                                                                                                               |                 | -               |                 |        |

| VINMAX                    | Max input signal                                   | GAIN = 4 V/V                                                                                                  |                 | 1.65            |                 | V      |

| VINMIN                    | Min input signal                                   |                                                                                                               |                 | 0.82            |                 | V      |

| G                         | Gain                                               | Programmable in 4 steps                                                                                       | 4               |                 | 32              | V/V    |

| GE                        | Gain Error                                         | Any gain                                                                                                      |                 | 2.5             |                 | %      |

| VOUT                      | Output Voltage Range                               |                                                                                                               | 0.2             |                 | VDD -<br>0.2    | ٧      |

| PSRR                      | Power Supply Rejection Ratio                       | DC, 3.3V to 5V supply, gain = 4V/V                                                                            | 90              | 110             |                 | dB     |

| PhDly                     | Phase Delay                                        | 100mV input sine 35kHz signal, Gain = 8,<br>VOUT measured at 1.65V, R <sub>L</sub> = 10kΩ                     |                 | 1               |                 | μs     |

| TCPhDly                   | Phase Delay variation with<br>Temperature          | 250mV input step signal, Gain = 8, Vout measured at Vdd/2                                                     |                 | 84              |                 | ns     |

| SSBW                      | Small Signal Bandwidth                             | Gain = 32 V/V                                                                                                 |                 | 360             |                 | kHz    |

| Cin                       | Input Capacitance                                  |                                                                                                               |                 | 5               |                 | pF     |

|                           | Input-Referred Noise Density                       | Combination of both current and voltage noise, with a 86kΩ source impedance at 5Hz                            |                 | 1.8             |                 | μV/√Hz |

| en                        | Input-Referred Integrated<br>Noise                 | Combination of both current and voltage noise, with a 86kΩ source impedance 0.1Hz to 10Hz                     |                 | 6               |                 | μVrms  |

| CLOAD,<br>OUT             | OUT Pin Load Capacitance                           | Series RC                                                                                                     |                 | 1               |                 | μF     |

| RLOAD,<br>OUT             | OUT Pin Load Resistance                            | Series RC                                                                                                     |                 | 1               |                 | kΩ     |

| Combined                  | Amplifier Chain Specification                      | 22 22                                                                                                         |                 |                 |                 |        |

| en                        | Input-Referred Noise Density                       | Combination of both current and voltage noise, with a $86k\Omega$ source impedance at 5Hz, Gain = $7986$      |                 | 30              |                 | nV/√Hz |

|                           | Input-Referred Integrated<br>Noise                 | Combination of both current and voltage noise, with a $86k\Omega$ source impedance 0.1Hz to 10Hz, Gain = 7986 |                 | 0.1             | 0.12            | μVrms  |

|                           |                                                    | PGA1 GAIN = 42, PGA2 GAIN = 4                                                                                 |                 | 167             |                 |        |

|                           |                                                    | PGA1 GAIN = 42, PGA2 GAIN = 8                                                                                 |                 | 335             |                 |        |

|                           |                                                    | PGA1 GAIN = 42, PGA2 GAIN = 16                                                                                |                 | 669             |                 |        |

|                           | Caia                                               | PGA1 GAIN = 42, PGA2 GAIN = 32                                                                                |                 | 1335            |                 | 1/0/   |

| G                         | Gain                                               | PGA1 GAIN = 250, PGA2 GAIN = 4                                                                                |                 | 1002            |                 | V/V    |

|                           |                                                    | PGA1 GAIN = 250, PGA2 GAIN = 8                                                                                |                 | 2004            |                 |        |

|                           |                                                    | PGA1 GAIN = 250, PGA2 GAIN = 16                                                                               |                 | 4003            |                 |        |

|                           |                                                    | PGA1 GAIN = 250, PGA2 GAIN = 32                                                                               |                 | 7986            |                 |        |

| GE                        | Gain Error                                         | Any gain                                                                                                      |                 | 5               |                 | %      |

| TCCGE                     | Gain Temp Coefficient (Note                        |                                                                                                               |                 |                 | 100             | ppm/°C |

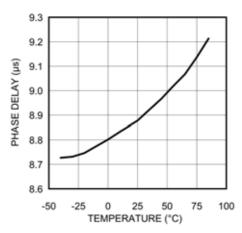

| PhDly                     | Phase Delay                                        | 1mV input step signal, Gain = 1002, Vout measured at Vdd/2                                                    |                 | 9               |                 | μs     |

| TCPhDly                   | Phase Delay variation with<br>Temperature (Note 8) | 1mV input step signal, Gain=1002, Vout measured at Vdd/2                                                      |                 |                 | 500             | ns     |

### **電気的特性** (Note 4) (つづき)

特記のない限り、以下の仕様は VDD = 3.3V、 VCM = 1.15V に対して適用され、**太字**の値は  $T_A = -40$   $\mathbb{C} \sim +85$   $\mathbb{C}$ に対して適用されます。その他のすべてのリミット値は  $T_A = T_J = +25$   $\mathbb{C}$ に対して適用されます。

| Symbol   | Parameter                  | Conditions                                  | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units |

|----------|----------------------------|---------------------------------------------|-----------------|-----------------|-----------------|-------|

|          |                            | Gain = 167 V/V                              | -0.525          |                 | 0.525           |       |

|          |                            | Gain = 335 V/V                              | -0.60           |                 | 0.60            |       |

|          |                            | Gain = 669 V/V                              | -0.90           |                 | 0.90            |       |

| TOUGE    | Output Offset Voltage      | Gain = 1335 V/V                             | -1.50           |                 | 1.50            | mV/°C |

| TCVOS    | Temperature Drift (Note 7) | Gain = 1002 V/V                             | -1.20           |                 | 1.20            |       |

|          |                            | Gain = 2004 V/V                             | -1.90           |                 | 1.90            |       |

|          |                            | Gain = 4003 V/V                             | -3.70           |                 | 3.70            |       |

|          |                            | Gain = 7986V/V                              | -7.10           |                 | 7.10            |       |

| Common M | Mode Generator             | Annual Contractor                           |                 |                 |                 |       |

| VCM      | Common Mode Voltage        | Programmable, see Common Mode<br>Generation |                 | 1.15 or<br>2.59 |                 | ٧     |

|          | VCM accuracy               |                                             | L.              | 2               |                 | %     |

| CLOAD    | CMOut Load Capacitance     | 17                                          |                 | 10              |                 | nF    |

#### SPI インタフェース (Note 4)

特記のない限り、以下の仕様は VDD = 3.3V、VCM = 1.15V、 $C_L=15pF$  に対して適用され、**太字**の値は  $T_A=-40$   $\mathbb{C}\sim+85$   $\mathbb{C}$  に対して適用されます。 その他のすべてのリミット値は  $T_A=T_J=+25$   $\mathbb{C}$ に対して適用されます。

| Symbol          | Parameter                     | Conditions | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units |

|-----------------|-------------------------------|------------|-----------------|-----------------|-----------------|-------|

| V <sub>IH</sub> | Logic Input High              |            | 0.7<br>× VDD    |                 |                 | ٧     |

| V <sub>IL</sub> | Logic Input Low               |            |                 |                 | 0.8             | ٧     |

| V <sub>OH</sub> | Logic Output High             |            | 2.6             |                 |                 | V     |

| V <sub>OL</sub> | Logic Output Low              |            |                 |                 | 0.4             | V     |

| IIH/IIL         | Input Digital Leakage Current |            | -100<br>-200    |                 | 100<br>200      | nA    |

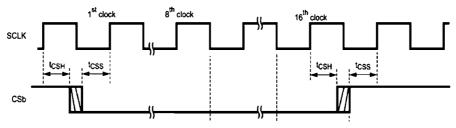

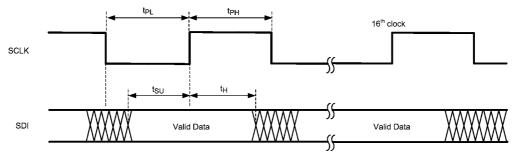

### タイミング特性 (Note 4)

特記のない限り、以下の仕様は VDD = 3.3V、VCM = 1.15V、 $C_L=15pF$  に対して適用され、**太字**の値は  $T_A=-40$   $\mathbb{C}\sim+85$   $\mathbb{C}$  に対して適用されます。 その他のすべてのリミット値は  $T_A=T_J=+25$   $\mathbb{C}$ に対して適用されます。

| Symbol            | Parameter                                         | Conditions | Min<br>(Note 6)       | Typ<br>(Note 5) | Max<br>(Note 6) | Units |

|-------------------|---------------------------------------------------|------------|-----------------------|-----------------|-----------------|-------|

| t <sub>wu</sub>   | Wake up time                                      |            |                       | 1               |                 | ms    |

| f <sub>SCLK</sub> | Serial Clock Frequency                            |            |                       |                 | 10              | MHz   |

| t <sub>PH</sub>   | SCLK Pulse Width High                             |            | 0.4/f <sub>SCLK</sub> |                 |                 | ns    |

| tpL               | SCLK Pulse Width Low                              |            | 0.4/f <sub>SCLK</sub> |                 |                 | ns    |

| t <sub>CSS</sub>  | CSB Setup Time                                    |            | 10                    |                 |                 | ns    |

| t <sub>csH</sub>  | CSB Hold Time                                     |            | 10                    |                 |                 | ns    |

| t <sub>su</sub>   | SDI Setup Time prior to rise edge of SCLK         |            | 10                    |                 |                 | ns    |

| t <sub>sH</sub>   | SDI Hold Time prior to rise edge of SCLK          |            | 10                    |                 |                 | ns    |

| t <sub>DOD1</sub> | SDO Disable Time after rise edge of CSB           |            |                       |                 | 45              | ns    |

| t <sub>DOD2</sub> | SDO Disable Time after 16th<br>rise edge of SCLK  |            |                       |                 | 45              | ns    |

| t <sub>DOE</sub>  | SDO Enable Time from the fall<br>edge of 8th SCLK |            |                       |                 | 35              | ns    |

| t <sub>DOA</sub>  | SDO Access Time after the fall edge of SCLK       |            |                       |                 | 35              | ns    |

| t <sub>DOH</sub>  | SDO hold time after the fall edge of SCLK         |            | 5                     |                 |                 | ns    |

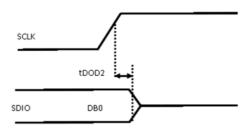

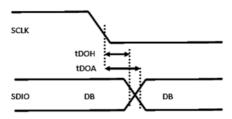

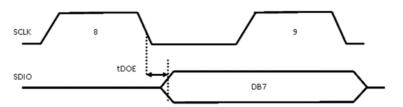

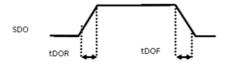

#### タイミング特性 (Note 4)

特記のない限り、以下の仕様は VDD = 3.3V、VCM = 1.15V、 $C_L = 15pF$  に対して適用され、**太字**の値は  $T_A = -40$   $\mathbb{C} \sim +85$   $\mathbb{C}$  に対して適用されます。 その他のすべてのリミット値は  $T_A = T_J = +25$   $\mathbb{C}$  に対して適用されます。

| Symbol           | Parameter     | Conditions | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units |

|------------------|---------------|------------|-----------------|-----------------|-----------------|-------|

| t <sub>DOR</sub> | SDO Rise time |            |                 | 5               |                 | ns    |

| t <sub>DOF</sub> | SDO Fall time |            |                 | 5               |                 | ns    |

- Note 1: 「絶対最大定格」とは、IC に破壊が発生したり、使用不能になったり、信頼性や性能が低下する可能性のあるリミット値を示します。これは、絶対 最大定格において、または推奨動作定格に示されている動作条件を超える条件でこのデバイスが有効に機能することや品質が劣化しないことは意味 していません。「動作定格」とは、デバイスが正常に機能する条件を示しており、この範囲を超えて動作させることは避けてください。

- **Note 2:** 人体モデル適用規格: MIL-STD-883、 Method 3015.7。マシン・モデル適用規格: JESD22-A115-A (JEDEC の ESD MM 規格 )。 電場 ( 界 ) 誘導 帯電モデル適用規格: JESD22-C101-C (JEDEC の ESD FICDM 規格 )。

- Note 3: 最大消費電力は、 $T_{J(MAX)}$ 、 $\theta_{JA}$ 、周囲温度 TA の関数です。任意の周囲温度における最大許容消費電力は、 $P_{DMAX} = (T_{J(MAX)} T_A)/\theta_{JA}$ で表されます。 すべての数値は、プリント基板に直接ハンダ付けするパッケージに適用されます。

- Note 4: 「電気的特性」の値は、記載温度における工場出荷試験条件にのみ適用されます。工場試験条件で生じる自己発熱は、 $T_J = T_A$ となる程度にきわめてわずかです。「電気的特性」には、自己発熱により  $T_J > T_A$ となる条件下で保証されるパラメータ性能値は記載されていません。「絶対最大定格」に記載されている接合部温度上限を超えるとデバイスに物理的または電気的な恒久的損傷を与えるおそれがあります。

- Note 5: 代表値 (typ) は、特性解析時に確定された最も標準的なパラメータ値を示します。実測値は、経時的に変化するとともに、アプリケーションや構成にも依存します。この代表値はテストされた値ではなく、出荷済みの製品材料に対する保証値ではありません。

- Note 6: リミット値は 25 ℃において製品の全数検査を行っています。動作温度範囲でのリミット値は標準統計品質管理 (SQC) 手法を用いた相関によって保証されています。

- Note 7: TCCGE と TCVOS は、-40  $^{\circ}$   $^{\circ$

- Note 8: TCPhDly は、-40  $^{\circ}$ C  $^{\circ}$ 25  $^{\circ}$ Cの測定と25  $^{\circ}$ C  $^{\circ}$ 85  $^{\circ}$ Cの測定における位相遅延の最大の変化です。

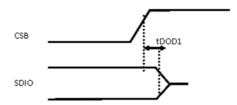

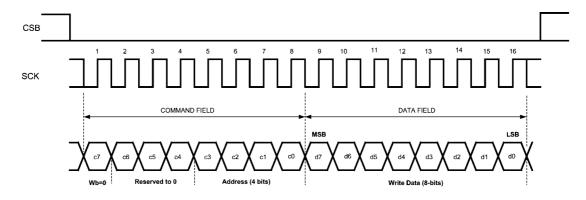

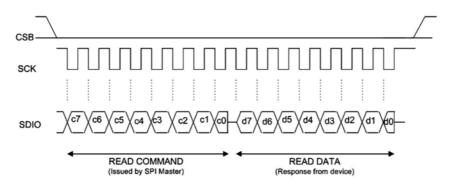

### タイミング図

FIGURE 1. SPI Timing Diagram

FIGURE 2. SPI Set-up Hold Time

6

### **タイミング図**(つづき)

FIGURE 3. SDO disable time after 16<sup>th</sup> rise edge of SCLK

FIGURE 4. SDO access time ( $t_{DOA}$ ) and SDO hold time ( $t_{DOH}$ ) after the fall edge of SCLK

FIGURE 5. SDO Enable time from the fall edge of 8<sup>th</sup> SCLK

FIGURE 6. SDO disable time after rise edge of CSB

FIGURE 7. SDO rise and fall times

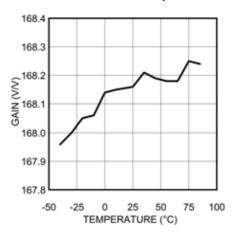

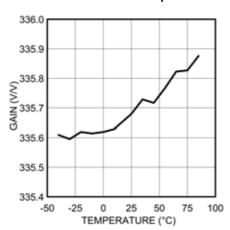

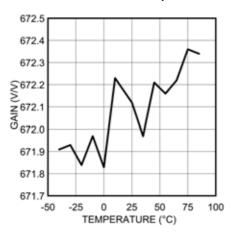

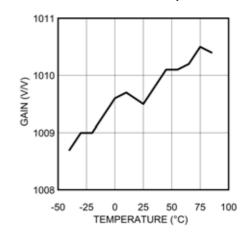

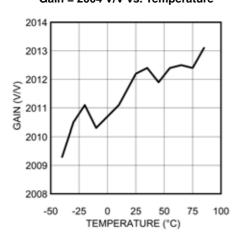

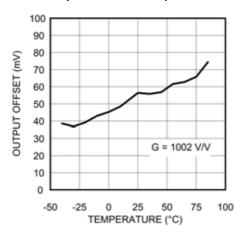

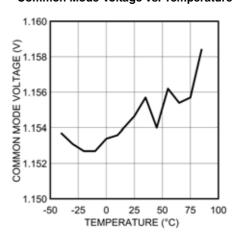

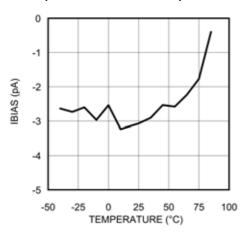

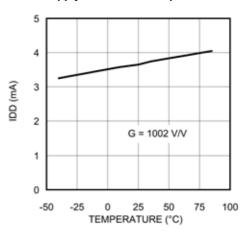

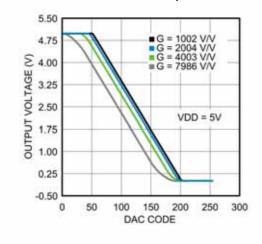

### 代表的な性能特性

特記のない限り、 VDD=+ 3.3 V、 VCM=1.15 V、  $T_A=25$   $^{\circ}$  C で適用。

Gain = 167 V/V vs. Temperature

Gain = 335 V/V vs. Temperature

Gain = 669 V/V vs. Temperature

Gain = 1002 V/V vs. Temperature

Gain = 2004 V/V vs. Temperature

Phase Delay vs. Temperature

### 代表的な性能特性(つづき)

特記のない限り、VDD = + 3.3V、VCM = 1.15V、 $T_A = 25$  °Cで適用。

#### **Output Offset vs. Temperature**

#### Common Mode Voltage vs. Temperature

Input Bias Current vs. Temperature

**Supply Current vs. Temperature**

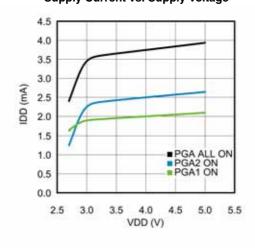

Supply Current vs. Supply Voltage

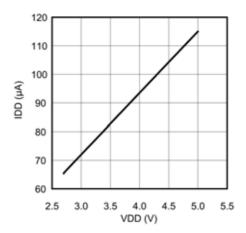

Power Down Supply Current vs. Supply Voltage

### 代表的な性能特性(つづき)

特記のない限り、VDD = + 3.3V、VCM = 1.15V、 $T_A = 25$  °Cで適用。

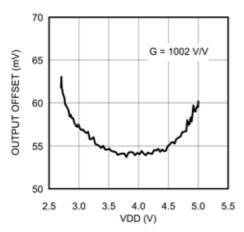

**Output Offset vs. Supply Voltage**

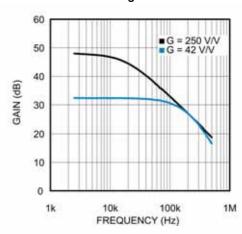

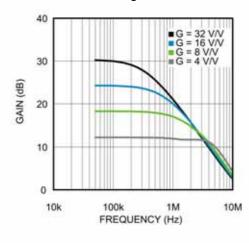

**PGA1 Small Signal Bandwidth**

**PGA2 Small Signal Bandwidth**

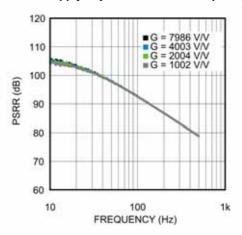

Power Supply Rejection Ratio vs. Frequency

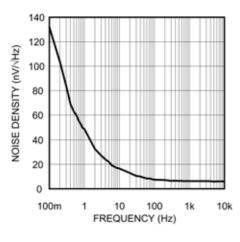

Input-Referred Noise Density vs. Frequency

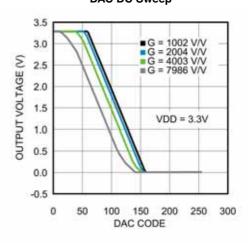

DAC DC Sweep

### 代表的な性能特性(つづき)

特記のない限り、 VDD=+ 3.3 V、 VCM=1.15 V、  $T_A=25$   $^{\circ}$  C で適用。

### **DAC DC Sweep**

#### 機能説明

#### プログラマブル・ゲイン・アンプ

LMP91050 は 2 つのプログラマブル・ゲイン・モード(低/高)を備え、それぞれに 4 つのプログラマブル・ゲイン設定があります。ゲイン・モードの目的は、幅広い暗電圧レベルのサーモパイルへの対応を可能にすることです。すべてのゲイン設定には、GAIN1 ビットと GAIN2 ビット [1:0] からアクセスできます。

低ゲイン・モードの範囲は  $167V/V \sim 1,335V/V$ 、高ゲイン・モードの範囲は  $1,002V/V \sim 7,986V/V$  です。PGA は内部で生成された VCM を基準にします。高ゲイン・モードの場合、入力信号はこの VCM 電圧を基準に $\pm 2mV$  以内に収める必要があります (VINMAX\_HGM の仕様を参照)。低ゲイン・モードの場合、第 1 段のゲインは 250V/V ではなく 42V/V なので、最大入力信号は $\pm 12mV$  まで対応できます (VINMAX\_LGM)。

**TABLE 1. Gain Modes**

| ビット記号       | ゲイン                                        |

|-------------|--------------------------------------------|

| GAIN1       | <b>0: 250 (default)</b><br>1: 42           |

| GAIN2 [1:0] | <b>00: 4 (default)</b> 01: 8 10: 16 11: 32 |

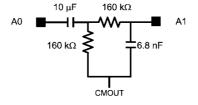

#### 外部フィルタ

LMP91050 では、EXT\_FILT ビットを利用して 2 種類の測定 モードを選択できます。EXT\_FILT ビットはデバイス構成レジス タ内に存在し、SPI を介してプログラムが可能です。

**TABLE 2. Measurement Modes**

| ビット記号    | 測定モード                                                                                             |

|----------|---------------------------------------------------------------------------------------------------|

| EXT_FILT | 0: サーモパイルからの信号は、追加の外部デカップリングやフィルタリングを利用せずに内部 PGA によって処理されます (デフォルト)。                              |

|          | 1: サーモパイルからの信号は、まず内部 PGA によって処理されてから、A0 ピンに送られます。A0 ピンと A1 ピンには外部フィルタ(ローパス、ハイパス、またはバンドパス)を接続できます。 |

外部フィルタは、EXT\_FILT = 1 の場合に適用できます。以下の図に代表的なバンドパス・フィルタを示します。図に示したように、LMP91050 の CMOUT ピンには抵抗とコンデンサを接続

できます。参考のためディスクリート部品の値を記載してあります。

FIGURE 8. Typical Bandpass Filter

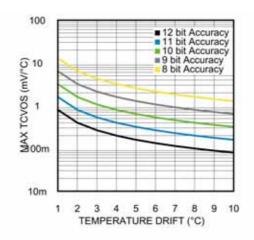

#### オフセット調整

オフセット調整の手順としては、まず「暗信号」を測定してから、DACをプログラムして調整を行います。次に、第2のサイクルで暗信号の残余を測定し、 $\mu$ C内で追加の信号操作を行います。信号源では、オフセット成分(暗信号)が実際の信号よりも大きくなることが予想されます。センサによって光が検出されない「暗フェーズ」の際に、 $\mu$ CはLMP91050の内部DACをプログラムして、測定されたオフセットを補正できます。

出力オフセット電圧温度ドリフト (TCVOS) が低いと、全温度範囲で高いシステム精度を得られます。次の Figure 9 に、特定の温度ドリフトにおいて n ビットのシステム精度を得る上での最大許容 TCVOS を示します。

FIGURE 9. System Accuracy vs. TCVOS and Temperature Drift

#### コモンモード生成

センサのオフセットはバイポーラなので、センサには VCM を供給する必要があります。これは 1.15V または 2.59V (3.3V または5V電源の約半分)としてプログラムできます。3.3V電源で2.59V VCM を使用することは推奨しません。

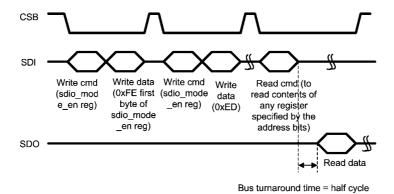

#### SPI インタフェース

2 段の PGA ゲイン、外部フィルタのイネーブル、PGA の電力のイネーブル、オフセット調整、コモンモード (VCM) 電圧など、デバイス・パラメータのプログラムには SPI インタフェースを利用できます。

#### インタフェース・ピン

シリアル・インタフェースは、SDIO (シリアル・データ入出力)、 SCLK (シリアル・インタフェース・クロック)、CSB (チップ・セレクト・バー)で構成されています。このインタフェースは、デフォルトでは書き込み専用です。SDIO\_MODE\_PASSWD のロックを解除すると、読み出し動作にも対応します。詳細は後述します。

#### **CSB**

チップ・セレクトはアクティブ Low 信号です。トランザクション中は、CSB をアサートしておく必要があります。すなわち、CSB

は単一トランザクションの命令バイトとデータ・バイトの間で変動すべきではありません。

CSBをネゲートすると常に、まだ完了していない実行中のトランザクションが終了します。同様に、CSBをアサートすると常に、前のトランザクションの終了状態にかかわらず、デバイスが次のトランザクションに備えた状態に移行します。

2 線式 SPI 通信プロトコルの場合、 CSB を恒久的に Low へ固 定できます。

#### **SCLK**

書き込みトランザクションの場合、SCLK は High または Low に 維持します。ただし読み出しトランザクションの場合は、High に 維持する必要があります。SCLK の入力はシュミット・トリガ式で す。これにはヒステリシスが存在しますが、不注意によりグリッチで SPI フレームを損なわないように、SCLK をできる限りクリーンな状態に保つことを推奨します。

#### 通信プロトコル

SPIでの通信は通常、書き込みトランザクションと読み出しトランザクションを伴います。書き込みトランザクションは、単一の書き込みコマンド・バイトと、それに続く単一のデータ・バイトで構成されます。次の図に、書き込みトランザクションの SPI インタフェース・プロトコルを示します。

FIGURE 10. SPI Interface Protocol

読み出しトランザクションの場合、ユーザーはまず SDIO モード・イネーブル・レジスタへの書き込みを行って、SPI 読み出しモードをイネーブルにする必要があります。デバイスの読み出しがイネーブルになると、読み出しトランザクションのデータ・フィールドの間、SDIO ピン上でデータの送信が行われます。

SDIO ピンは、この目的のために双方向ピンとして設計されています。 Figure 6 に、読み出しトランザクションを示します。 SPI 読み出しモードをイネーブルにする上で SPI マスタが発行する必要があるコマンド・シーケンスについては、 Figure 12 に示します

#### READ TRANSACTION

Note: Read command is issued by the SPI Master, who after issuing the c0 (LSBit of the command byte) bit should relinquish the data line (high-Z) after meeting the hold timing(10ns) and stop SCK idling high.

FIGURE 11. Read Transaction

Sequence of transactions for unlocking SDIO\_MODE

#### Note

- 1. Once the SDIO\_mode is unlocked. The user can read as many registers as long as nothing else is written to sdio\_mode\_en register to disturb the state of SDIO\_mode

- 2. The separate signals SDI and SDO are given in the figure for the sake of understanding. However, only one signal SDIO exists in the design

FIGURE 12. Enable SDIO Mode for reading SPI registers

#### レジスタ編成

デバイスの構成は、デバイス内の指定レジスタの「書き込み」 を使って実行します。レジスタはすべて、固有のアドレスを持ち

個別にアドレス指定可能なバイト長レジスタとして編成されてい ます。次の図に、書き込み/読み出し命令の形式を示します。

TABLE 3. Write / Read Instruction Format

| Bit[7]                | Bit[6:4]      | Bit[3:0] |

|-----------------------|---------------|----------|

| 0 : Write Instruction | Decemand to 0 | Addraga  |

| 1 : Read Instruction  | Reserved to 0 | Address  |

Note: ビット [6:4] にゼロ以外の値を指定することは禁止されています。

#### レジスタ

ここでは、デバイスのプログラマブル・レジスタと、関連するプ 次の表に、ユーザーが利用可能なすべてのレジスタと、その ログラミング・シーケンス(該当する場合)について説明します。 パワーアップ値の一覧を示します。

| Title                | Address (Hex) | Туре                                      | Power-up/Reset<br>Value (Hex) |

|----------------------|---------------|-------------------------------------------|-------------------------------|

| Device Configuration | 0x0           | Read-Write<br>(Read allowed in SDIO Mode) | 0x0                           |

| DAC Configuration    | 0x1           | Read-Write<br>(Read allowed in SDIO Mode) | 0x80                          |

| SDIO Mode Enable     | 0xF           | Write-only                                | 0x0                           |

Note: 予期せぬ結果を防ぐために、推奨値は指定された位置にプログラムする必要があります。本書に記載されていないアドレスへの書き込みは避けてください。そのようなアドレスへの書き込みは、予期せぬ結果を招くことがあります。

### デバイス構成 - デバイス構成レジスタ(アドレス 0x0)

| Bit   | Bit Symbol | Description                         |

|-------|------------|-------------------------------------|

| 7     | RESERVED   | Reserved to 0.                      |

| [6:5] | EN         | 00: PGA1 OFF PGA2 OFF (default)     |

|       |            | 01: PGA1 OFF, PGA2 ON               |

|       |            | 10: PGA1 ON, PGA2 OFF               |

|       |            | 11: PGA1 ON, PGA2 ON                |

| 4     | EXT_FILT   | 0: PGA1 to PGA2 direct (default)    |

|       |            | 1: PGA1 to PGA2 via external filter |

| 3     | CMN_MODE   | 0 : 1.15V (default)                 |

|       |            | 1 : 2.59V                           |

| [2:1] | GAIN2      | 00: 4 (default)                     |

|       |            | 01: 8                               |

|       |            | 10: 16                              |

|       |            | 11: 32                              |

| 0     | GAIN1      | 0: 250 (default)                    |

|       |            | 1: 42                               |

### DAC 構成 - DAC 構成レジスタ (アドレス 0x1)

出力 DC レベルは、式 Vout\_shift = -33.8mV \* (NDAC -128) に従って変化します。

| Bit   | Bit Symbol | Description                                                    |

|-------|------------|----------------------------------------------------------------|

| [7:0] | NDAC       | 128 (0x80): Vout_shift = -33.8mV * (128 - 128) = 0mV (default) |

### SDIO モード – SDIO モード・イネーブル・レジスタ (アドレス 0xf)

書き込みのみ

| Bit   | Bit Symbol   | Description                                    |

|-------|--------------|------------------------------------------------|

| [7:0] | SDIO MODE EN | SDIO モードに移行するには、逐次シーケンス 0xFE および 0xED を書き込みます。 |

|       |              | SDIO モードを終了するには、このシーケンス以外の任意の文字を書き込みます。        |

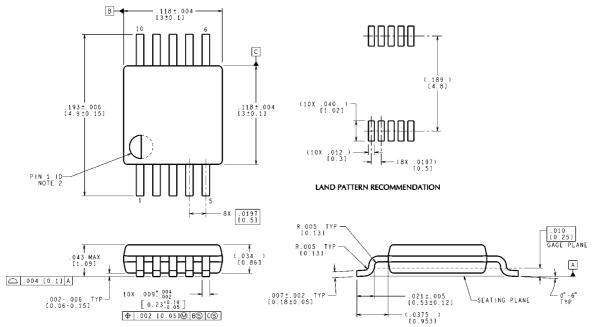

MUB10A (Rev B)

## 外形寸法図 特記のない限り inches (millimeters)

10-Lead MSOP Order Numbers LMP91050MM/X **NS Package Number MUB10A**

CONTROLLING DIMENSION IS INCH VALUES IN [] ARE MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY

すべて商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。 資料によっては正規英語版資料の更新に対応していないものがあります。日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を

製品のC・検討わるびご休用にあたりましては必り正規英語版の取制資料を ご確認下さい。 Tiおよび日本Tiは、正規英語版にて更新の情報を提供しているにもかかわ らず、更新以前の情報に基づいて発生した問題や障害等につきましては如 何なる責任も負いません。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated (TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TT製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2012, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

### 2. 温·湿度環境

● 温度: 0~40°C、相対湿度: 40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

#### 4. 機械的衝擊

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

### 5. 熱衝撃

● はんだ付け時は、最低限260°C以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上