**TMUX9616**

JAJSKN6 - SEPTEMBER 2023

# TMUX9616 ラッチアップ耐性付き、220V 高電圧 1:1、16 チャネル・スイッチ

# 1 特長

- 広い電源電圧範囲または入力信号範囲:

- 両電源: ±20V~±110V、220V<sub>PP</sub>

- 240V<sub>PP</sub> の絶対最大値

- 低いオフ容量:5pF

- 低いオン容量:10pF

- 低いオン抵抗 (R<sub>ONI</sub>):12Ω

- 高速ターンオン時間:3µs (最大値)

- 最大 72MHz のデータ・シフト・クロック周波数

- ロジック・レベル:1.8V~5V

- 非常に優れたオフ絶縁性能:-70dB (5MHz 時)

- 出力にブリード抵抗を内蔵

- デバイス構造に基づくラッチアップ耐性

- 拡張温度

範囲:-40℃~125℃

業界標準の 7mm × 7mm (本体サイズ) LQFP パッケ ージによるピン互換の実現

# 2 アプリケーション

- 医療用超音波画像処理

- 非破壊試験 (NDT) による金属の欠陥検出

- 圧電性のトランスデューサ・ドライバ

- 超音波流量トランスミッタ

- プリンタ

- 光 MEMS モジュール

# 3 概要

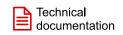

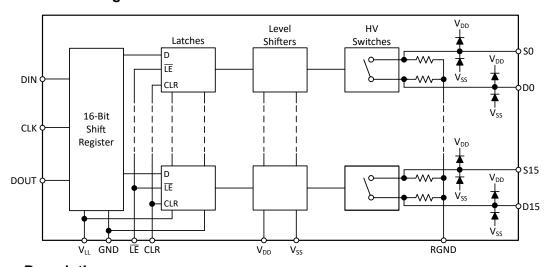

TMUX9616 は、ラッチアップ耐性を備えた、16 チャネ ル、低抵抗、低静電容量、高電圧のアナログ・スイッチ集 積回路 (IC) です。各デバイスは、独立して選択可能な 16 個の 1:1 単極単投 (SPST) スイッチ・チャネルを備えてい ます。このデバイスは、最大±110Vの両電源で良好に動 作します。推奨電源範囲内では、非対称の電源バイアスも サポートされています。 TMUX9616 は、ソース (Sx) およ びドレイン (Dx) ピンで、Vss から VDD までの範囲の双方 向アナログおよびデジタル信号をサポートします。 TMUX9616 また、ソース (Sx) ピンとドレイン (Dx) ピンに ブリード抵抗を内蔵しており、圧電トランスデューサなどの 容量性負荷を放電します。TMUX9616 医療用超音波イ メージングやその他の圧雷トランスデューサ・ドライバ・アプ リケーション向けの優れた選択肢になります。

TMUX9616 カスケード接続可能な 16 ビット・シフト・レジ スタを内蔵し、16個の各スイッチを制御するためのラッチ を搭載しています。デイジーチェーン機能により、デバイス ごとに個別のチップ・セレクトを必要とせずに、多くの TMUX9616 デバイスを制御できます。潜在的なクロック・ フィードスルーによる信号パスのノイズを低減するために、 データがシフト・レジスタにロードされている間、アクティ ブ・ローのラッチ・イネーブルを High に保持することがで きます。16 ビット・シフト・レジスタは、1.8V~5V の電源で 動作できます。 16 ビット・シフト・レジスタは、最高 72MHz のクロック速度をサポートできます。

#### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ・サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| TMUX9616 | PT (LQFP, 48)        | 9mm × 9mm                |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

- パッケージ・サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

English Data Sheet: SCDS436

資料に関するフィードバック (ご意見やお問い合わせ) を送信

# **Table of Contents**

| 1 特長                                     | 1  | 7.7 Isolation Diode Current             | 16              |

|------------------------------------------|----|-----------------------------------------|-----------------|

| 2 アプリケーション                               |    | 8 Detailed Description                  | 18              |

| 3 概要                                     |    | 8.1 Overview                            | 18              |

| 4 Revision History                       |    | 8.2 Functional Block Diagram            | 18              |

| 5 Pin Configuration and Functions        |    | 8.3 Feature Description                 | 18              |

| 6 Specifications                         |    | 8.4 Device Functional Modes             | <mark>20</mark> |

| 6.1 Absolute Maximum Ratings             |    | 8.5 Device Logic Table                  | <mark>20</mark> |

| 6.2 ESD Ratings                          |    | 9 Application and Implementation        | 21              |

| 6.3 Thermal Information                  |    | 9.1 Application Information             | 21              |

| 6.4 Recommended Operating Conditions     |    | 9.2 Typical Application                 | 21              |

| 6.5 Electrical Characteristics: TMUX9616 |    | 9.3 Power Supply Recommendations        | <mark>25</mark> |

| 6.6 Switching Characteristics: TMUX9616  |    | 9.4 Layout                              | 25              |

| 6.7 Digital Timings: TMUX9616            |    | 10 Device and Documentation Support     | <mark>26</mark> |

| 6.8 Timing Diagrams                      |    | 10.1 Documentation Support              | 26              |

| 6.9 Typical Characteristics              |    | 10.2ドキュメントの更新通知を受け取る方法                  | 26              |

| 7 Parameter Measurement Information      |    | 10.3 サポート・リソース                          | 26              |

| 7.1 Off-Leakage Current                  | 14 | 10.4 Trademarks                         | 26              |

| 7.2 Device Turn On/Off Time              |    | 10.5 静電気放電に関する注意事項                      | 26              |

| 7.3 Off Isolation                        | 15 | 10.6 用語集                                | 26              |

| 7.4 Inter-Channel Crosstalk              |    | 11 Mechanical, Packaging, and Orderable |                 |

| 7.5 Output Voltage Spike                 |    | Information                             | 26              |

| 7.6 Switch DC Offset Voltage             |    |                                         |                 |

|                                          |    |                                         |                 |

# **4 Revision History**

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2023 | *        | Initial Release |

# TEXAS INSTRUMENTS www.ti.com/ja-jp

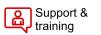

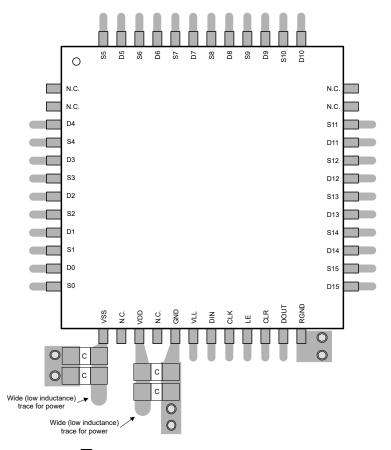

# **5 Pin Configuration and Functions**

図 5-1. PT Package, 48-Pin LQFP (Top View)

表 5-1. Pin Functions

|                 | PIN | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                 |

|-----------------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO. | - ITPE(")           | DESCRIPTION                                                                                                                                                                                                 |

| N.C.            | 1   | _                   | No internal connection. Leave floating or connect to GND.                                                                                                                                                   |

| N.C.            | 2   | _                   | No internal connection. Leave floating or connect to GND.                                                                                                                                                   |

| D4              | 3   | I/O                 | Drain pin 4. Can be an input or an output.                                                                                                                                                                  |

| S4              | 4   | I/O                 | Source pin 4. Can be an input or an output.                                                                                                                                                                 |

| D3              | 5   | I/O                 | Drain pin 3. Can be an input or an output.                                                                                                                                                                  |

| S3              | 6   | I/O                 | Source pin 3. Can be an input or an output.                                                                                                                                                                 |

| D2              | 7   | I/O                 | Drain pin 2. Can be an input or an output.                                                                                                                                                                  |

| S2              | 8   | I/O                 | Source pin 2. Can be an input or an output.                                                                                                                                                                 |

| D1              | 9   | I/O                 | Drain pin 1. Can be an input or an output.                                                                                                                                                                  |

| S1              | 10  | I/O                 | Source pin 1. Can be an input or an output.                                                                                                                                                                 |

| D0              | 11  | I/O                 | Drain pin 0. Can be an input or an output.                                                                                                                                                                  |

| S0              | 12  | I/O                 | Source pin 0. Can be an input or an output.                                                                                                                                                                 |

| V <sub>SS</sub> | 13  | Р                   | Negative power supply. This pin is the most negative power-supply potential. For reliable operation, connect a decoupling capacitor ranging from 0.1 $\mu$ F to 10 $\mu$ F between V <sub>SS</sub> and GND. |

| N.C.            | 14  | _                   | No internal connection. Leave floating or connect to GND.                                                                                                                                                   |

Copyright © 2023 Texas Instruments Incorporated

# 表 5-1. Pin Functions (続き)

|                 | PIN(1) |                     |                                                                                                                                                                                                      |  |  |  |

|-----------------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME            | NO.    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                          |  |  |  |

| $V_{DD}$        | 15     | Р                   | Positive power supply. This pin is the most positive power-supply potential. For reliable operation, connect a decoupling capacitor ranging from 0.1 $\mu$ F to 10 $\mu$ F between $V_{DD}$ and GND. |  |  |  |

| N.C.            | 16     | _                   | No internal connection. Leave floating or connect to GND.                                                                                                                                            |  |  |  |

| GND             | 17     | Р                   | Ground (0 V) reference.                                                                                                                                                                              |  |  |  |

| V <sub>LL</sub> | 18     | Р                   | 1.8 V – 5 V SPI power supply. For reliable operation, connect a decoupling capacitor ranging from 0.1 $\mu$ F to 1 $\mu$ F between $V_{LL}$ and GND.                                                 |  |  |  |

| DIN             | 19     | 1                   | SPI (Daisy Chain) Data Input.                                                                                                                                                                        |  |  |  |

| CLK             | 20     | - 1                 | SPI (Daisy Chain) Clock Input.                                                                                                                                                                       |  |  |  |

| LE              | 21     | ı                   | Latch enable input, active low.                                                                                                                                                                      |  |  |  |

| CLR             | 22     | ı                   | Latch clear input, active high.                                                                                                                                                                      |  |  |  |

| DOUT            | 23     | 0                   | SPI (Daisy Chain) Data Output.                                                                                                                                                                       |  |  |  |

| RGND            | 24     | Р                   | Bleed Resistor GND. Connect to ground (0 V) reference.                                                                                                                                               |  |  |  |

| D15             | 25     | I/O                 | Drain pin 15. Can be an input or an output.                                                                                                                                                          |  |  |  |

| S15             | 26     | I/O                 | Source pin 15. Can be an input or an output.                                                                                                                                                         |  |  |  |

| D14             | 27     | I/O                 | Drain pin 14. Can be an input or an output.                                                                                                                                                          |  |  |  |

| S14             | 28     | I/O                 | Source pin 14. Can be an input or an output.                                                                                                                                                         |  |  |  |

| D13             | 29     | I/O                 | Drain pin 13. Can be an input or an output.                                                                                                                                                          |  |  |  |

| S13             | 30     | I/O                 | Source pin 13. Can be an input or an output.                                                                                                                                                         |  |  |  |

| D12             | 31     | I/O                 | Drain pin 12. Can be an input or an output.                                                                                                                                                          |  |  |  |

| S12             | 32     | I/O                 | Source pin 12. Can be an input or an output.                                                                                                                                                         |  |  |  |

| D11             | 33     | I/O                 | Drain pin 11. Can be an input or an output.                                                                                                                                                          |  |  |  |

| S11             | 34     | I/O                 | Source pin 11. Can be an input or an output.                                                                                                                                                         |  |  |  |

| N.C.            | 35     | _                   | No internal connection. Leave floating or connect to GND.                                                                                                                                            |  |  |  |

| N.C.            | 36     | _                   | No internal connection. Leave floating or connect to GND.                                                                                                                                            |  |  |  |

| D10             | 37     | I/O                 | Drain pin 10. Can be an input or an output.                                                                                                                                                          |  |  |  |

| S10             | 38     | I/O                 | Source pin 10. Can be an input or an output.                                                                                                                                                         |  |  |  |

| D9              | 39     | I/O                 | Drain pin 9. Can be an input or an output.                                                                                                                                                           |  |  |  |

| S9              | 40     | I/O                 | Source pin 9. Can be an input or an output.                                                                                                                                                          |  |  |  |

| D8              | 41     | I/O                 | Drain pin 8. Can be an input or an output.                                                                                                                                                           |  |  |  |

| S8              | 42     | I/O                 | Source pin 8. Can be an input or an output.                                                                                                                                                          |  |  |  |

| D7              | 43     | I/O                 | Drain pin 7. Can be an input or an output.                                                                                                                                                           |  |  |  |

| S7              | 44     | I/O                 | Source pin 7. Can be an input or an output.                                                                                                                                                          |  |  |  |

| D6              | 45     | I/O                 | Drain pin 6. Can be an input or an output.                                                                                                                                                           |  |  |  |

| S6              | 46     | I/O                 | Source pin 6. Can be an input or an output.                                                                                                                                                          |  |  |  |

| D5              | 47     | I/O                 | Drain pin 5. Can be an input or an output.                                                                                                                                                           |  |  |  |

| S5              | 48     | I/O                 | Source pin 5. Can be an input or an output.                                                                                                                                                          |  |  |  |

(1) I = input, O = output, P = power

English Data Sheet: SCDS436

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1) (2) (3)

|                                  |                                                     | MIN             | MAX      | UNIT |

|----------------------------------|-----------------------------------------------------|-----------------|----------|------|

| V <sub>DD</sub> -V <sub>SS</sub> |                                                     |                 | 240      | V    |

| V <sub>DD</sub>                  | Supply voltage                                      | -0.5            | 120      | V    |

| V <sub>SS</sub>                  |                                                     | -120            | 0.5      | V    |

| V <sub>LL</sub>                  | SPI/Logic supply voltage                            | -0.5            | 6        | V    |

| V <sub>L</sub>                   | Logic control pin voltage (DIN, DOUT, CLK, LE, CLR) | -0.5            | $V_{LL}$ | V    |

| IL                               | Logic control pin current (DIN, DOUT, CLK, LE, CLR) | -30             | 30       | mA   |

| V <sub>S</sub> or V <sub>D</sub> | Source or drain voltage (Sx, D)                     | V <sub>SS</sub> | $V_{DD}$ | V    |

| I <sub>PK</sub>                  | Analog Signal Peak Current/Channel                  |                 | 3        | Α    |

| T <sub>A</sub>                   | Ambient temperature                                 | -40             | 125      | °C   |

| T <sub>stg</sub>                 | Storage temperature                                 | -65             | 150      | °C   |

| T <sub>J</sub>                   | Junction temperature                                | -40             | 150      | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Rating may cause permanent device damage. Absolute Maximum Rating do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Condition. If used outside the Recommended Operating Condition but within the Absolute Maximum Rating, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) The algebraic convention, whereby the most negative value is a minimum and the most positive value is a maximum.

- (3) All voltages are with respect to ground, unless otherwise specified.

# 6.2 ESD Ratings

|                    |                         |                                                                                     | VALUE                  | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|------------------------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | , per ANSI/ESDA/ ±1000 |      |

|                    |                         | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±500                   | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Thermal Information

|                        |                                              | TMUX9616  |      |

|------------------------|----------------------------------------------|-----------|------|

|                        | THERMAL METRIC(1)                            | PT (LQFP) | UNIT |

|                        |                                              | 48 PINS   |      |

| R <sub>θJA</sub>       | Junction-to-ambient thermal resistance       | 60.8      | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 15.4      | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 26.9      | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.5       | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 26.6      | °C/W |

| R <sub>0JC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | N/A       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.4 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                  |                                                                                          | MIN                   | NOM  | MAX                   | UNIT |

|----------------------------------|------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| $V_{DD} - V_{SS}$                | Power supply voltage differential                                                        | 40                    | 200  | 220                   | V    |

| V <sub>DD</sub>                  | Positive power supply voltage                                                            | 20                    | 100  | 110                   | V    |

| V <sub>SS</sub>                  | Negative power supply voltage                                                            | -110                  | -100 | 0                     | V    |

| V <sub>S</sub> or V <sub>D</sub> | Signal path input/output voltage (source or drain pin) (Sx, D) <sup>(1)</sup>            | V <sub>SS</sub> + 10  |      | V <sub>DD</sub> – 10  | V    |

| V <sub>LL</sub>                  | SPI/Logic power supply voltage                                                           | 1.7                   |      | 5.5                   | V    |

| V <sub>L</sub>                   | Logic control pin voltage (DIN, DOUT, CLK, LE, CLR)                                      | 0                     |      | $V_{LL}$              | V    |

| V <sub>IH</sub>                  | Logic control pin high-level input voltage (DIN, DOUT, CLK, LE, CLR)                     | 0.9 x V <sub>LL</sub> |      |                       | V    |

| V <sub>IL</sub>                  | Logic control pin low-level input voltage (DIN, DOUT, CLK, $\overline{\text{LE}}$ , CLR) |                       |      | 0.1 x V <sub>LL</sub> | V    |

| T <sub>A</sub>                   | Ambient temperature                                                                      | -40                   |      | 85                    | °C   |

| T <sub>J</sub>                   | Junction temperature                                                                     | -40                   |      | 125                   | °C   |

<sup>(1)</sup>  $V_S$ ,  $V_D$  operation up to  $V_{SS}$  and  $V_{DD}$  is acceptable for recommended operation.  $R_{ON\ FLAT}$  may increase when operating beyond  $V_{SS}$  + 10 V and  $V_{DD}$  – 10 V

### 6.5 Electrical Characteristics: TMUX9616

$V_{DD}$  = +110 V,  $V_{SS}$  = -110 V,  $V_{LL}$  = 1.7 V - 5.5 V, GND = 0 V (unless otherwise noted) Typical at  $V_{DD}$  = +110 V,  $V_{SS}$  = -110 V,  $V_{LL}$  = 3.3 V,  $V_{LL}$  = 25°C (unless otherwise noted)

|                       | PARAMETER                                 | TEST CONDITIONS                                                                                           | T <sub>A</sub> | MIN                       | TYP  | mAX                       | UNIT |

|-----------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------|---------------------------|------|---------------------------|------|

| ANALOG                | SWITCH                                    |                                                                                                           |                |                           |      |                           |      |

|                       | 0                                         | V <sub>S</sub> = -100 V to +100 V                                                                         | 25°C           |                           | 14   | 19                        | Ω    |

| R <sub>ON</sub>       | On-resistance                             | $I_D = -5 \text{ mA}$                                                                                     | –40°C to +85°C |                           |      | 24                        | Ω    |

| D                     | On-resistance                             | V <sub>S</sub> = -100 V to +100 V                                                                         | 25°C           |                           | 13   | 17                        | Ω    |

| R <sub>ON</sub>       | On-resistance                             | $I_D = -200 \text{ mA}$                                                                                   | –40°C to +85°C |                           |      | 19                        | Ω    |

| <b>A.D.</b>           | On-resistance mis mAtch                   | V <sub>S</sub> = -100 V to +100 V                                                                         | 25°C           |                           | 2    |                           | %    |

| ΔR <sub>ON</sub>      | between channels                          | $I_D = -5 \text{ mA}$                                                                                     | –40°C to +85°C |                           |      | 20                        | %    |

| R <sub>ONL</sub>      | Large-Signal On-resistance                | I <sub>D</sub> = -1A                                                                                      | 25°C           |                           | 12   |                           | Ω    |

| I <sub>SWPK</sub>     | Switch Peak Output Current                | t <sub>PW</sub> ≤100 ns, duty cycle ≤ 0.1%, current into source or drain.                                 | 25°C           |                           | 3    |                           | Α    |

| I <sub>SWPK_DIO</sub> | Switch Peak Isolation Diode<br>Current    | t <sub>PW</sub> ≤300 ns, duty cycle ≤ 2%                                                                  | 25°C           |                           | 300  |                           | mA   |

| V <sub>DC_OFFS</sub>  | Switch DC Offeet Voltage                  | Switch ON or OFF, R <sub>L</sub> = No load                                                                | 25°C           |                           | 1.6  |                           | mV   |

| ET                    | Switch DC Offset Voltage                  | (Integrated Bleed Resistors)                                                                              | –40°C to +85°C | -60                       |      | 30                        | mV   |

| R <sub>INT</sub>      | Output Bleed Resistor                     | Source or Drain Output to GND,<br>I <sub>RINT</sub> = 20 μA. Switch is OFF                                | 25°C           | 20                        | 35   | 50                        | kΩ   |

|                       |                                           | V <sub>DD</sub> = 110 V, V <sub>SS</sub> = -110 V                                                         | 25°C           |                           | 0.07 |                           | μΑ   |

| I <sub>S(OFF)</sub>   | Source off leakage current <sup>(1)</sup> | Switch state is off<br>$V_S = +100 \text{ V} / -100 \text{ V}$<br>$V_D = -100 \text{ V} / +100 \text{ V}$ | -40°C to +85°C | -4                        |      | 4                         | μΑ   |

|                       |                                           | V <sub>DD</sub> = 110 V, V <sub>SS</sub> = -110 V                                                         | 25°C           |                           | 0.07 |                           | μΑ   |

| $I_{D(OFF)}$          | Drain off leakage current <sup>(1)</sup>  | Switch state is off<br>$V_S = +100 \text{ V} / -100 \text{ V}$<br>$V_D = -100 \text{ V} / +100 \text{ V}$ | -40°C to +85°C | -4                        |      | 4                         | μΑ   |

| DIGITAL I             | OGIC (DIN, DOUT, CLK, LE, CL              | R Pins)                                                                                                   |                |                           |      | '                         |      |

| V <sub>IH</sub>       | Logic voltage high                        | V <sub>LL</sub> = 1.7 V - 5.5 V                                                                           | -40°C to +85°C | 0.66 x<br>V <sub>LL</sub> |      |                           | V    |

| V <sub>IL</sub>       | Logic voltage low                         | V <sub>LL</sub> = 1.7 V - 5.5 V                                                                           | -40°C to +85°C |                           |      | 0.33 x<br>V <sub>LL</sub> | V    |

| I <sub>IH</sub>       | Input leakage current                     |                                                                                                           | -40°C to +85°C |                           |      | 1.0                       | μA   |

# 6.5 Electrical Characteristics: TMUX9616 (続き)

$V_{DD} = +110 \text{ V}, V_{SS} = -110 \text{ V}, V_{LL} = 1.7 \text{ V} - 5.5 \text{ V}, \text{GND} = 0 \text{ V} \text{ (unless otherwise noted)}$  Typical at  $V_{DD} = +110 \text{ V}, V_{SS} = -110 \text{ V}, V_{LL} = 3.3 \text{ V}, T_A = 25^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                      | PARAMETER                                | TEST CONDITIONS                                          | T <sub>A</sub> | MIN                   | TYP  | mAX                                                                    | UNIT |

|----------------------|------------------------------------------|----------------------------------------------------------|----------------|-----------------------|------|------------------------------------------------------------------------|------|

| I <sub>IL</sub>      | Input leakage current                    |                                                          | -40°C to +85°C | -1.0                  |      |                                                                        | μΑ   |

| C <sub>IN</sub>      | Logic input capacitance                  |                                                          | -40°C to +85°C |                       | 3    | 10                                                                     | pF   |

| V <sub>OH</sub>      | Logic high output voltage                | I <sub>SOURCE</sub> = 1 mA                               | -40°C to +85°C | V <sub>LL</sub> - 0.1 |      |                                                                        | V    |

| V <sub>OL</sub>      | Logic low output voltage                 | I <sub>SINK</sub> = 1 mA, includes open drain /THERM pin | -40°C to +85°C |                       |      | 0.1                                                                    | V    |

| POWER                | SUPPLY                                   |                                                          |                |                       |      |                                                                        |      |

|                      |                                          | V <sub>DD</sub> = 110 V, V <sub>SS</sub> = -110 V        | 25°C           |                       | 15   |                                                                        | μΑ   |

| I <sub>DDQ_OFF</sub> | V <sub>DD</sub> quiescent supply current | I <sub>D</sub> = -5 mA<br>Switches OFF                   | –40°C to +85°C |                       |      | 23                                                                     | μΑ   |

|                      |                                          | $V_{DD} = 110 \text{ V}, V_{SS} = -110 \text{ V}$        | 25°C           |                       | 40   |                                                                        | μΑ   |

| I <sub>DDQ_ON</sub>  | V <sub>DD</sub> quiescent supply current | I <sub>D</sub> = -5 mA<br>Switches ON                    | -40°C to +85°C |                       |      | 95                                                                     | μΑ   |

|                      |                                          | V <sub>DD</sub> = 110 V, V <sub>SS</sub> = -110 V        | 25°C           |                       | 10   | 3 10<br>0.1<br>0.1<br>5 23<br>10 95<br>10 65<br>22 40<br>4 4 .1 4 .8 8 | μA   |

| I <sub>SSQ_OFF</sub> | V <sub>SS</sub> quiescent supply current | I <sub>D</sub> = -5 mA<br>Switches OFF                   | -40°C to +85°C |                       |      |                                                                        | μA   |

| _                    |                                          | V <sub>DD</sub> = 110 V, V <sub>SS</sub> = -110 V        | 25°C           |                       | 22   |                                                                        | μΑ   |

| I <sub>SSQ_ON</sub>  | V <sub>SS</sub> quiescent supply current | I <sub>D</sub> = -5 mA<br>Switches ON                    | -40°C to +85°C |                       |      | 40                                                                     | μΑ   |

|                      |                                          | $V_{DD} = 110 \text{ V}, V_{SS} = -110 \text{ V}$        | 25°C           |                       | 2.4  |                                                                        | mA   |

| I <sub>DD</sub>      | V <sub>DD</sub> dynamic supply current   | All switches turned ON and OFF at f = 50 kHz             | -40°C to +85°C |                       |      | 4                                                                      | mA   |

|                      |                                          | V <sub>DD</sub> = 110 V, V <sub>SS</sub> = -110 V        | 25°C           |                       | 3.1  |                                                                        | mA   |

| I <sub>SS</sub>      | V <sub>SS</sub> dynamic supply current   | All switches turned ON and OFF at f = 50 kHz             | -40°C to +85°C |                       |      | 4                                                                      | mA   |

| 1                    | V <sub>II</sub> quiescent supply current |                                                          | 25°C           |                       | 3.8  |                                                                        | μΑ   |

| I <sub>LLQ</sub>     | VLL quiescent supply cultent             |                                                          | -40°C to +85°C |                       |      | 8                                                                      | μΑ   |

|                      | V dynamia aupply aurrent                 | fOLK = 5 MHz \/ = 5 \/                                   | 25°C           |                       | 0.20 |                                                                        | mA   |

| ارر                  | V <sub>LL</sub> dynamic supply current   | $fCLK = 5 MHz, V_{LL} = 5 V$                             | –40°C to +85°C |                       |      | 0.25                                                                   | mA   |

<sup>(1)</sup> When  $V_S$  is positive,  $V_D$  is negative, or when  $V_S$  is negative,  $V_D$  is positive.

# 6.6 Switching Characteristics: TMUX9616

$V_{DD} = +110 \text{ V, } V_{SS} = -110 \text{ V, } V_{LL} = 1.7 \text{V - } 5.5 \text{ V, GND} = 0 \text{ V (unless otherwise noted)}$  Typical at  $V_{DD} = +110 \text{ V, } V_{SS} = -110 \text{ V, } V_{LL} = 3.3 \text{ V, } T_A = 25 ^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER            |                                    | TEST CONDITIONS                                                                                                             | T <sub>A</sub> | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------|-----|-----|-----|------|

| +                    | Turn-on time from enable           | V <sub>S</sub> = 100 V                                                                                                      | 25°C           |     | 1.5 |     | μs   |

| t <sub>ON</sub>      | Turn-on time from enable           | $R_L = 10 \text{ k}\Omega$                                                                                                  | -40°C to +85°C |     |     | 3   | μs   |

|                      | Turn-off time from enable          | V <sub>S</sub> = 100 V                                                                                                      | 25°C           |     | 0.8 |     | μs   |

| t <sub>OFF</sub>     | Turr-on time nom enable            | $R_L = 10 \text{ k}\Omega$                                                                                                  | -40°C to +85°C |     |     | 2.5 | μs   |

| dV/dt <sub>MAX</sub> | Maximum Analog Signal Slew<br>Rate |                                                                                                                             | -40°C to +85°C |     |     | 20  | V/ns |

| O <sub>ISO_TX</sub>  | Off-isolation TX                   | $R_L = 50 \Omega$<br>V <sub>S</sub> = 0 V <sub>BIAS</sub> , 10 V <sub>PP</sub> , f = 5 MHz                                  | 25°C           |     | -70 |     | dB   |

| O <sub>ISO_TX</sub>  | Off-isolation TX                   | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$<br>$V_S = 0 \text{ V}_{BIAS}$ , $10 \text{ V}_{PP}$ , $f = 5 \text{ MHz}$ | 25°C           |     | -54 |     | dB   |

| O <sub>ISO_RX</sub>  | Off-isolation RX                   | $R_L = 50 \Omega$<br>$V_D = 0 V_{BIAS}, 10 V_{PP}, f = 5 MHz$                                                               | 25°C           |     | -70 |     | dB   |

Copyright © 2023 Texas Instruments Incorporated

8

# 6.6 Switching Characteristics: TMUX9616 (続き)

$V_{DD} = +110 \text{ V}, V_{SS} = -110 \text{ V}, V_{LL} = 1.7 \text{V} - 5.5 \text{ V}, \text{GND} = 0 \text{ V} \text{ (unless otherwise noted)}$   $\text{Typical at V}_{DD} = +110 \text{ V}, V_{SS} = -110 \text{ V}, V_{LL} = 3.3 \text{ V}, T_A = 25 ^{\circ}\text{C} \text{ (unless otherwise noted)}$

|                                                       | PARAMETER                                                       | TEST CONDITIONS                                                                                                                                          | TA             | MIN TYP     | MAX | UNIT |

|-------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-----|------|

| O <sub>ISO_RX</sub>                                   | Off-isolation RX                                                | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$<br>$V_D = 0 \text{ V}_{BIAS}$ , $10 \text{ V}_{PP}$ , $f = 5 \text{ MHz}$                              | 25°C           | -54         |     | dB   |

| X <sub>TALK_TX</sub>                                  | Crosstalk TX                                                    | $R_L = 50 \Omega$<br>$V_S = 0 V_{BIAS}, 10 V_{PP}, f = 5 MHz$                                                                                            | 25°C           | <b>–</b> 75 | dB  |      |

| X <sub>TALK_RX</sub>                                  | Crosstalk RX                                                    | $R_L = 50 \Omega$<br>$V_D = 0 V_{BIAS}, 10 V_{PP}, f = 5 MHz$                                                                                            | 25°C           | <b>–</b> 75 | dB  |      |

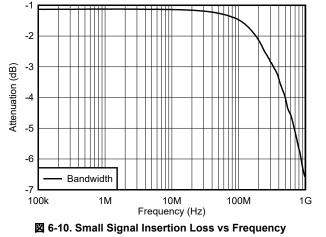

| BW <sub>SS_TX</sub>                                   | -3dB Bandwidth (Small Signal)<br>TX                             | $R_L = 50 \Omega$<br>V <sub>S</sub> = 0 V, Vpp = 200 mV                                                                                                  | 25°C           | 500         |     | MHz  |

| BW <sub>SS_RX</sub>                                   | -3dB Bandwidth (Small Signal)<br>RX                             | $R_L = 50 \Omega$<br>$V_D = 0 V, Vpp = 200 mV$                                                                                                           | 25°C           | 500         |     | MHz  |

| HD2PC_<br>LL_TX                                       | Second Harmonic Distortion Pulse Cancellation (Large Signal) TX | $V_{PP} = 200 \text{ V}, V_S = 0 \text{ V}$ $R_L = 100 \Omega \parallel 100 \text{ pF}$ $f = 5 \text{ MHz}, 2 \text{ Cycles, dv/dt:}$ $7.1 \text{ V/ns}$ | 25°C           | 54          |     | dBc  |

| C <sub>S(OFF)</sub>                                   | Source off capacitance                                          | $V_S = 0 V_{BIAS}$ , 100 m $V_{PP}$ , f = 1 MHz                                                                                                          | 25°C           | 5           |     | pF   |

| C <sub>D(OFF)</sub>                                   | Drain off capacitance                                           | $V_D = 0 V_{BIAS}$ , 100 m $V_{PP}$ , f = 1 MHz                                                                                                          | 25°C           | 5           |     | pF   |

| $\begin{matrix} C_{S(ON),} \\ C_{D(ON)} \end{matrix}$ | On capacitance                                                  | $V_S/V_D = 0 V_{BIAS}$ , 100 m $V_{PP}$ , f = 1 MHz                                                                                                      | 25°C           | 10          |     | pF   |

| $V_{SPK}$                                             | Output voltage spike                                            | $R_{L\_Source}$ = 1k $\Omega$ , $R_{L\_Drain}$ = 50 $\Omega$<br>Enable and Disable Switch                                                                | 25°C           | -45         | 18  | mV   |

| V <sub>SPK</sub>                                      | Output voltage spike                                            | $R_{L\_Source}$ = 1k $\Omega$ , $R_{L\_Drain}$ = 50 $\Omega$<br>Enable and Disable Switch                                                                | -40°C to +85°C | -55         | 25  | mV   |

# 6.7 Digital Timings: TMUX9616

$V_{DD}$  = 4.5 V - 5.5 V,  $V_{LL}$  = 1.7V - 5.5 V, GND = 0 V (unless otherwise noted) Typical at  $V_{DD}$  = 5 V,  $V_{LL}$  = 3.3 V,  $T_A$  = 25°C (unless otherwise noted)

|                                     | PARAMETER                                        | TEST CONDITIONS         | T <sub>A</sub> | MIN   | TYP MAX | UNIT |

|-------------------------------------|--------------------------------------------------|-------------------------|----------------|-------|---------|------|

| f <sub>CLK_SPI</sub>                | SPI Clock Frequency (including daisy chain mode) | V <sub>LL</sub> = 5 V   | -40°C to +85°C |       | 72      | MHz  |

| f <sub>CLK_SPI</sub>                | SPI Clock Frequency (including daisy chain mode) | V <sub>LL</sub> = 3.3 V | -40°C to +85°C |       | 54      | MHz  |

| f <sub>CLK_SPI</sub>                | SPI Clock Frequency (including daisy chain mode) | V <sub>LL</sub> = 1.8 V | -40°C to +85°C |       | 24      | MHz  |

| t <sub>R</sub> , t <sub>F_SPI</sub> | SPI Clock Rise and Fall Times                    |                         | -40°C to +85°C |       | 50      | ns   |

| t <sub>CLK_SPI</sub>                | CLK SPI Period                                   | V <sub>LL</sub> = 5 V   | -40°C to +85°C | 11.76 |         | ns   |

| t <sub>CLK_SPI</sub>                | CLK SPI Period                                   | V <sub>LL</sub> = 3.3 V | –40°C to +85°C | 16.67 |         | ns   |

| t <sub>CLK_SPI</sub>                | CLK SPI Period                                   | V <sub>LL</sub> = 1.8 V | -40°C to +85°C | 41.67 |         | ns   |

| t <sub>CLK_H_SPI</sub>              | CLK High Time SPI                                | V <sub>LL</sub> = 5 V   | -40°C to +85°C | 5.29  |         | ns   |

| t <sub>CLK_H_SPI</sub>              | CLK High Time SPI                                | V <sub>LL</sub> = 3.3 V | -40°C to +85°C | 7.5   |         | ns   |

| t <sub>CLK_H_SPI</sub>              | CLK High Time SPI                                | V <sub>LL</sub> = 1.8 V | -40°C to +85°C | 18.75 |         | ns   |

| t <sub>CLK_L_SPI</sub>              | CLK Low Time SPI                                 | V <sub>LL</sub> = 5 V   | -40°C to +85°C | 5.29  |         | ns   |

| t <sub>CLK_L_SPI</sub>              | CLK Low Time SPI                                 | V <sub>LL</sub> = 3.3 V | -40°C to +85°C | 7.5   |         | ns   |

| t <sub>CLK_L_SPI</sub>              | CLK Low Time SPI                                 | V <sub>LL</sub> = 1.8 V | -40°C to +85°C | 18.75 |         | ns   |

| t <sub>SU_SPI</sub>                 | Set Up Time Data to Clock SPI                    | V <sub>LL</sub> = 5 V   | -40°C to +85°C | 1.0   |         | ns   |

| t <sub>SU_SPI</sub>                 | Set Up Time Data to Clock SPI                    | V <sub>LL</sub> = 3.3 V | -40°C to +85°C | 2     |         | ns   |

| t <sub>SU_SPI</sub>                 | Set Up Time Data to Clock SPI                    | V <sub>LL</sub> = 1.8 V | –40°C to +85°C | 5     |         | ns   |

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# 6.7 Digital Timings: TMUX9616 (続き)

$\begin{aligned} &V_{DD} = 4.5 \text{ V} - 5.5 \text{ V}, V_{LL} = 1.7 \text{V} - 5.5 \text{ V}, \text{GND} = 0 \text{ V} \text{ (unless otherwise noted)} \\ &\text{Typical at } V_{DD} = 5 \text{ V}, V_{LL} = 3.3 \text{ V}, T_{A} = 25 ^{\circ}\text{C} \text{ (unless otherwise noted)} \end{aligned}$

|                    | PARAMETER                    | TEST CONDITIONS         | T <sub>A</sub> | MIN | TYP MAX | UNIT |

|--------------------|------------------------------|-------------------------|----------------|-----|---------|------|

| t <sub>H_SPI</sub> | Hold Time Data to Clock SPI  | V <sub>LL</sub> = 5 V   | -40°C to +85°C | 1.0 |         | ns   |

| t <sub>H_SPI</sub> | Hold Time Data to Clock SPI  | V <sub>LL</sub> = 3.3 V | -40°C to +85°C | 1.2 |         | ns   |

| t <sub>H_SPI</sub> | Hold Time Data to Clock SPI  | V <sub>LL</sub> = 1.8 V | -40°C to +85°C | 3   |         | ns   |

| t <sub>DO</sub>    | Clock Delay Time to Data Out | V <sub>LL</sub> = 5 V   | -40°C to +85°C | 3   | 12.8    | ns   |

| t <sub>DO</sub>    | Clock Delay Time to Data Out | V <sub>LL</sub> = 3.3 V | -40°C to +85°C | 4   | 16.3    | ns   |

| t <sub>DO</sub>    | Clock Delay Time to Data Out | V <sub>LL</sub> = 1.8 V | -40°C to +85°C | 7   | 34      | ns   |

| t <sub>S/LE</sub>  | Set Up Time Before LE Rises  |                         | -40°C to +85°C | 25  |         | ns   |

| t <sub>W/LE</sub>  | Time Width of LE             |                         | -40°C to +85°C | 12  |         | ns   |

| t <sub>WCLR</sub>  | Time Width of CLR            |                         | -40°C to +85°C | 55  |         | ns   |

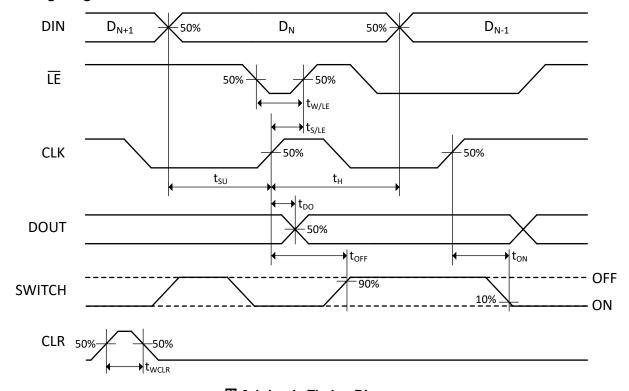

# **6.8 Timing Diagrams**

図 6-1. Logic Timing Diagram

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2023 Texas Instruments Incorporated

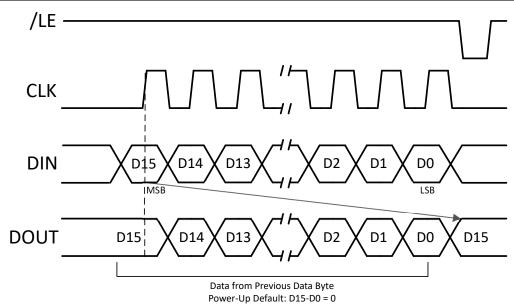

図 6-2. Latch Enable Timing Diagram

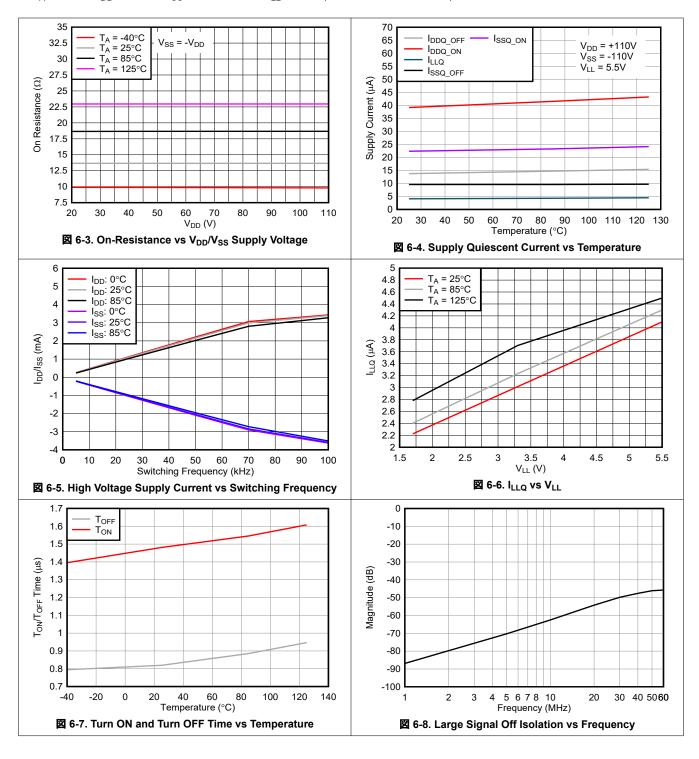

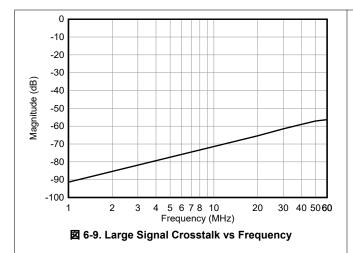

### 6.9 Typical Characteristics

at  $T_A = 25$ °C,  $V_{DD} = 110$  V,  $V_{SS} = -110$  V, and  $V_{LL} = 3.3$ V (unless otherwise noted)

# **6.9 Typical Characteristics (continued)**

at  $T_A$  = 25°C,  $V_{DD}$  = 110 V,  $V_{SS}$  = -110 V, and  $V_{LL}$  = 3.3V (unless otherwise noted)

13

### 7 Parameter Measurement Information

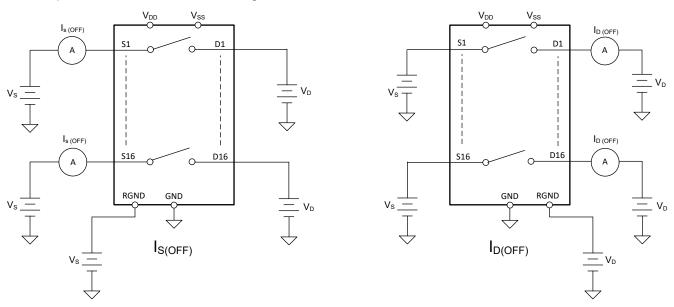

# 7.1 Off-Leakage Current

There are two types of leakage currents associated with a switch during the off state:

- Source off-leakage current I<sub>S(OFF)</sub>: the leakage current flowing into or out of the source pin when the switch is off.

- 2. Drain off-leakage current  $I_{D(OFF)}$ : the leakage current flowing into or out of the drain pin when the switch is off.

The setup used to measure both off-leakage currents is shown in ⊠ 7-1.

図 7-1. Off-Leakage Measurement Setup

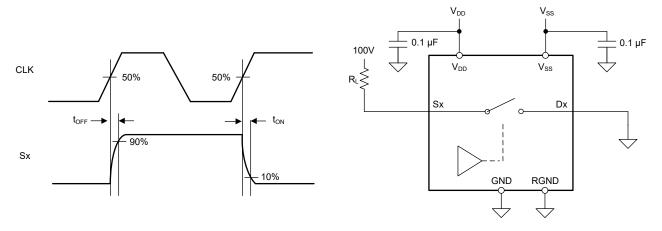

#### 7.2 Device Turn On/Off Time

Turn-off time ( $t_{OFF}$ ) is defined as the time taken by the Sx pin of the TMUX9616 to rise to a 90% final value after the CLK signal has risen to 50% of its final value. Turn-on time ( $t_{ON}$ ) is defined as the time taken by the output of the TMUX9616 to fall to a 10% initial value after the CLK signal has risen) to 50% of its final value.  $\boxtimes$  7-2 shows the setup used to measure  $t_{ON}$  and  $t_{OFF}$ .

図 7-2. Turn-on/off Measurement Setup

Copyright © 2023 Texas Instruments Incorporated

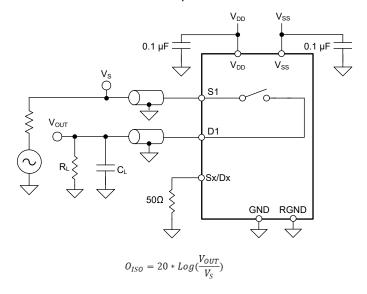

# 7.3 Off Isolation

Off isolation is defined as the ratio of the signal at the drain pin (Dx) of the device when a signal is applied to the source pin (Sx) of an off-channel.  $\boxtimes$  7-3 shows the setup used to measure off isolation.

図 7-3. Off Isolation Measurement Setup

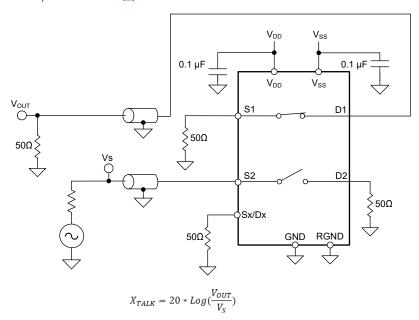

#### 7.4 Inter-Channel Crosstalk

Crosstalk ( $X_{TALK}$ ) is defined as the ratio of the output signal at the Dx pin of an on-channel to the input signal at the Sx pin of an off-channel, as shown in  $\boxtimes$  7-4.

図 7-4. Crosstalk Measurement Setup

15

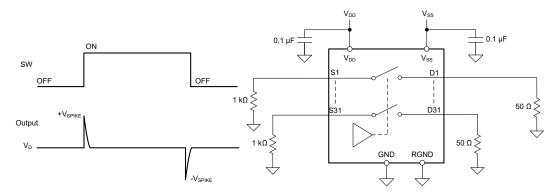

### 7.5 Output Voltage Spike

Output Voltage Spike ( $V_{SPIKE}$  or  $V_{SPK}$ ) is the magnitude of the transient output voltage spike which occurs on an input or output pin when turning the switch channel ON or OFF. When measuring  $V_{SPK}$  on the Dx pin, 50  $\Omega$  is placed on the Dx pin and 1 k $\Omega$  is placed on the Sx pin. Likewise, when measuring  $V_{SPK}$  on the Sx pin, 50  $\Omega$  is placed on the Sx pin and 1 k $\Omega$  is placed on the Dx pin.  $\boxtimes$  7-5 shows the setup used to measure the  $V_{SPK}$  of the switch.

図 7-5. V<sub>SPK</sub> Measurement Setup

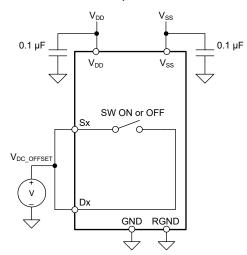

### 7.6 Switch DC Offset Voltage

The switch DC offset voltage ( $V_{DC\_OFFSET}$ ) is the DC offset voltage that can be present on an Sx or Dx pin when the switch channel is ON or OFF.  $\boxed{2}$  7-6 shows the setup used to measure the  $V_{DC\_OFFSET}$  voltage of the device.

☑ 7-6. V<sub>DC</sub> OFFSET Measurement Setup

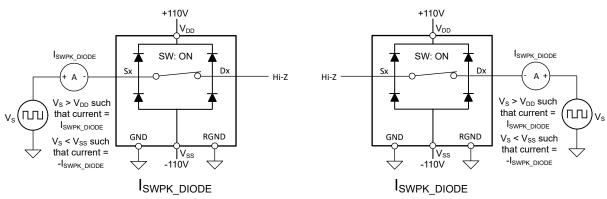

#### 7.7 Isolation Diode Current

The switch peak isolation diode current ( $I_{SWPK\_DIODE}$ ) is the maximum peak current the isolation diodes on each channel can sustain.  $\boxtimes$  7-7 shows the set-up used to measure  $I_{SWPK\_DIODE}$

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2023 Texas Instruments Incorporated

図 7-7. Isolation Diode Current Measurement Setup

17

# 8 Detailed Description

#### 8.1 Overview

The TMUX9616 is a 16-channel low resistance, low capacitance high-voltage analog switch integrated circuit (IC) with latch-up immunity. Each device has 16 independently selectable 1:1, single-pole, single-throw (SPST) switch channels. The device works well with dual supplies up to  $\pm 110$  V. Asymmetric supply biasing is also supported within the recommended supply range. The TMUX9616 supports bidirectional analog and digital signals on the source (Sx) and drain (Dx) pins ranging from  $V_{SS}$  to  $V_{DD}$ . TMUX9616 also integrates bleed resistors on its source (Sx) and drain (Dx) pins to discharge capacitive loads, like piezoelectric transducers.

#### 8.2 Functional Block Diagram

# 8.3 Feature Description

#### 8.3.1 Wide Input Signal Range (up to ±110 V, 220 V<sub>PP</sub>)

TMUX9616 can pass a wide input signal range, up to  $V_{DD}/V_{SS}$  of ±110 V (220  $V_{PP}$ ), which is very beneficial as many high voltage transmitters are designed to transmit up to ±100 V. The extra headroom above ±100 V that TMUX9616 provides is critical for operating the high voltage transmitters in systems up to ±100 V for a few reasons. First, with high voltage supply multiplexers (±110 V  $V_{DD}/V_{SS}$ ), typically as the  $V_S$  pin approaches  $V_{DD}$  ( $V_S > V_{DD}$  - (5 V to 10 V)), the  $R_{ON}$  of the switch starts to rapidly increase. With a large change in  $R_{ON}$  when  $V_S$  is near  $V_{DD}$ , this can cause the harmonic distortion performance of the system to degrade (HD2PC, so fourth). Setting the high voltage supplies 10 V above the pulser operating voltage, allows  $V_S$  to stay  $\leq$  ( $V_{DD}$  - 10 V), keeping the switch in its flat  $R_{ON}$  operating region for the intended TX signal, and therefore greatly improving system harmonic distortion performance.

Second, various system parasitics (or even intentionally added tuning inductors) and transmission line reflections in the system (due to cables, long PCB traces, and so forth) can cause some temporary peaking of the maximum voltage that the TMUX9616 receives above the ±100 V maximum output voltage of the high voltage transmitter. Having the high voltage multiplexer in the system have voltage tolerance above the high voltage transmitter (up to VDD = +110 V and VSS = -110 V per *Recommended Operating Conditions*) is crucial for being able to run the system at the high voltage transmitters maximum voltage output capability.

#### 8.3.2 Bidirectional Operation

The devices conduct equally well from source (Sx) to drain (Dx) or from drain (Dx) to source (Sx). Each signal path has very similar characteristics in both directions.

Copyright © 2023 Texas Instruments Incorporated

English Data Sheet: SCDS436

#### 8.3.3 Device Digital Logic Control

The TMUX9616 is controlled by a SPI interface to a 16-bit shift register, and a CLR pin. The SPI interface can run at speeds up to 72 MHz. It can also be run with 1.8 V – 5 V logic levels (set by logic supply  $V_{LL}$ ). The DIN pin will take in the data for the 16-bit register, and CLK will take in the clock signal. Data is shifted in on the DIN pin with the most-significant bit (MSB) first. After writing in 16 bits into the shift register using DIN and CLK,  $\overline{LE}$  is then used to latch the state of the switches in the shift register to change the state of the switches in analog. The switches go to a state of retaining their present state on the rising edge of the  $\overline{LE}$  pin. When  $\overline{LE}$  is high, updates to the shift register does not change the condition of the 16 switches until  $\overline{LE}$  is made low again. When  $\overline{LE}$  is low, the shift register data flows through the latch and the condition of the 16 switches will be changed as the shift register is updated.

TMUX9616 16-bit shift register can be used in daisy chain mode. This is done by connecting the DOUT pin of the first TMUX9616 device to the DIN pin of the next TMUX9616 device in the chain. All TMUX9616 in the daisy chain will share the same source CLK signal (the CLK pin of each device in the daisy chain will be shorted together). DOUT is the data output pin of the 16<sup>th</sup> bit of the shift register, which is the data on DIN clock shifted by 16 clock cycles. The LE pin of each device in the chain will be shorted together, using the same LE source.

Assuming N number of TMUX9616 devices in the daisy chain, the standard method of writing to the shift registers is to write 16 \* N bits of data, corresponding to each switch in the daisy chain, with  $\overline{\text{LE}}$  set high. Once all 16 \* N bits are written into the shift register,  $\overline{\text{LE}}$  is pulsed low for at least  $t_{\text{WLE}}$  to update the condition of the 16 \* N switches in the daisy chain to the new state recorded in the shift register. Then  $\overline{\text{LE}}$  is set high again so that the state of the switches will not change until the next 16 \* N bits are written into the shift register (and  $\overline{\text{LE}}$  is pulsed low again following the 16 \* N bit write).

The CLR pin, when asserted high, causes all the 16 switches in TMUX9616 to turn OFF, regardless of the state of the bits in the 16-bit shift register. When the CLR pin asserted low, the switches will then use the shift register again to set its values.

For more details on programming the shift register and the logic state of each switch, see the *Device Logic Table* section. For more details of programming the shift register with the correct digital timings, see the *Timing Diagrams* section and the *Digital Timings* table. For more details on the maximum speeds obtainable in daisy chain mode depending on device configuration, see the *Switching Characteristics* table. 🗵 8-1 shows more details on how to connect the TMUX9616 device's in daisy chain mode.

図 8-1. Daisy Chain System Block Diagram

19

#### 8.3.4 Latch-Up Immunity by Device Construction

Latch-up is a condition where a low impedance path is created between a supply pin and ground. This condition is caused by a trigger (current injection or overvoltage), but once activated, the low impedance path remains even after the trigger is no longer present. This low impedance path may cause system upset or catastrophic damage due to excessive current levels. The latch-up condition typically requires a power cycle to eliminate the low impedance path.

The TMUX9616 is constructed on silicon on insulator (SOI) based process where an oxide layer is added between the PMOS and NMOS transistor of each CMOS switch to prevent parasitic structures from forming. The oxide layer is also known as an insulating trench and prevents triggering of latch up events due to overvoltage, fast voltage slew rates, and current injections. The latch-up immunity feature allows the TMUX9616 to be used in harsh environments. For more information on latch-up immunity, refer to Using Latch Up Immune Multiplexers to Help Improve System Reliability.

#### 8.4 Device Functional Modes

#### 8.4.1 Normal Mode

In normal mode operation, TMUX9616 is controlled by its digital logic, which is detailed in the *Device Digital* Logic Control section. In normal mode, switches are available to be used to pass high voltage ±110 V signals (signals from V<sub>SS</sub> to V<sub>DD</sub>). More details of the device operation in normal mode can be found in the Feature Description and Device Logic Table sections.

#### 8.4.2 Device Power Up

TMUX9616 will be powered up once  $V_{LL}$ ,  $V_{DD}$ , and  $V_{SS}$  reach their final voltage.  $V_{LL}$ ,  $V_{DD}$ , and  $V_{SS}$  can be powered up in any order (there is no power sequencing requirement). The device digital logic control will not receive updates until both V<sub>LL</sub>, V<sub>DD</sub>, and V<sub>SS</sub> are powered up. Additionally, after V<sub>LL</sub>, V<sub>DD</sub>, and V<sub>SS</sub> are powered up, the system FPGA or controller should wait at least 500 µs until writing to the device digital logic control. For more details on the device digital logic control, see the Device Digital Logic Control section.

On power-up, all 16 switches in TMUX9616 will be in the OFF state.

#### 8.5 Device Logic Table

Inputs Outputs D0 D1 D15 Œ CLR SW0 SW1 SW15 0 OFF L L ī L ON 0 L L OFF L ON L L L L L 1 L L ON HOLD PREVIOUS STATE Н Х Χ Х Χ Х Н

表 8-1. Device Logic Table (1)(2)(3)(4)(5)(6)(7)

- (1) All 16 switches operate independently.

- Serial data is clocked in on the rising edge of CLK. Data is shifted in on the DIN pin with the most-significant bit (MSB) first.

- The switches go to a state of retaining their present state on the rising edge of the  $\overline{\text{LE}}$  pin. Once the  $\overline{\text{LE}}$  pin is high, updates to the shift register no longer change the condition of the 16 switches until the LE pin is made low again. When the LE is low, the shift register data flows through the latch.

- Shift register clocking has no effect on the switch states if the LE pin is high.

- DOUT is the data output pin of the 16 bit shift register for daisy chaining multiple muxes together. It is the data of the DIN clock shifted by the 16 clock cycles.

- The CLR input overrides all other inputs.

- While LE = H or CLR = H, if the CLK pin still receiving a valid clock signal, DIN will still function and input data into the shift register, and DOUT will still output the contents on the shift register. However, while  $\overline{LE} = H$  or CLR = H, the state of the analog switches is no longer dependent on the contents of the shift register, but rather takes the state per this logic table.

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

The TMUX9616 is a 16-channel low harmonic distortion, low resistance, low capacitance, high-voltage analog switch integrated circuit (IC) with latch-up immunity. Each device has 16 independently selectable 1:1, single-pole, single-throw (SPST) switch channels. The device can support high voltage supplies and signals up to ±110V. It comes in popular, pin-to-pin (P2P) 48-pin QFP package for 16CH SPST multiplexers. This makes TMUX9616 a great replacement in an existing design with fixed foot print, where improvement is needed on harmonic distortion performance of the system. Also, TMUX9616 a great solution any time the application may require a leaded package.

# 9.2 Typical Application

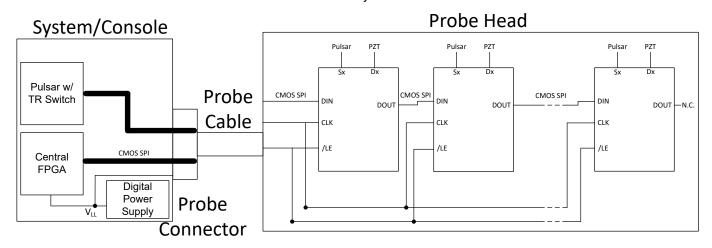

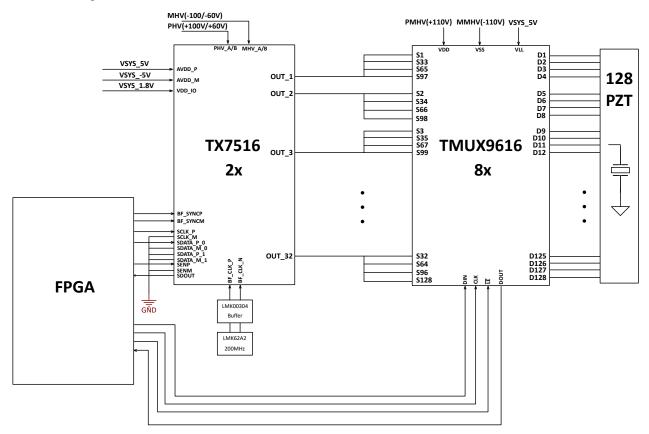

☑ 9-1 shows a multiplexer configuration that is found in a variety of ultrasound applications. Two TX7516 are used to provide 32 TX/RX channels, and 8x TMUX9616 are used to multiplex the 32 TX/RX channels to 128 piezoelectric (PZT) elements, making a 4:1 multiplexer configuration. An FPGA controls both the TX7516 and TMUX9616 using SPI.

図 9-1. TMUX9616 Application Schematic

21

#### 9.2.1 Design Requirements

表 9-1. Design Parameters

| PARAMETERS                                         | VALUES          |

|----------------------------------------------------|-----------------|

| Positive analog supply (V <sub>DD</sub> ) TMUX9616 | +110 V          |

| Negative analog supply (V <sub>SS</sub> ) TMUX9616 | -110 V          |

| Logic supply (V <sub>LL</sub> ) TMUX9616           | 5 V             |

| Pulser supply A (PHV_A/MHV_A) TX7516               | +100 V/-100 V   |

| Pulser supply B (PHV_B/MHV_B) TX7516               | +60 V/-60 V     |

| Analog signal support TMUX9616                     | ±110 V          |

| Maximum SPI speed supported TMUX9616               | 72 MHz          |

| System level HD2PC target requirement              | ≥40 dB          |

| System level HD1PC target requirement              | ≥40 dB          |

| System test load                                   | 100 Ω    100 pF |

#### 9.2.2 Detailed Design Procedure

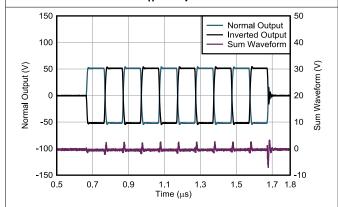

☑ 9-1 shows a system configuration found in a variety of ultrasound applications. The TX7516 has two supply rails A (PHV\_A/MHV\_A) and B (PHV\_B/MHV\_B) that enable switching between multiple TX levels for 3-Level mode, and also enable transmitting 5-Level mode. Each supply channel (A or B) can both provide up to 2 A output current, and the two channels can be operated in parallel for a 4 A output mode. Two TX7516 are used to provide 32 TX channels, and eight TMUX9616 are used to multiplex the 32 TX channels to the 128 PZT elements (4:1 mux configuration). Supply A will transmit at ±100 V, and supply B will transmit ±60 V.

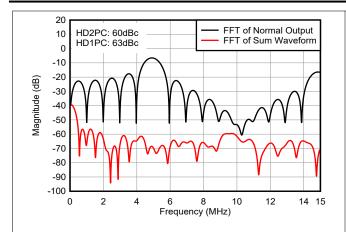

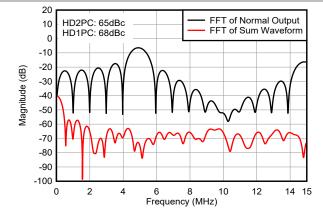

A very important system level requirement for good image quality is to target ≥40 dB for both HD2PC and HD1PC (harmonic distortion pulse cancellation). The entire system, including both the TX7516 pulser and TMUX9616 mux, must output a TX signal at ≥40 dB. TX7516 is a pulser with excellent output signal performance, performing higher than the ≥40 dB target. Additionally, TMUX9616 is an excellent multiplexer, having minimal and in many cases negligible impact on the HD2PC/HD1PC performance, keeping the output signal performance high for good image quality while also allowing to increase the number of PZT elements in the system without increasing the number of pulser TX channels.

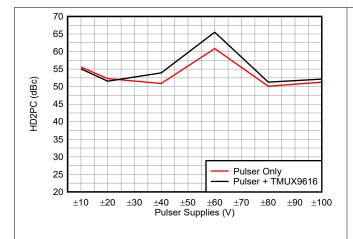

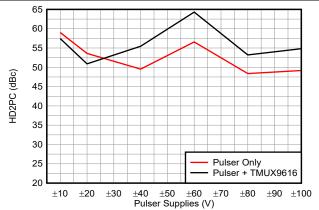

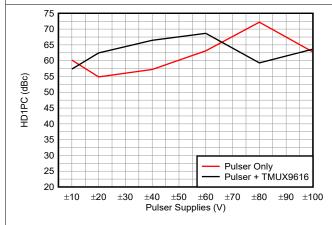

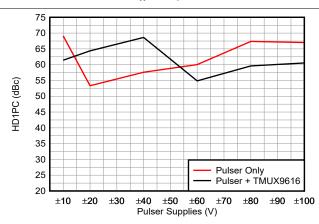

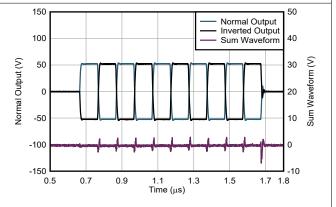

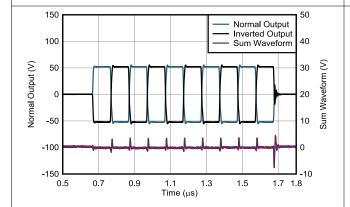

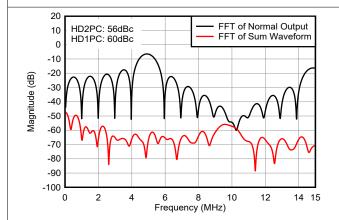

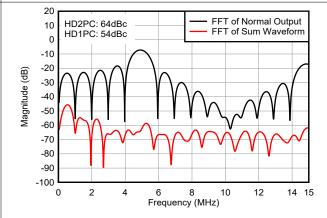

An example system use case using the TX7516EVM with the TMUX9616 EVM was performed first with the TMUX9616 removed and replaced with a pass through connection. Second, the same system level use case was performed by removing the pass through connection and adding the TMUX9616 back into the signal path. For a  $\pm 100$  V pulser supply in this system use case, transmitting in 3-level mode with 5 cycles at 5 MHz with a 100  $\Omega$  || 100 pF test load, TX7516 alone performed with an HD2PC of 49 dB and an HD1PC of 67 dB. For the same use case, adding in TMUX9616 into the signal path, the system performed with an HD2PC of 54 dB and an HD1PC of 60 dB. Therefore, in this use case the TMUX9616 has negligible impact on the system level HD2PC/HD1PC performance; TX7516, by itself, and TX7516 with TMUX9616 in its signal path perform at an HD2PC/HD1PC performance level well above 40 dB.

For more details on the HD2PC and HD1PC performance of TX7516 and TMUX9616 across multiple supply levels, see the *Application Curves*. Additionally, some example use cases are plotted in the time domain and frequency domain for observation.

Product Folder Links: TMUX9616

つせ) を送信 Copyright © 2023 Texas Instruments Incorporated

# 9.2.3 Application Curves

図 9-2. HD2PC TMUX9616 Input, 5 MHz, 5 Cycles, 100 Ω || 100 pF Load

図 9-3. HD2PC TMUX9616 Output, 5 MHz, 5 Cycles, 100 Ω || 100 pF Load

図 9-4. HD1PC TMUX9616 Input, 5 MHz, 5 Cycles, 100 Ω || 100 pF Load

図 9-5. HD1PC TMUX9616 Output, 5 MHz, 5 Cycles, 100 Ω || 100 pF Load

図 9-6. Pulser Only, Mux Input Side, ±60 V Pulser Supplies, 5 MHz, 5 Cycles, 100  $\Omega$  || 100 pF Load

図 9-7. Pulser + TMUX9616, Mux Input Side, ±60 V Pulser Supplies, 5 MHz, 5 Cycles, 100  $\Omega$  || 100 pF Load

図 9-8. Pulser Only, Mux Input Side,  $\pm 60$  V Pulser Supplies, 5 MHz, 5 Cycles,  $\pm 100$   $\Omega$  || 100 pF Load

図 9-9. Pulser + TMUX9616, Mux Input Side, ±60 V Pulser Supplies, 5 MHz, 5 Cycles, 100  $\Omega$  || 100 pF Load

図 9-10. Pulser Only, Mux Output Side,  $\pm 60$  V Pulser Supplies, 5 MHz, 5 Cycles, 100  $\Omega$  || 100 pF Load

図 9-11. Pulser + TMUX9616, Mux Output Side, ±60 V Pulser Supplies, 5 MHz, 5 Cycles, 100 Ω || 100 pF Load

図 9-12. Pulser Only, Mux Output Side,  $\pm 60$  V Pulser Supplies, 5 MHz, 5 Cycles,  $100 \Omega \parallel 100$  pF Load

図 9-13. Pulser + TMUX9616, Mux Output Side, ±60 V Pulser Supplies, 5 MHz, 5 Cycles, 100 Ω || 100 pF Load

### 9.3 Power Supply Recommendations

The TMUX9616 supports a wide signal range of ±110 V (signals from V<sub>SS</sub> to V<sub>DD</sub>). It is recommended to use a supply decoupling capacitor of at least 0.1 µF at the V<sub>DD</sub> pin to ground and at the V<sub>SS</sub> pin to ground. It is also recommended to use a supply decoupling capacitor for the logic supply V<sub>LL</sub> of at least 0.1 μF (V<sub>LL</sub> pin to ground). The TMUX9616 EVM uses 1  $\mu$ F capacitor in parallel with a 0.1  $\mu$ F capacitor for both the  $V_{DD}$ ,  $V_{SS}$ , and  $V_{LL}$ supply pins.

There are no specific power sequencing requirements between the V<sub>DD</sub>, V<sub>SS</sub>, and V<sub>LL</sub> supplies.

#### 9.4 Lavout

#### 9.4.1 Layout Guidelines

The following image shows an example of a PCB layout with the TMUX9616. Some key considerations are as

- For reliable operation, connect at least one decoupling capacitor of at least 0.1 µF of capacitance between  $V_{DD}$  and  $V_{SS}$  to GND. The TMUX9616 EVM uses a 0.1  $\mu F$  in parallel with a 1  $\mu F$  capacitor. It is recommended to place the lowest value capacitor as close to the pin as possible. Ensure that the capacitor voltage rating is sufficient for the supply voltage.

- Keep the input lines as short as possible.

- Use a solid ground plane to help distribute heat and reduce electromagnetic interference (EMI) noise pickup.

- Do not run sensitive analog traces in parallel with digital traces. Avoid crossing digital and analog traces if possible, and only make perpendicular crossings when necessary.

#### 9.4.2 Layout Example

図 9-14. TMUX9616 Layout Example

資料に関するフィードバック(ご意見やお問い合わせ)を送信

25

English Data Sheet: SCDS436

# 10 Device and Documentation Support

# **10.1 Documentation Support**

#### 10.1.1 Related Documentation

For related documentation, see the following:

Texas Instruments, Using Latch Up Immune Multiplexers to Help Improve System Reliability

#### 10.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

# 10.3 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。 TI の使用条件を参照してください。

#### 10.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 10.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 10.6 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

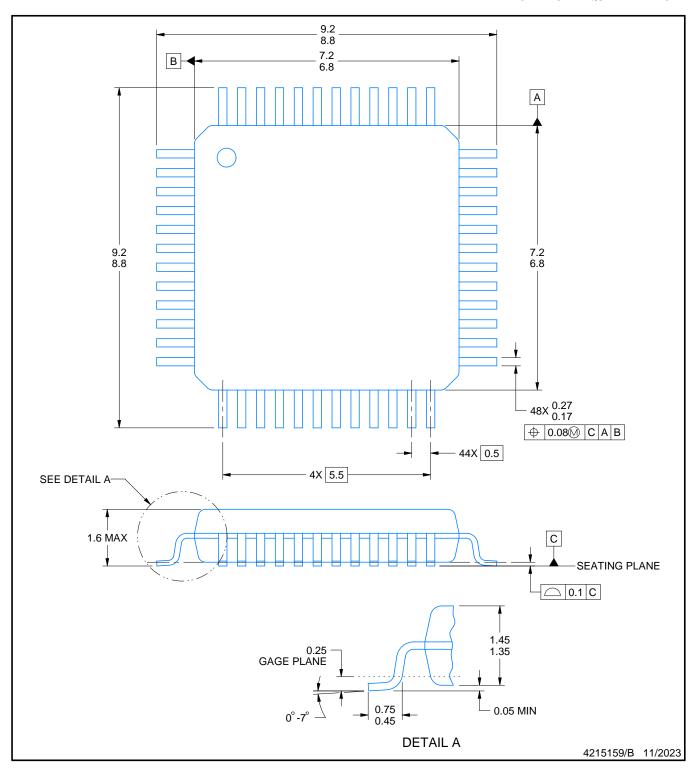

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

www.ti.com 1-Oct-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TMUX9616PTR      | ACTIVE | LQFP         | PT                 | 48   | 1000           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | TM9616                  | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

LOW PROFILE QUAD FLATPACK

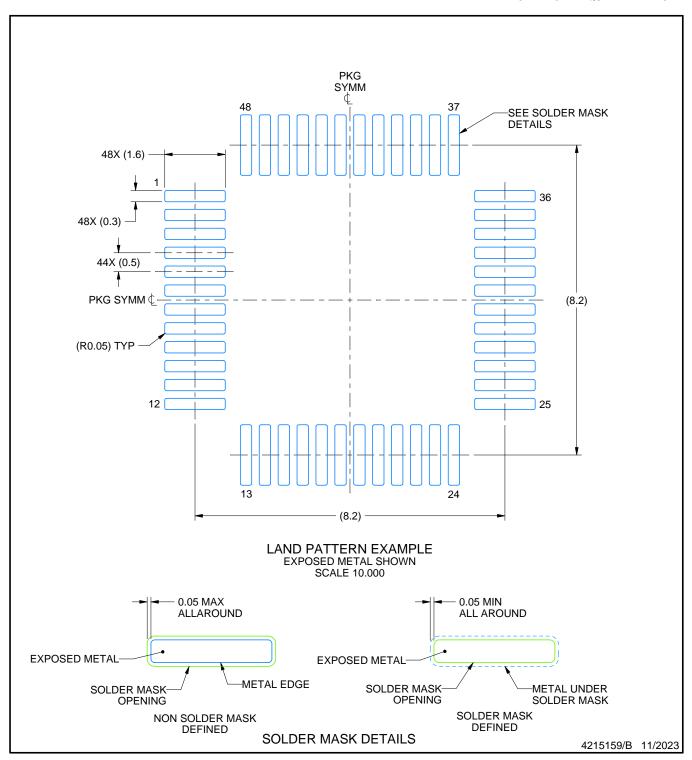

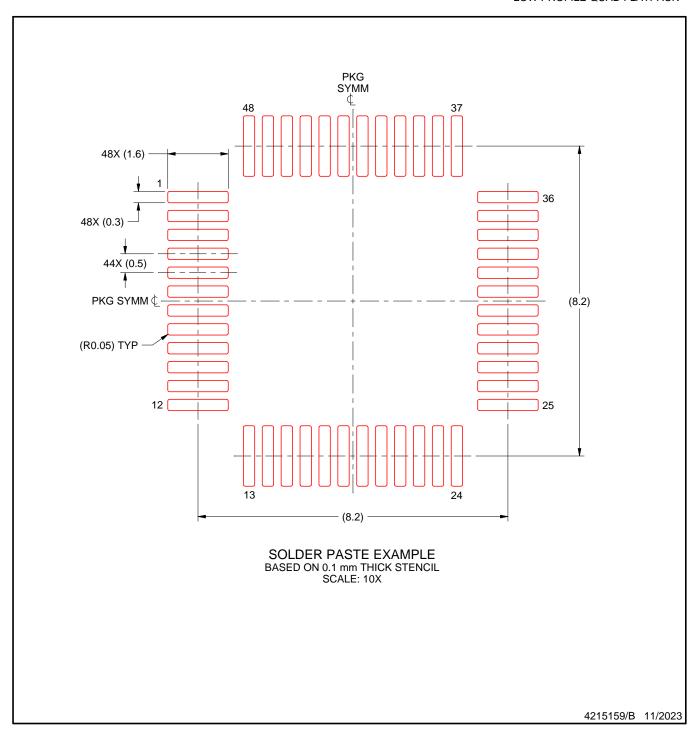

### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

Reference JEDEC registration MS-026.

This may also be a thermally enhanced plastic package with leads conected to the die pads.

LOW PROFILE QUAD FLATPACK

NOTES: (continued)

- 5. Publication IPC-7351 may have alternate designs.