# PCIExpressサーバ用 2スロット・ホットプラグ・コントローラ

# 特長

- PCIExpress<sup>TM</sup>ホットプラグ要求に適合

- プログラミング可能な12V電流制限

- 突入電流制限

- SMBusコントロールモード

- ダイレクト・コントロール・モード

- VAUX用ホットプラグFET内蔵

- 汎用入力(GPIA/B)

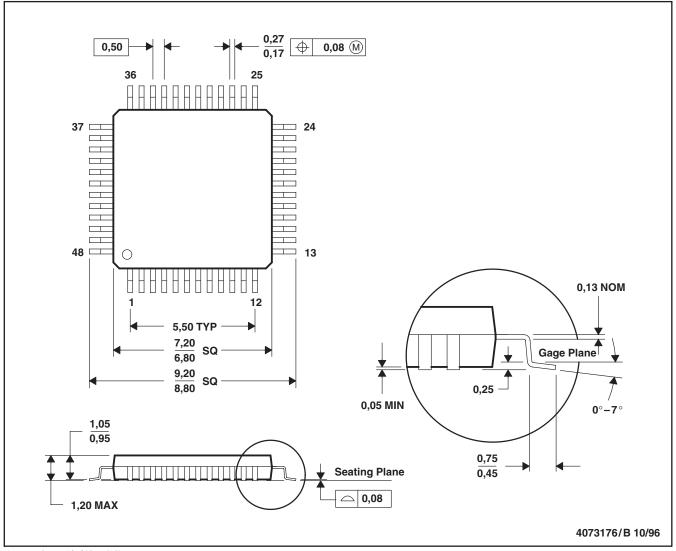

- 48ピンTQFPパッケージ

- 機能追加されたMIC2592Bとのピン互換品

## 概要

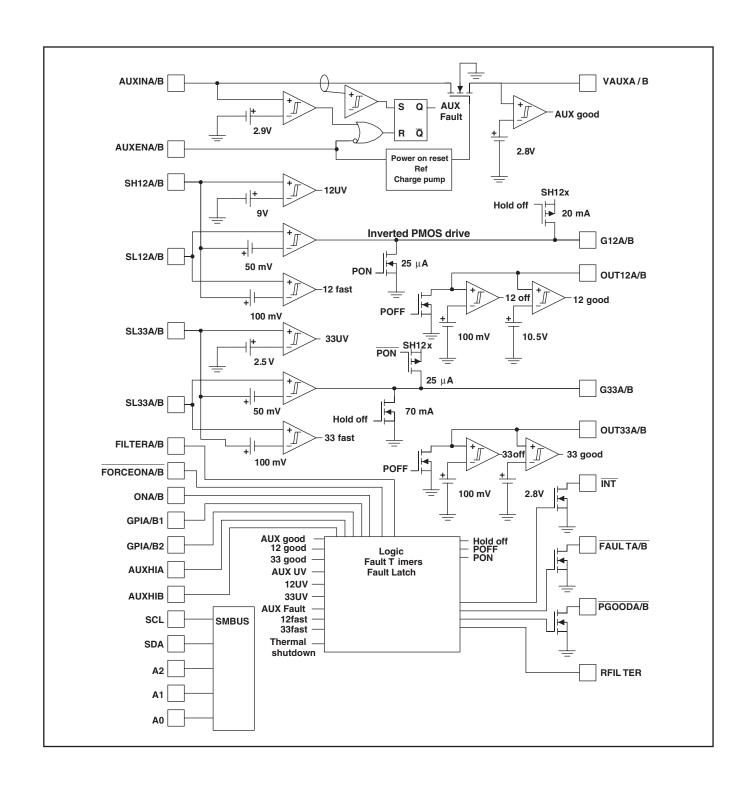

TPS2363は、SMBusによる制御機能と監視機能を備えた2スロットPCIExpressホットプラグ・コントローラです。センス抵抗を持つことで、3.3V電源および12V電源に対する電流制限をプログラムできます。

TPS2363は、AUX(補助電源)に対してのFETスイッチを内蔵し、各スロットのメイン電源 (3.3Vおよび12V) に対しては、2つの外部FETスイッチで動作します。

TPS2363PFBは48ピンのTQFPパッケージにて供給されます。

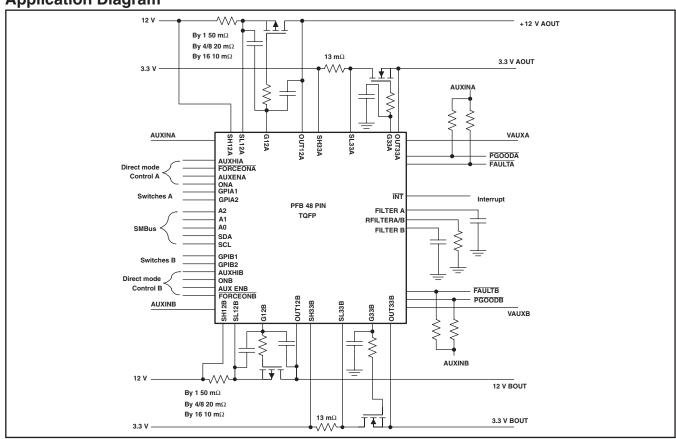

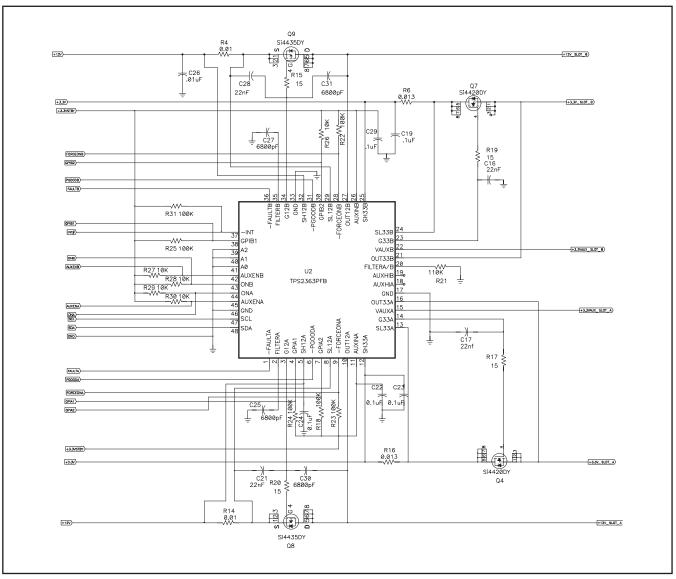

## **Application Diagram**

PCIExpressは、テキサス・インスツルメンツの登録商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

Tlおよび日本Tlは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

## アプリケーション図

TPS2363は、取り外しの前にモジュールを放電するためのブリード・ダウン回路を備えています。電圧がコンパレータの下限スレッシュホールドより低い場合、スロットPWROFFがセットされ、モジュールを安全に取り外せることを示します。この機能はSMBusにより利用できます。

ゲート・キャパシタを使用して立ち上がり時間を設定することにより、スロットのソフト・オンが可能になり、電源グリッチを防止できます。

TPS2363はダイレクト・モードで動作できますが、この場合はSMBusが使用されません。

A/Dコンバータを持たない48ピン・パッケージのTPS2363PFBは、他社製品を直接置き換えることが可能ですが、いくつかの改善も加えられています。

## 他製品との比較

ファンクション・レジスタは、新しい機能を実現するために 追加されたTPS2363独自の機能です。

- VAUXA/Bの電流値を800mAまでプログラム可能。従来のアドイン・モジュールの中には、PCI規格の許容値より低い電流を維持出来ないものもありました。

- AUX電流制限の精度が向上。MIC2592Bが375mA~1.35Aであるのに対し、TPS2363は400mA~750mAです。

- 各スロットにデバウンス機能を備えた2つの入力。通常、 各スロットにはスイッチとアテンション・ボタンが実装されます。

- SMBusによる電流制限をオフにする機能。アプリケーションによっては電流制限よりもサーキット・ブレーカ動作の方が望ましい場合があります。

- メイン電源に依存しないVAUX電源。

- SMBusによる電源オフ・スロット情報。これにより、モジュールの全電圧が100mV未満であることを確認でき、モジュールを安全に取り外すことができます。

- 障害(フォルト)タイマをより厳密に制御可能。

- エッジトリガではなく、レベル検出型のAUXENA/B。

## 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## オーダー情報

| T <sub>A</sub> | FAST TRIP | AUXHI PINS 18 and 19 | PINS   | PACKAGED DEVICES(1) |  |

|----------------|-----------|----------------------|--------|---------------------|--|

| -40°C to 85°C  | 100 mV    | Yes                  | 48 PFB | TPS2363PFB          |  |

(1) 部品番号の末尾がR以外の場合、部品はトレイで出荷されます。部品番号の末尾がRの場合、テープ/リールで出荷されます。

## 絶対最大定格

動作温度範囲内(特に記述のない限り)(1)

| PARAMETER                            | VALUE      | UNIT |  |

|--------------------------------------|------------|------|--|

| Supply 12 V, SH12A/B                 | 0 to 15    |      |  |

| Supply 3.3 V & SH33A/B, AUXINA/B     | 0 to 5     | V    |  |

| Logic input/output                   | -0.5 to 5  | V    |  |

| VAUXA/B output voltage               | 0 to 5     |      |  |

| VAUXA/B output current               | 1.4        | A    |  |

| FAULTA/B, PGOODA/B, INT sink current | 10         | mΛ   |  |

| SDA sink current                     | 10         | · mA |  |

| Operating junction temperature       | -40 to 125 |      |  |

| Storage temperature                  | -65 to 150 | °C   |  |

| LEAD temperature soldering           | 260        |      |  |

<sup>(1)</sup> 絶対最大定格以上のストレスは、致命的なダメージを製品に与えることがあります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を越える状態での本製品の機能動作は含まれていません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

## 静電放電(ESD)保護

|     | TEST METHOD          | MIN | UNIT |

|-----|----------------------|-----|------|

| HBM | Human body model     | 2   | 14)/ |

| CDM | Charged device model | 1   | kV   |

## 定格消費電力

| PACKAGE      | T <sub>A</sub> ≤ 25°C POWER<br>RATING | DERATING<br>FACTOR ABOVE<br>T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C POWER RATING | T <sub>A</sub> = 85°C POWER RATING |

|--------------|---------------------------------------|---------------------------------------------------|------------------------------------|------------------------------------|

| PFB(48 TQFP) | 1025.6 mW                             | 10.256 mW/°C                                      | 564.1mW                            | 410.3 mW                           |

## 推奨動作条件

動作温度範囲内(特に記述のない限り)

|                | PARAMETER                                            | MIN  | NOM | MAX  | UNIT |

|----------------|------------------------------------------------------|------|-----|------|------|

|                | 12 V input voltage range, SH12A/B                    | 10.8 | 12  | 13.2 | V    |

|                | AUX and 3.3 V input voltage range, SH33A/B, AUXINA/B | 3.0  | 3.3 | 3.6  | V    |

|                | VAUXA/B output current, PCI standard                 |      |     | 375  | mA   |

| TJ             | Operating junction temperature range                 | -40  |     | 125  | °C   |

| T <sub>A</sub> | Operating ambient temperature range                  | -40  |     | 85   | C    |

## 電気的特性

特に指定のない限り、電源電圧:SH33A/B および AUXINA/B = 3.0V $\sim$ 3.6V、SH12A/B = 10.8V $\sim$ 13.2V、 $T_A=-40^{\circ}C\sim$ 85 $^{\circ}C$ 、RFILTER = オープン、すべての出力は無負荷です。 $^{(1)}$

| PARAMETER                       |            | TEST CONDITIONS                                                | MIN         | TYP  | MAX     | UNIT |

|---------------------------------|------------|----------------------------------------------------------------|-------------|------|---------|------|

| PCIExpress 12-V Supply Gate Con | troller    |                                                                |             |      |         |      |

| 12-V voltage, SH12A/B           |            |                                                                | 10.8        |      | 13.2    | V    |

|                                 |            | ONA/B = high, (No load)                                        |             |      | 1       | A    |

| 12-V supply current, SH         | 12A/B, per | ONA/B = low, disabled main supply                              |             |      | 0.5     | mA   |

| slot                            |            | Leakage, VAUX = 3.3 V , SH33A/B and SH12A/B = 0 V              |             |      | 1       | μΑ   |

| SL12A/B input current           |            |                                                                |             | 0.35 |         | ,    |

| 12-V gate voltage, G12A         | /B         | ONA/B = high                                                   | 0           |      | 1       | V    |

| 12-V gate sink current          |            | ONA/B = high, G12A/B = SH12A/B                                 | 15          | 25   | 35      | μΑ   |

| 12-V gate source current        | t          | ONA/B = High, G12A/B = SH12A/B-2.5 V, during a fault condition | 20          |      |         | mA   |

| Current limit threshold         |            | Current limit                                                  | 45          | 50   | 55      | m\/  |

| Fast trip threshold             |            | Fast trip                                                      | 90          | 100  | 110     | mV   |

| 111/4 0                         |            | Increasing                                                     | 8           | 9    | 10      | V    |

| UVLO                            |            | Hysteresis                                                     |             | 180  |         | mV   |

| PGOOD                           |            | Increasing                                                     | 10.2        | 10.5 | 10.8    | V    |

| PGOOD                           |            | Hysteresis                                                     |             | 50   |         | mV   |

| Bleed down resistance           |            | ONA/B = LOW, OUT12A/B = 6.0 V                                  |             | 1600 |         | Ω    |

| low comparator threshold        | d          |                                                                | 0.075       | 0.1  | 0.15    | V    |

| PCIExpress 3.3-V Gate Control   |            |                                                                |             |      |         |      |

| 3.3-V voltage, SH33A/B          |            | PCIExpress limits, not device limits                           | 3.0         |      | 3.6     | V    |

|                                 |            | ONA/B = high                                                   |             |      | 0.2     | A    |

| 3.3-V supply current, SH        | 33A/B, per | ONA/B = low, Disabled main supply                              |             |      | 0.2     | mA   |

| slot                            |            | Leakage, AUXINA/B = 3.3 V,<br>SH33A/B and SH12A/B = 0 V        |             |      | 1       | μА   |

| SL33A/B input current           |            |                                                                |             | 0.35 |         |      |

| 3.3-V gate voltage, G33A        | A/B        | ONA/B = high, capacitive load only                             | SH12A/B - 1 |      | SH12A/B | V    |

| 3.3-V gate sink current         |            | ONA/B = high, G33A/B = 2.5 V, on a fault condition.            | 50          |      |         | mA   |

| +3.3 volt gate source cur       | rrent      | ONA/B = high, G33A/B = SH12A/B                                 | 15          | 25   | 35      | μΑ   |

| Current limit threshold         |            | Current limit                                                  | 45          | 50   | 55      | m\/  |

| Fast trip threshold             |            | Fast trip                                                      | 90          | 100  | 110     | mV   |

| 10/10                           |            | Increasing                                                     | 2.2         | 2.5  | 2.75    | V    |

| UVLO                            |            | Hysteresis                                                     |             | 180  |         | mV   |

| D0005                           |            | Increasing                                                     | 2.7         | 2.8  | 2.9     | V    |

| PGOOD                           |            | Hysteresis                                                     |             | 50   |         | mV   |

| Bleed down resistance           |            | ONA/B = low, OUT33A/B = 1.65 V                                 |             | 150  |         | Ω    |

| low comparator threshold        | b          |                                                                | 0.075       | 0.1  | 0.15    | V    |

<sup>(1) &</sup>quot;ハイ"になっているアドレスと"ロー"になっているアドレスがある場合、電流は絶対値で示しています。

## 電気的特性

特に指定のない限り、電源電圧:SH33A/B および AUXINA/B = 3.0V $\sim$ 3.6V、SH12A/B = 10.8V $\sim$ 13.2V、 T<sub>A</sub> =  $-40^{\circ}$ C $\sim$ 85 $^{\circ}$ C、RFILTER = オープン、すべての出力は無負荷です。

|         | PARAMETER                           | TEST CONDITIONS                                                                                         | MIN   | TYP  | MAX   | UNIT |

|---------|-------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| PCIExpi | ress AUX                            |                                                                                                         |       |      |       |      |

|         | AUXINA/B voltage                    |                                                                                                         | 3.0   |      | 3.6   | V    |

|         |                                     | AUXENA/B = high, (no load), ONA/B = high                                                                |       |      | 1     |      |

|         | AUXINA/B supply current             | AUXENA/B = high, (no load), ONA/B = low                                                                 |       |      | 1     | mA   |

|         |                                     | AUXENA/B = low, ONA/B = low                                                                             |       |      | 1     |      |

|         | VAUXA/B on resistance               | AUXENA/B = high, I(VAUXA/B) = 375 mA                                                                    |       |      | 400   | mΩ   |

|         |                                     | Default current limit, VAUXA/B = 1 V                                                                    | 400   |      | 750   | mA   |

|         | Current Ilmit                       | VAUXA/B set to high current limit<br>(SMBus) or (pins 18 & 19),<br>VAUXA/B = 1 V                        | 0.8   |      | 1.4   | А    |

|         | 10/10                               | Increasing                                                                                              | 2.8   | 2.9  | 3.0   | V    |

|         | UVLO                                | Hysteresis                                                                                              |       | 50   |       | mV   |

|         | PGOOD                               | Increasing                                                                                              | 2.7   | 2.8  | 2.9   | V    |

|         | PGOOD                               | Hysteresis                                                                                              |       | 50   |       | mV   |

|         | bleed down resistance               | AUXENA/B = low, VAUXA/B = 1.65                                                                          |       | 400  |       | Ω    |

|         | low comparator threshold            |                                                                                                         | 0.075 | 0.1  | 0.15  | V    |

|         | Off-state output offset voltage (2) | AUXENA/B = low, T <sub>J</sub> = 125°C                                                                  |       |      | 50    | mV   |

| Timing  |                                     |                                                                                                         |       | •    | -     |      |

|         | V <sub>FILTER</sub> (CFILTERA/B)    | Threshold voltage                                                                                       | 1.2   | 1.25 | 1.3   | V    |

|         | I <sub>FILTER</sub> (CFILTERA/B)    | Filter charging current, when the voltage across the sense resistor is greater than the threshold limit | 2.1   | 2.5  | 3.1   | μΑ   |

|         |                                     | Filter discharging current, 1.5 V                                                                       | 1     |      |       | mA   |

|         | R <sub>FILTER</sub>                 |                                                                                                         | 108.8 | 110  | 111.2 | kΩ   |

|         | Scaling factor SF                   | The voltage across the sense resistor is greater than the threshold limit                               | 4.5   | 5    | 5.5   | V    |

|         | Fast trip                           | (SH12A/B - SL12A/B =110 mV) or<br>(SH33A/B - SL33A/B =110 mV) (2)                                       |       | 200  | 500   |      |

|         | PGOOD response to output UV         | 12 V at 9.2 V, 3.3 V and VAUXA/B at 2.5 V <sup>(2)</sup>                                                |       | 100  | 200   | ns   |

|         | POR, power on reset                 | After AUXINA/B becomes valid <sup>(2)</sup>                                                             |       | 250  |       | μs   |

|         | GPIA/Bx, debounce                   | Designed for switch contact closure <sup>(2)</sup>                                                      |       | 5    |       | ms   |

<sup>(2)</sup> 設計とエンジニアリング・テストによって確認されていますが、出荷時の製品テストは行っていません。

## 電気的特性

特に指定のない限り、電源電圧:SH33A/B および AUXINA/B = 3.0V $\sim$ 3.6V、SH12A/B = 10.8V $\sim$ 13.2V、 $T_A = -40^{\circ}C \sim 85^{\circ}C$ 、RFILTER = オープン、すべての出力は無負荷です。

|                       | PARAMETER                                                                       | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |  |

|-----------------------|---------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|------|--|

| SCL, SDA              | A Address, GPI, and enable logic                                                |                                    |     | ·   | ·   |      |  |

| V <sub>IL</sub>       | Input Low voltage (SDA, SCL, A0, A1, A2, ONA/B, FORCEONA/B, AUXENA/B, GPIA/Bx)  |                                    |     |     | 0.8 | V    |  |

| V <sub>IH</sub>       | Input High voltage (SDA, SCL, A0, A1, A2, ONA/B, FORCEONA/B, AUXENA/B, GPIA/Bx) |                                    | 2.0 |     |     | V    |  |

| I <sub>IL</sub>       | SCL, ONA/B, AUXENA/B, FORCEONA/B, input leakage current                         | V <sub>PIN</sub> = AUXINA/B or 0 V |     |     | ±5  | μΑ   |  |

|                       | Address pull up to AUXINA/B (A0 - A2)                                           |                                    |     | 40  |     | kΩ   |  |

|                       | GPIA/Bx input pull down                                                         |                                    |     | 100 |     |      |  |

| V <sub>OL</sub>       | Low-level output voltage FAULTA/B, PGOODA/B, INT, SDA                           | IL = 4 mA                          |     | 0.2 | 0.4 | V    |  |

| I <sub>LKG(off)</sub> | FAULTA/B, PGOODA/B, INT, SDA off-state leakage current                          | V <sub>PIN</sub> = AUXINA/B        |     |     | ±5  | μΑ   |  |

| SMBus T               | iming                                                                           |                                    |     |     |     |      |  |

|                       | SCL (Clock) period                                                              |                                    | 2.5 |     |     | μs   |  |

|                       | Data in setup to SCL high                                                       |                                    | 100 |     |     |      |  |

|                       | Data out stable after SCL low                                                   |                                    | 300 |     |     | 200  |  |

|                       | Data low setup time to SCL low                                                  |                                    | 100 |     |     | ns   |  |

|                       | Data high hold time to SCL high                                                 |                                    | 100 |     |     |      |  |

| Thermal               | Shutdown                                                                        |                                    |     |     |     |      |  |

|                       |                                                                                 | TSHUT1, rising                     |     | 140 |     |      |  |

|                       | Thermal Shutdown                                                                | Hysteresis                         |     | 10  |     | °C   |  |

|                       |                                                                                 | TSHUT2, rising                     |     | 160 |     |      |  |

# デバイス情報

# 端子機能

|            | TERMINAL     |       |     |                                                                                                                                                                                                                                                           |

|------------|--------------|-------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       |              |       | 1/0 | DESCRIPTION                                                                                                                                                                                                                                               |

| TPS2363    | MIC2592B     | NO.   |     | 2-2001 11011                                                                                                                                                                                                                                              |

| FAULTA/B   | /FAULTA/B    | 1/36  | 0   | スロットの障害 (フォルト) 出力です (フィルタ適用)。アクティブ・ローです。 FAULTA/B は、AUXまたはメイン電源で、過電流、低電圧、或いは過熱保護が発生したことを示します。AUXで発生した障害 (フォルト) をリセットするには、AUXENA/Bをディスエーブルにする必要があります。メイン電源での障害(フォルト)をリセットするには、ONA/Bをディスエーブルにする必要があります。このオープン・ドレイン出力は、100kΩの抵抗を使用してAUXINA/Bにプルアップする必要があります。 |

| FILTERA/B  | FILTERA/B    | 2/35  | I   | この端子からグランドに外部キャパシタが接続されます。これを使用して、スロットA/Bメイン電源がオフになるまで障害(フォルト)イベント(MAINまたはAUX)を継続できる時間を設定します。キャパシタの選定については、「障害(フォルト)タイマ」の項で詳しく説明します。                                                                                                                      |

| G12A/B     | 12VGATEA/B   | 3/34  | 0   | 12VのPチャネルFETのゲート駆動ピンです。このピンとOUT12A/Bピンの間にキャパシタを接続することにより、突入電流を制限するためのスルーレートを設定します。ゲート・キャパシタの選定については、「突入電流」の項を参照してください。                                                                                                                                    |

| GPIA/B1    | GPI_A0/B0    | 4/38  | I   | メカニカル・スイッチへの直接接続用にフィルタされる汎用入力です。この入力の状態は、SMBusの共通ステータス・レジスタを使用して読み取ることができます。使用しない場合は、このピンをグランドに接続します。これらのピンはスイッチ (挿入されるモジュール検出) またはアテンション・ボタンに使用できます。内部に100kΩのプルダウン抵抗があります。                                                                               |

| SH12A/B    | 12VINA/B     | 5/32  | I   | 12V電源入力で、電流センス抵抗の高電位側です。これらのピンおよび関連するセンス抵抗を配置する際には、注意が必要です。センス抵抗の配置については、「レイアウトに関する考慮事項」を参照してください。このピンは、0.1μFのバイパス・キャパシタを経由してグランドに接続する必要があります。                                                                                                            |

| PGOODA/B   | /PWRGDA/B    | 6/31  | 0   | スロットの全電圧がパワー・グッドであることを示す、アクティブ・ローの出力です。この<br>オープン・ドレイン出力は、100kΩの抵抗を使用してAUXINA/Bにプルアップする必要があ<br>ります。                                                                                                                                                       |

| GPIA/B2    | NC           | 7/30  | ı   | メカニカル・スイッチへの直接接続用にフィルタされる汎用入力です。この入力の状態は、SMBusの共通ステータス・レジスタを使用して読み取ることができます。これらのピンはスイッチ (挿入されるモジュール検出) またはアテンション・ボタンに使用できます。これらのGPIはTPS2363でのみ使用できます。使用しない場合は、未接続(NC)の状態にしてください。                                                                          |

| SL12A/B    | 12VSENSEA/B  | 8/29  | 1   | 12V電源入力に接続する、センス抵抗の低電位側です。センス抵抗にかかる電圧が電流制限スレッシュホールドを超えた場合、スロットは過電流状態になります。センス抵抗の配線には、ケルビン接続を使用します。「レイアウトに関する考慮事項」の項を参照してください。                                                                                                                             |

| FORCEONA/B | /FORCE_ONA/B | 9/28  | 1   | アクティブ・ローです。診断が必要な障害がある場合でも、強制的にチャネルをオンにします。これは、SMBusのFORCEON INHIBビットを使用してディスエーブルにすることができます。サーマル・シャットダウンはFORCEONA/Bよりも優先されます。SMBusのSTATA/Bレジスタが、スロットA/Bの状態を示します。                                                                                          |

| OUT12A/B   | 12VOUTA/B    | 10/27 | I/O | スロットA/B電圧がパワー・グッドかどうかを監視するために使用する、 $12V$ チャネル出力ピンです。メイン電源をオフにすると、 $1.2k\Omega$ のブリード・ダウン回路が接続されます。すべての電圧が $100mV$ を下回ったときに、スロットの電源オフ情報をSMBusから読み取ることができます。                                                                                                |

| AUXINA/B   | VSTBYA/B     | 11/26 | I   | PCIExpressアプリケーション、SMBus、内部ロジックに使用される3.3V補助電源です。AUX<br>電源がない場合、AUXINA/Bを3.3V電源に接続する必要があります。このピンは、0.1μF<br>のバイパス・キャパシタを経由してグランドに接続する必要があります。                                                                                                               |

| SH33A/B    | 3VINA/B      | 12/25 | I   | 3.3V入力電源です。センス抵抗の高電位側です。これらのピンおよび関連するセンス抵抗を配置する際には注意が必要です。センス抵抗の配置については、「レイアウトに関する考慮事項」を参照してください。このピンは、0.1µFのバイパス・キャパシタを経由してグランドに接続する必要があります。                                                                                                             |

| SL33A/B    | 3VSENSEA/B   | 13/24 | I   | 3.3V電源入力に接続する、センス抵抗の低電位側です。センス抵抗にかかる電圧が電流制限スレッシュホールドを超えた場合、スロットは過電流状態になります。センス抵抗の配線には、ケルビン接続を使用します。「レイアウトに関する考慮事項」の項を参照してください。                                                                                                                            |

| G33A/B     | 3VGATEA/B    | 14/23 | 0   | 3.3VのNチャネルFETのゲート駆動ピンです。このピンとグランド間にキャパシタを接続することにより、突入電流を制限するためのスルーレートを設定します。キャバシタの選定については、「突入電流」の項で説明しています。                                                                                                                                               |

| VAUXA/B    | VAUXA/B      | 15/22 | 0   | スロットA/Bに対するVAUX出力。                                                                                                                                                                                                                                        |

## 端子機能

|             | TERMINAL      |            |     |                                                                                                                                                                                                                  |

|-------------|---------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        |               |            | I/O | DESCRIPTION                                                                                                                                                                                                      |

| TPS2363     | MIC2592B      | NO.        |     |                                                                                                                                                                                                                  |

| OUT33A/B    | 3VOUTA/B      | 16/21      | I/O | スロットA/B電圧がパワー・グッドかどうかを監視するために使用する、 $3.3$ Vチャネル出力です。メイン電源をオフにすると、 $1.2$ k $\Omega$ のブルダウン、ブリード・ダウン回路が接続されます。すべての電圧が $100$ mVを下回ったときに、スロットの電源オフ情報をSMBusから読み取ることができます。                                              |

| GND         | GND           | 17, 46, 33 |     | グランド。                                                                                                                                                                                                            |

| AUXHIA/B    | N/C           | 18, 19     | I   | AUXHIA/Bを使用して、高いAUX電流 (800mA) を選択します。これらのピンを10kΩの最大抵抗によりAUXINA/Bにプルアップすることで、800mAを選択します。内部に40kΩのプルダウン抵抗があるため、VAUXA/Bがデフォルトの400mAの場合、NCまたはグランド接続とします。AUX高電流設定は、TPS2363でのみ使用できます。                                  |

| RFILTER A&B | RFILTER [A&B] | 20         | I   | このピンとグランドの間に110kΩの抵抗を接続することにより、障害(フォルト)タイマの<br>精度が向上します。詳細については、「障害(フォルト)タイマ」の項を参照してください。                                                                                                                        |

| ĪNT         | /INT          | 37         | 0   | INT はオープン・ドレイン出力です。障害 (フォルト) が発生するとアクティブ・ローになります。SMBus割り込みマスクにより、出力がディスエーブルになります。 INT をクリアするには、ステータス・レジスタをリセットします。これについては、SMBusのプログラミングに関するセクションで説明します。このピンは、バスの末端で10kΩの外部抵抗を使用して3.3VまたはAUXINA/Bにプルアップする必要があります。 |

| A0, A1, A2  | A0, A1, A2    | 41/40/39   | I   | SMBusアドレス選択入力です。これらの入力は内部で40kQの抵抗を使用して3.3VまたはAUXINA/Bにプルアップされます。ロジック1をプログラムする場合はこのピンをオープンのままにし、ロジック0をプログラムする場合はグランドに接続します。コントローラは初期化時にのみアドレス・ビットを読み取ります。                                                         |

| AUXENA/B    | AUXENA/B      | 45/42      | I   | このアクティブ・ハイ信号により、VAUXスロット電圧がオンになります。この信号を"ロー"にすると、VAUX電圧により発生していたスロットの障害(フォルト)がクリアされます。SMBusインタフェースを使用して制御を行う場合は、これらのピンをグランドに接続します。                                                                               |

| ONA/B       | ONA/B         | 44/43      | I   | このアクティブ・ハイ信号により、メイン・スロット電圧がオンになります。この信号を<br>"ロー"にすると、メイン電圧により発生していたスロットの障害(フォルト)がクリアさ<br>れます。SMBusインタフェースを使用して制御を行う場合は、これらのピンをグランドに<br>接続します。                                                                    |

| SCL         | SCL           | 47         | I   | SMBusクロック入力です。このピンは、バスの末端で10kΩの外部抵抗を使用して3.3VまたはAUXINにプルアップする必要があります。                                                                                                                                             |

| SDA         | SDA           | 48         | I/O | SMBusのデータ入出力およびアドレス入力です。このピンは、バスの末端で10kΩの外部<br>抵抗を使用して3.3VまたはAUXINにプルアップする必要があります。                                                                                                                               |

## 参考情報

## PCIExpress CEM (Card Electromechanical Specification) 規格

#### 雷源レールについての要求

| POWER RAIL        | x1 CONNECTOR  | x4/x8 CONNECTOR | x16 CONNECTOR     |

|-------------------|---------------|-----------------|-------------------|

|                   | 3.0           | 3 V             |                   |

| Voltage tolerance | ±9% (max)     | ±9% (max)       | ±9% (max)         |

| Supply current    | 3.0 A (max)   | 3.0 A (max)     | 3.0 A (max)       |

| Capacitive load   | 1000 μF (max) | 1000 μF (max)   | 1000 μF (max)     |

|                   | 12            | 2 V             |                   |

| Voltage tolerance | ±8%           | ±8%             | ±8%               |

| Supply current    | 0.5 A         | 2.1 A (max)     | 4.4 / 5.5 A (max) |

| Capacitive load   | 300 μF (max)  | 1000 μF (max)   | 2000 μF (max)     |

|                   | 3.3 \         | AUX             |                   |

| Voltage tolerance | ±9% (max)     | ±9% (max)       | ±9% (max)         |

| Supply current    | 375 mA (max)  | 375 mA (max)    | 375 mA (max)      |

| Wakeup enabled    | 20 mA (max)   | 20 mA (max)     | 20 mA (max)       |

|                   | Non-wake      | up enabled      |                   |

| Capacitive load   | 150 μF (max)  | 150 μF (max)    | 150 μF (max)      |

## アドイン·カードの消費電力 (1)(2)(3)(4)

|                   | х                                               | (1 | x4/x8      | x16                                  |  |

|-------------------|-------------------------------------------------|----|------------|--------------------------------------|--|

| Standard height   | 10 W <sup>1</sup> (max) 25 W <sup>1</sup> (max) |    | 25 W (max) | 25 W <sup>2</sup> (max) 75 W (max) ( |  |

| Low profile card3 | 10 W (max)                                      |    | 10 W (max) | 25 W (max)                           |  |

- (1) デスクトップ・アプリケーション向けの標準高さx1アドイン・カードは、長さがハーフ・レングス・アドイン・カード以下、最大消費電力が10Wに限定されています。サーバI/Oアプリケーション向けの標準高さx1アドイン・カードは、最大消費電力が25W、長さが177.80mm(7.0インチ)以上で、フルレングス・アドイン・カードの長さ以下である必要があります。アドイン・カードのサイズの定義については、『PCIExpress CEM』の表6-1を参照してください。初期電力投入時には、高消費電力デバイスとして構成されるまではサーバI/Oアドイン・カードの消費電力が10Wを超えないようにします。ただし高消費電力デバイスとして設定した場合には、消費電力が25Wを超えないようにします。電力設定のメカニズムについては、『PCI Express Base Specification』の第6章を参照してください。

- (2) サーバI/Oアプリケーション向けの標準高さx16アドイン・カードでは、消費電力が25Wに制限されます。グラフィックス・アプリケーション向けの標準高さx16アドイン・カードでは、初期電力投入時に高消費電力デバイスとして構成されるまでは消費電力が25Wを超えないようにします。ただし高消費電力デバイスとして設定した場合には、消費電力が60/75Wを超えないようにします。電力設定のメカニズムについては、『PCI Express Base Specification』の第6章を参照してください。

- (3) ロー・プロファイル・アドイン・カードは、長さをハーフ・レングス・アドイン・カード以下にし、「アドイン・カードの消費電力」の表に示した消費電力を超えないようにします。

- (4) x16グラフィックス・カードの消費電力は60/75Wに制限されます。最大消費電力60/75Wは、12Vレールと3.3Vレールを組み合わせることにより実現できますが、各レールの引き込み電力は「電源レールの要件」の表で示されている要件により制限されます。また、2つのレールの引き込み電力の合計値が60/75Wを超えないようにしてください。

- (5) 150W、x16グラフィックス・カード150W ATXの場合、追加コネクタが必要になります。障害が発生したときにコネクタが損傷しないように、各コネクタで75W以下になるように電流を制限する必要があります。追加ケーブル用の12Vホット・スワップ・コントローラには、TPS2490をお勧めします。

# アプリケーション情報 パワー・オン・リセット

AUXINA/Bはロジック電圧電源です。AUXINA/B電圧が低電圧ロックアウト (UVLO)電圧を超えると、TPS2363がリセットを開始します。リセットが行われると、すべてのレジスタがクリアされ、すべてのSlotA/B電圧がオフに保持されます。AUXINA/Bの電圧がUVLO電圧を超えてから250ms以内に、初期化が完了します。AUXINA/Bで電源グリッチが生じると、TPS2363がリセットされます。リセット後は、ONA/B入力がアクティブの場合でも、メイン出力がオフになります。FAULTA/B出力をクリアすると、TPS2363の電源が投入されます。

TPS2363のAUXENA/B入力は、電源投入時のレース状態を回避するためのレベル検出です。AUXENA/Bがアクティブの場合、TPS2363の電源投入時にVAUXA/Bがオンになり、FAULTA/B出力がクリアされます。

FORCEONA/Bがアクティブの場合、リセット後にVAUXA/B およびメイン・スロット電源出力がアクティブになります。

最初にAUXINA/Bの電源を投入した後で、12Vおよび3.3Vの電源を投入します。AUXINA/Bと3.3Vの電源が同じである場合、同時に電源投入できます。

システムでVAUXA/Bを使用しない場合は、AUXINA/Bを基板の3.3V電源プレーンに接続する必要があります。

## 動作モード

TPS2363は、2つの制御モードのどちらかで動作できます。 ダイレクト・モードではONA/BおよびAUXENA/Bを使用して スロット電源を制御し、SMBusモードではSMBusの制御レジ スタを使用します。ダイレクト・モードでもSMBusを使用して 状態を監視できますが、電源はONA/BおよびAUXENA/Bを使 用して制御します。ダイレクトモードの場合に、SMBusのコントロール・レジスタ・ビットに書き込みを行うことはできません。 書き込みを行うとTPS2363はSMBusモードに切り替わります。

## モードとピン接続

| MODE                                     | SIGNAL     | CONNECTION                  |  |

|------------------------------------------|------------|-----------------------------|--|

| SMBus                                    | AUXENA/B   | CNID                        |  |

|                                          | ONA/B      | GND                         |  |

|                                          | FORCEONA/B | 100 kΩ pull up to VAUXINA/B |  |

| DIRECT (if the SMBus is not used to read | A0         | GND                         |  |

| status)                                  | A1         |                             |  |

|                                          | A2         |                             |  |

|                                          | SCL        | 10 kΩ pull up to VAUXINA/B  |  |

|                                          | SDA        |                             |  |

- SMBusおよびINTを複数のデバイスに接続する場合、バスの末端で終端し、アプリケーションに応じて10kΩ抵抗を使用して 3.3VまたはAUXINにプルアップする必要があります。

- SMBusおよびINTが短いポイント・ツー・ポイント接続である場合、100kΩ抵抗による3.3VまたはAUXINへのプルアップを使用できます。

## システムの動作

TPS2363ホットプラグ·コントローラを使用することで、動 作中のシステムでスロットの電源がオフの場合、PCIExpress カードの挿入と取り外しが可能になります。モジュールを挿入 するとスイッチが投入され、シーケンスが開始されます。スイッ チの入力にはGPIピンを使用できます。内部FETを使用して 3.3VのVAUXA/B電源をオンにすることで、VAUXA/Bがイネー ブルになります。VAUXA/Bの電流はデフォルトで400mAに制 限されています。PCIExpress規格では、上限値は375mAです。 一部のモジュールは規格に適合せず、これよりも大きい電流を 引き込むため、VAUXA/Bの電流制限はSMBusを使用して 800mAに設定できます。ダイレクト·モードでは、18ピンと19 ピンを使用して設定します。出力がユーザが障害(フォルト) タイマに定義した時間以上最大電流制限値を超えた場合、 VAUXA/Bがオフになります。その後、スロットのメイン電源 がオンになります。メイン電源は、ゲート・キャパシタにより 調整されたスルーレートでオンになります。12V電源の電流定 格は、カード·スロットの種類 (x1、x8、x16) によって異なる ことに注意してください。12V電源には3つの電流制限用抵抗 が推奨されています。各抵抗が、各々のスロットタイプの電流 をプログラムします。電圧が出力低電圧スレッシュホールドを 超えた場合、PGOODがアサートされ、シーケンスを完了します。 通常、モジュールの取り外しはアテンション・ボタンを押す ことで通知されます。GPIピンの1つをアテンション・ボタンに 使用できます。システムはモジュールの動作を停止し、モジュー ルがリセットされた後、ONA/BおよびAUXENA/Bまたは SMBUSを使用してスロット電源をオフします。TPS2363はブ リード·ダウン回路を持ち、電圧を監視します。電圧が100mV を下回ると、SMBusにより電源オフ信号を読み取ることがで きます。モジュールがオンのとき、LEDは点灯しています。電 源遮断中には点滅し、モジュールが安全に取り外せるようにな ると消灯します。

### VAUXA/Bの電流制限

標準のVAUX最大出力は、PCIExpressの仕様に準拠する400mAです。SMBusを使用してTPS2363をプログラムすることで、800mAを出力でき、仕様に準拠しないアドイン・モジュールにも対応できます。SMBusのファンクション・レジスタ・ビットを使用することで、ダイナミックに高電流設定または低電流設定を選択できます。ファンクション・レジスタ・ビットの定義については、「プログラミング」の項を参照してください。

AUXHIA/B、(ピン18とピン19)がNCまたはグランド接続されている場合、AUX出力はデフォルトで400mAになります。10kΩ最大抵抗を使用してVAUXIA/Bにプルアップすると、VAUXA/B出力は高電流モードに切り替わります。またSMBusファンクション・レジスタにより、VAUXA/Bの最大出力電流を制御できます。AUXHIA/Bピンがハイにプルアップされると、SMBusファンクション・レジスタによってVAUXA/B出力を低電流設定にすることができなくなります。

AUXHIA/Bは、ダイレクト・モードでSMBusを使用せずに高電流モードをイネーブルにしたい場合に便利です。結線接続が制限される場合、FPGAや他のロジックを使用してAUXHIA/Bピンをアクティブにできます。

## 障害(フォルト)の条件

障害(フォルト)条件は、次に示すいずれかのイベントが1つ 以上発生した場合に満たされます。

- 1. メイン電源 (12Vおよび3.3V) のオンの命令が出され、なおかつ、SH12A/BまたはSH33A/B、あるいはその両方の電圧が指定された最低電圧 (UVLO) に達しなかった。

- 2. メイン電源またはVAUXA/B、あるいはその両方が過電流状態になり、なおかつ、障害(フォルト)タイマ時間が経過した。

- 3. メイン電源またはVAUXA/B、あるいはその両方が過電流状態になり、なおかつ、チップ温度がTSHUT1を超えた。

- 4. 高速過電流遮断が検出された。

- 5. チップ温度がTSHUT2を超えた。

ダイレクト・モードでは、 $\overline{FAULTA/B}$ ピンがアクティブになり、SMBus STATA/Bレジスタの $\overline{FAULTA/B}$ ビットがセットされます。

SMBusモードの制御では、FAULTA/B信号ピンは偽になり、SMBus STATA/BレジスタのFAULTA/Bビットが非アクティブになります。障害 (フォルト) 状態のVAUXFA/B、12VFA/B、3VFA/BはSMBus STATA/Bレジスタから、OT\_INT, UV\_INTは共通ステータス・レジスタから読み取られます。

## 障害(フォルト)

障害 (フォルト) は、入力電源の3.3V-VAUX (VAUXINA/B)、3.3V (SH33H)、12V (SH12A/B) のどれでも発生する可能性があります。これらの入力は低電圧状態かどうかが監視されます。電圧がスレッシュホールドを下回り、電源セグメントが命令されると、 $\overline{FAULTA/B}$ が送出されます。 $\overline{VAUXINA/B}$  UVLOが発生すると、パワー・オン・リセットが実行され、 $\overline{FAULTA/B}$ がクリアされます。

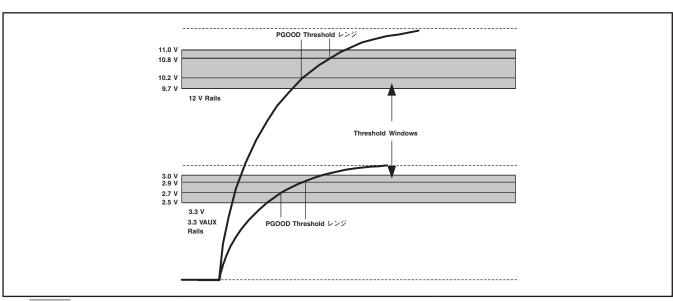

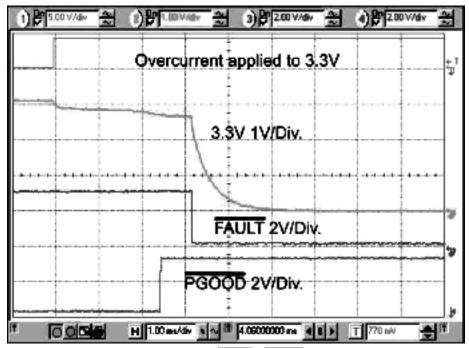

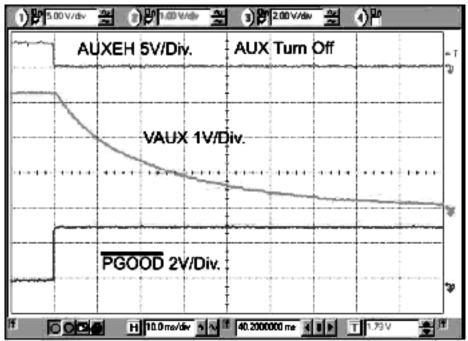

SlotA/Bの電圧 (ホットプラグ出力電圧) についても、低電圧 状態かどうかが監視されます。通常、スロットの最初の障害 (フォルト) 通知は、PGOODA/Bのデアサートです。これは、コントローラが電流制限を開始したときに、出力電圧がスレッシュホールドを下回るためです。電流制限がディスエーブルに なっている場合には、FAULTが最初に通知されます。図1に、PGOODのスレッシュホールドを示します。

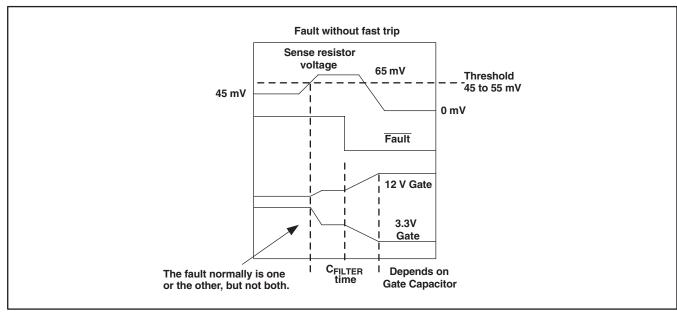

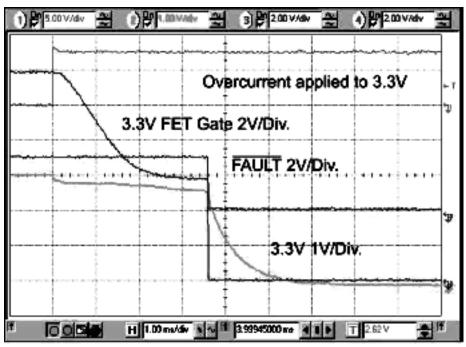

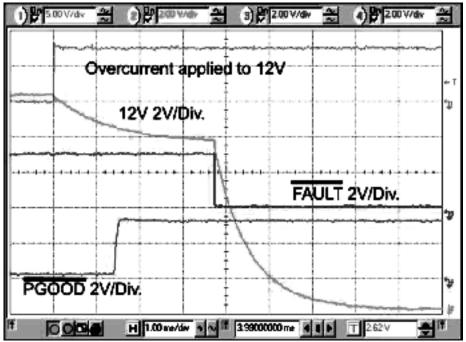

低電圧状態ではないものの、過電流状態が発生している場合には、最初にFAULTA/Bアクティブが通知されます。図2に、一般的な過電流遮断を示します。

TPS2363によってスロットへの出力電流が制限され、この状態がユーザが障害(フォルト)タイマに定義した時間継続し、回復しない場合には、SlotA/Bの電源がオフになり、FAULTA/B出力がセットされます。この電流制限は、SMBusによりディスエーブルにすることができます。ダイレクト・モードでFAULTA/Bをリセットするには、AUXENA/BピンまたはONA/Bピンをオフにします。SMBusを使用して障害(フォルト)情報を読み取ることができます。スロットのステータス・バイト(レジスタSTATA/B)については、SMBusレジスタに関する説明を参照してください。

図 1. PGOOD スレッシュホールド (灰色の部分はPCIExpress CEM 1.1規格を表します)

図 2. 高速過電流遮断が実行されない場合の過電流検出動作

## フォルト・タイマ

不用意に遮断が発生しないようにするには、通常の過電流イベントにおけるメイン電源およびAUXのオフ時間を障害 (フォルト) タイマで制御します。この過電流コンパレータの応答時間を表す $t_{FLT}$ は、ユーザが選択できます。チャネルごとに1つの外部キャパシタを使用して設定します。キャパシタは、FILTERA/Bとグランドの間に接続します。障害 (フォルト) タイマ・キャパシタを表す $C_{FILTERA/B}$ は、次の式を使って計算します。

$$C_{FILTER} = \frac{\left(t_{FLT} \times I_{FILTER}\right)}{\left(V_{FILTER} \times 1000\right)}$$

タイミング・パラメータの表に記載されている $V_{FILTER}$ および  $I_{FILTER}$ の値を使用すると、 $C_{FILTER}$ および関連する障害 (フォルト) 時間は、部品許容差を除外して最大60%変動します。障害 (フォルト) タイマの精度を向上するには、FILTERA/Bピンとグランドの間に $110k\Omega$ の抵抗を接続します。次の式を使って  $C_{FILTERA/B}$ を再計算します。

$$C_{\mathsf{FILTER}} = \frac{t_{\mathsf{FLT}}}{\left(\mathsf{R}_{\mathsf{FILTER}} \times \mathsf{SF}\right)}$$

ここで、 $R_{FILTER}$ は110 $k\Omega$ の1%抵抗、SFはタイミング・パラメータの表に記載されている換算計数です。この手法の場合、部品許容差を除外すると変動は22%未満に抑えられます。

他製品では、公表されているデータシートを基に計算すると、 抵抗を使用しない場合は200%、抵抗を使用した場合は27%の変 動になります。

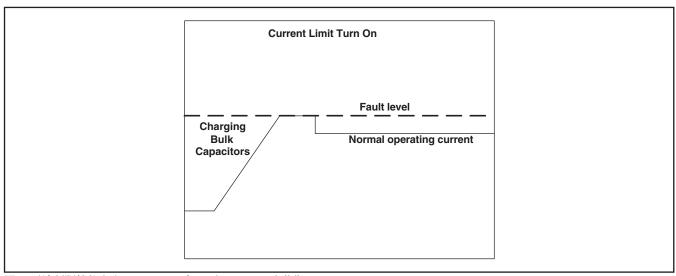

### 電流制限

電流制限ホットプラグ·コントローラにより、モジュールが引き込む電流量を制限することで、システムのバックプレーン電源レールへの過負荷やグリッチを防止します。モジュールの電流制限は障害(フォルト)タイマの間だけ継続し、その後で回路がオープンとなります。障害(フォルト)タイマが終了する前に障害(フォルト)状態が解決されると、モジュールは通常の動作モードに戻ります。欠点としては、電流制限の間にモジュールの電源が低下し、モジュールのロジックが不定状態やハング状態になる可能性があることです。モジュールをリセットするか、モジュールにパワー・サイクルを実行してロジックをリセットする必要があります。

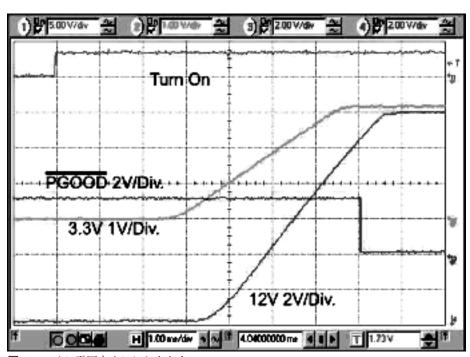

図3に、電流制限を利用してモジュールをオンにする様子を示します。電流制限を使用する場合、一般的にフォルト・タイマにはサーキット・ブレーカとしての応答時間よりも長い時間を設定します。電流が制限されると、キャパシタの充電にかかる時間が長くなります。

図3.電流制限機能をもったホットプラグ(ターンオン)動作

図 4. サーキット・ブレーカ機能を持ったホットプラグ (ターンオン)動作

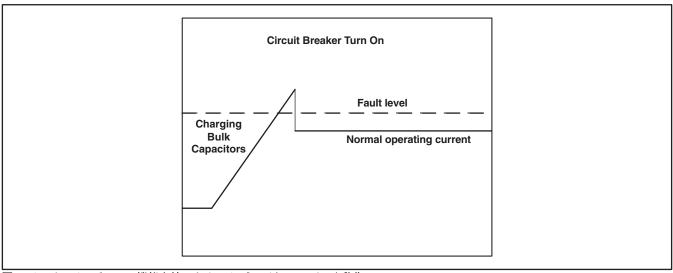

## サーキット・ブレーカ

サーキット・ブレーカ制御機能では、障害発生時のグリッチか らシステムを保護しません。バックプレーンおよび電源システ ムをより高電流レベル用向けに設計する必要があります。ピー ク電流は、ホットプラグに使用されるFETスイッチの $R_{DS(on)}$ によってのみ制限されます。障害が発生したときにモジュール の電源をいつオフにするかは障害(フォルト)タイマによって 制御されます。一般的に障害(フォルト)タイマは10msレンジに 設定します。障害により高電流が発生すると、バックプレーン の電圧が低下し、システムおよびその他の基板が不明な状態にな ることがあります。そのような場合、システムの障害時リセット や電源サイクルを実行する必要があります。高速遮断モードは、 SMBusでディスエーブルにしない限りアクティブです。電流 引き込みが障害(フォルト)電流の設定値を大幅に上回った場 合、障害(フォルト)タイマが終了するまで待機することなく、 直ちに出力がオフになります。これにより、システムおよびそ の他のモジュールが不明な状態になる原因である電圧グリッチ の発生確率が低下します。

図4に、サーキット・ブレーカを使用してモジュールをオンに する様子を示します。電流上昇時に電流量が障害(フォルト) レベルを超え、キャパシタの充電が終わると低下します。

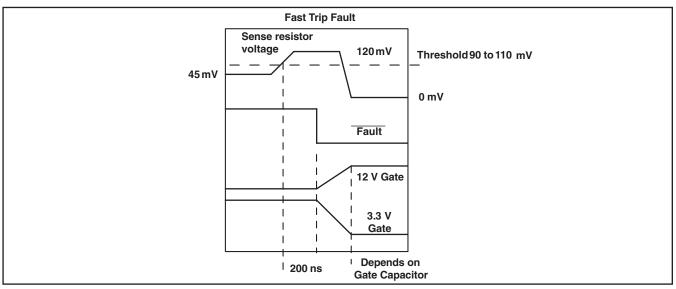

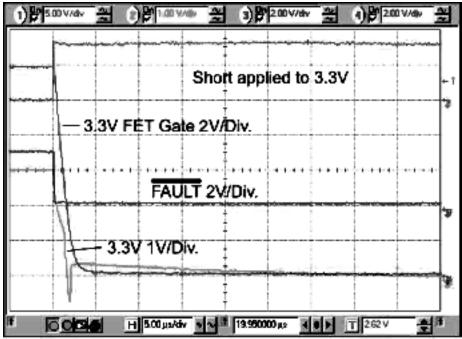

## 高速遮断

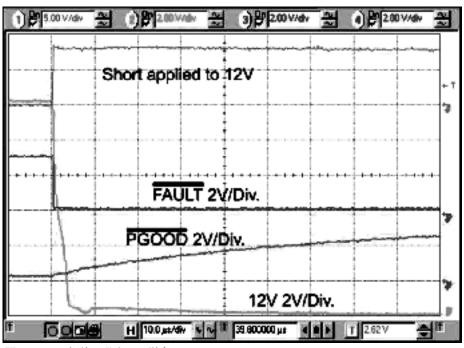

図5に、高速遮断を示します。高速遮断を使用することで、通常、障害(フォルト)電流の2倍まで対応でき、大電流による障害にも200nsで対応できます。障害(フォルト)電流設定が6Aの場合、障害(フォルト)タイマ時間まで6A~12Aが許容されます。障害(フォルト)タイマの時間は、選定した障害(フォルト)キャパシタに応じて、通常10ms前後になります。12A以上の電流が発生すると、200ns後にスロットがオフになります。ピーク電流は電源FETのR<sub>DS(on)</sub>およびホットプラグ用のセンス抵抗によってのみ制限されます。システム電圧がシステム内の部品の許容電圧範囲よりも低下することなく、このような電流負荷に対応できるように、システム電源を設計する必要があります。

図 5. 高速遮断の動作

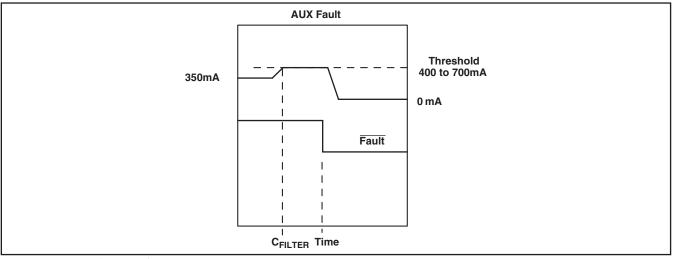

図 6. AUX電源障害(フォルト)

### 電流制限機能のトレードオフ

システム設計により、コントローラの電源オフ特性が決まります。一般的なハイエンド無障害システムでは、電流制限機能を使用し、障害が検出されたときにモジュールをパワー・オフにします。このようなシステムでは、障害が発生したモジュールが回復する機会があることと、システムがハングしないことが重要です。

ミッドレンジ・サーバでは、一般的に高速遮断機能を持った サーキット・ブレーカが使用されます。システム電圧がシステム内の部品の許容電圧範囲よりも低下することなく、このよう な電流負荷に対応できるように、システム電源を設計する必要 があります。

電流制限を行うと、モジュールのターンオン時間が長くなります。この場合、障害(フォルト)タイマがタイムアウトする前にモジュールが立上がるために、障害(フォルト)タイマの時間を長くする必要があります。

VAUXA/Bは高速遮断モードの影響を受けません。VAUXA/B の過電流シャットダウンは、常に障害(フォルト)タイマによって制御されます。低電圧時の電源オフは、AUXINA/Bに応じて直ちに実行されます。図6を参照してください。

## 障害(フォルト)スレッシュホールドの算出

過電流障害(フォルト)は、センス抵抗に生じる電圧によって検出します。スロットの電流スイッチ・パスに、通常数十ミリオーム未満の小さな抵抗が配置されます。センス抵抗に生じる電圧はコンパレータに入力され、電圧が電流制限スレッシュホールドを超えると、コンパレータがオンになります。

3.3Vの場合、コネクタ幅に関係なくPCIExpress規格によって 3.0Aに定められています。

- 抵抗とプリント回路の許容差を考慮して、電流を3.5Aに制限 します

- 3.3Vにおける電流制限の最小スレッシュホールドは45mVです。

$$R_{SENSE} = \frac{Threshold\ Voltage}{I_{SENSE}} = \frac{0.045}{3.5A} = 0.0128\Omega$$

(13mΩの抵抗を使用します)

最大電流制限をチェックします。

- 1%抵抗は最小で12.87mΩです。

- 電流制限の最大スレッシュホールドは55mVです。

$$I_{MAX} = \frac{Threshold\ Voltage}{R_{SENSE}} = \frac{0.055\ V}{12.87\ m\Omega} = 4.27A$$

#### 3.3Vセンス抵抗の値

|        | RESISTOR (mΩ) | AVG CURRENT (A) | MAX CURRENT (A) |  |

|--------|---------------|-----------------|-----------------|--|

| +3.3 V | 13            | 3.5             | 4.27            |  |

コネクタ幅が1、8、16の場合に推奨される12V電源のRSENSEの値を示します。

#### 12Vセンス抵抗の値

| CONNECTOR WIDTH | RESISTOR (m $\Omega$ ) | AVG CURRENT (A) | MAX CURRENT (A) |  |

|-----------------|------------------------|-----------------|-----------------|--|

| 1               | 50                     | 0.9             | 1.11            |  |

| 4,8             | 20                     | 2.1             | 2.78            |  |

| 16              | 10                     | 4.4             | 5.56            |  |

| 16 graphics     | 8                      | 5.5             | 6.94            |  |

## 突入電流

突入電流は、起動時に容量性負荷が原因で発生する大電流です。これによってシステム電圧が低下し、システム内の他の動作中モジュールで問題が発生することがあります。大きな突入電流が発生すると、コネクタ・ピンや回路ボードが破壊される可能性があります。TPS2363のような過電流ブレーカ制御を行う場合、適切なゲート・キャパシタを選択し、障害(フォルト)タイマを適切に設定しなければ、突入電流によって過電流コンパレータがオンになり、スロットがオンにならないことがあります。

突入電流を制限するには、スロットの電源のターンオン・レートを制御します。平均突入電流は、負荷の容量と、スロット電圧のターンオン時間を調べることで計算できます。一般的に、平均突入電流がスロット・コントローラの過電流設定点の1/3未満の場合、スロット・コントローラは遮断を行いません。

3.3V出力については、ソース・フォロワ構成でNチャネルFETを使用します。スロット電圧のオンになる速度は、FETゲートにキャパシタを接続し、出力がオンになるまでの時間を長くすることで遅くできます。ゲート・キャパシタの値を決定するには、負荷のdv/dtを計算した後、同じdv/dtをFETゲートに適用します。次に、3.3Vメイン電源のゲート・キャパシタの値を計算する例を示します。

#### 例:

- PCIExpressの仕様では、3.3V電源に対して最大1000µFの容量を許容します。

- 3.3V、13mΩの抵抗で3.3Vの最小遮断電流は3.46Aです。3.46/3で、1.15Aを使用します。

- I<sub>GATE</sub>は25µAです。

$$\begin{split} I_{LOAD} &= C_{LOAD} \times \frac{dv}{dt} \;, \frac{dv}{dt} = \frac{I_{LOAD}}{C_{LOAD}} \\ I_{GATE} &= C_{GATE} \times \frac{dv}{dt} \;, \frac{dv}{dt} = \frac{I_{GATE}}{C_{GATE}} \\ \frac{I_{LOAD}}{C_{LOAD}} &= \frac{I_{GATE}}{C_{GATE}} \\ C_{GATE} &= \left(\frac{I_{GATE}}{I_{LOAD}}\right) \times C_{LOAD} = \left(\frac{25 \; \mu A}{1.15 \; A}\right) \times 1000 \; \mu F \\ &= 21.7 \; nF \; (use22 \; \mu F) \\ \frac{dv}{dt} &= \frac{25 \; \mu A}{22 \; nF} = 1136 \; V/s \end{split}$$

ONA/Bをアサートした後、ゲート電圧が $V_{GS(th)}$ に上昇するまで出力がオンになりません。ゲート・キャパシタにより、電源信号をアサートしてから電圧の上昇が開始するまでわずかな遅延が生じます。

12V出力については、制御用に $V_{GS}$ が十分に大きくなるように PチャネルFETを使用します。この構成では、FETは高ゲイン増幅器になります。12Vの場合のスルーレートは、FETのゲートからソースまでのミラー容量により制御します。計算方法は3.3Vの場合と同じですが、FETのgfsにより、 $C_{MILLER}$ が小さくなります。

#### 例:

- PCIExpressの仕様では、12V電源に対して最大2000μFの容量を許容します。

- 8mΩ抵抗での12Vの最小遮断電流は5.63Aです。5.63/3で、 1.88Aを使用します。

- FETのgfsは約3であると仮定します。

- I<sub>GATE</sub>は25µAです。

12Vにおけるスルーレートを計算する式は、次のとおりです。

$$\frac{dv}{dt} = \frac{I_{GATE}}{C_{MILLER} \times (gfs + 1)}$$

$$\frac{I_{LOAD}}{C_{LOAD}} = \frac{I_{GATE}}{\left(C_{MILLER} \times 4\right)}$$

$$\left(C_{MILLER} \times 4\right) = \frac{I_{GATE} \times C_{LOAD}}{I_{LOAD}}$$

$$C_{MILLER} = \frac{(25 \mu A \times 2000 \mu F)}{1.88 \times 4}$$

= 6.6 nF, (use 6800 pF)

ONA/Bからの遅延時間は、 $C_{GATE}$ および $C_{MILLER}$ の合計値により制御します。12V FETゲートにゲート・キャパシタを追加することにより、電源オン時の遅延時間を3.3V FETとほぼ同じにします。 $C_{MILLER}$ は3.3Vにおける $C_{GATE}$ よりも小さいため、12Vゲートの場合にも3.3Vと同じキャパシタ値を使用します。

次の表に、さまざまなコネクタ幅の場合に3.3Vおよび12V電源で推奨されるゲート・キャパシタ容量を示します。

### 推奨ゲート・キャパシタ (1)

| VOLTAGE | VOLTAGE WIDTH |  | C <sub>GATE</sub> (nF) |

|---------|---------------|--|------------------------|

| +3.3    | All           |  | 22                     |

| +12     | +12 All       |  | 22                     |

(1) 突入電流を制限するために推奨されるキャパシタです。

The 3.3-V slew rate is  $\frac{3.3}{1136 \text{ V/s}} = 2.9 \text{ ms}$

## MOSFET R<sub>DS</sub> (on)

FETを選択するときに重要なパラメータは、オン抵抗を表す  $R_{DS\,(on)}$ です。 $R_{DS\,(on)}$ を低くすると、MOSFETの定常状態の電力消費が小さくなり、PCIで推奨されるバス電圧を維持することが容易になります。ただし、 $R_{DS\,(on)}$ を低くすると、短絡状態における過電流が増大します。これについては後で解説します。また、 $R_{DS\,(on)}$ を低くすればするほど、高価になります。

#### VDSSドレイン・ソース間電圧

$V_{DSS} > 2 \times V_{IN}$

#### IDドレイン電流(連続)

定常状態の負荷を扱う場合、最も温度が高い状況 (通常70℃ ~100°C) で、MOSFETの電流定格であるIDの最低値は次のように設定します。

$2 \times I_{TRIP(max)}$

(R<sub>SENSE</sub>の算出に関するセクションを参照してください)

$T_{C(max)}$ における  $I_D > 2 \times I_{TRIP(max)}$

#### IDMパルス・ドレイン電流 (PDおよびSOAを含む)

TPS2363には短絡出力保護機能があります。最大500nsの間、MOSFETは大きな電力消費にさらされます。この間、電流は "電源電圧/  $(R_{DS(on)} + R_{SENSE})$ " になります。過電流スパイクが発生すると、障害 (フォルト) タイマの時間にわたって、電源電圧でMOSFETに遮断電流が流れます。デバイスにおける最大電力消費の定格と安全動作領域を考慮して、IDMを計算し、デバイスを選択する必要があります。

IDM、PD、およびSOAを計算します。

### VGSゲート・ソース間電圧

3.3V MOSFETのゲート・ソース間電圧定格VGSは、15V以上にします。これは、TPS2363の3.3Vゲート電圧が15Vに達し、ソース電圧がグランドに短絡されることがあるためです。

#### VGS(3.3) > 15V

12V MOSFETのVGSは15Vにします。これは、ソースが15V時に、TPS2363のゲート電圧が0Vになることがあるためです。

VGS(12) = 15V

## リファレンス・デザイン

図7. リファレンス・デザイン

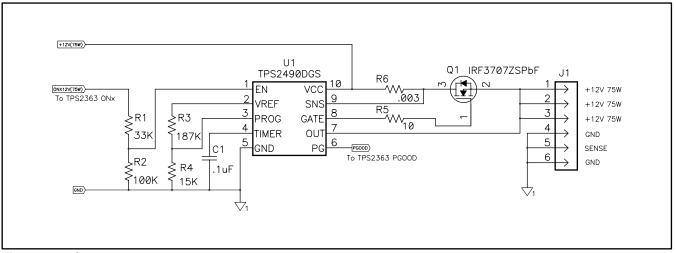

## 150Wアドイン・モジュール

PCI Express x16グラフィックス150W-ATX仕様1.0では、次のように定められています。

- スロット・コネクタのメイン電源では最大75Wが供給されます。

- アドイン·モジュールに追加ケーブルを取り付けることで、75Wの12V電源を追加します。

- スロットの12Vメイン電源と12V追加電源は互いに独立しています。

- PCI Express CEM1.1のホットプラグ機能はサポートされません。

このような150Wモジュールをホットスワップ環境で使いやすくするために、TPS2490電源コントローラによって12V 75W ソースを制御できます。

- TPS2363スロット電源コントローラと共にTPS2490をオンに します。

- 各コントローラのパワー·グッド出力をOR接続します。

- いずれかの電源で過電流または電源障害が発生すると、スロット電源がオフになります。

- モジュールをスロットに挿入する前に、12V 75W電源をモジュールに接続しておくと、モジュールへのすべての電源を一斉にオンにできます。

図 8.150Wアプリケーション

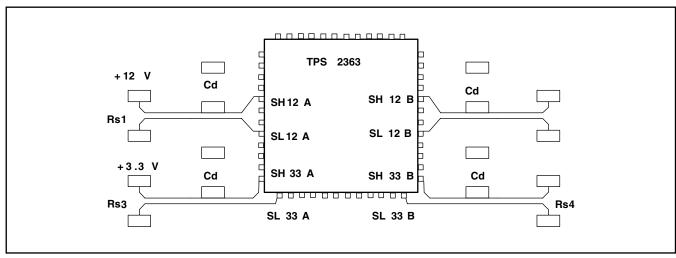

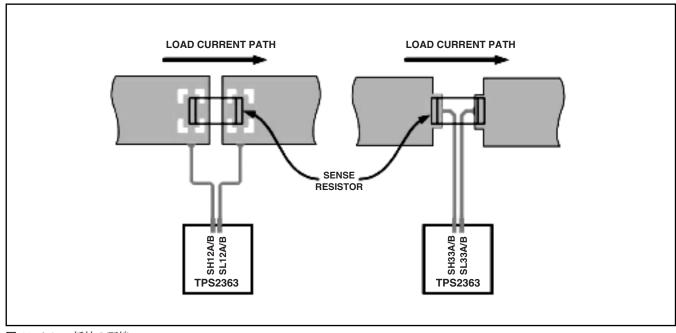

## レイアウトに関する考慮事項

TPS2363へのメイン電圧入力はセンス抵抗への入力でもあるため、出力電流を正確に読み取るためには、レイアウトに注意する必要があります。

図9および図10を参照してください。

- センス抵抗はTPS2363の近くに配置します。

- TPS2363のピンSH12A/BおよびSH33A/Bは、内部層の電源 に接続しません。

- センス抵抗の高電位側を内部層の電源に接続します。

- 0.1µFを使用して、センス抵抗をTPS2363の近くでデカップリングします。

- SH12AからSH12Bへ、またはSH33AからSH33Bへの付加的な接続をしないでください。

- システムの状態によっては、センス抵抗に並列に、又は TPS2363の近くでセンス抵抗の低電位側とグランドの間に 1nFキャパシタを配置する必要があります。

図 9. センス抵抗(電源レイアウト)

図 10. センス抵抗の配線

## 過熱

TPS2363の動作接合部温度範囲は広く、各チャネルが独立して対応します。1つのスロットのコントローラの温度がTSHUT1まで上昇し、通常のVAUXA/B過電流条件が発生している場合、過電流が発生したチャネルでは直ちにスロットに対するすべてのメイン電源とVAUX電源がオフになります。過熱シャットダウンでは障害(フォルト)タイマが使用されません。タイマが進行中の場合でも、過熱シャットダウンが優先されます。他のチャネルは動作を継続します。電源がオフにされたスロットでは、FAULTビットがアクティブになります。ヒステリシス値よりも低い温度に戻ると、FAULTをクリアできます。メイン電源が原因だった場合はONA/Bを使用してクリアし、VAUXA/Bが原因だった場合はAUXENA/Bを使用してクリアします。その後、スロットは動作を継続します。SMBusモードの場合は、「プログラミング」を参照してください。

チップ温度がTSHUT2まで上昇した場合、電流制限の状態に関係なく、TPS2363の両方のチャネルが直ちにシャットダウンし、共通ステータス・レジスタのOT\_INTビットがセットされます。ヒステリシス値よりも低い温度に戻ると、シャットダウン前の状態に復帰します。

## 障害(フォルト)時の割り込み

ダイレクト・モードまたはSMBusモードで $\overline{\text{INT}}$ 出力信号を使用することで、電力障害 (フォルト) の発生時にプロセッサに割り込みをかけることができます。メイン電源またはVAUXA/B電源の障害 (フォルト)、メイン電源での低電圧、またはTSHUT2過熱状態が発生すると、 $\overline{\text{INT}}$ が "ロー" にアサートされます。

ダイレクト・モードでは、 $\overline{\text{INT}}$ 信号は常にイネーブルです。障害 (フォルト) 状態が取り除かれると、割り込みがクリアされます。メイン電源の障害 (フォルト) をクリアするには、ONA/Bをデアサートします。VAUXA/B電源の障害 (フォルト) は、AUXENA/Bがデアサートされるとクリアされます。 $\overline{\text{INT}}$ を使用しない場合は、100kΩ抵抗を使用してピンをAUXINA/Bにプルアップし、 $\overline{\text{FAULTA}}$ B出力を使用してスロット状態をチェックします。

SMBusモードでは、共通ステータス・レジスタのINTMASK ビットをセットすることで $\overline{\text{INT}}$ 出力をディスエーブルにできます。 $\overline{\text{INT}}$ をディスエーブルにした場合、状態レジスタをポーリングして障害 (フォルト) 情報を取得します。デフォルトでINT-MASKビットは"ロー"になっており、 $\overline{\text{INT}}$ 出力がイネーブルになっています。

STATA/Bレジスタは、FAULTA/B (D7)、および障害(フォルト)の原因となった電源としてVAUXFA/B (D4)、12VFA/B (D2)、3VFA/B (D0)を示します。障害(フォルト)をクリアする方法はダイレクト・モードの場合と似ており、メイン電源の場合はCNTRLA/BのMAINENA/B (D1)をデアサートし、補助電源の場合はAUXENA/B (D0)をデアサートします。障害(フォルト)が取り除かれた後も、元の障害(フォルト)状態はSTATA/Bレジスタに残ります。この障害(フォルト)状態をクリアするには、STATA/Bビット位置に "1"を書き込んでクリアします(3VFA/B、12VFA/B、またはVAUXFA/B)。レジスタSTATA/BのFAULTA/Bは書き込み不可ですが、障害(フォルト)状態ビットがすべてクリアされると、クリアされます。

その他の障害(フォルト)状態は、共通ステータス・レジスタから取得できます。メイン電源での低電圧イベントは、UV\_INT(D2)により示されます。TSHUT2に達する過熱は、OT\_INT(D1)により示されます。これらのステータス・ビットをクリアするには、共通ステータス・レジスタの該当するビット位置に"1"を書き込みます。

## 出力の強制イネーブル

システム動作のために $\overline{FORCEONA/B}$ を使用してスロットをオンにすることは推奨されていませんが、デバッグや試験の際には便利です。 $\overline{FORCEONA/B}$ を "ロー"にアサートすると、過電流状態、短絡状態、低電圧状態であろうと関係なく、VAUXA/B電源およびメイン電源の電圧出力がオンになります。ただし、AUXINA/Bの低電圧検出がアクティブで、VAUXA/B出力のシャットダウンに影響する場合は例外です。TSHUT1の温度ではすべての電圧出力がオンのままですが、TSHUT2の温度に達すると障害(フォルト)タイマを使用せずにシャットダウンされます。 $\overline{FORCEONA/B}$ を使用しない場合は、100k $\Omega$ 抵抗を使用してこれらの入力をAUXINA/Bにプルアップします。

FORCEONA/Bがアクティブなときには、出力FAULTA/BおよびPGOODA/Bが偽になります。実際の障害(フォルト)状態は、SMBus STATA/Bおよび共通ステータス・レジスタから読み取ることができます。

$\overline{FORCEONA/B}$ 入力をディスエーブルにするには、コントロール・レジスタCNTRLA/Bの $\overline{FORCEON}$  INHIB (A/B) ビットをセットします。このように、ダイレクト・モード・ハードウェアでは制御インタフェースとしてのSMBusを無効にすることはできません。このビットのデフォルト状態では、 $\overline{FORCEONA/B}$ がイネーブルになります。

## 汎用入力ピン

汎用入力(GPI)ピンを任意の3.3Vデジタル信号に接続することで、システム・コントローラへのリードバックを行えます。これらの入力は、VAUXA/B制御(スイッチ)やアテンション、手動固定ラッチへの直接接続に使用できるようにスイッチ・デバウンスされています。各GPIピンには、内部に100k $\Omega$ プルダウン抵抗があります。

## パワーオフ

PWROFFA/Bビットは、SMBusファンクション・レジスタから使用できます。メイン電源とVAUXの電圧が低コンパレータ・スレッシュホールド(100mV typ)よりも低い場合、PWROFFが論理1になります。これを利用して、スロットがオフであるか、スロット内にモジュールを取り付けたり取り外したりしても安全かどうかを判断できます。

## SMBusを備えたPFB48ピン・パッケージのピン・アウト

**図 11.** PFB48ピン・パッケージ

### ダイレクト・モード

ダイレクト・モードでは、AUXENA/B及びONA/Bを用いることで、それぞれVAUXA/B、メイン電源がコントロールされます。 $\overline{FORCEONA/B}$ を使用して試験とデバッグを行うことができます。 $\overline{SMBus}$ を使用せずに取得できるステータス情報は、 $\overline{PGOODA/B}$ と $\overline{FAULTA/B}$ のみです。

ダイレクト・モードを使用するために、SMBusをディスエーブルにする必要はありません。SMBusを使用して、ステータスや汎用入力を読み取ることができます。TPS2363がダイレクト・モードのときには、コントロールA/Bレジスタに書き込まないでください。コントロールA/Bレジスタに書き込みを行うと、TPS2363がSMBusモードに切り替わります。TPS2363で電源サイクルが実行されるまで、ダイレクト・モードには戻りません。ファンクション・レジスタへの書き込みは、VAUXA/Bの電流制限レベルを変更したり、メイン電源の電流制限をディスエーブルにする場合に使用が許可されます。

SMBusを使用しない場合は、100k $\Omega$ の抵抗を使用してSCLとSDAを3.3VまたはAUXINA/Bにプルアップし、A0~A2をグランドに接続します。

割り込みを使用しない場合は、 $100k\Omega$ の抵抗を使用して $\overline{\text{INT}}$ を3.3VまたはAUXINA/Bにプルアップします。

## SMBusモード

SMBusモードでは、TPS2363はSMBusレジスタによって制御されます。ダイレクト・モードをディスエーブルにするには、AUXENA/BおよびONA/Bをグランドに接続します。

STATA/BレジスタのFAULTA/Bビットは、FAULTA/Bピンの状態を示します。このビットはSMBusモードでは非アクティブです。

モードと接続の関係については、「パワー・オン・リセット」 の項の表「モードとピン接続」を参照してください。

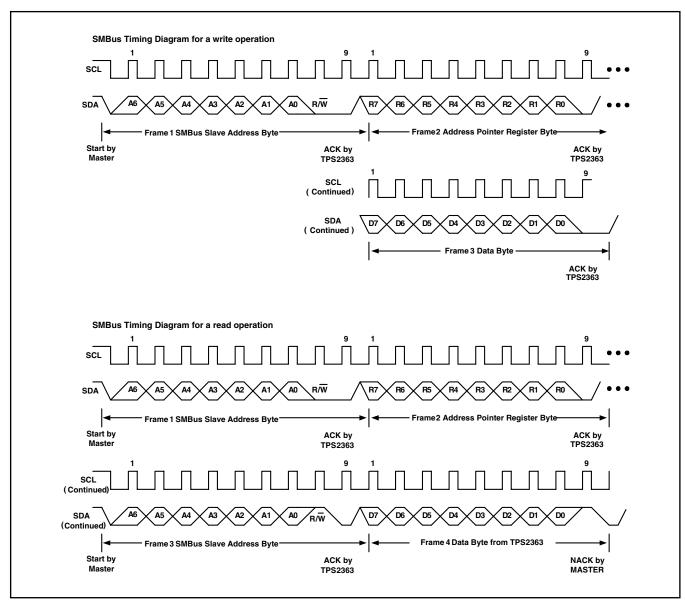

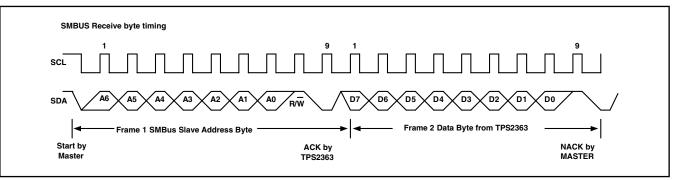

#### プログラミング

クロック・ラインとデータ・ラインは、SMBusの終端で $10k\Omega$  の抵抗を使って3.3VまたはAUXINA/Bにプルアップします。この終端抵抗は、電源投入時とイネーブルにしたときにデフォルト値に設定します。

コントローラはSDAピンおよびSCLピンを使ってプログラムされます。通常このピンは"ハイ"になっており、SCLのクロックの立ち下がりエッジによってデータをクロック制御します。データ・ラインをアサートすることでシーケンスが開始され、25ns後以降にクロック・ラインがアサートされます。アサートによって、ラインが"ロー"に移行します。クロック・ラインは、読み取りを行う場合はネゲートし、書き込みを行う場合はアサートしたままにします。クロック・ラインがアサートされ、25ns後にネゲートされた後、次にクロック・ラインがアサートされたときには、D7、D6、D5、D4、D3、D2、D1、D0、ACK(ハイ)、stop(ロー)を使用した読み取りまたは書き込みが開始されます。アドレスは、読み取り/書き込みビット、対象アドレス・バイト、ペイロード・バイトを使用して送出します。アドレスには7個のレジスタを使用できます。

アドレスは7ビット長です。TPS2363のアドレス選択では、A0~A2が使用されます。1000000bではビットがセットされません。1000001bではA0のみセットされ、1000010bではA1のみ、1000011bではA0およびA1、1000100bではA2のみ、1000101bではA0およびA2、1000110bではA1およびA2、1000111bではA0、A1、およびA2がセットされます。8番目のビットは読み取り/書き込みの指定に使用します。

SMBusはダイレクト・モードでも使用できます。AUXENA/BまたはONA/Bを使用した場合、レジスタは、SMBusを使ってオンにした場合とは異なる動作になります。

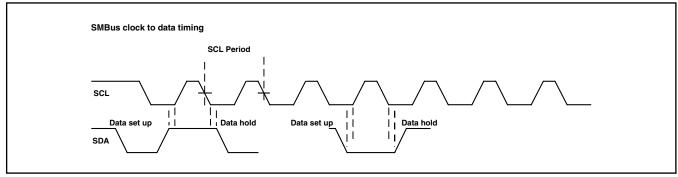

## SMBusシリアル・クロック入力端子(SCL)

SCL端子を利用して、ホスト・コントローラからクロック信号を送出し、TPS2363のSDA端子の入出力データを同期させます。このクロックの周波数は、10kHz~400kHzの間で任意に設定できます。タイミング図に、SCLとSDAの関係を示します。

## SMBusシリアル・データ入出力端子(SDA)

ホスト・コントローラはSDA端子を利用して、TPS2363をプログラムし、ステータスを読み取ることができます。SDA端子で入出力されるデータは、SCLの立ち上がりエッジで同期されます。タイミング図に、SDAとSCLの関係を示します。

## エコー・リセット

STATA/B及び共通ステータス・レジスタの一部のビットによって障害(フォルト)が通知されると、割り込みが発生します。障害(フォルト)状態がクリアされても、これらのビットはセットされたままです。ビットがセットされたままになるのは、コントローラが割り込みを処理し、障害(フォルト)状態を読み取

る時間を与えるためです。セットされているビットに1を書き込むと、次にレジスタを読み取るときに障害(フォルト)状態が解決されていれば、ビットがクリアされます。これを、エコー・リセットと呼びます。該当するビットは、STATA/Bのビット位置D0、D2、D4、および共通ステータス・レジスタのD1、D2です。

図 12. SMBusのクロックによるデータ·タイミング

図 13. 書き込み/読み取り動作時のSMBusタイミング図

図 14. SMBusの受信バイト·タイミング

## レジスタ・セット<sup>(1)(2)(3)(4)</sup>

| TARGET    | TARGET REGISTER   |      | BYTE VALUE | POWER-ON DEFAULT |

|-----------|-------------------|------|------------|------------------|

| LABEL     | DESCRIPTION       | READ | WRITE      |                  |

| Reserved  |                   | 00h  | N/A        | N/A              |

| Reserved  | Reserved          |      | 01h        | 00h              |

| CNTRLA    | Slot A control    | 02h  | 02h        | 00h              |

| CNTRLB    | Slot B control    | 03h  | 03h        | 00h              |

| STATA     | Slot A status     | 04h  | 04h        | 00h              |

| STATB     | Slot B status     | 05h  | 05h        | 00h              |

| Chip STAT | Common status     | 06h  | 06h        | 00h              |

| FUNCTION  | Special functions | 07h  | 07h        | 0dh              |

- (1) DMC = ダイレクト・モード制御

- (2) SMC = SMBus制御

- (3) UVLO = 低電圧ロックアウト

- (4) RSVDビットは読み取り専用であり、Oが読み取られます。

## コントロール・レジスタ <sup>(1)</sup>

| AUX PG(A/B) | MAIN PG(A/B) | RSVD | RSVD | RSVD | -FORCEON<br>INHIB(A/B) | MAINEN(A/B) | AUXEN (A/B) |

|-------------|--------------|------|------|------|------------------------|-------------|-------------|

| R           | R            | R    | R    | R    | R/W                    | R/W         | R/W         |

(1) CNTRL A (02h)、CNTRL B (03h)。デフォルトは00hです(ダイレクト・モードではこのレジスタに書き込まないでください)。

#### 有効な書き込みコマンド:

- 00h: 強制モードを適用し、すべての電源をディスエーブル にします。

- 01h:強制モードを使用してVAUXA/B電源をイネーブルに します。

- 02h:強制モードを使用してメイン電源をイネーブルにします。

- 03h:強制モードを使用してメイン電源とVAUXA/B電源を イネーブルにします。

- 04h:FORCEONピンをディスエーブルにし、すべての電源 をディスエーブルにします。

- 05h:強制モードを使用せずにVAUXA/B電源をイネーブル にします。

- 06h:強制モードを使用せずにメイン電源をイネーブルにします。

- 07h:強制モードを使用せずにすべての電源をイネーブルに します。

(ダイレクト・モードでこのレジスタに書き込みを行うと、TPS2363がSMBusモードに切り替わります。TPS2363で電源サイクルを実行するまで、ダイレクト・モードには戻りません。)

**有効な読み取り.データ:**(Yに入る値については、上記の表に記載されている組み合わせを参照してください。)

- 0Yh: VAUXA/B電源およびメイン電源がパワー·グッド・モードではありません。

- 4Yh:メイン電源のみがパワー·グッド·モードです。

- 8Yh: VAUXA/B電源のみがパワー·グッド·モードです。

- cYh: VAUXA/B電源およびメイン電源がパワー·グッド· モードです。

**AUX PG(A/B)(R):**このビットは、VAUXA/B出力のパワー・ グッド状態を表します。

- 1:VAUXA/B出力がパワー·グッド·スレッシュホールドを 超えています。

- 0:VAUXA/B出力がパワー·グッド·スレッシュホールドを 超えていません。

このビットは、次の条件がすべて満たされている場合にセットされます。

- SMBusモードまたはダイレクト・モードの制御によって VAUXA/Bがイネーブルになっている。

- VAUXA/B出力がパワー·グッド·スレッシュホールドを超えている。

このビットの値は、FORCEONA/Bの影響を受けません。

MAIN PG (A/B) (R): このビットは、3.3Vと12Vのパワー·グッド 状態を示します。

- 1:3.3V出力と12V出力の両方が、それぞれのパワー·グッド·スレッシュホールドを超えています。

- 0:メイン電源(3.3Vまたは12V)のどちらかまたは両方とも パワー・グッド・スレッシュホールドを超えていません。

このビットは、次の条件がすべて満たされている場合にセットされます。

- SMBusモードまたはダイレクト・モードの制御によってメイン電源がイネーブルになっている。

- 3.3Vおよび12Vの両方がパワー·グッド·スレッシュホール ドを超えている。

このビットの値は、 $\overline{\text{FORCEON}}$  INHIBA/Bビットの影響を受けません。

FORCEON INHIB (A/B) (R/W): このビットを使用して、FORCEONA/Bピンをインヒビットします。

- 1: FORCEONA/Bピンが無視されます。

- 0: FORCEONA/Bピンを使用できます。

**MAINEN (A/B) (R/W)**: このビットによってメイン電源 (3.3V および12V) を制御します。

- 1:3.3Vと12V出力をイネーブルにします。

- 0:3.3Vと12V出力をディスエーブルにします。

このビットがセットされ、次の条件がすべて満たされたときに、チャネルがイネーブルになります。

- 3.3Vまたは12Vに障害 (高速遮断、タイムアウトを伴う過電流、TSHUT1を超える過電流、UVLOまたはTSHUT2) が発生していない。

- AUXINA/B入力がUVLOスレッシュホールドを超えている。

- 障害 (フォルト) 状態をリセットするためには、このビットをオフにして、再度オンにする必要があります。

**AUXEN (A/B) (R/W)**: このビットによってVAUXA/B出力を制御します。

- 1: VAUXA/Bチャネルをネーブルにします。

- 0: VAUXA/Bチャネルをディスエーブルにします。

このビットがセットされ、次の条件が満たされたときに、チャネルがイネーブルになります。

- VAUXA/Bに障害が発生していない。(タイムアウトを伴う 過電流、TSHUT1を超える過電流、UVLOまたはTSHUT2)

- AUXINA/B入力がUVLOスレッシュホールドを超えている。

- 障害 (フォルト) 状態をリセットするためには、このビットをオフにして、再度オンにする必要があります。

**STAT A (04h)、STAT B (05h)**: デフォルト00h

| FAULTA/B | MAINA/B | AUXA/B | VAUXFA/B | RSVD | 12VFA/B | RSVD | 3VFA/B |

|----------|---------|--------|----------|------|---------|------|--------|

| R        | R       | R      | R/W      | R    | R/W     | R    | R/W    |

**有効な書き込みコマンド:**書き込みコマンドを使用して、レジスタの障害(フォルト)状態をクリアします。

• 00h, 01h, 04h, 05h, 10h, 11h, 14h, 15h

有効な読み取りコマンド: $0Y \sim fY(Y t t 0, 1, 4, 5 n t 0)$  です)

**FAULT A/B:**このビットはFAULTA/Bピンの状態を表します。

- ●1: <u>FAULTA/B</u>ピンは "ロー" です。

- $0: \overline{FAULTA/B}$ ピンは "ハイ"  $(オープン \cdot F \nu + \Gamma \nu)$ です。

このビットが過電流のためセットされた場合、対応するイネーブル・ビットまたはピンをオフにし、再度オンにすることで、障害(フォルト)状態をクリアし、SMBusモードのエコー・リセットを行う必要があります。

FORCEONA/Bが "ロー"の場合、FAULTA/Bはオープン・ドレイン状態です。FAULTA/Bビットは影響を受けません。SMBusを使用して制御しているときには、このビットは非アクティブになります。

MAINA/B: このビットは、メイン電源の内部イネーブル状態を示します。

- 1:3.3Vと12Vがイネーブルになっています(障害フォルト状態、ULVO状態、FORCE状態が発生していないことを確認した後)。

- 0:3.3Vと12Vがディスエーブルになっています。

AUXA/B:このビットは、AUX電源の内部イネーブル状態を示します。

- 1:3.3V AUXがイネーブルされています。

- 0:3.3V AUXがディスエーブルされています。

VAUXFA/B: このビットは、VAUXA/Bで過電流障害(フォルト)状態が発生していることを示します。

- 1: VAUXA/Bで過電流状態(次のどちらかの状態)が発生 しています。

- 通常の過電流とタイムアウト

- 通常の過電流とTSHUT1

- 0:過電流状態が発生していません。

SMBusを使用してTPS2363をイネーブルにする場合、マスターによってこのビットをクリアする (ECHO RESET状態、つまりマスターによってこのビットに1を書き込む) 必要があります。この処理が完了すると、INTピンがデアサートされます (つまり "ハイ"になります)。

**12VFA/B:**このビットは、12V出力における過電流障害(フォルト)状態が発生していることを示します。

- 1:12V出力で過電流状態(次のいずれかの状態)が発生しています。

- 通常の過電流とタイムアウト

- 通常の過電流とTSHUT1

- 一 高速遮断

- 0:過電流状態が発生していません。

SMBusを使用してTPS2363をイネーブルにする場合、マスターによってこのビットをクリアする (ECHO RESET状態、つまりマスターによってこのビットに1を書き込む) 必要があります。この処理が完了すると、 $\overline{INT}$ ピンがデアサートされます(つまり"ハイ"になります)。

**3VFA/B:**このビットは、3.3V出力で過電流障害(フォルト)状態が発生していることを示します。

- 1:3.3V出力で過電流状態(次のいずれかの状態)が発生しています。

- 通常の過電流とタイムアウト

- 通常の過電流とTSHUT1

- 高速遮断

- 0:過電流状態が発生していません。

SMBusを使用してTPS2363をイネーブルにする場合、マスターによってこのビットをクリアする (ECHO RESET状態、つまりマスターによってこのビットに1を書き込む)必要があります。この処理が完了すると、INTピンがデアサートされます (つまり"ハイ"になります)。

#### 共通ステータス·レジスタ(06h):デフォルト00h

| GPI-B2 | GPI-A2 | GPI-B1 | GPI-A1 | INTMASK | UV_INT | OT_INT | RSVD |

|--------|--------|--------|--------|---------|--------|--------|------|

| R      | R      | R      | R      | R/W     | R/W    | R/W    | R    |

有効な書き込みコマンド:書き込みコマンドを使用して、 UVLO、otsd2による障害(フォルト)状態をクリアします。

● 00, 02, 04, 06, 08, 0a, 0c, 0e

**有効な読み取りコマンド:**0Y~fY(Yに入る値については、上 記の表に記載されている組み合わせを参照してください)。

**GPI\_B2/GPI\_A2/GPI\_B1/GPI\_A1:**これらのビットは、5msの デグリッチ時間後GPIxピンの状態を表します。

- 1: GPIA/Bピンは"ハイ"になっています。

- 0: GPIA/Bピンは "ロー" になっています。

- 1: INTピンがディスエーブルになっています。

- 0: INTピンがイネーブルになっています。

このビットが0で、いずれかのチャネルで障害(フォルト)が 発生している場合、INTピンは"ロー"になります。 UV\_INT: このビットは、メイン電源のみのUVLO状態を示します。このビットの状態は、メインのイネーブル・ピンまたはコントロール・レジスタのメインのイネーブル・ビットによって決まります。メイン電源がディスエーブルの場合、このビットは0になります。

- 1: UVLO障害(フォルト)が発生しています(電源はイネーブルです)。

- 0: UVLO障害(フォルト)が発生していません。電源電圧は UVLOスレッシュホールドを上回っています。

SMBusを使用する場合、このビットをリセットするにはエコー・リセットを使用します。

**OT\_INT:**チップにおけるTSHUT2状態を示します。

- 1:チップ温度 > 160℃

- 0:チップ温度 < 160℃

SMBusを使用する場合、このビットをリセットするにはエコー・リセットを使用します。

### ファンクション·レジスタ(07h):デフォルト:0dh

| П | LIM_AU XB | ILIM_AUXA | PWROFFB | PWROFFA | ILIM_MAINB | ILIM_MAINA | RSVD | TI* |

|---|-----------|-----------|---------|---------|------------|------------|------|-----|

|   | R/W       | R/W       | R       | R       | R/W        | R/W        | R    | 1   |

**有効な書き込みコマンド:**0dh ー デフォルト状態。A/Bスロットに電流制限をイネーブルします。

• 01, 05, 09, 4d, 41, 45, 49, 81, 85, 89, 8d, c1, c5, c9, cd

**有効な読み取りコマンド:**00hを除くすべての組み合わせが有 効です。

ILIM\_AUX\_B: このビットにより、 VAUX (スロットB) \*における電流制限のレベルを指定します。

- 1:高電流制限値(800 ~ 1500mA)。

- 0:低電流制限値(400~800mA)。

ILIM\_AUX\_A: このビットにより、 VAUX (スロットA) \*における電流制限のレベルを指定します。

- 1:高電流制限値 (800 ~ 1500mA)。

- 0:低電流制限値(400 ~ 800mA)。

\*出力電流モードは、ILIM\_AUX\_A/BとAUXHIA/BピンをOR 演算した結果により決まります。AUXHIA/Bがプルアップされる場合、ILIM\_AUX\_A/Bを使って低い電流制限モードを選択することはできません。

PWROFF\_B:チャネルBにおける電源オフ状態を示します。

- 1:VAUXB電源およびBチャネルのメイン電源の出力が 100mV未満です。

- 0:VAUXB電源とBチャネルのメイン電源のどちらか、あるいは両方で出力が100mVを超えています。

PWROFF\_A:チャネルAにおける電源オフ状態を示します。

- 1: VAUXA電源およびAチャネルのメイン電源の出力が 100mV未満です。

- 0:VAUXA電源とAチャネルのメイン電源のどちらか、あるいは両方で出力が100mVを超えています。

ILIM\_MAIN\_B (アクティブ・ロー) :このビットは、電流制限 がチャネルBのメイン電源でイネーブルになっているかどうか を示します。

- 1:高速遮断と通常の電流制限がイネーブルになっています。(これがデフォルト・モードです。)

- 0:高速遮断はイネーブルになっていますが、電流制限は ディスエーブルになっています。

ILIM\_MAIN\_A (アクティブ・ロー) :このビットは、電流制限がチャネルAのメイン電源でイネーブルになっているかどうかを示します。

- 1: 高速遮断と通常の電流制限がイネーブルになっていま す。(これがデフォルト・モードです。)

- 0:高速遮断はイネーブルになっていますが、電流制限は ディスエーブルになっています。

**TI:** "1"は、これがTI TPS2363であり、有効なレジスタであることを示します。

図 15.3.3V電源で過電流が発生した場合(FAULTとPGOOD)

図 16.3.3Vで過電流が発生した場合(Gate)

図 17.3.3Vで短絡が発生した場合

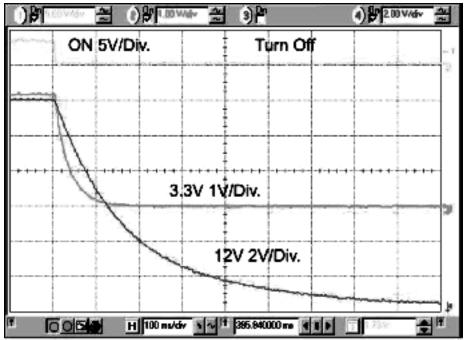

図 18. メイン電圧をオンにしたとき

図 19. メイン電圧をオフにしたとき

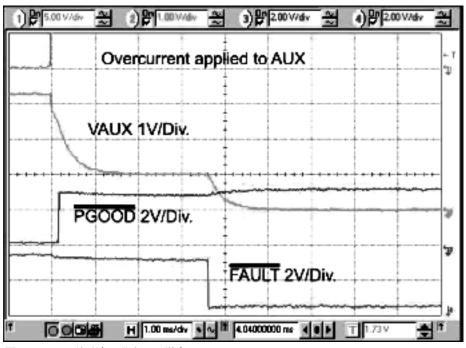

図 20. AUXで過電流が発生した場合

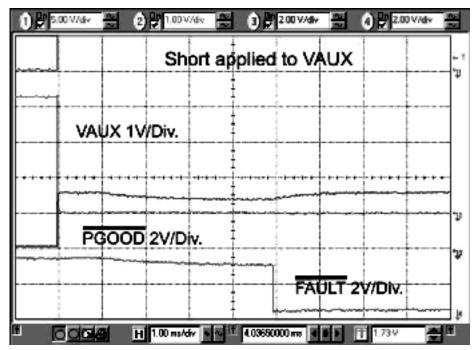

図 21. AUXで短絡が発生した場合

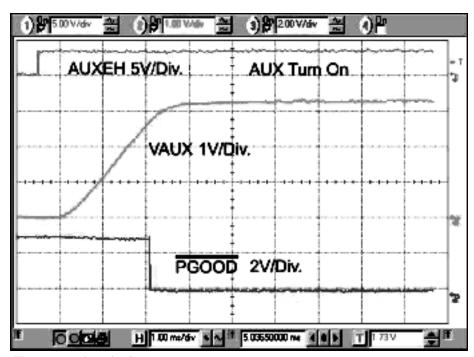

図 22. AUXイネーブルをオンにしたとき

図 23. AUXディスエーブル(オフ)にしたとき

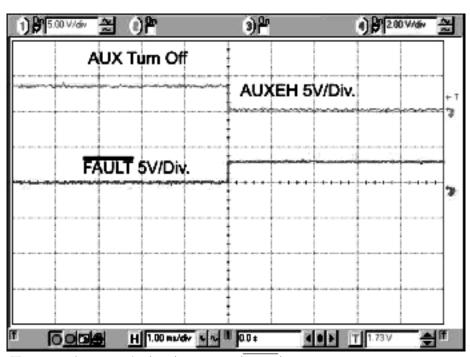

図 24. AUXディスエーブル (オフ) にしたとき (FAULT)

図 25. 12Vで過電流が発生した場合

図 26. 12Vで短絡が発生した場合

注: A. 全ての線寸法の単位はミリメートルです。 B. 図は予告なく変更することがあります。 C. JEDEC MS-026に該当します。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上