TPS65313-Q1 JAJSIR5C - OCTOBER 2019 - REVISED OCTOBER 2023

# TPS65313-Q1 VIN 範囲の広い車載アプリケーション向けのパワー・マネージ メントに

#### 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み: - デバイス温度グレード 1:-40℃~+125℃、TA

- ASIL-C (ISO 26262)/SIL-2 (IEC 61508) に準じたシ ステム・レベルの機能安全性要件に対応

- 同期整流降圧プリレギュレータ (BUCK1)

- 4V~36Vの入力電圧範囲

- 最大 3.1A の出力電流

- 工場で選択可能な出力電圧:3.3V または 3.6V

- 同期整流降圧レギュレータ (BUCK2)

- 固定入力電圧:3.3V または 3.6V

- 最大 2A の出力電流

- 工場で選択可能な出力電圧:1.2V、1.25V、1.8V、 または 2.3V

- 同期整流昇圧コンバータ (BOOST)

- 3.3V または 3.6V の固定入力電圧

- 最大 600mA の出力電流

- 5V の出力電圧

- フェーズ・ロック・ループ (PLL)

- 2.2MHz 前後の出力周波数

- SYNC IN ピンで変調または非変調の外部クロック をサポート

- すべてのレギュレータ用

- ソフトスタート機能

- 独立した電圧監視と診断機能

- 過電流、過負荷、過電圧、低電圧、熱保護

- ループ補償内蔵

- レギュレータのスイッチング・クロック用に適応型ランダ ム化スペクトラム拡散 (ARSS)変調を内蔵

- OFF 状態の静止電流 3µA

- SPI による制御および診断

- 2 つの汎用外部電圧モニタ

- MCU または DSP 用の Q&A ウォッチドッグおよびリセ ット・スーパバイザを内蔵

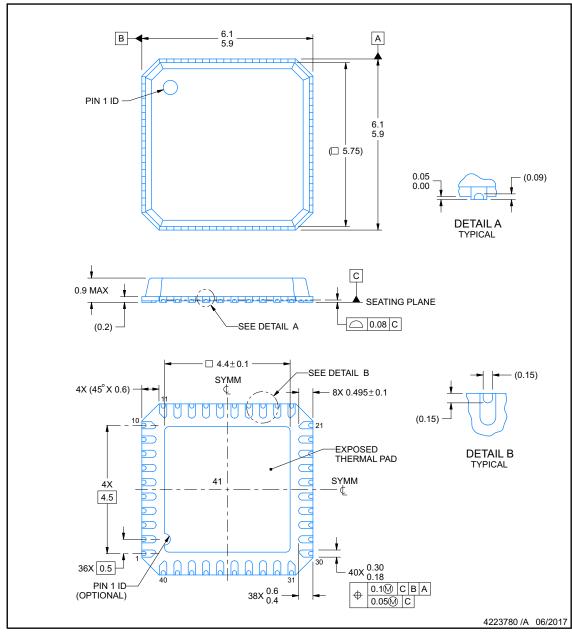

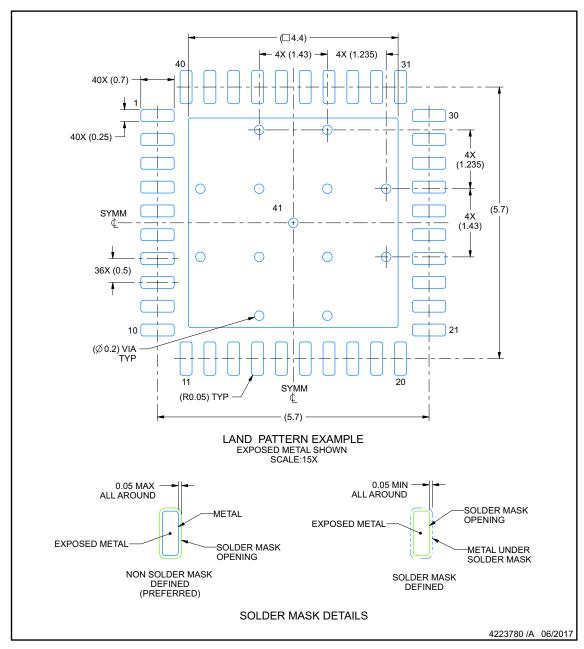

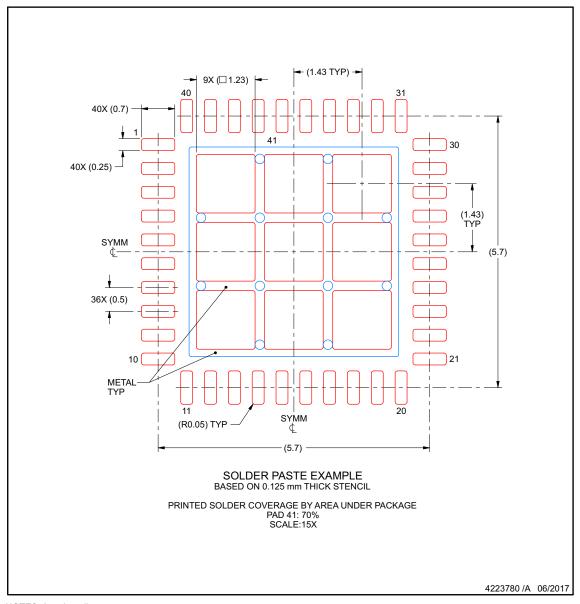

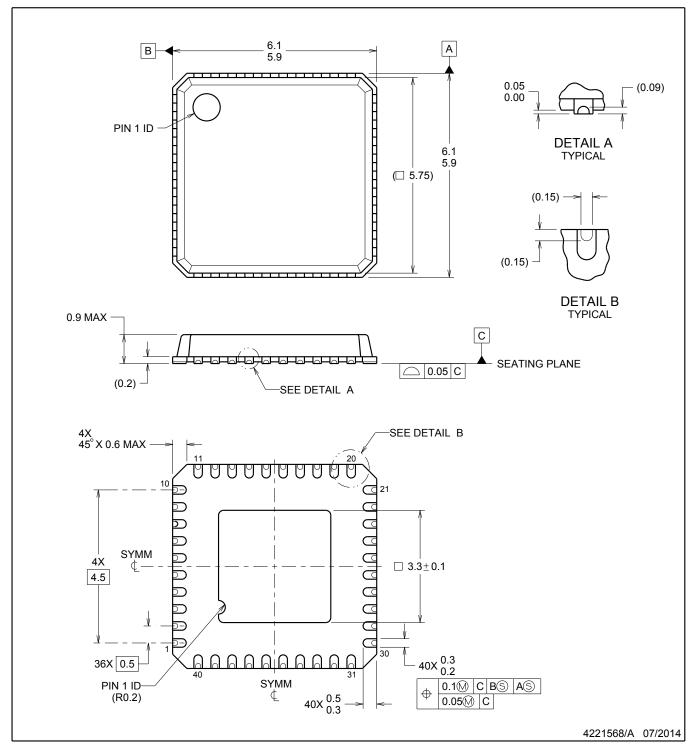

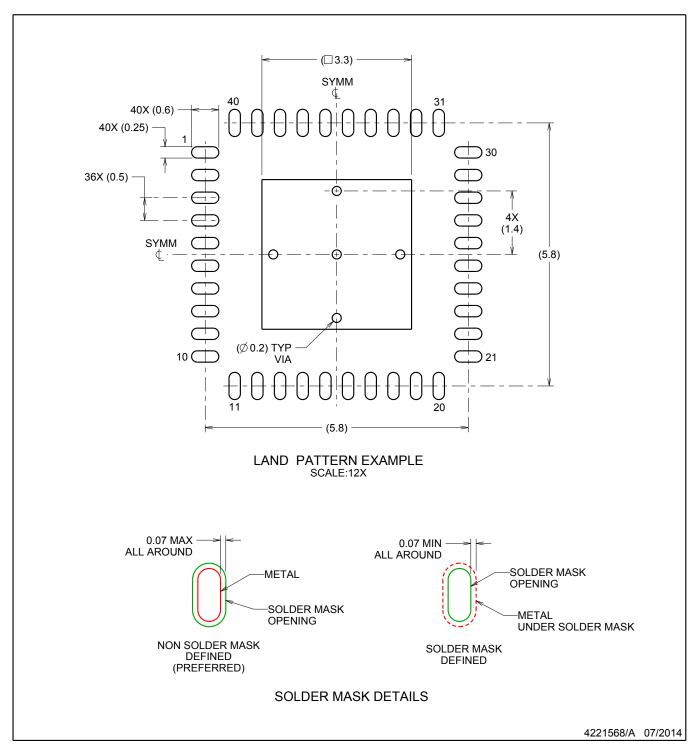

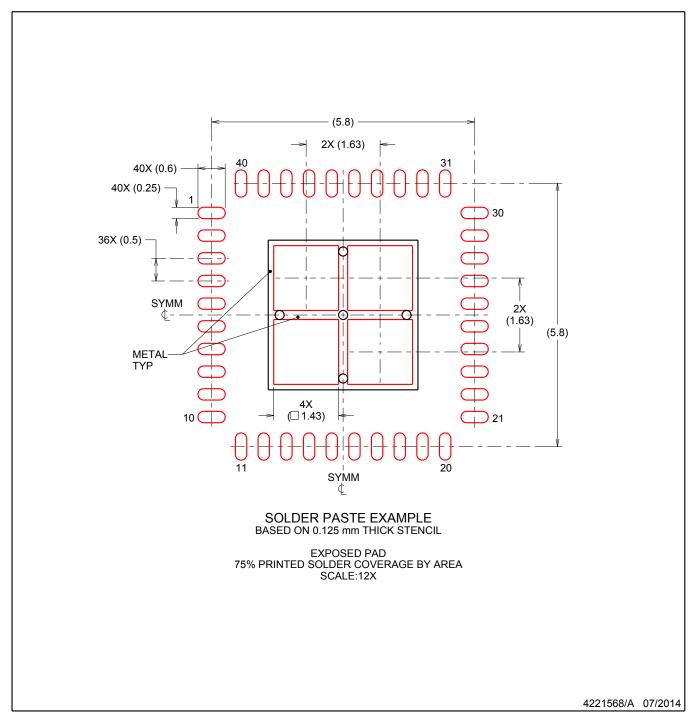

- 熱的に強化された 40 ピン、0.5mm ピッチの VQFNP パッケージ

# 2 アプリケーション

- 車載用レーダーおよびカメラ・アプリケーション

- 車載用センサ・フュージョン・アプリケーション

- 産業用レーダー・アプリケーション

- ビルディングおよびファクトリ・オートメーション・アプリケ ーション

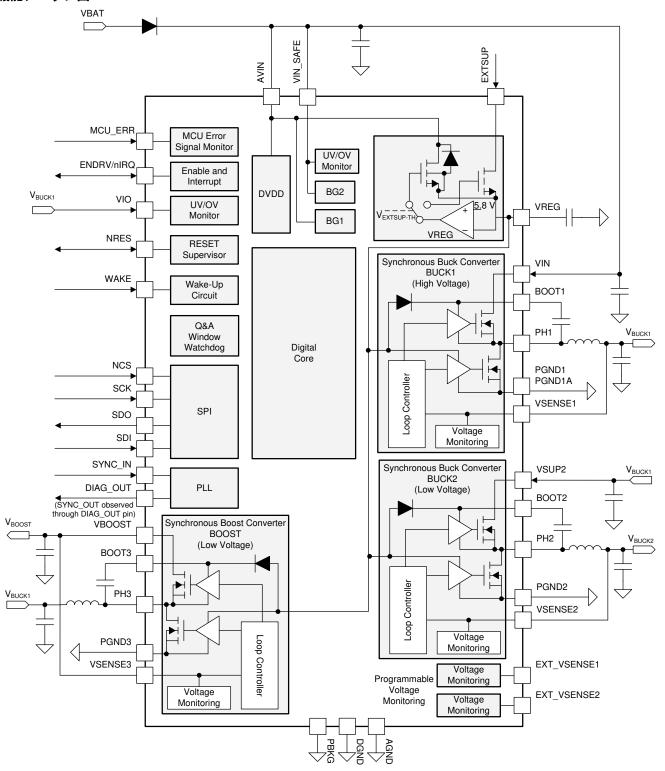

# 3 概要

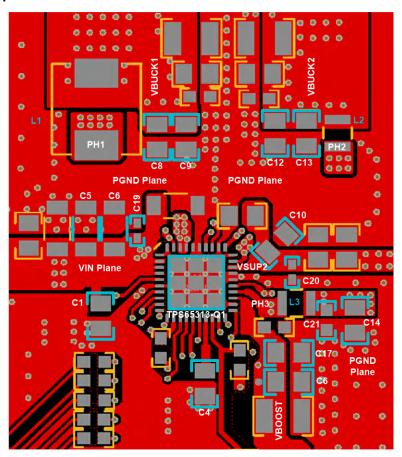

TPS65313-Q1 デバイスは電力管理 IC (PMIC)で、MCU 制御または DSP 制御の車載用、工業用、機械、または輸 送システムの要件を満たしています。このデバイスには一 般的に使用される機能が統合されているため、基板面積 とシステムのコストを削減するのに役立ちます。™

このデバイスには、1 つの VIN 範囲が広い同期整流降圧 レギュレータ (BUCK1)、1 つの低電圧 (LV) 降圧レギュレ ータ (BUCK2)、および VIN 範囲の広い降圧レギュレータ (BUCK1) から給電される 1 つの昇圧コンバータ (BOOST) が搭載されています。このデバイスは、OFF 状 態の静止電流が小さいのが特長で、システムが恒久的に 電源に接続されている場合、消費電流が減少します。す べての出力は、過電圧、過負荷、過熱状態から保護され ています。

#### 製品情報

| 部品番号        | パッケージ <sup>(1) (2)</sup> | 本体サイズ (公称)      |  |  |

|-------------|--------------------------|-----------------|--|--|

| TPS65313-Q1 | VQFNP (40)               | 6.00mm × 6.00mm |  |  |

- 利用可能なすべてのパッケージについては、データシートの末尾 (1) にある注文情報を参照してください。

- 2 ビットの 16 進数のデバイス構成値は、DEV ID レジスタにマッ (2) プされます。

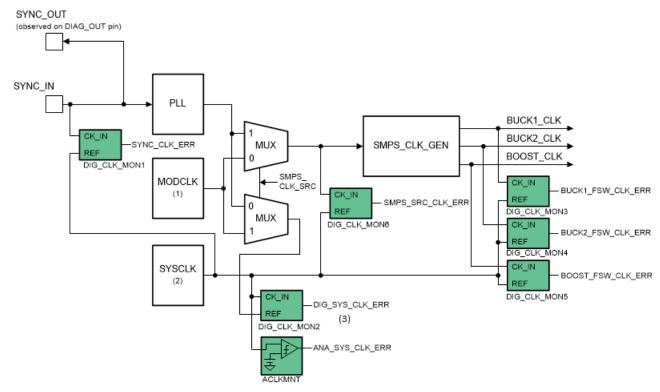

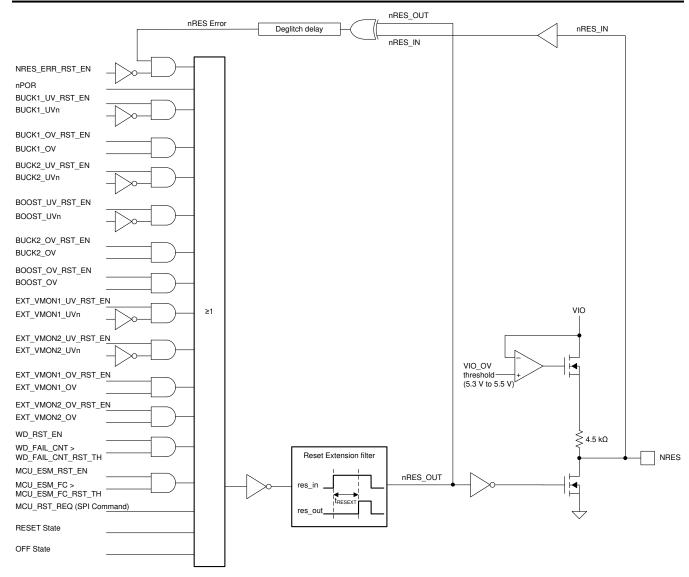

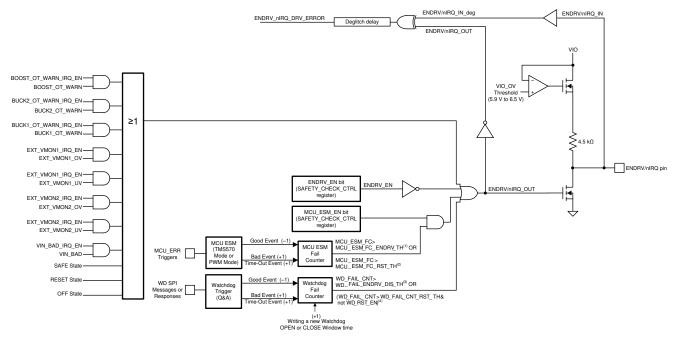

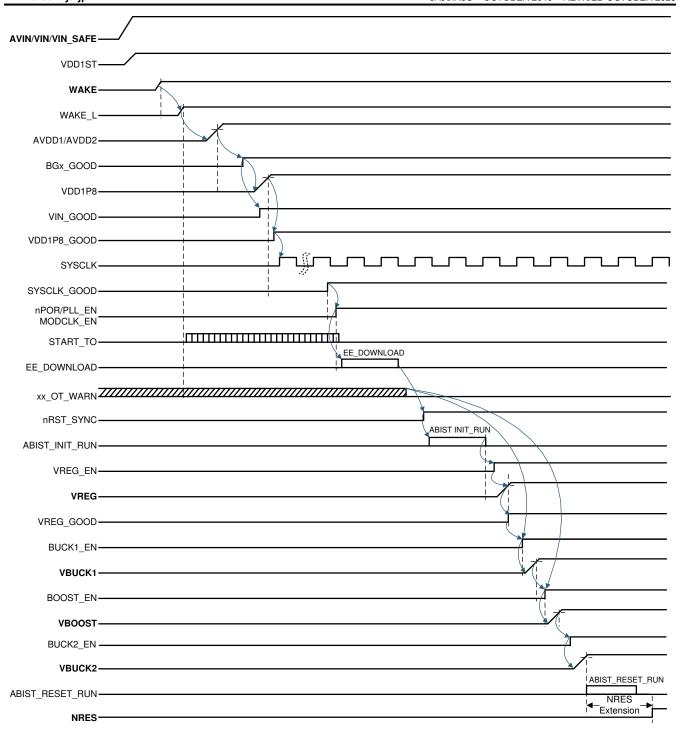

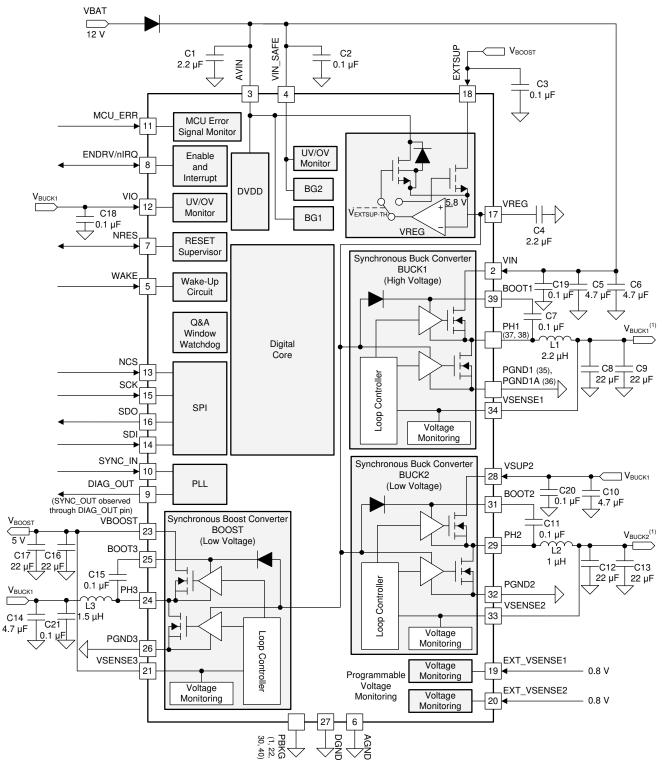

# 4 デバイスの機能ブロック図

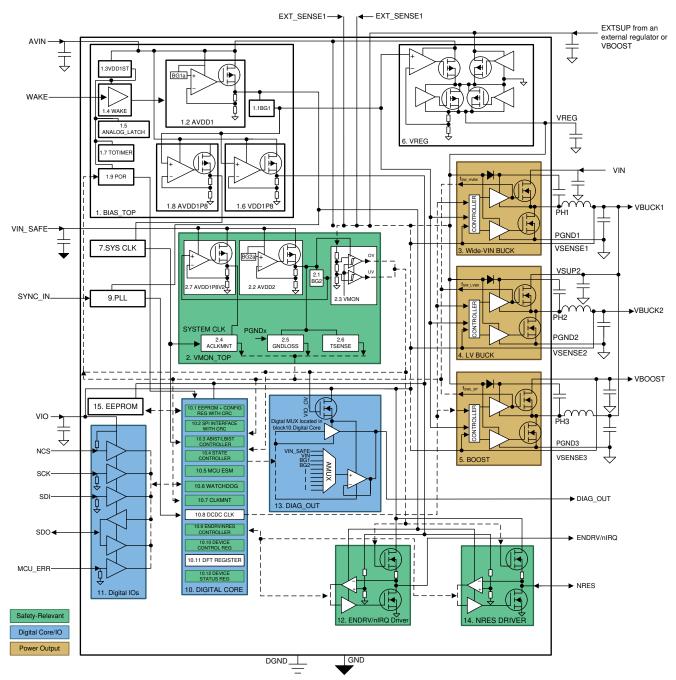

# 機能ブロック図

図 4-1. デバイスの機能ブロック図

# **Table of Contents**

| I 特長                                                 | 1   | 9.21 SPI Timing Requirements                         | 19  |

|------------------------------------------------------|-----|------------------------------------------------------|-----|

| 2 アプリケーション                                           |     | 9.22 SPI Characteristics                             | 19  |

| 3 概要                                                 |     | 9.23 Typical Characteristics                         | 20  |

| <b>1</b> デバイスの機能ブロック図                                |     | 10 Parameter Measurement Information                 | 25  |

| 5 Revision History                                   |     | 11 Detailed Description                              |     |

| 5 概要 (続き)                                            |     | 11.1 Overview                                        | 27  |

| 7 Device Option Table                                |     | 11.2 Functional Block Diagram                        | 28  |

| B Pin Configuration and Functions                    | 6   | 11.3 Wide-VIN Buck Regulator (BUCK1)                 | 28  |

| 9 Specifications                                     |     | 11.4 Low-Voltage Buck Regulator (BUCK2)              | 32  |

| 9.1 Absolute Maximum Ratings                         |     | 11.5 Low-Voltage Boost Converter (BOOST)             | 35  |

| 9.2 ESD Ratings                                      |     | 11.6 VREG Regulator                                  | 38  |

| 9.3 Recommended Operating Conditions                 |     | 11.7 BUCK1, BUCK2, and BOOST Switching Clocks        |     |

| 9.4 Thermal Information                              |     | and Synchronization (SYNC_IN) Clock                  | 38  |

| 9.5 Power-On-Reset, Current Consumption, and         | 9   | 11.8 BUCK1, BUCK2, and BOOST Switching-Clock         |     |

| State Timeout Characteristics                        | 0   | Spread-Spectrum Modulation                           | 44  |

| 9.6 PLL/Oscillator and SYNC IN Pin Characteristics   |     | 11.9 Monitoring, Protection and Diagnostics Overview |     |

| 9.7 Wide-VIN Synchronous Buck Regulator (Wide-       | 10  | 11.10 General-Purpose External Supply Voltage        |     |

| VIN BUCK) Characteristics                            | 10  | Monitors                                             | 95  |

|                                                      | 10  | 11.11 Analog Wake-up and Failure Latch               |     |

| 9.8 Low-Voltage Synchronous Buck Regulator (LV       | 44  | 11.12 Power-Up and Power-Down Sequences              | 98  |

| BUCK) Characteristics                                | 11  | 11.13 Device Fail-Safe State Controller (Monitoring  |     |

| Characteristics                                      | 12  | and Protection)                                      | 100 |

| 9.10 Internal Voltage Regulator (VREG)               | 13  | 11.14 Wakeup                                         | 106 |

| Characteristics                                      | 1.1 | 11.15 Serial Peripheral Interface (SPI)              |     |

| 9.11 Voltage Monitors for Regulators Characteristics |     | 11.16 Register Maps                                  |     |

| 9.12 External General Purpose Voltage Monitor        | 14  | 12 Applications, Implementation, and Layout          | 164 |

| Characteristics                                      | 16  | 12.1 Application Information                         |     |

| 9.13 VIN and VIN SAFE Under-Voltage and Over-        | 10  | 12.2 Typical Application                             |     |

| _ ~                                                  | 16  | 12.3 Power Supply Coupling and Bulk Capacitors       |     |

| Voltage Warning Characteristics                      |     | 13 Device and Documentation Support                  | 187 |

| 9.15 NRES (nRESET) Output Characteristics            |     | 13.1 Documentation Support                           | 187 |

| 9.16 ENDRV/nIRQ Output Characteristics               |     | 13.2 ドキュメントの更新通知を受け取る方法                              |     |

| 9.17 Analog DIAG_OUT                                 |     | 13.3 サポート・リソース                                       |     |

| 9.18 Digital INPUT/OUTPUT IOs (SPI Interface IOs,    | 17  | 13.4 Trademarks                                      |     |

| DIAG OUT/SYNC OUT, MCU ERROR)                        | 10  | 13.5 静電気放電に関する注意事項                                   |     |

| 9.19 BUCK1, BUCK2, BOOST Thermal Shutdown /          | 10  | 13.6 用語集                                             |     |

| Over Temperature Protection Characteristics          | 18  | 14 Mechanical, Packaging, and Orderable              | 101 |

| 9.20 PGNDx Loss Detection Characteristics            |     | Information                                          | 189 |

| 3.20 1 GINDA LUSS DELECTION CHARACTERSTICS           | 13  | invillation                                          | 100 |

# **5 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (March 2020) to Revision C (October 2023)                                                 | Page             |

|-------------------------------------------------------------------------------------------------------------------|------------------|

|                                                                                                                   | 1                |

| · Deleted digital system clock monitor slow clock error detection and fast clock error detection specifica        | tion14           |

| Added note to      11-4                                                                                           |                  |

| Updated text                                                                                                      | 45               |

| Added table note to 表 11-2                                                                                        | 48               |

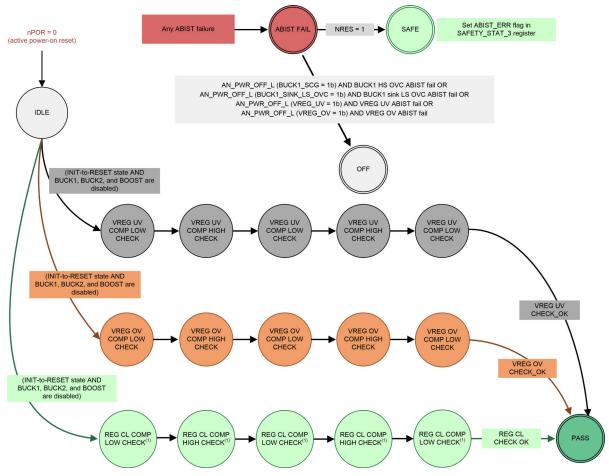

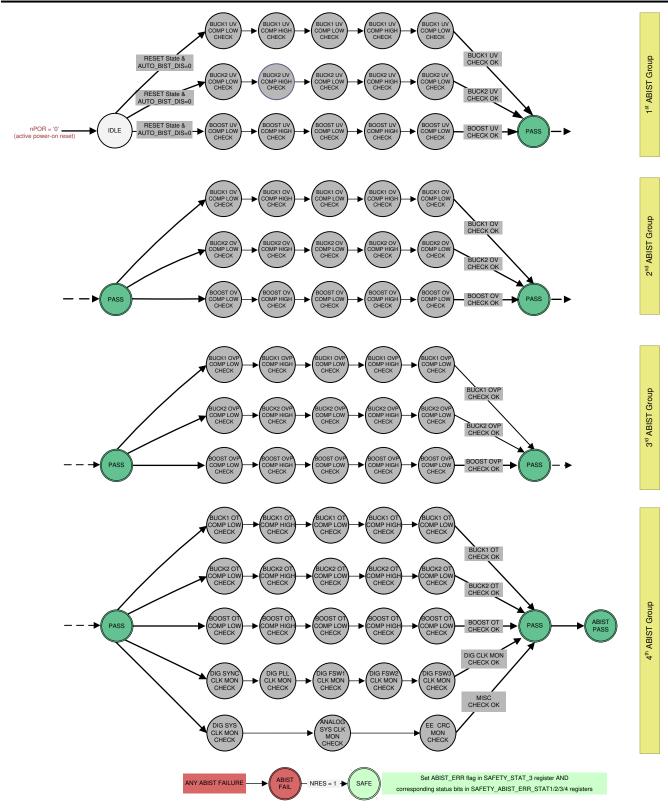

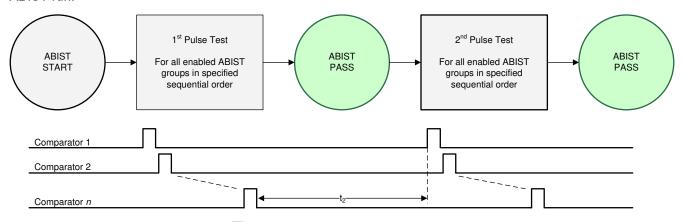

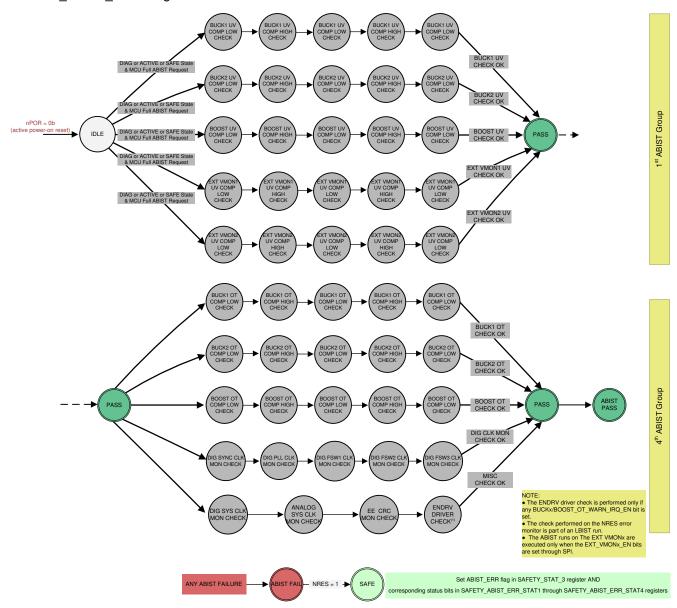

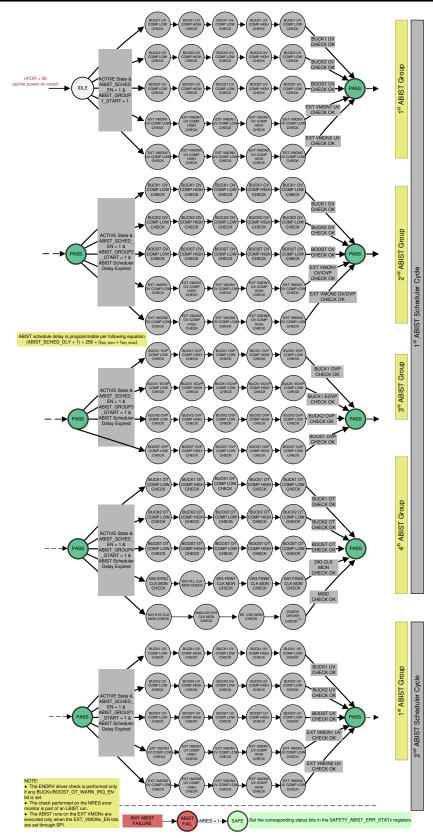

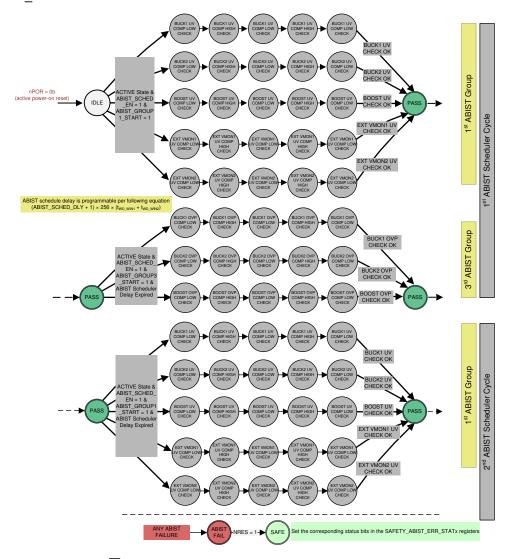

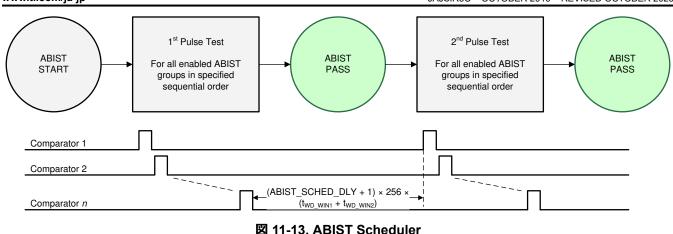

| Added more information to this topic to more clearly explain the ABIST function                                   | <mark>5</mark> 3 |

| Updated WD_ANSWER_RESP_0 to WD_ANSWER_RESP_1 in 図 11-17                                                           | 72               |

| • Updated content in 表 11-10                                                                                      | 74               |

| <ul> <li>Changed "inversion enabled" to "inversion not enabled" to reflect the actual device operation</li> </ul> | 94               |

| <ul> <li>Added descriptive information to the setting EE_CRC_ERR bit in SAFETY_ERR_STAT1 during EEPR</li> </ul>   | ROM              |

| CRC diagnostic test run                                                                                           | 95               |

|                                                                                                                   |                  |

TPS65313-Q1 JAJSIR5C – OCTOBER 2019 – REVISED OCTOBER 2023

| <ul><li>データシートの最初の公開リリース</li></ul>                                                              |      |

|-------------------------------------------------------------------------------------------------|------|

| Changes from Revision A (September 2018) to Revision B (March 2020)                             | Page |

| Added note to SAFETY_LBIST_CTRL Register Field Descriptions                                     | 113  |

| Added note to SAFETY_CLK_STAT Register Field Descriptions table                                 |      |

| · Changed "inversion enabled" to "inversion not enabled" to reflect the actual device operation |      |

| Updated 図 11-34                                                                                 | 100  |

| • Changed "inversion enabled" to "inversion not enabled" to reflect the actual device operation | 95   |

# 6 概要 (続き)

独立の監視および保護機能を持つ、すべてのレギュレートされる電源出力は、ASIL-C/SIL-2 のシステム・レベル機能安全性要件に対応できます。潜在的なフォルトを防止するための必須およびプログラム可能診断機能 (アナログおよびロジックの組み込み自己テスト) も含まれています。 デバイスにはプログラム可能なスーパバイザ、ウォッチドッグ機能、MCUまたは DSP のエラー・ピン監視機能も内蔵されています。

5

# 7 Device Option Table

| OPTION VALUE (1)                                                                                                     | BUCK1           | BUCK2                              | f <sub>SW</sub> MODULATION | EXT_VMON1 ENABLED<br>AT POWER-UP | EXT_VMON2 ENABLED<br>AT POWER-UP | DEFAULT NRES<br>EXTENSION DELAY |

|----------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------|----------------------------|----------------------------------|----------------------------------|---------------------------------|

| For device 2-bit hexadecimal option value and configuration setting refer to device Technical Reference Manual (TRM) | 3.6 V and 3.3 V | 1.2 V, 1.25 V, 1.8<br>V, and 2.3 V | Internal and External      | YES and NO                       | YES and NO                       | LONG and SHORT                  |

<sup>(1) 2-</sup>bit hexadecimal device configuration value is mapped to the DEV\_ID register.

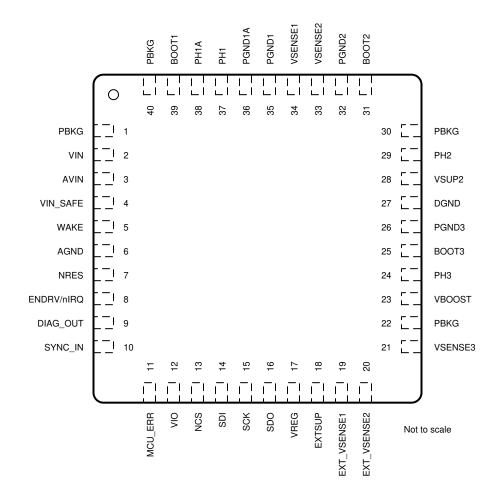

# 8 Pin Configuration and Functions

☑ 8-1 shows the 40-pin RWG Plastic Quad Flatpack - No Lead Outline.

図 8-1. 40-Pin RWG VQFNP (Top View)

Product Folder Links: TPS65313-Q1

資料に関するフィードバック(ご意見やお問い合わせ) を送信

Copyright © 2023 Texas Instruments Incorporated

# 表 8-1. Pin Attributes

|     | PIN <sup>(1)</sup> |      |                                                                                                                                                             |  |  |

|-----|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME               | TYPE | DESCRIPTION                                                                                                                                                 |  |  |

| 1   |                    |      |                                                                                                                                                             |  |  |

| 22  |                    |      |                                                                                                                                                             |  |  |

| 30  | PBKG               | GND  | Die substrate. Connect this pin to the system ground.                                                                                                       |  |  |

| 40  |                    |      |                                                                                                                                                             |  |  |

| 2   | VIN                | PWR  | Supply input for the BUCK1.                                                                                                                                 |  |  |

| 3   | AVIN               | PWR  | Supply input for the internal reference and supply-rail generations for the output voltage regulations.                                                     |  |  |

| 4   | VIN SAFE           | ı    | Supply input for monitoring circuits.                                                                                                                       |  |  |

| 5   | WAKE               | ı    | Wake-up input                                                                                                                                               |  |  |

| 6   | AGND               | GND  | Analog ground                                                                                                                                               |  |  |

| 7   | NRES               | I/O  | Active-low reset output to the system MCU or warm reset input from the system MCU. If pin is not used it can be left open since it has an internal pull up. |  |  |

| 8   | ENDRV/nIRQ         | I/O  | Enable drive output for external peripherals or interrupt output for system MCU. If pin is not used it can be left open since it has an internal pull up.   |  |  |

| 9   | DIAG_OUT           | 0    | Diagnostic output (analog MUX and digital MUX output). If pin is not used it can be left open.                                                              |  |  |

| 10  | SYNC_IN            | I    | PLL input clock. If pin is not used it can be left open since it has an internal pull down.                                                                 |  |  |

| 11  | MCU_ERR            | I    | MCU error-signal input. If pin is not used it can be left open since it has an internal pull down.                                                          |  |  |

| 12  | VIO                | PWR  | IO supply input for the digital interface pins from and to the system MCU.                                                                                  |  |  |

| 13  | NCS                | I    | Active-low SPI pin for the chip-select input. If pin is not used it can be left open since it has an internal pull up.                                      |  |  |

| 14  | SDI                | I    | SPI pin for the slave-data input. If pin is not used it can be left open since it has an internal pull down.                                                |  |  |

| 15  | SCK                | I    | SPI pin for the clock input. If pin is not used it can be left open since it has an internal pull down.                                                     |  |  |

| 16  | SDO                | 0    | SPI pin for the slave-data output (push-pull output). If this pin is not used, then it can be left open.                                                    |  |  |

| 17  | VREG               | 0    | Internal regulator output for the high-side and low-side gate drivers.                                                                                      |  |  |

| 18  | EXTSUP             | PWR  | External low-voltage supply input for the VREG. If pin is not used it has to be connected to GND.                                                           |  |  |

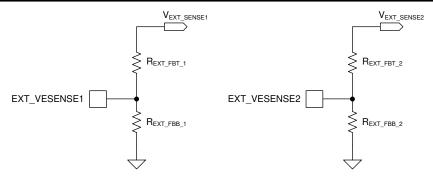

| 19  | EXT_VSENSE1        | I    | External general-purpose voltage monitor input 1. If pin is not used it has to be connected to GND.                                                         |  |  |

| 20  | EXT_VSENSE2        | I    | External general-purpose voltage monitor input 2. If pin is not used it has to be connected to GND.                                                         |  |  |

| 21  | VSENSE3            | I    | BOOST external sense-voltage input                                                                                                                          |  |  |

| 23  | VBOOST             | PWR  | BOOST output                                                                                                                                                |  |  |

| 24  | PH3                | 0    | Switch node of the BOOST converter                                                                                                                          |  |  |

| 25  | воот3              | I    | Bootstrap supply for the BOOST high-side FET driver circuit. A 100-nF capacitor (minimum) is required between the BOOT3 and PH3 pins.                       |  |  |

| 26  | PGND3              | GND  | BOOST power ground                                                                                                                                          |  |  |

| 27  | DGND               | GND  | Ground for the digital circuitry                                                                                                                            |  |  |

| 28  | VSUP2              | PWR  | BUCK2 supply input                                                                                                                                          |  |  |

| 29  | PH2                | 0    | Switch node of the BUCK2 regulator                                                                                                                          |  |  |

| 31  | BOOT2              | 1    | Bootstrap supply for the BUCK2 high-side FET driver circuit. A 100-nF capacitor (minimum) is required between the BOOT2 and PH2 pins.                       |  |  |

| 32  | PGND2              | GND  | BUCK2 power ground                                                                                                                                          |  |  |

| 33  | VSENSE2            | I    | BUCK2 external sense-voltage input                                                                                                                          |  |  |

| 34  | VSENSE1            | I    | BUCK1 external sense-voltage input                                                                                                                          |  |  |

| 35  | PGND1              | GND  | BUCK1 power ground                                                                                                                                          |  |  |

| 36  | PGND1A             | GND  | BUCK1 power ground                                                                                                                                          |  |  |

| 37  | PH1                | 0    | Switch node of the BUCK1 regulator                                                                                                                          |  |  |

| 38  | PH1A               | 0    | Switch node of the BUCK1 regulator                                                                                                                          |  |  |

| 39  | BOOT1              | 1    | Bootstrap supply for the BUCK1 high-side FET driver circuit. A 100-nF capacitor (minimum) is required between the BOOT1 and PH1 or the PH1A pins.           |  |  |

| _   | Thermal Pad        | GND  | Connect to the thermal pad to the printed circuit board (PCB) ground planes using multiple vias for good thermal performance.                               |  |  |

(1) I = input, O = output, I/O = input and output, PWR = power, GND = ground.

# 9 Specifications

# 9.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted).(1)

| GROUP                    | PIN NAME                                                                         | MIN               | MAX                    | UNIT |

|--------------------------|----------------------------------------------------------------------------------|-------------------|------------------------|------|

|                          | VIN, AVIN, VIN_SAFE                                                              | -0.3              | 40                     | V    |

| Cumply Inputs            | VSUP2                                                                            | -0.3              | 5.5                    | V    |

| Supply Inputs            | VBOOST                                                                           | -0.3              | 10                     | V    |

|                          | VIO, EXTSUP                                                                      | -0.3              | 5.5                    | V    |

|                          | BOOT1                                                                            | -0.3              | V <sub>PH1</sub> + 5.5 | V    |

| Wide-VIN BUCK Regulator  | PH1                                                                              | -1(3)             | 40                     | V    |

|                          | VSENSE1                                                                          | -0.3              | 5.5                    | V    |

|                          | BOOT2                                                                            | -0.3              | V <sub>PH2</sub> + 5.5 | V    |

| LV Buck Regulator        | PH2                                                                              | -1(3)             | 5.5                    | V    |

|                          | VSENSE2                                                                          | -0.3              | 5.5                    | V    |

|                          | VSENSE3                                                                          | -0.3              | 10                     | V    |

| Boost Converter          | воот3                                                                            | -0.3              | V <sub>PH3</sub> + 5.5 | V    |

|                          | PH3                                                                              | -1                | 10 <sup>(4)</sup>      | V    |

| Digital Interface        | NCS, SCK, SDO, SDI, MCU_ERR,<br>SYNC_IN, DIAG_OUT/<br>SYNC_OUT, NRES, ENDRV/nIRQ | -0.3              | 5.5                    | V    |

| Wake Input               | WAKE                                                                             | -7 <sup>(2)</sup> | 40                     | V    |

| General Purpose Monitors | EXT_VSENSE1/2                                                                    | -0.3              | 5.5                    | V    |

| Driver Supply Decoupling | VREG                                                                             | -0.3              | 5.5                    | V    |

| T D-4:                   | Junction temperature, T <sub>J</sub>                                             | -40               | 150                    | °C   |

| Temperature Ratings      | Storage temperature, T <sub>stg</sub>                                            | -55               | 165                    | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) I<sub>max</sub> = 40 mA max allowed current in substrate diode for t < 2 ms. For more negative voltage level series resistor is required.

- (3) -2V for 10 ns.

- (4) V<sub>BOOST</sub> + 2V for 10 ns

# 9.2 ESD Ratings

|        |  |                                       |                                                 | VALUE | UNIT |

|--------|--|---------------------------------------|-------------------------------------------------|-------|------|

|        |  | Human-body model (HBM), per AEC Q100- | 002 <sup>(1)</sup>                              | ±2000 |      |

| V(ESD) |  | Charged device model (CDM) nor AEC    | All pins                                        | ±500  | V    |

| (LOD)  |  | Q100-011                              | Corner pins (1, 10, 11, 20, 21, 30, 31, and 40) | ±750  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 9.3 Recommended Operating Conditions

| POS   |                                                                                                                                                                                                                        | MIN | NOM MAX | UNIT |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|

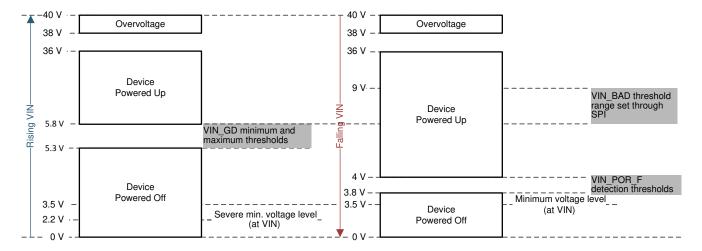

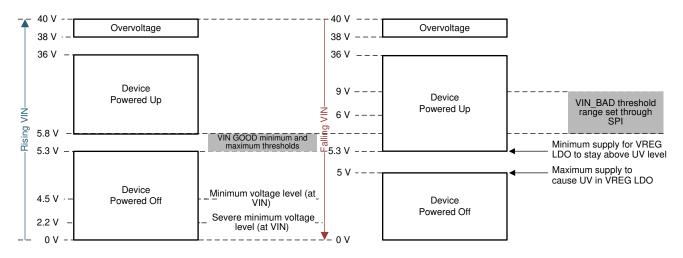

| R1.1  | Input supply voltage range on VIN, AVIN, and VIN_SAFE pins for initial power-up (startup from the OFF State) to one of the powered-up states (RESET, DIAGNOSTIC, ACTIVE, or SAFE state). <sup>(1)</sup>                | 5.8 | 36      | V    |

| R1.2a | Input supply voltage range on VIN, AVIN and VIN_SAFE pins to maintain the device in powered-up state when the BOOST converter (or other min 4.5 V external supply) supplies the EXTSUP pin. V <sub>BUCK1</sub> = 3.3 V | 4.0 | 36      | V    |

| R1.2b | Input supply voltage range on VIN, AVIN and VIN_SAFE pins to maintain the device in powered-up state when the BOOST converter (or other min 4.5 V external supply) supplies the EXTSUP pin. $V_{BUCK1}$ = 3.6 V        | 4.3 | 36      | V    |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

# 9.3 Recommended Operating Conditions (続き)

| POS   |                                                                                                                                                                  | MIN | NOM MAX | UNIT |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|

| R1.2c | Input supply voltage range on VIN, AVIN, and VIN_SAFE pins to maintain the device in powered-up state when there is no power supply connected to the EXTSUP pin. | 5.3 | 36      | V    |

| R1.3  | Input supply voltage range at which full device functionality and performance is assured                                                                         | 6   | 18      | V    |

| R1.4  | Input supply voltage range at which full device functionality is assured while some performance parameters may be compromised.                                   | 18  | 36      | V    |

| R1.5  | Input supply voltage range at which Wide-VIN Synchronous BUCK regulator is allowed to operate in a pulse-skipping mode.                                          | 25  | 36      | V    |

| R1.6  | VIO supply voltage                                                                                                                                               | 3   | 5.1     | V    |

| R1.7  | Operating free air temperature, T <sub>A</sub>                                                                                                                   | -40 | 125     | °C   |

<sup>(1)</sup> This initial voltage needs to be present for >100 ms and device must be started-up from the OFF State to one of the powered-up states (RESET, DIAGNOSTIC, ACTIVE or SAFE State) before battery voltage is allowed to drop to ranges specified in R1.2a

#### 9.4 Thermal Information

|                       |                                              | TPS65313-Q1 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RWG (VQFN)  | UNIT |

|                       |                                              | 40 PINS     | -    |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 24.2        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 15.5        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.8         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.2         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 6.7         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.5         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 9.5 Power-On-Reset, Current Consumption, and State Timeout Characteristics

VIN/AVIN/VIN\_SAFE = 4V to 36V,  $T_A = -40$ °C to 125°C,  $T_J$  up to 150°C, unless otherwise noted

| POS  | PARAMETER                  |                                                                                                                                | TEST CONDITIONS                                                                                                                                                           | MIN  | TYP | MAX  | UNIT |

|------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| 1.0a | V <sub>IN_POR_F</sub>      | Power On Reset assertion threshold                                                                                             | Falling VIN                                                                                                                                                               | 3.8  |     | 4.0  | V    |

| 1.0b | V <sub>IN_POR_R</sub>      | Power On Reset de-assertion threshold                                                                                          | Rising VIN                                                                                                                                                                | 5.3  |     | 5.8  | V    |

|      |                            |                                                                                                                                | T <sub>J</sub> = 25°C, all regulator outputs disabled, WAKE = 0 V, 2.3 V ≤ VIN/AVIN/VIN_SAFE ≤ 12 V                                                                       |      | 3   | 12   | μА   |

| 1.1  | I <sub>OFF</sub>           | Total current consumption in the OFF state from VIN, AVIN, and VIN_SAFE pins                                                   | T <sub>J</sub> = 125°C, all regulator outputs disabled,<br>WAKE = 0 V, 2.3 V ≤ VIN/AVIN/VIN_SAFE ≤ 12<br>V                                                                |      |     | 20   | μА   |

|      |                            | pins                                                                                                                           | T <sub>J</sub> = 150°C, all regulator outputs disabled,<br>WAKE = 0 V, 2.3 V ≤ VIN/AVIN/VIN_SAFE ≤ 12<br>V                                                                |      |     | 50   | μА   |

| 1.2a | I <sub>IN_PU</sub>         | Total current consumption in one of the powered-up state (RESET, DIAGNOSTIC, ACTIVE or SAFE) from VIN, AVIN, and VIN_SAFE pins | All regulators are enabled with 0 A load. VIN/<br>AVIN/VIN_SAFE = 14 V, VREG powered from<br>BOOST.                                                                       |      | 47  |      | mA   |

| 1.4  | t <sub>START_UP_TO</sub>   | Start-up/Power-up timeout interval                                                                                             | Measured from WAKE input rising edge until all switched-mode regulators are enabled. If regulators are not enabled in this time interval device transitions to OFF state. | 550  |     | 1700 | ms   |

| 1.5  | treset_state_to            | RESET state timeout interval                                                                                                   | Measured from the start of active RESET state condition until RESET state condition is removed and NRES extension is started                                              |      | 1.2 |      | s    |

| 1.6  | t <sub>DIAG_STATE_TO</sub> | DIAGNOSTIC state timeout interval                                                                                              | Measured from NRES rising edge until the device enters SAFE state                                                                                                         |      | 640 |      | ms   |

| 1.7  | tsafe_state_to             | SAFE state timeout interval range                                                                                              | Measured from time when the device enters SAFE state from DIAGNOSTIC or ACTIVE or RESET state and based on SAFE_TO [1:0] bits setting.                                    | 1.25 |     | 640  | ms   |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# 9.6 PLL/Oscillator and SYNC\_IN Pin Characteristics

| POS  |                             | PARAMETER                                                                                                | TEST CONDITIONS                                                                                            | MIN  | TYP  | MAX   | UNIT |

|------|-----------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|------|-------|------|

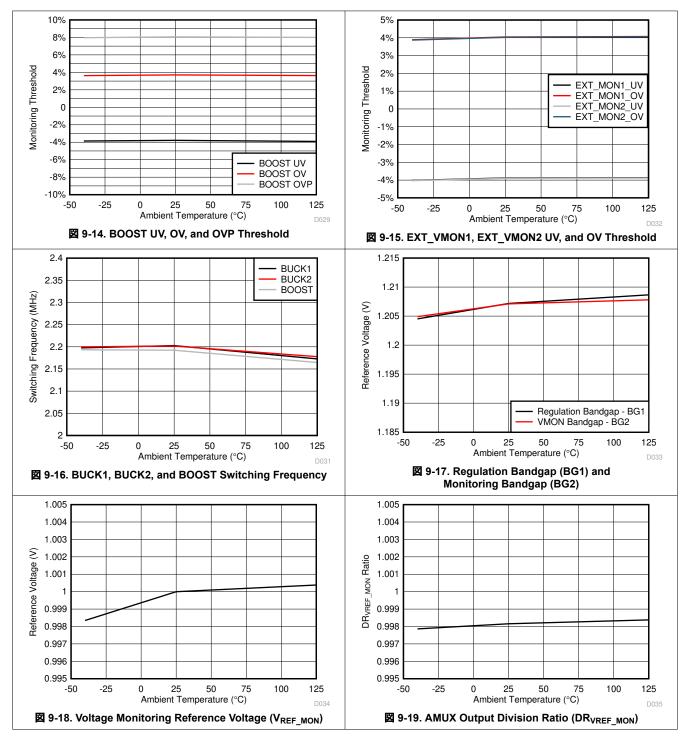

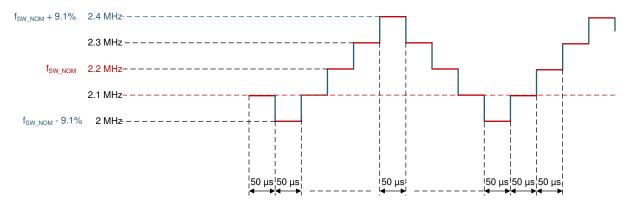

| 2.0b | f <sub>PLL_UNLOCK</sub>     | Free-running PLL output clock<br>frequency range as DC-DC converters<br>switching frequency clock source |                                                                                                            | 2.0  | 2.2  | 2.4   | MHz  |

| 2.1  | f <sub>PLL_LOCK</sub>       | PLL output clock frequency while synchronized to SYNC_IN input clock                                     |                                                                                                            | 2.0  | 2.2  | 2.4   | MHz  |

| 2.2  | D <sub>f/f</sub>            | Spread spectrum variation for internally generated and modulated around 2.2 MHz clock                    | Spread Spectrum type/mode for internally generated f <sub>SW</sub> clock is set through EEPROM mapped bits | 1.79 | 2.1  | 2.398 | MHz  |

| 2.3  | f <sub>SSM_STEP_INT_</sub>  | Internal clock spread spectrum modulation steps                                                          | fssm_step/fsw                                                                                              |      | 1.25 |       | %    |

| 2.4  | f <sub>DITHER_STEP_S</sub>  | SYNC_IN input clock dithering steps for 2.2 MHz of nominal frequency <sup>(1)</sup>                      | f <sub>DITHER_STEP</sub> /f <sub>SYNC_IN</sub> =100 kHz / 2.2 MHz                                          |      |      | 5     | %    |

| 2.5  | f <sub>PLL_UNLOCK_AC</sub>  | PLL Clock Output accuracy when VCO is in free-running mode.                                              |                                                                                                            | -5   |      | 5     | %    |

| 2.6  | f <sub>PLL_LOCK_ACC</sub>   | PLL Clock Output accuracy when PLL is locked to SYNC_IN input clock                                      |                                                                                                            | -1   |      | 1     | %    |

| 2.7  | t <sub>PLL_LOCK</sub>       | PLL Lock time <sup>(2)</sup>                                                                             | When SYNC_IN clock frequency changes from 0 Hz to 2.2 MHz ±5%                                              |      | 100  | 150   | μs   |

| 2.8  | V <sub>SYNC_HIGH_TH</sub> R | SYNC_IN clock input high level threshold                                                                 |                                                                                                            | 1.84 |      |       | V    |

| 2.9  | V <sub>SYNC_LOW_TH</sub> R  | SYNC_IN clock input low level threshold                                                                  |                                                                                                            |      |      | 0.76  | V    |

| 2.10 | D <sub>SYNC</sub>           | SYNC_IN clock input duty cycle                                                                           |                                                                                                            | 10   |      | 90    | %    |

| 2.13 | f <sub>SYSCLK</sub>         | System Clock Frequency                                                                                   |                                                                                                            | 7.6  | 8    | 8.4   | MHz  |

| 2.14 | f <sub>MODCLK</sub>         | Internal Modulation Clock Frequency                                                                      |                                                                                                            | 2.09 | 2.2  | 2.31  | MHz  |

- (1) The input SYNC\_IN clock can be modulated in a staircase (triangular) fashion step-by-step, with minimum step duration of 50 μs and clock frequency change of 50 kHz to 100 kHz.

- (2) After the PLL is locked, SYNC\_IN clock can change within ranges defined by f<sub>PLL\_LOCK</sub> with maximum frequency step defined by f<sub>DITHER\_STEP\_SYNC</sub>.

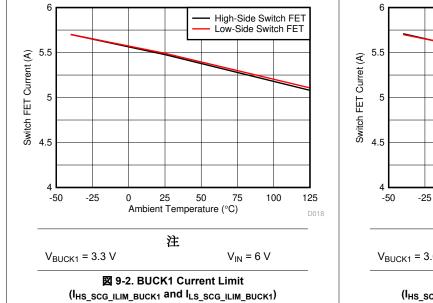

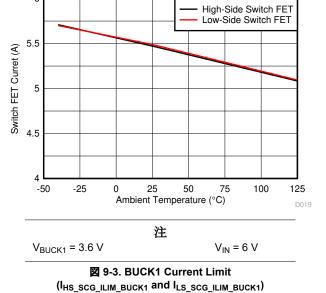

# 9.7 Wide-VIN Synchronous Buck Regulator (Wide-VIN BUCK) Characteristics

TA = -40°C to 125°C, TJ up to 150°C, unless otherwise noted. (1)

| POS   |                               | PARAMETER                                                                                                                                                              | TEST CONDITIONS                                                                                                                                                      | MIN  | TYP | MAX                    | UNIT |

|-------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------------------------|------|

| 3.0   | f <sub>SW_BUCK1</sub>         | Wide-VIN BUCK switching frequency                                                                                                                                      | 6V ≤ VIN/AVIN/VIN_SAFE<br>≤ 36V                                                                                                                                      | 2.0  | 2.2 | 2.4                    | MHz  |

| 3.1a  | VIN                           | Wide-VIN BUCK supply voltage                                                                                                                                           | V <sub>BUCK1</sub> = 3.3 V                                                                                                                                           | 4.0  |     | 36                     | V    |

| 3.1b  | VIN                           | Wide-VIN BUCK supply voltage                                                                                                                                           | V <sub>BUCK1</sub> = 3.6 V                                                                                                                                           | 4.3  |     | 36                     | V    |

| 3.2a  | V <sub>BUCK1</sub>            | Wide-VIN BUCK output voltage                                                                                                                                           |                                                                                                                                                                      |      | 3.3 |                        | V    |

| 3.2b  | V <sub>BUCK1</sub>            | Wide-VIN BUCK output voltage                                                                                                                                           |                                                                                                                                                                      |      | 3.6 |                        | V    |

| 3.3   | VBUCK1_DC_ACCUR               | Wide-VIN BUCK DC output voltage accuracy                                                                                                                               | 6 V ≤ VIN/AVIN/<br>VIN_SAFE ≤ 18 V,<br>measured at VSENSE1<br>pin <sup>(3)</sup>                                                                                     | -1.7 |     | 1.7                    | %    |

| 3.4a  |                               | Wide-VIN BUCK load current(2)                                                                                                                                          | min(VIN) ≤ VIN/AVIN/<br>VIN_SAFE ≤ 6V <sup>(4)</sup>                                                                                                                 |      |     | Refer to<br>Figure 9.5 | А    |

| J.4a  | IBUCK1_LOAD                   | Wide-VIIV BOOK load cullette                                                                                                                                           | 6 V ≤ VIN/AVIN/<br>VIN_SAFE ≤ 18 V                                                                                                                                   |      | 3.1 | Α                      |      |

| 3.5a  | V <sub>BUCK1_RIPPLE</sub>     | Wide-VIN BUCK output peak voltage ripple (0.5 × $V_{PP}$ ), in percentage of target regulation voltage                                                                 | $ 6 \text{ V} \leq \text{VIN/AVIN/} \\ \text{VIN\_SAFE} \leq 18 \text{ V,} \\ I_{\text{BUCK1\_LOAD}} = 0 \text{ A to} \\ \text{max} (I_{\text{BUCK1\_LOAD}})^{(3)} $ |      | 0.3 |                        | %    |

| 3.5b  | V <sub>BUCK1_RIPPLE_SS</sub>  | Wide-VIN BUCK output peak voltage ripple $(0.5 \times V_{PP})$ , in percentage of target regulation voltage, when $f_{SW}$ clock spread spectrum modulation is enabled | $ 6 \text{ V} \leq \text{VIN/AVIN/} \\ \text{VIN\_SAFE} \leq 18 \text{ V,} \\ I_{BUCK1\_LOAD} = 0 \text{ A to} \\ \text{max} (I_{BUCK1\_LOAD})^{(3)} $               |      | 0.3 |                        | %    |

| 3.6   | R <sub>DSON_HS_BUCK1</sub>    | ON resistance of high-side switch FET                                                                                                                                  | V <sub>GS</sub> =4.5V, I <sub>DS</sub> = 0.7A                                                                                                                        |      | 150 | 250                    | mΩ   |

| 3.7   | R <sub>DSON_LS_BUCK1</sub>    | ON resistance of low-side switch FET                                                                                                                                   | V <sub>GS</sub> =4.5V, I <sub>DS</sub> = 0.7A                                                                                                                        |      | 80  | 150                    | mΩ   |

| 3.10  | tss_buck1                     | Wide-VIN BUCK internal soft-start duration                                                                                                                             | Measured from Wide-VIN BUCK enable event to V <sub>BUCK1</sub> crossing its UV threshold. C <sub>BUCK1</sub> = 100 µF                                                |      | 1   |                        | ms   |

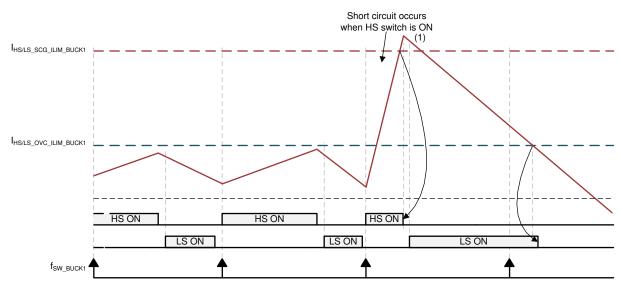

| 3.12a | I <sub>HS_SCG_ILIM_BUCK</sub> | High side switch current limit for weak-<br>short/hard-short conditions                                                                                                |                                                                                                                                                                      | 4    | 5.5 | 7                      | А    |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2023 Texas Instruments Incorporated

10

# 9.7 Wide-VIN Synchronous Buck Regulator (Wide-VIN BUCK) Characteristics (続き)

TA = -40°C to 125°C, TJ up to 150°C, unless otherwise noted. (1)

| POS   |                                                                  | PARAMETER                                                                                                                                                                                 | TEST CONDITIONS                                                                                                                                                             | MIN  | TYP  | MAX   | UNIT |

|-------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------|

| 3.12b | I <sub>HS_OVC_ILIM_BUCK</sub>                                    | High side switch current limit for over-load conditions.                                                                                                                                  |                                                                                                                                                                             |      | 3.8  | 5     | А    |

| 3.12c | I <sub>HS_SCG_ILIM_BUCK</sub> 1/ I <sub>HS_OVC_ILIM_BUCK</sub> 1 | Ratio between short-circuit current limit and over-load current limit for high-side switch                                                                                                |                                                                                                                                                                             |      | 1.43 |       | A/A  |

| 3.13a | I <sub>LS_SCG_ILIM_BUCK1</sub>                                   | Low side switch current limit for weak-<br>short/hard-short conditions                                                                                                                    |                                                                                                                                                                             | 4    | 5.5  | 7     | А    |

| 3.13b | I <sub>LS_OVC_ILIM_BUCK1</sub>                                   | Low side switch current limit for over-load conditions                                                                                                                                    |                                                                                                                                                                             |      | 3.8  | 5     | Α    |

| 3.13c | I <sub>LS_SCG_ILIM_BUCK1</sub> / I <sub>LS_OVC_ILIM_BUCK1</sub>  | Ratio between short-circuit current limit and over-load current limit for low-side switch                                                                                                 |                                                                                                                                                                             |      | 1.43 |       | A/A  |

| 3.14  | I <sub>LS_SINK_BUCK1</sub>                                       | Low side sinking current limit                                                                                                                                                            |                                                                                                                                                                             | -2.5 | -2   | -1.40 | Α    |

| 3.18a | R <sub>DISCH_BUCK1</sub>                                         | Wide-VIN BUCK internal discharge resistance when device is in RESET state                                                                                                                 | Wide-VIN BUCK disabled,<br>V <sub>BUCK1</sub> = 1 V                                                                                                                         | 100  | 180  | 400   | Ω    |

| 3.18b | R <sub>DISCH_BUCK1_OFF</sub>                                     | Wide-VIN BUCK internal discharge resistance when device is in OFF state                                                                                                                   | Wide-VIN BUCK disabled,<br>V <sub>BUCK1</sub> = 1 V                                                                                                                         | 400  | 800  | 1200  | Ω    |

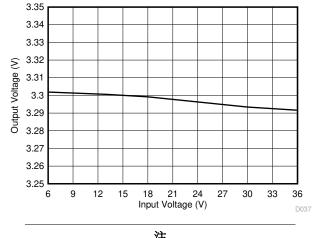

| 3.19  | ΔV <sub>BUCK1_LINEREG_</sub>                                     | Output voltage line regulation NOTE: DC line regulation as output voltage change in % ( $\Delta V_{BUCK1}$ / $V_{BUCK1}$ ) as VIN is changing from 6 V to 18 V                            | 6 V ≤ VIN/AVIN/<br>VIN_SAFE ≤ 18 V,<br>I <sub>BUCK1_LOAD</sub> = 1.5 A (3)                                                                                                  |      | 0.1  | 0.2   | %    |

| 3.20  | ΔV <sub>BUCK1_LOADREG</sub><br>_DCWide-VIN                       | Output voltage load regulation NOTE: DC load regulation as output voltage change in % ( $\Delta V_{BUCK1} / V_{BUCK1}$ ) as $I_{BUCK1\_LOAD}$ changes from 0A to max( $I_{BUCK1\_LOAD}$ ) | 6 V ≤ VIN/AVIN/<br>VIN_SAFE ≤ 18 V <sup>(3)</sup>                                                                                                                           |      | 0.1  | 0.2   | %    |

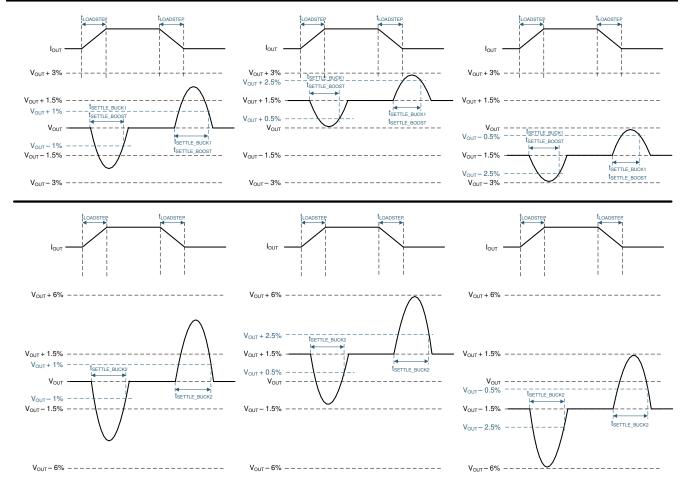

| 3.21a | VBUCK1_BUCK1_LOA<br>D_TRAN1                                      | Load transient regulation, in percentage of steady-state regulation voltage                                                                                                               | 6 V ≤ VIN/AVIN/<br>VIN_SAFE ≤ 18 V,<br>I <sub>BUCK1_LOAD</sub> load steps:<br>- 0.5 A to 1.5 A<br>- 1.5 A down to 0.5 A<br>dl <sub>BUCK1_LOAD</sub> /dt = 300 mA/<br>µs (3) | -3   |      | 3     | %    |

| 3.21b | VBUCK1_LOAD_TRA                                                  | Load transient regulation, in percentage of steady-state regulation voltage                                                                                                               | 6 V ≤ VIN/AVIN/<br>VIN_SAFE ≤ 18 V,<br>I <sub>BUCK1_LOAD</sub> load steps:<br>- 2 A to 3.1 A<br>dI <sub>BUCK1_LOAD</sub> /dt = 60 mA/<br>µs (3)                             | -3   |      | 3     | %    |

| 3.21c | VBUCK1_LOAD_TRA                                                  | Load transient regulation, in percentage of steady-state regulation voltage                                                                                                               | 6 V ≤ VIN/AVIN/<br>VIN_SAFE ≤ 18 V,<br>IBUCK1_LOAD load steps:<br>- 3.1 A to 1 A<br>dlBuCK1_LOAD/dt = 100 mA/<br>µs (3)                                                     | -3   |      | 3     | %    |

| 3.22  | tsettle_buck1                                                    | Load transient recovery time to 1% below starting point or 1% above starting point.                                                                                                       | Refer to 3.21a, 3.21b, and 3.21c.                                                                                                                                           |      |      | 20    | μs   |

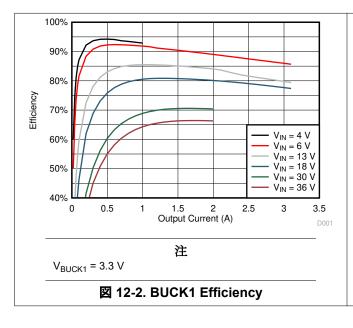

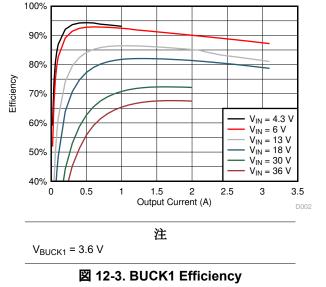

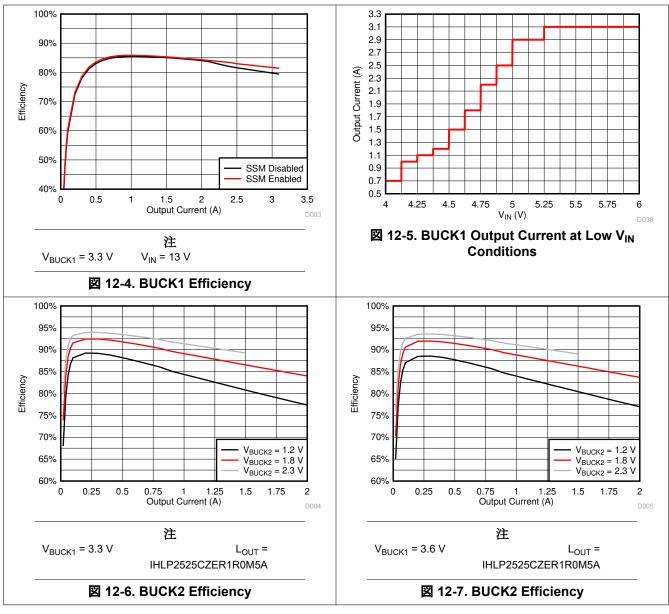

| 3.24a | <b>П</b> ВИСК1                                                   | Wide-VIN BUCK Efficiency                                                                                                                                                                  | VIN/AVIN/VIN_SAFE = 13<br>V, V <sub>BUCK1</sub> =3.3V,<br>I <sub>BUCK1</sub> _LOAD = 1.5 A<br>Other conditions covered<br>in efficiency plot diagram                        |      | 83   |       | %    |

| 3.26  | VBUCK1_RESTART_L                                                 | Wide-VIN BUCK output voltage level before ramp-up starts, in percentage of target regulation voltage                                                                                      | After wide-VIN BUCK regulator is shutdown its output voltage is discharged below this level before a new start-up event.                                                    |      |      | 45    | %    |

- (1) Total output capacitance, C<sub>BUCK1</sub>, including board parasitic capacitance, should not exceed 100 μF.

- (2) Advanced thermal design may be required to avoid thermal shutdown.

- (3) Refer to Regulator LC Selection table for inductor and capacitor values.

- (4) Some of the BUCK1 performance electrical parameters may not be met when VIN/AVIN/VIN\_SAFE ≤ 6.

# 9.8 Low-Voltage Synchronous Buck Regulator (LV BUCK) Characteristics

VIN/AVIN/VIN\_SAFE = 4 V to 36 V, TA = -40°C to 125°C, TJ up to 150°C, unless otherwise noted. (1)

| POS |                       | PARAMETER                   | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----|-----------------------|-----------------------------|-----------------|-----|-----|-----|------|

| 4.0 | f <sub>SW_BUCK2</sub> | LV BUCK switching frequency |                 | 2.0 | 2.2 | 2.4 | MHz  |

| 4.1 | V <sub>SUP2_NOM</sub> | LV BUCK supply voltage      |                 |     | 3.3 |     | V    |

Copyright © 2023 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

# 9.8 Low-Voltage Synchronous Buck Regulator (LV BUCK) Characteristics (続き)

VIN/AVIN/VIN SAFE = 4 V to 36 V, TA = -40°C to 125°C, TJ up to 150°C, unless otherwise noted. (1)

| POS   |                                 | PARAMETER                                                                                                                                                        | TEST CONDITIONS                                                                                                                                       | MIN  | TYP  | MAX  | UNIT |

|-------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 4.1   | V <sub>SUP2_NOM</sub>           | LV BUCK supply voltage                                                                                                                                           |                                                                                                                                                       |      | 3.6  |      | V    |

| 4.1a  | V <sub>SUP2</sub>               | LV BUCK supply voltage range, in percentage of V <sub>SUP2_NOM</sub>                                                                                             |                                                                                                                                                       | 94   |      | 106  | %    |

| 4.2   | V <sub>BUCK2</sub>              | LV BUCK output voltage                                                                                                                                           |                                                                                                                                                       |      | 1.2  |      | V    |

| 4.2   | V <sub>BUCK2</sub>              | LV BUCK output voltage                                                                                                                                           |                                                                                                                                                       |      | 1.25 |      | V    |

| 4.2   | V <sub>BUCK2</sub>              | LV BUCK output voltage                                                                                                                                           |                                                                                                                                                       |      | 1.8  |      | V    |

| 4.2   | V <sub>BUCK2</sub>              | LV BUCK output voltage                                                                                                                                           |                                                                                                                                                       |      | 2.3  |      | V    |

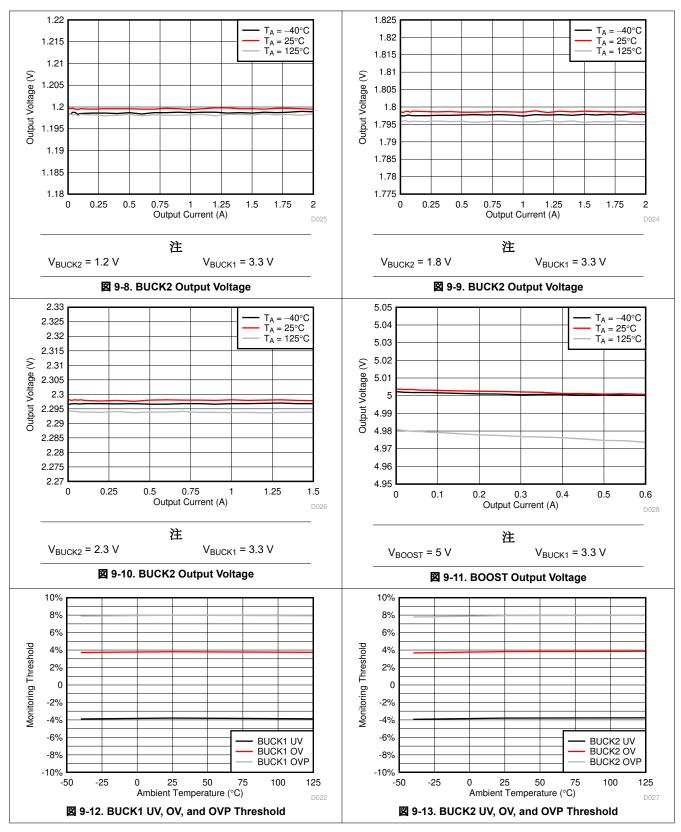

| 4.3   | VBUCK2_DC_ACCURACY              | LV BUCK DC output voltage accuracy                                                                                                                               | I <sub>BUCK2_LOAD</sub> = 0 A to max(I <sub>BUCK2_LOAD</sub> ),<br>measured at VSENSE2 pin <sup>(3)</sup>                                             | -1.5 |      | +1.5 | %    |

| 4.4a  | I <sub>BUCK2_LOAD</sub>         | LV BUCK load current <sup>(2)</sup>                                                                                                                              | VSUP2 = 3.3 V for V <sub>BUCK2</sub> = 1.2 V, 1.25 V, 1.8 V                                                                                           |      |      | 2    | Α    |

| 4.4b  | I <sub>BUCK2_LOAD</sub>         | LV BUCK load current <sup>(2)</sup>                                                                                                                              | VSUP2 = 3.3 V , V <sub>BUCK2</sub> = 2.3 V                                                                                                            |      |      | 1.5  | Α    |

| 4.5a  | V <sub>BUCK2_RIPPLE</sub>       | LV BUCK output peak voltage ripple $(0.5 \times V_{PP})$ , in percentage of target regulation voltage                                                            | I <sub>BUCK2_LOAD</sub> = max(I <sub>BUCK2_LOAD</sub> ) <sup>(3)</sup>                                                                                |      | 0.6  |      | %    |

| 4.5b  | V <sub>BUCK2_RIPPLE_SSM</sub>   | LV BUCK output peak voltage ripple $(0.5 \times V_{PP})$ , in percentage of target regulation voltage, when $f_{SW}$ spread spectrum clock modulation is enabled | I <sub>BUCK2_LOAD</sub> = max(I <sub>BUCK2_LOAD</sub> ) (3)                                                                                           |      | 0.6  |      | %    |

| 4.6   | I <sub>SUP_BUCK2_NO_LOAD</sub>  | LV BUCK no-load supply current                                                                                                                                   | I <sub>BUCK2_LOAD</sub> = 0 A <sup>(3)</sup>                                                                                                          |      | 3    | 6.5  | mA   |

| 4.7   | R <sub>DSON_HS_BUCK2</sub>      | ON resistance of high-side switch FET                                                                                                                            | V <sub>GS</sub> =4.5V, I <sub>DS</sub> = 1.0A                                                                                                         |      | 90   | 180  | mΩ   |

| 4.8   | R <sub>DSON_LS_BUCK2</sub>      | ON resistance of low-side switch FET                                                                                                                             | V <sub>GS</sub> =4.5V, I <sub>DS</sub> = 1.0A                                                                                                         |      | 110  | 220  | mΩ   |

| 4.11  | tss_Buck2                       | LV BUCK soft-start duration                                                                                                                                      | Measured from LV BUCK enable event to $V_{BUCK2}$ crossing its UV threshold. $C_{OUT}$ = 100 $\mu$ F                                                  |      | 0.85 |      | ms   |

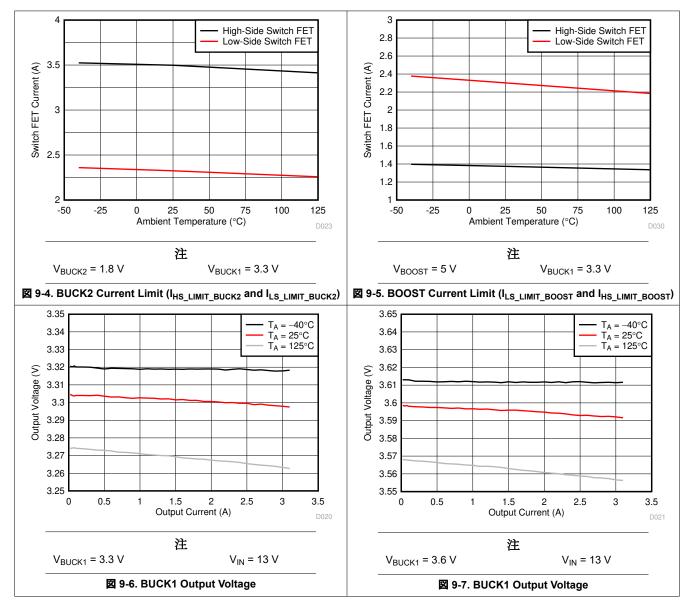

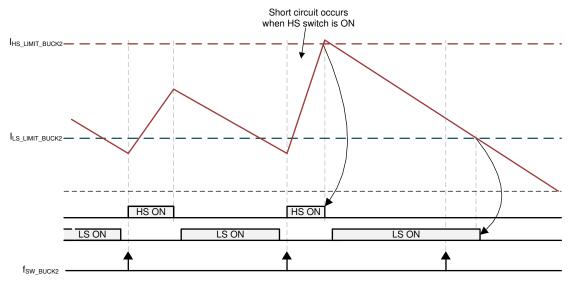

| 4.12  | I <sub>HS_LIMIT_BUCK2</sub>     | High-side switch current limit for weak-short/hard-short conditions                                                                                              |                                                                                                                                                       | 2.6  | 3.5  | 4.5  | Α    |

| 4.13  | I <sub>LS_LIMIT_BUCK2</sub>     | Low-side switch current limit for functional over-load conditions                                                                                                |                                                                                                                                                       | 2.1  | 2.7  | 3.3  | Α    |

| 4.14  | I <sub>LS_SINK_BUCK2</sub>      | Low-side switch sinking current limit                                                                                                                            |                                                                                                                                                       | -1.1 | -0.8 | -0.5 | Α    |

| 4.18a | R <sub>DISCH_BUCK2</sub>        | LV BUCK internal discharge resistance when the device is in RESET state                                                                                          | LV BUCK disabled, V <sub>BUCK2</sub> = 1 V                                                                                                            | 100  | 200  | 400  | Ω    |

| 4.18b | R <sub>DISCH_BUCK2_OFF</sub>    | LV BUCK internal discharge resistance when the device is OFF state                                                                                               | LV BUCK disabled, V <sub>BUCK2</sub> = 1 V                                                                                                            | 400  | 800  | 1200 | Ω    |

| 4.19  | ΔV <sub>BUCK2_LINEREG_DC</sub>  | Output voltage line regulation NOTE: DC line regulation as output voltage change in % ( $\Delta V_{BUCK2}$ / $V_{BUCK2}$ ) as $V_{SUP2}$ and to $V_{SUP2}$ Max   | 0.97 × V <sub>SUP2_NOM</sub> ≤ V <sub>SUP2</sub> ≤ 1.03 × V <sub>SUP2_NOM</sub> .   Buck2_Load = 1.5 A <sup>(3)</sup>                                 |      | 0.1  | 0.2  | %    |

| 4.20  | ΔV <sub>BUCK2_LOADREG_DC</sub>  | Output voltage load regulation NOTE: DC load regulation as output voltage change in % ( $\Delta V_{BUCK2}$ / $V_{BUCK2}$ ) as $I_{BUCK2}$ changes from 0A to 2A  | I <sub>BUCK2_LOAD</sub> = 0 A to max(I <sub>BUCK2_LOAD</sub> ) <sup>(3)</sup>                                                                         |      | 0.2  | 0.3  | %    |

| 4.21  | V <sub>BUCK2_LOAD_TRAN1</sub>   | LV BUCK load transient regulation, in percentage of steady-state regulation voltage                                                                              | I <sub>BUCK2_LOAD</sub> load step:<br>- 0.5 A to 1.5 A<br>- 1.5 A down to 0.5 A<br>dI <sub>BUCK2_LOAD</sub> /dt = 300 mA/μs                           | -6   |      | 6    | %    |

| 4.22  | tsettle_Buck2                   | Load transient recovery time to 1% below starting point, or 1% above starting point.                                                                             | l <sub>BUCK2_LOAD</sub> load step:<br>- 0.5 Å to 1.5 Å<br>- 1.5 Å down to 0.5 Å<br>dl <sub>BUCK2_LOAD</sub> /dt = 300 mÅ/µs                           |      |      | 20   | μs   |

| 4.24  | V <sub>BUCK2_RESTART_LEVE</sub> | LV BUCK output voltage level before ramp-up starts, in percentage of target regulation voltage                                                                   | NOTE: when there is a shutdown event<br>followed by new start-up event, device<br>cannot start-up again until LV BUCK2<br>discharges below this level |      |      | 45   | %    |

<sup>(1)</sup> Total output capacitance,  $C_{BUCK2}$ , including board parasitic capacitance, should not exceed 100  $\mu F$ .

English Data Sheet: SLDS222

<sup>(2)</sup> Advanced thermal design may be required to avoid thermal shutdown.

<sup>(3)</sup> Refer to Regulator LC Selection table for inductor and capacitor values.

# 9.9 Synchronous Boost Converter (BOOST) Characteristics

VIN/AVIN/VIN\_SAFE = 4 V to 36 V, TA = -40°C to 125°C, TJ up to 150°C, unless otherwise noted. (1)

| POS   |                                    | PARAMETER                                                                                                                                                               | TEST CONDITIONS                                                                                                                                     | MIN   | TYP | MAX   | UNIT |

|-------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| 5.0   | V <sub>SUP_BOOST_NOM</sub>         | BOOST supply voltage                                                                                                                                                    |                                                                                                                                                     |       | 3.3 |       | V    |

| 5.0   | V <sub>SUP_BOOST_NOM</sub>         | BOOST supply voltage                                                                                                                                                    |                                                                                                                                                     |       | 3.6 |       | V    |

| 5.0a  | V <sub>SUP_BOOST</sub>             | BOOST supply voltage range, in percentage of V <sub>SUP_BOOST_NOM</sub>                                                                                                 |                                                                                                                                                     | 94    |     | 106   | %    |

| 5.1   | V <sub>BOOST</sub>                 | Boost output voltage                                                                                                                                                    |                                                                                                                                                     |       | 5   |       | V    |

| 5.2   | f <sub>SW_BOOST</sub>              | BOOST switching frequency                                                                                                                                               |                                                                                                                                                     | 2.0   | 2.2 | 2.4   | MHz  |

| 5.3   | V <sub>BOOST_DC_ACCURAC</sub>      | BOOST DC output voltage accuracy                                                                                                                                        | I <sub>BOOST_LOAD</sub> = 0 A to max(I <sub>BOOST_LOAD</sub> ),<br>measured at VSENSE3 pin <sup>(3)</sup>                                           | -1.5  |     | 1.5   | %    |

| 5.4a  | V <sub>BOOST_RIPPLE</sub>          | BOOST output peak voltage ripple $(0.5 \times V_{PP})$ , in percentage of target regulation voltage                                                                     | $I_{BOOST\_LOAD} = max(I_{BOOST\_LOAD})^{(3)}$                                                                                                      |       | 0.3 |       | %    |

| 5.4b  | V <sub>BOOST_SSM_RIPPLE</sub>      | BOOST output peak voltage ripple $(0.5 \times V_{PP})$ , in percentage of target regulation voltage, when $f_{SW}$ clock modulation is enabled                          | $I_{BOOST\_LOAD} = max(I_{BOOST\_LOAD})^{(3)}$                                                                                                      |       | 0.3 |       | %    |

|       |                                    |                                                                                                                                                                         | I <sub>BOOST_LOAD</sub> load step #1                                                                                                                |       |     |       |      |

|       |                                    |                                                                                                                                                                         | • 520 mA to 600 mA                                                                                                                                  |       |     |       |      |

|       |                                    |                                                                                                                                                                         | • 600 mA down to 520 mA                                                                                                                             |       |     |       |      |

| 5.5   | V <sub>BOOST_LOAD_TRAN</sub>       | Load transient regulation, in percentage of steady-state                                                                                                                | I <sub>BOOST LOAD</sub> load step #2                                                                                                                | -3    |     | 3     | %    |

|       | -BOOST_LOAD_TRAIN                  | regulation voltage                                                                                                                                                      | • 60 mA to 140 mA                                                                                                                                   |       |     |       |      |

|       |                                    |                                                                                                                                                                         | • 140 mA to 60 mA                                                                                                                                   |       |     |       |      |

|       |                                    |                                                                                                                                                                         |                                                                                                                                                     |       |     |       |      |

|       |                                    |                                                                                                                                                                         | dl <sub>BOOST_LOAD</sub> /dt = 300 mA/μs                                                                                                            |       |     |       |      |

| 5.6   | tsettle_boost                      | Load transient recovery time to 1% below starting point or 1% above starting point.                                                                                     |                                                                                                                                                     |       |     | 20    | μs   |

| 5.7   | R <sub>DS_ON_HS_BOOST</sub>        | ON resistance of high-side switch FET                                                                                                                                   | V <sub>GS</sub> =4.5V, I <sub>DS</sub> = 1.0A                                                                                                       |       | 110 | 140   | mΩ   |

| 5.8   | R <sub>DS_ON_LS_BOOST</sub>        | ON resistance of low-side switch FET                                                                                                                                    | V <sub>GS</sub> =4.5V, I <sub>DS</sub> = 1.0A                                                                                                       |       | 210 | 350   | mΩ   |

| 5.10a | R <sub>DISCH_BOOST</sub>           | BOOST internal discharge resistance when the device is in powered states                                                                                                |                                                                                                                                                     | 100   | 200 | 400   | Ω    |

| 5.10b | R <sub>DISCH_BOOST_OFF</sub>       | BOOST internal discharge resistance when device is in OFF state                                                                                                         |                                                                                                                                                     |       | 800 |       | Ω    |

| 5.11  | tss_BOOST                          | BOOST internal soft-start duration                                                                                                                                      | Measured from BOOT enable event to $V_{BOOST}$ crossing its UV threshold. $C_{OUT}$ = 100 $\mu F$                                                   |       | 2   |       | ms   |

| 5.14a | I <sub>BOOST_LOAD</sub>            | BOOST load current(2)                                                                                                                                                   |                                                                                                                                                     |       |     | 600   | mA   |

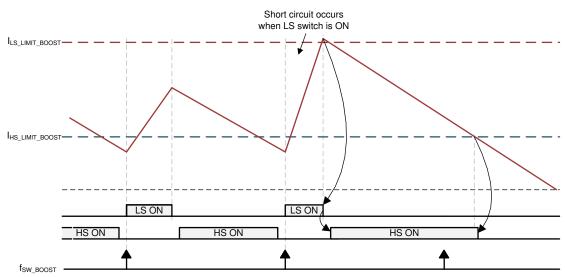

| 5.15  | I <sub>LS_LIMIT_BOOST</sub>        | Low-side switch source current limit (weak/short current limit)                                                                                                         |                                                                                                                                                     | 1.9   | 2.3 | 2.7   | А    |

| 5.16  | I <sub>HS_LIMIT_BOOST</sub>        | High-side switch source current limit                                                                                                                                   |                                                                                                                                                     | 1     | 1.4 | 1.8   | Α    |

| 5.17  | I <sub>CL_HS_SINK_BOOST</sub>      | Internal high-side switch sink current limit                                                                                                                            |                                                                                                                                                     | -1.30 |     | -0.75 | Α    |

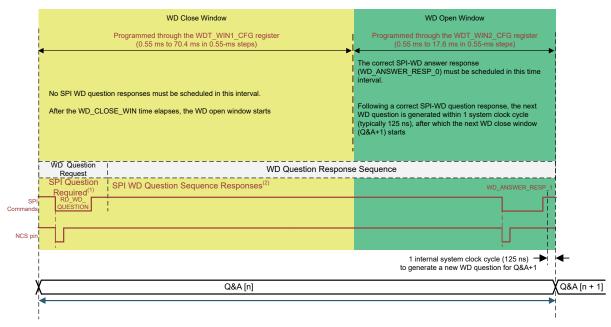

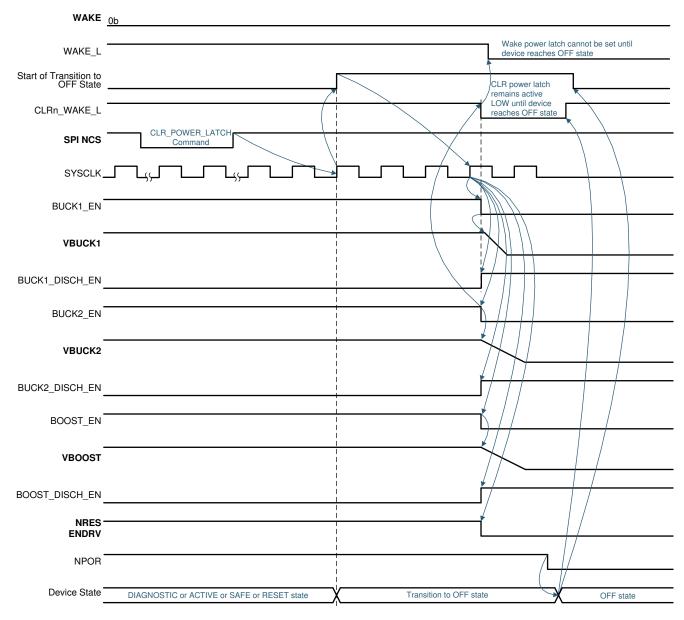

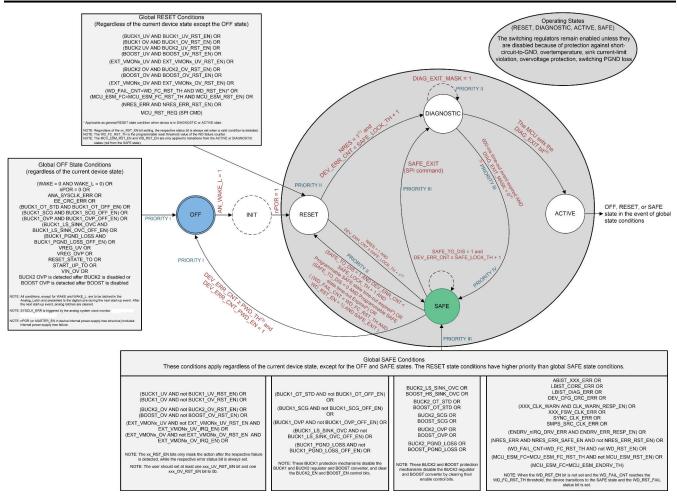

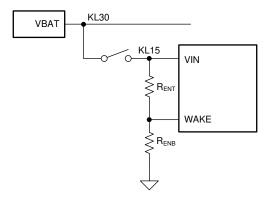

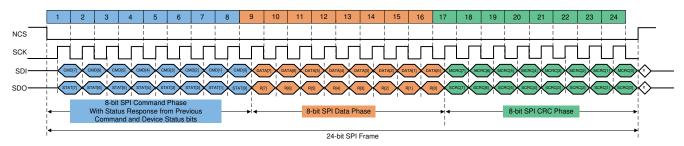

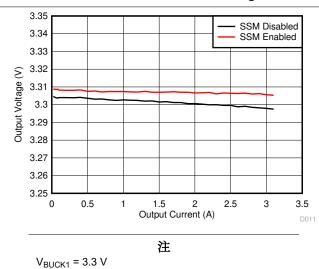

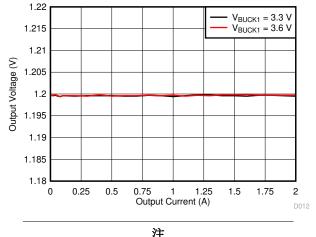

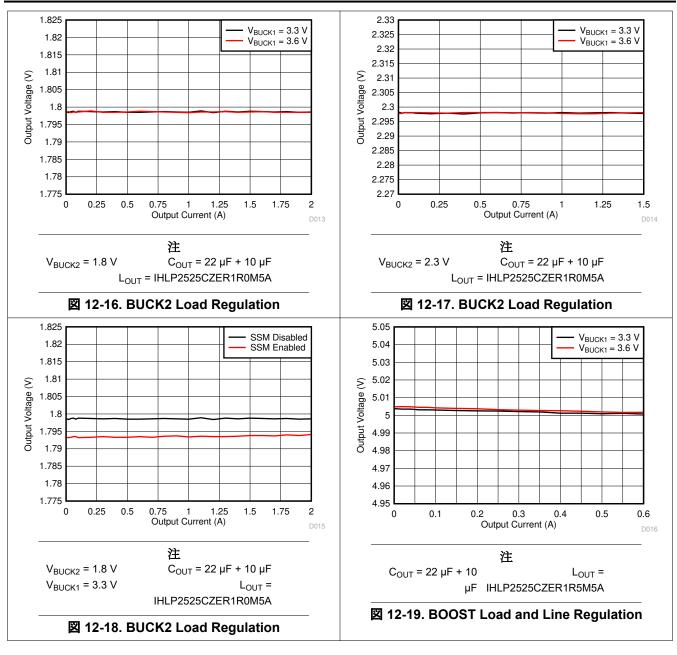

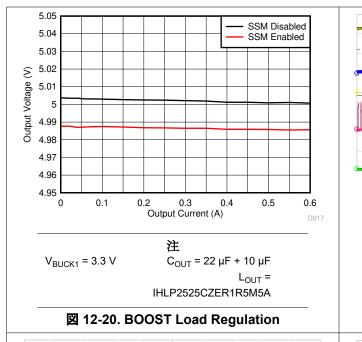

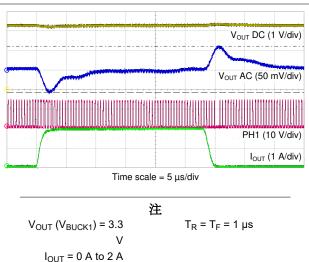

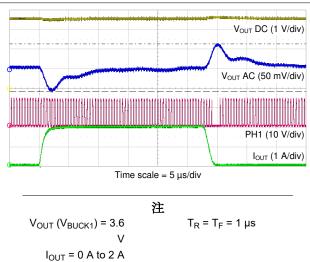

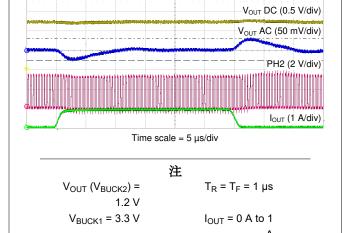

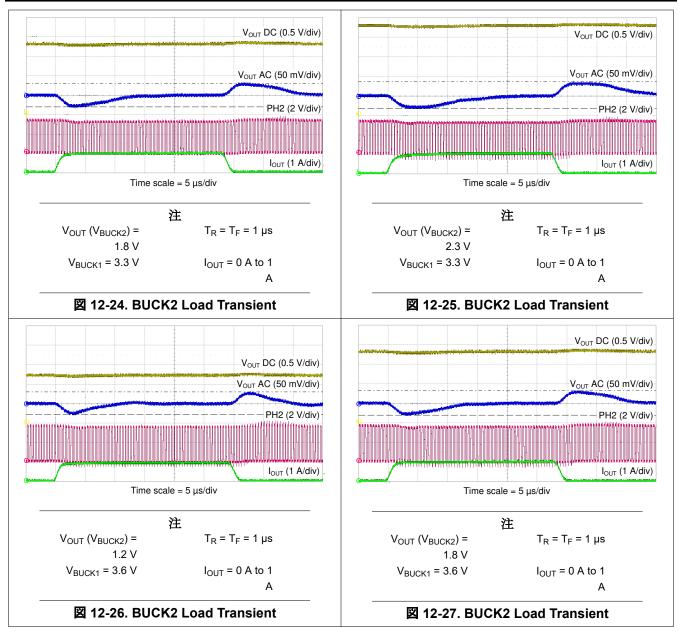

| 5.20  | VSUP_BOOST_NO_LOA                  | BOOST no-load supply current                                                                                                                                            | I <sub>BOOST_LOAD</sub> = 0 A                                                                                                                       |       | 7   | 8     | mA   |