Technical documentation

**TPS659128** JAJSLX5A - MAY 2021 - REVISED JUNE 2021

# TPS659128 PMU、プロセッサ電源用

# 1 特長

- 4 つの降圧コンバータ

- 入力電圧 (V<sub>IN</sub>) 範囲:2.7V~5.5V

- 軽負荷電流時のパワー・セーブ・モード

- PWM モード時の出力電圧精度:±2%

- コンバータごとの静止電流:26µA (標準値)

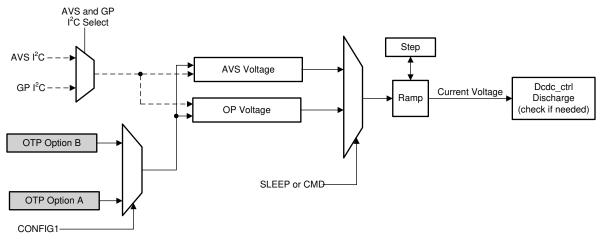

- ダイナミック電圧スケーリング

- 100% デューティ・サイクル動作による最小のドロッ プアウト電圧

- 10 個の LDO

- 8 つの汎用 LDO

- 出力電圧範囲:0.8V~3.3V

- LDO ごとの静止電流:32µA (標準値)

- 2 つの低ノイズ RF-LDO

- 出力電圧範囲:1.6V~3.3V

- 個別の電源入力によるプリレギュレーションのサポ ート

- Eco-mode<sup>™</sup> 制御方式

- 以下の V<sub>IN</sub> 電圧範囲に対応する LDO

- 1.8V~3.6V

- 3V∼5.5V

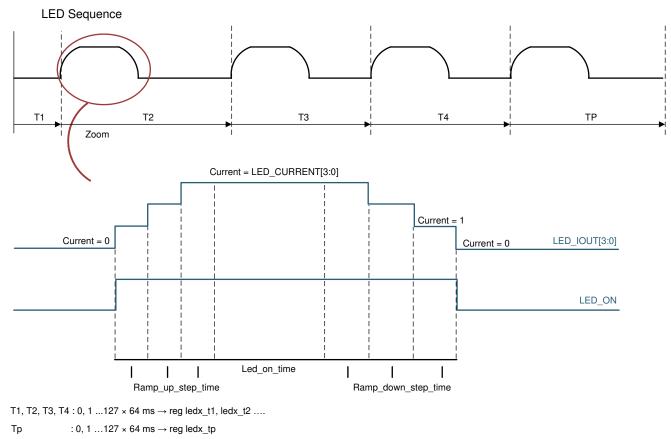

- 3 つの LED ドライバ

- I<sup>2</sup>C を利用した内蔵調光機能

- - 電流シンクごとに最大 20mA

- 温度監視

- 高温の警告

- サーマル・シャットダウン

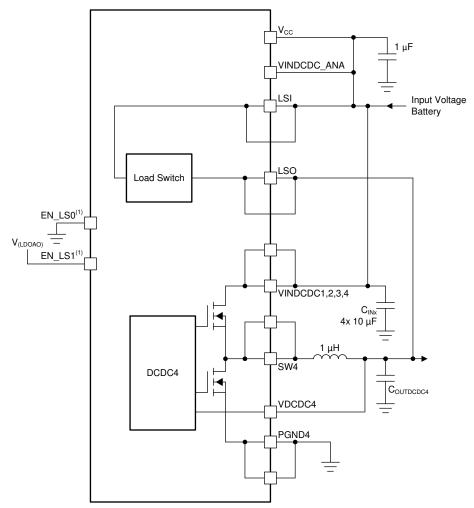

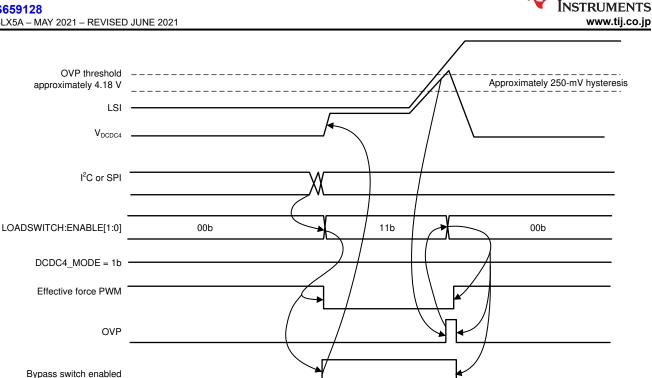

- バイパス・スイッチ - 無線周波数パワー・アンプ (RF-PA) に給電するア プリケーションで DCDC4 と組み合わせて使用

- インターフェイス

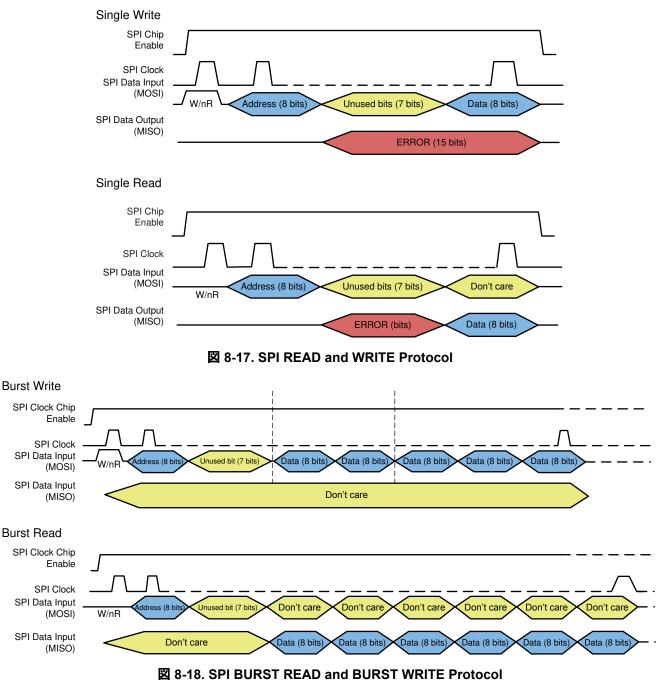

- $|^{2}C / \gamma P \gamma T + \gamma P$

- パワー I<sup>2</sup>C インターフェイスによる動的電圧スケー リング (DVS)

- シリアル・ペリフェラル・インターフェイス (SPI)

- 32kHz RC 発振器

- 低電圧誤動作防止、バッテリ・フォルト・コンパレータ、 ボタン長押し検出

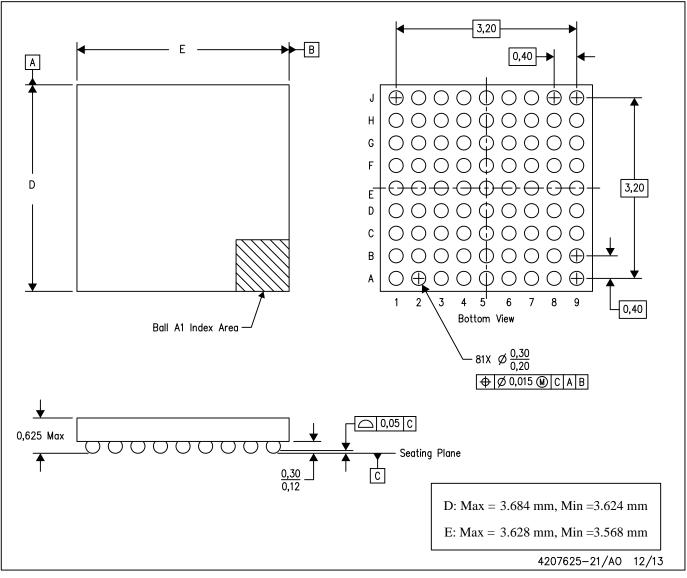

- 3.6mm × 3.6mm の DSBGA パッケージ、0.4mm ピッ チ

# 2 アプリケーション

- スマートフォン

- 無線ルータおよびスイッチ

- タブレット

- 産業用アプリケーション

- LTE モデム

GPS

## 3 概要

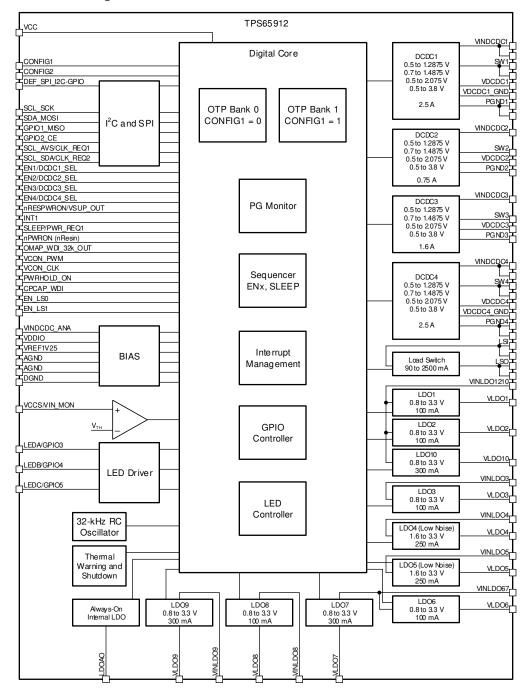

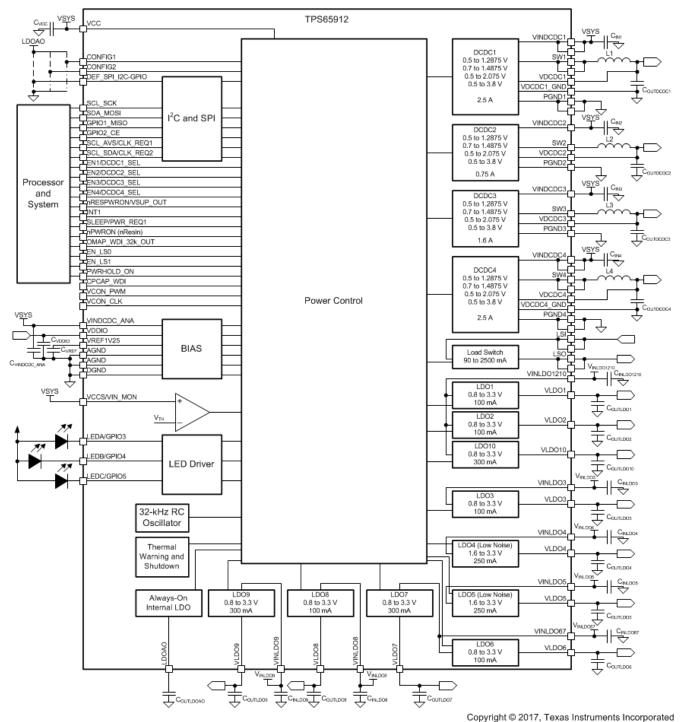

TPS659128x デバイスは、最大出力電流 2.5A の構成可 能な 4 つの降圧コンバータと、10 個の外部用 LDO レギ ュレータを備えています。これらの LDO には、バッテリま たはプリレギュレーション済みの電源から給電が可能で す。本デバイスには、部品番号ごとに異なる電源オンおよ び電源オフ・シーケンスが工場出荷時にプログラムされて います。

TPS659128x デバイスは、電源オンまたは電源オフ時に すべてのリソースのシーケンスを調整するため、32kHzの RC 発振器を内蔵しています。 すべての LDO と DC/DC コンバータは、I<sup>2</sup>C/SPI インターフェイスまたは基本的なブ ート後のイネーブル・ピンで制御できます。また、電圧スケ ーリング・インターフェイスを使うことで、I<sup>2</sup>C または基本的 なルーフ / フロア制御によって DC/DC コンバータを別の 電圧に遷移させることができます。本デバイスは、先進の 調光機能を備えた3 つの LED ドライバを内蔵していま す。汎用入出力 (GPIO) 機能は各種ピン (例:LED ピン、 ENx ピン、SPI ピン)と多重化されています。各 GPIO は、電源オン・シーケンスの一部として外部リソースを制御 するように設定できます。 SLEEP ピン1本で、アクティブ・ モードとあらかじめプログラムされたスリープ・モードを切り 替えることで電力を最適化できます。TPS659128x デバイ スは 9 ピン DSBGA パッケージ (3.6mm × 3.6mm、 0.4mm ピッチ) で供給されます。

#### 製品情報(1)

| 部品番号                     | パッケージ      | 本体サイズ           |  |

|--------------------------|------------|-----------------|--|

| TPS6591286<br>TPS6591287 | DSBGA (81) | 3.60mm × 3.60mm |  |

利用可能なすべてのパッケージについては、このデータシートの (1) 末尾にある注文情報を参照してください。

概略回路図

# **Table of Contents**

| 1 特長            |                                           |

|-----------------|-------------------------------------------|

|                 | ン1                                        |

|                 |                                           |

|                 | tory2                                     |

|                 | ation and Functions3                      |

|                 | 1 <b>S</b> 7                              |

|                 | Maximum Ratings7                          |

|                 | ngs7                                      |

|                 | ended Operating Conditions8               |

|                 | Characteristics9                          |

|                 | Characteristics – DCDC1, DCDC2,           |

| and DCDC        | 39                                        |

|                 | Characteristics – DCDC4 11                |

|                 | Characteristics – LDOs 12                 |

|                 | Characteristics – Digital Inputs, Digital |

|                 |                                           |

|                 | Characteristics – VMON Voltage            |

|                 | DDIO, Undervoltage Lockout (UVLO),        |

|                 | 0                                         |

|                 | al Characteristics – Load Switch          |

| •••••           | al Characteristics – LED Drivers          |

|                 | al Characteristics – Thermal Monitoring   |

| and Shuldo      | own                                       |

|                 |                                           |

|                 | ing Requirements                          |

|                 | face Timing Requirements                  |

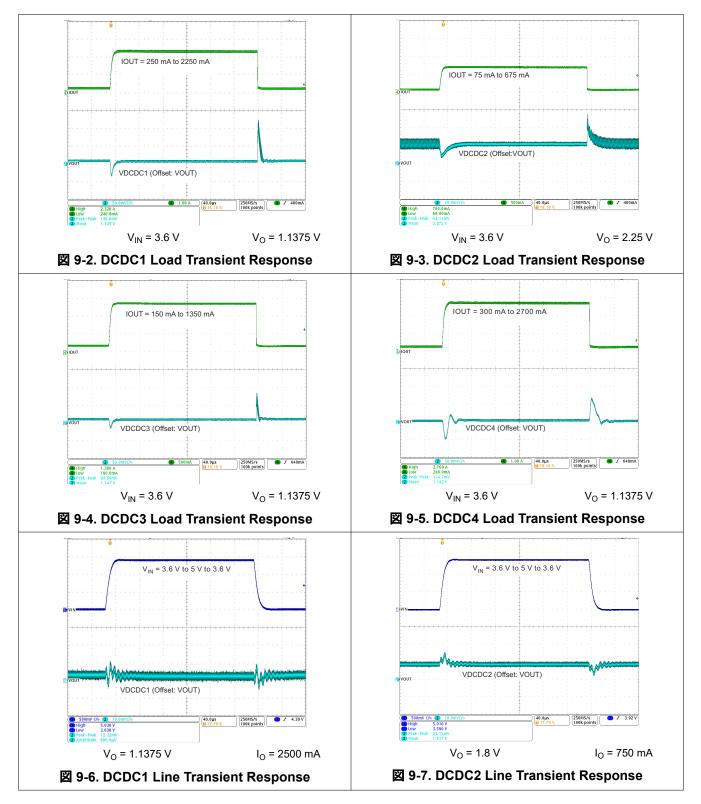

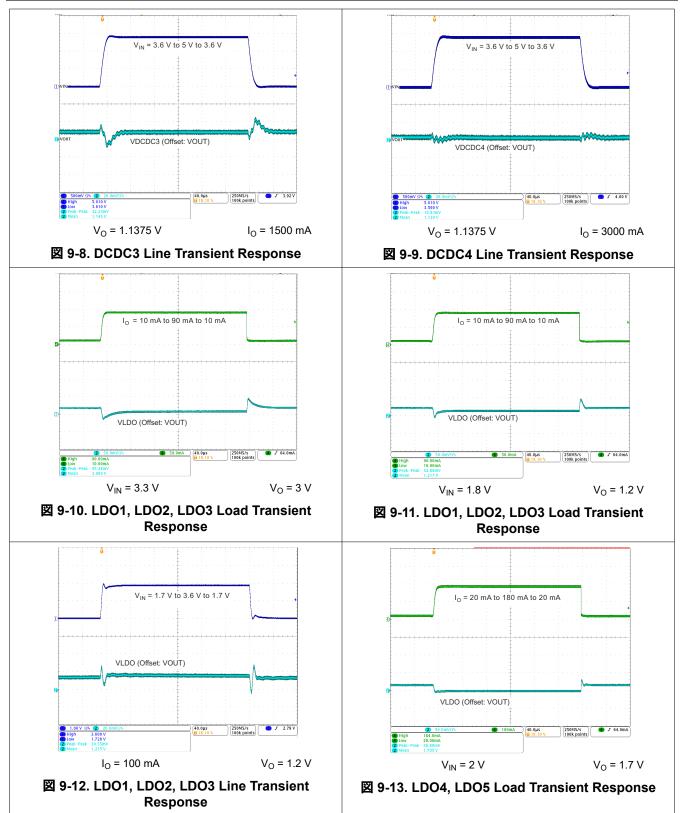

| o. to Typical C | Characteristics19                         |

| 7 Parameter Measurement Information             | 24  |

|-------------------------------------------------|-----|

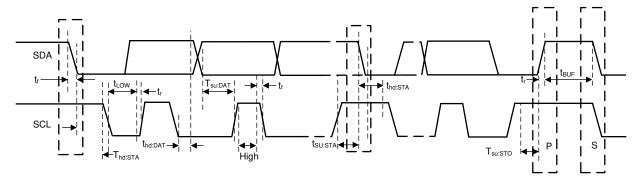

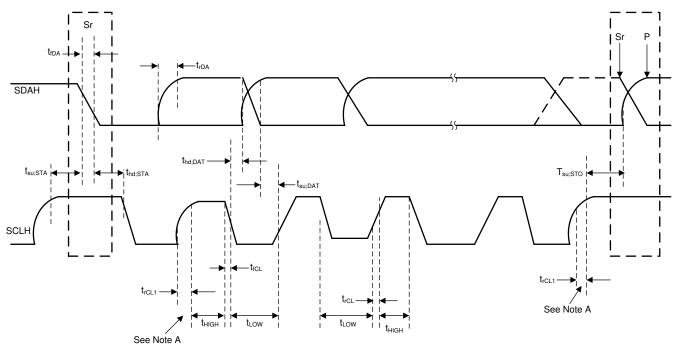

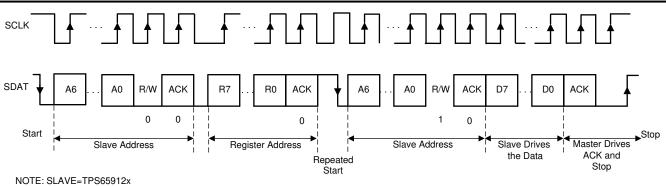

| 7.1 I <sup>2</sup> C Timing Diagrams            | 24  |

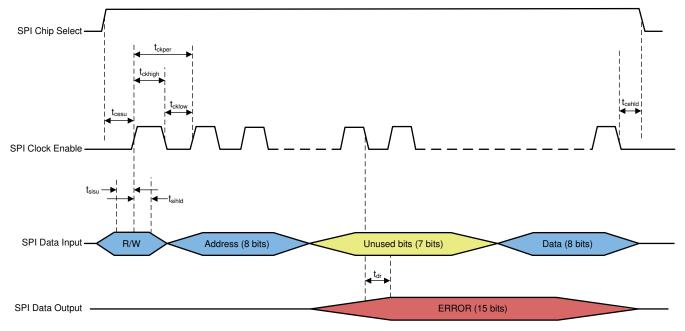

| 7.2 SPI Timing Diagram                          |     |

| 8 Detailed Description                          |     |

| 8.1 Overview                                    |     |

| 8.2 Functional Block Diagram                    |     |

| 8.3 Feature Description                         |     |

| 8.4 Device Functional Modes                     |     |

| 8.5 Register Maps                               |     |

| Application and Implementation                  |     |

| 9.1 Application Information                     |     |

| 9.2 Typical Application                         |     |

| 10 Layout                                       |     |

| 10.1 Layout Guidelines                          | 155 |

| 10.2 Layout Example                             |     |

| 11 Power Supply Recommendations                 |     |

| 12 Device and Documentation Support             |     |

| 12.1 Device Support                             |     |

| 12.2 Documentation Support                      |     |

| 12.3 Receiving Notification of Documentation Up |     |

| 12.4 サポート・リソース                                  |     |

| 12.5 Trademarks                                 |     |

| 12.6 Electrostatic Discharge Caution            |     |

| 12.7 Glossary                                   |     |

| 13 Mechanical, Packaging, and Orderable         |     |

| Information                                     | 160 |

|                                                 |     |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Cł | hanges from Revision * (May 2021) to Revision A (June 2021) | Page |

|----|-------------------------------------------------------------|------|

| •  | TPS6591287 をプレビューからアクティブに変更                                 | 1    |

# **5** Pin Configuration and Functions

☑ 5-1 shows the 81-pin YFF Die-Size Ball-Grid Array pin assignments.

|   | 1                                                                                                                                                                                                                                                                                                                                                        | 2          | 3          | 4             | 5                                               | 6          | 7                               | 8         | 9        |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|---------------|-------------------------------------------------|------------|---------------------------------|-----------|----------|

|   |                                                                                                                                                                                                                                                                                                                                                          | /\         | /          | //            | //                                              | /\         | /\                              | /\        | //)      |

| А | ( VLD07 )(                                                                                                                                                                                                                                                                                                                                               | VINLDO67   | VLDO6      | ( VDCDC4 )(   | PGND4                                           | SW4        |                                 | LSO )     | LSO      |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | >=<                                             |            |                                 |           |          |

| В |                                                                                                                                                                                                                                                                                                                                                          | LEDB/GPIO4 | LEDA/GPIO3 |               | PGND4                                           | SW4        |                                 |           | LSI      |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | >=<                                             |            |                                 |           | _==      |

| С |                                                                                                                                                                                                                                                                                                                                                          | EN_LS1     | EN_LS0     |               | N4/DCDC4<br>_SEL                                | Lens/DCDC3 |                                 |           | VINDCDC2 |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | )==(                                            |            |                                 |           |          |

| D | ( sw3 )(                                                                                                                                                                                                                                                                                                                                                 | CONFIG2    | nPWRON     | GPIO1_MISO    | SCL_SCK                                         | WRHOLD_ON  | VDCDC2                          | EN2/DCDC2 | SW2      |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | )==(                                            |            |                                 |           |          |

| Е |                                                                                                                                                                                                                                                                                                                                                          | CONFIG1    |            | ( sda_mosi )/ | SCL_AVS                                         | / SDA_AVS  | ) / DEF_SPI ) /<br>I2C-GPIO ) \ | EN1/DCDC1 | PGND2    |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | )= </td <td></td> <td></td> <td></td> <td></td> |            |                                 |           |          |

| F |                                                                                                                                                                                                                                                                                                                                                          | VDCDC3     | AGND       | (vcon_pwm)( v | CON_CLK                                         | OMAP_WDI   |                                 |           | VLDO3    |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | >==\                                            |            |                                 |           |          |

| G | $\begin{pmatrix} & \\ & \\ & \\ & \\ & \\ & \end{pmatrix} \begin{pmatrix} & \\ & \\ & \\ & \\ & \end{pmatrix} \begin{pmatrix} & \\ & \\ & \\ & \\ & \end{pmatrix} \begin{pmatrix} & \\ & \\ & \\ & \\ & \\ & \end{pmatrix} \begin{pmatrix} & \\ & \\ & \\ & \\ & \\ & \\ & \end{pmatrix} \begin{pmatrix} & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ &$ | VCCS/VIN   |            | SLEEP/PWR     | INT1                                            |            |                                 |           | VLDO5    |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | )==(                                            |            |                                 |           |          |

| н |                                                                                                                                                                                                                                                                                                                                                          | vcc );     | VREF1V25   |               | PGND1                                           | SW1        |                                 |           | VLDO8    |

|   |                                                                                                                                                                                                                                                                                                                                                          |            |            |               | >==                                             |            |                                 |           |          |

| J |                                                                                                                                                                                                                                                                                                                                                          | VINLDO1210 |            |               | PGND1                                           | SW1        |                                 |           | VLDO9    |

|   | \`′                                                                                                                                                                                                                                                                                                                                                      | ` <u>`</u> | <u>``'</u> | ``'``         | <u>`</u> ′                                      | <u>``</u>  | ``'                             | <u>``</u> | ``'      |

Not to scale

## ☑ 5-1. 81-Pin YFF DSBGA (Bottom View)

表 5-1. Pin Functions

| P                    | IN       |        |     | DESCRIPTION                                                                                                                |  |  |

|----------------------|----------|--------|-----|----------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                 | ALT NAME | NO.    | I/O | DESCRIPTION                                                                                                                |  |  |

| REFERENCE            |          |        |     |                                                                                                                            |  |  |

| VREF1V25             | _        | H3     | 0   | Internal reference voltage. Connect a 100-nF capacitor from this pin to AGND. Do not load this pin externally.             |  |  |

| AGND                 | —        | F3, C7 | _   | Analog-ground (AGND) connection. Connect this pin to the power-<br>ground (PGND) plane on the printed circuit board (PCB). |  |  |

| DRIVERS AND LIGHTING |          |        |     |                                                                                                                            |  |  |

| LEDA/GPIO3 — B3      |          |        | I/O | General-purpose I/O or LED driver output                                                                                   |  |  |

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback 3

# 表 5-1. Pin Functions (continued)

| Р                   | IN                                                                                                          |        |                                                               |                                                                                                                                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------|--------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                | ALT NAME                                                                                                    | NO.    | I/O                                                           | DESCRIPTION                                                                                                                                                                                 |

| LEDB/GPIO4          |                                                                                                             | B2     | I/O                                                           | General-purpose I/O or LED driver output                                                                                                                                                    |

| LEDC/GPIO5          |                                                                                                             | B1     | I/O                                                           | General-purpose I/O or LED driver output                                                                                                                                                    |

| STEP-DOWN CONVERTER | S                                                                                                           |        |                                                               |                                                                                                                                                                                             |

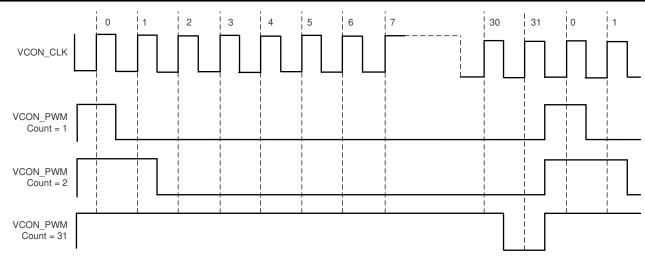

| VINDCDC_ANA         | _                                                                                                           | C8     | I                                                             | Analog supply input for the DC-DC converters. This pin must be connected to the VINDCDC1, VINDCDC2, VINDCDC3 and VINDCDC4 pins.                                                             |

| VINDCDC1            | _                                                                                                           | H7, J7 | I                                                             | Power input to the DCDC1 converter. Connect this pin to the VINDCDC2, VINDCDC3, VINDCDC4, and VINDCDC_ANA pins.                                                                             |

| VDCDC1              | _                                                                                                           | J4     | I                                                             | Remote positive voltage sense (feedback) input for the DCDC1 converter                                                                                                                      |

| VDCDC1_GND          | _                                                                                                           | H4     | I                                                             | Remote negative voltage sense (feedback) input for DCDC1. Tie this pin to the GND plane or to the AGND plane. Alternatively, tie this pin to the GND pad of the output capacitor.           |

| SW1                 | _                                                                                                           | H6, J6 | 0                                                             | Switch node of the DCDC1 converter. Connect this pin to the output inductor.                                                                                                                |

| PGND1 — H5, J5 —    |                                                                                                             |        |                                                               | Power GND connection for the DCDC1 converter                                                                                                                                                |

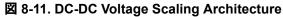

| VCON_PWM            | Pulse-width modulation (PWM) period signal for dynamic voltage scaling on the DCDC1 converter if using VCON |        |                                                               |                                                                                                                                                                                             |

| VCON_CLK            | _                                                                                                           | F5     | I                                                             | Clock signal for dynamic voltage scaling on the DCDC1 converter if using VCON                                                                                                               |

| VINDCDC2            | _                                                                                                           | C9     | I                                                             | Power input to the DCDC2 converter. Connect this pin to the VINDCDC1, VINDCDC3, VINDCDC4, and VINDCDC_ANA pins.                                                                             |

| VDCDC2              | VDCDC2 — D7 I Remote voltage sense (feedback) input for the DCD0                                            |        | Remote voltage sense (feedback) input for the DCDC2 converter |                                                                                                                                                                                             |

| SW2                 | _                                                                                                           | D9     | 0                                                             | Switch node of the DCDC2 converter. Connect this pin to the output inductor.                                                                                                                |

| PGND2               | _                                                                                                           | E9     | _                                                             | Power GND connection for the DCDC2 converter                                                                                                                                                |

| VINDCDC3            | _                                                                                                           | C1     | I                                                             | Power input to the DCDC3 converter. Connect this pin to the VINDCDC1, VINDCDC2, VINDCDC4, and VINDCDC_ANA pins.                                                                             |

| VDCDC3              | _                                                                                                           | F2     | I                                                             | Remote voltage sense (feedback) input for the DCDC3 converter                                                                                                                               |

| SW3                 | _                                                                                                           | D1     | 0                                                             | Switch node of the DCDC3 converter. Connect this pin to the output inductor.                                                                                                                |

| PGND3               |                                                                                                             | E1     |                                                               | Power GND connection for the DCDC3 converter                                                                                                                                                |

| VINDCDC4            | _                                                                                                           | A7, B7 | I                                                             | Power input to the DCDC4 converter. Connect this pin to the VINDCDC1, VINDCDC2, VINDCDC3, and VINDCDC_ANA pins.                                                                             |

| VDCDC4              | —                                                                                                           | A4     | I                                                             | Remote positive voltage sense (feedback) input for the DCDC4 converter                                                                                                                      |

| VDCDC4_GND          | _                                                                                                           | B4     | I                                                             | Remote negative voltage sense (feedback) input the DCDC4 converter. Tie this pin to the GND plane or to the AGND plane. Alternatively, tie this pin to the GND-pad of the output capacitor. |

| SW4                 | _                                                                                                           | A6, B6 | 0                                                             | Switch node of the DCDC4 converter. Connect this pin to the output inductor.                                                                                                                |

| PGND4               |                                                                                                             | A5, B5 |                                                               | Power GND connection for the DCDC4 converter                                                                                                                                                |

| LOAD SWITCH         |                                                                                                             |        |                                                               |                                                                                                                                                                                             |

| LSI                 | _                                                                                                           | B8, B9 | I                                                             | Input of the load switch                                                                                                                                                                    |

| LSO                 |                                                                                                             | A8, A9 | 0                                                             | Output of the load switch                                                                                                                                                                   |

| EN_LS0              | _                                                                                                           | C3     | I                                                             | Load switch enable pin. The status of this pin is copied to the ENABLE0 bit in the LOADSWITCH register in the CONFIG state.                                                                 |

| EN_LS1              | _                                                                                                           | C2     | I                                                             | Load switch enable pin. The status of this pin is copied to the ENABLE1 bit in the LOADSWITCH register in the CONFIG state.                                                                 |

| LOW-DROPOUT REGULAT | ORS                                                                                                         |        | 1                                                             | 1                                                                                                                                                                                           |

| VINLDO1210          | _                                                                                                           | J2     | I                                                             | Power input for the LDO1, LDO2, and LDO10 regulators                                                                                                                                        |

4 Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

# 表 5-1. Pin Functions (continued)

| P                               | IN        | 2,0111 |       |                                                                                                                                                                                                                                            |

|---------------------------------|-----------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                            | ALT NAME  | NO.    | - I/O | DESCRIPTION                                                                                                                                                                                                                                |

| VINLDO3                         |           | F8     | I     | Power input for the LDO3 regulator                                                                                                                                                                                                         |

| VINLDO4                         |           | F1     | I     | Power input for the LDO4 regulator                                                                                                                                                                                                         |

| VINLDO5                         | _         | G8     | I     | Power input for the LDO5 regulator                                                                                                                                                                                                         |

| VINLDO67                        | _         | A2     | I     | Power input for the LDO6 and LDO7 regulators                                                                                                                                                                                               |

| VINLDO8                         |           | H8     | I     | Power input for the LDO8 regulator                                                                                                                                                                                                         |

| VINLDO9                         | _         | J8     | I     | Power input for the LDO9 regulator                                                                                                                                                                                                         |

| LDOAO                           | _         | G3     | 0     | <i>LDO always on</i> internal supply. Connect this pin to the buffer capacitor.                                                                                                                                                            |

| VLDO1                           | —         | J3     | 0     | LDO1 output                                                                                                                                                                                                                                |

| VLDO2                           | _         | H1     | 0     | LDO2 output                                                                                                                                                                                                                                |

| VLDO3                           |           | F9     | 0     | LDO3 output                                                                                                                                                                                                                                |

| VLDO4                           | _         | G1     | 0     | LDO4 output                                                                                                                                                                                                                                |

| VLDO5                           | _         | G9     | 0     | LDO5 output                                                                                                                                                                                                                                |

| VLDO6                           |           | A3     | 0     | LDO6 output                                                                                                                                                                                                                                |

| VLDO7                           |           | A1     | 0     | LDO7 output                                                                                                                                                                                                                                |

| VLDO8                           | _         | H9     | 0     | LDO8 output                                                                                                                                                                                                                                |

| VLDO9                           | _         | J9     | 0     | LDO9 output                                                                                                                                                                                                                                |

| VLDO10                          | _         | J1     | 0     | LDO10 output                                                                                                                                                                                                                               |

| STANDARD INTERFACE              |           |        |       |                                                                                                                                                                                                                                            |

| DEF_SPI_I2C-GPIO                | _         | E7     | I     | Digital input that defines whether SPI is available or I <sup>2</sup> C and GPIOs are available on the C4, D4, E4, D5 pins. Shorting this pin to GND selects SPI. Shorting this pin to LDOAO selects I <sup>2</sup> C, and GPIO1 and GPIO2 |

| SCL_SCK                         | SCK       | D5     | I     | I <sup>2</sup> C SCL or SPI SCK based on DEF_SPI_I2C-GPIO                                                                                                                                                                                  |

| SDA_MOSI                        | MOSI      | E4     | I/O   | I <sup>2</sup> C SDA or SPI master-out slave-in device (MOSI) based on DEF_SPI_I2C-GPIO                                                                                                                                                    |

| GPIO1_MISO                      | MISO      | D4     | I/O   | GPIO1 or SPI master-out slave-in device (MISO) based on DEF_SPI_I2C-GPIO                                                                                                                                                                   |

| GPIO2_CE                        | CE        | C4     | I/O   | GPIO2 or SPI chip enable (CE) active high based on DEF_SPI_I2C-<br>GPIO                                                                                                                                                                    |

| ENABLE AND VOLTAGE SO           | CALING    |        | 1     |                                                                                                                                                                                                                                            |

| EN1/DCDC1_SEL <sup>(1)</sup>    | DCDC1_SEL | E8     | I     | Enable pin for EN1_SETx assigned resources or voltage-scaling pin<br>that changes the output of a converter or a group of converters<br>between two predefined values                                                                      |

| EN2/DCDC2_SEL <sup>(1)</sup>    | DCDC2_SEL | D8     | I     | Enable pin for EN2_SETx assigned resources or voltage-scaling pin that changes the output of a converter or a group of converters between two predefined values                                                                            |

| EN3/DCDC3_SEL <sup>(1)</sup>    | DCDC3_SEL | C6     | I     | Enable pin for EN3_SETx assigned resources or voltage-scaling pin that changes the output of a converter or a group of converters between two predefined values                                                                            |

| EN4/DCDC4_SEL <sup>(1)</sup>    | DCDC4_SEL | C5     | 1     | Enable pin for EN4_SETx assigned resources or voltage-scaling pin<br>that changes the output of a converter or a group of converters<br>between two predefined values                                                                      |

| SCL_AVS/CLK_REQ1 <sup>(2)</sup> | CLK_REQ1  | E5     | I     | Clock pin of power I <sup>2</sup> C for dynamic voltage scaling or clock request input signal 1 used to enable and disable power resources using EN2_SETx registers.                                                                       |

| SDA_AVS/CLK_REQ2 <sup>(2)</sup> | CLK_REQ2  | E6     | I/O   | Data pin of power I <sup>2</sup> C for dynamic voltage scaling or clock request input signal 2 used to enable and disable power resources using EN3_SETx registers.                                                                        |

| SLEEP/PWR_REQ <sup>(2)</sup>    | PWR_REQ   | G4     | I     | SLEEP state request input or power request input signal used to enable and disable power resources using EN1_SETx registers.                                                                                                               |

Copyright © 2021 Texas Instruments Incorporated

## 表 5-1. Pin Functions (continued)

| Р                  | PIN                    |     | I/O              | DESCRIPTION                                                                                                                                                                                                                                                                                                  |

|--------------------|------------------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | ALT NAME               | NO. | 1/0              | DESCRIPTION                                                                                                                                                                                                                                                                                                  |

| nRESPWRON/VSUP_OUT | VSUP_OUT               | G6  | 0                | Active low reset output to disable processor until power-up sequence completes or the output of the input voltage monitor                                                                                                                                                                                    |

| VCCS/VIN_MON       |                        |     | I                | Voltage sense for input voltage monitoring                                                                                                                                                                                                                                                                   |

| PWRHOLD_ON ON      |                        | D6  | I                | POWERHOLD or ON. This pin is an enable input.                                                                                                                                                                                                                                                                |

| INT1               | G5                     | 0   | Interrupt output |                                                                                                                                                                                                                                                                                                              |

| nPWRON             | nRESIN (OTP<br>option) | D3  | I                | Active-low, debounced power-on input or power-request input to start<br>the power-up sequencing. Alternatively, this pin is the active-low reset<br>input to the PMIC that is debounced by 10 ms (OTP option). Tie this<br>pin to the LDOAO pin for a logic high if not used.                                |

| OMAP_WDI_32k_OUT   | 32KCLKOUT              | F6  | 0                | Always used as 32KCLKOUT. Leave this pin floating if not using 32KCLKOUT.                                                                                                                                                                                                                                    |

| CPCAP_WDI          | —                      | G7  | —                | No connect, leave this pin floating.                                                                                                                                                                                                                                                                         |

| CONFIG1            | _                      | E2  | I                | Selects the predefined startup options and default voltages. Use this pin to choose from two internal OTP settings. Tie this pin to GND or the LDOAO pin.                                                                                                                                                    |

| CONFIG2            | _                      | D2  | I                | Selects between two device modes. With the CONFIG2 tied to LDOAO, the primary functions of the pins (ENx, SCL_AVS, SDA_AVS, and SLEEP) and SLEEP state is usable. With the CONFIG2 tied to GND, the alternate functions of the pins are used (DCDCx_SEL, CLK_REQx, and PWR_REQ) and SLEEP state is not used. |

| VCC —              |                        | H2  | I                | Digital supply input                                                                                                                                                                                                                                                                                         |

| VDDIO — F7         |                        | F7  | I                | Supply voltage input for GPIOs and output stages that sets the high-level voltage (I/O voltage)                                                                                                                                                                                                              |

| DGND               | _                      | E3  | -                | Digital GND connection. Tie this pin to the AGND and PGNDx on the PCB.                                                                                                                                                                                                                                       |

(1) The DCDCx\_SEL pin function is selected by pulling the CONFIG2 pin to GND which also selects the CLK\_REQx and PWR\_REQ pin functions as enable resources.

(2) The CLK\_REQ1, CLK\_REQ2, and PWR\_REQ pin functions are selected by puling the CONFIG2 pin to GND.

# **6** Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|              |                                                                                                                                                                                                                                                                                                                           | MIN   | MAX         | UNIT |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------|------|

|              | All pins except AGND pins, PGND pins, and pins listed below with respect to AGND                                                                                                                                                                                                                                          | -0.3  | 6           |      |

| Voltage      | VLDO1, VLDO2, VLDO3, VLDO4, VLDO5, VLDO6, VLDO7, VLDO8,<br>VLDO9, VLDO10, VINLDO1210, VINLDO3, EN1/DCDC1_SEL, EN2/<br>DCDC2_SEL, EN3/DCDC3_SEL, EN4/DCDC4_SEL, SLEEP/PWR_REQ,<br>CLK_REQ1, CLK_REQ2, VDDI0, CONFIG1, CONFIG2, DEF_SPI_I2C-<br>GPIO, EN_LS0, EN_LS1, OMAP_WDI, CPCAP_WDI, VCON_CLK with<br>respect to AGND | -0.3  | 3.6         | V    |

|              | VDCDC1, VDCDC2, VDCDC3, VDCDC4 with respect to AGND                                                                                                                                                                                                                                                                       | -0.3  | 3.8         |      |

|              | SDA_SDI, SCL_CLK, GPIO1_MISO, GPIO1_CE, SDA_AVS, SCL_AVS,<br>INT1, 32KCLKOUT, GPIO3 and GPIO4 and GPIO5 if defined as GPIOs with<br>push-pull output (otherwise it is 6-V rated), nRESPWRON if nRESPWRON<br>is push-pull output (otherwise it is 6-V rated) with respect to AGND                                          | -0.3  | VDDIO + 0.3 |      |

|              | V <sub>CC</sub>                                                                                                                                                                                                                                                                                                           | VDDIO | 6           |      |

| Current      | All non-power pins                                                                                                                                                                                                                                                                                                        |       | 5           | mA   |

| Current      | Power pins (per pin)                                                                                                                                                                                                                                                                                                      |       | 2           | A    |

| Operating fr | ee-air temperature, T <sub>A</sub>                                                                                                                                                                                                                                                                                        | -40   | 85          | °C   |

| Maximum ju   | inction temperature, T <sub>J</sub>                                                                                                                                                                                                                                                                                       |       | 125         | °C   |

| Storage terr | nperature, T <sub>stg</sub>                                                                                                                                                                                                                                                                                               | -65   | 150         | °C   |

|              |                                                                                                                                                                                                                                                                                                                           |       |             | 1    |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* (セクション 6.3) is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|      |                         |                                                                  | VALUE | UNIT |

|------|-------------------------|------------------------------------------------------------------|-------|------|

| V    | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS001 <sup>(1)</sup> | 1000  | V    |

| VESD | Electrostatic discharge | Charged device model (CDM), per JESD22-C101 <sup>(2)</sup>       | 250   | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                                                                                                                                               |                                                                                                                                             | MIN | NOM | MAX | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| DC-DC CONVE                                                                                                                                                                   | RTERS                                                                                                                                       |     |     |     |      |

| VIN1, VIN2,<br>VIN3, VIN4                                                                                                                                                     | Input voltage for step-down converter DCDC1, DCDC2, DCDC3, DCDC4                                                                            | 2.7 |     | 5.5 | V    |

|                                                                                                                                                                               | Output voltage for step-down converter DCDC1, DCDC2, DCDC3, DCDC4 <sup>(1)</sup>                                                            | 0.5 |     | 3.8 | V    |

|                                                                                                                                                                               | Inductance at L1, L2, L3, L4                                                                                                                | 0.5 | 1   | 1.3 | μH   |

| C <sub>IN1</sub> , C <sub>IN4</sub>                                                                                                                                           | Input capacitance at VIN1 and VIN4 (on each pin)                                                                                            | 10  | 22  |     | μF   |

| C <sub>IN2</sub> , C <sub>IN3</sub>                                                                                                                                           | Input capacitance at VIN2 and VIN3 (on each pin)                                                                                            | 4.7 | 10  |     | μF   |

| C <sub>OUTDCDC1,2,3</sub>                                                                                                                                                     | Output capacitance at DCDC1, DCDC2 and DCDC3                                                                                                | 4.7 | 10  | 22  | μF   |

| C <sub>OUTDCDC4</sub>                                                                                                                                                         | Output capacitance at DCDC4                                                                                                                 | 10  | 22  | 47  | μF   |

| LDOs                                                                                                                                                                          |                                                                                                                                             |     |     |     |      |

| VINLDO1210                                                                                                                                                                    | Input voltage for LDO1, LDO2 and LDO10                                                                                                      | 1.7 |     | 3.6 | V    |

| VINLDO4                                                                                                                                                                       | Input voltage for LDO4                                                                                                                      | 1.9 |     | 5.5 | V    |

| VINLDO5                                                                                                                                                                       | Input voltage for LDO5                                                                                                                      | 1.9 |     | 5.5 | V    |

| V <sub>LDO1</sub> , V <sub>LDO2</sub> ,<br>V <sub>LDO3</sub> ,<br>V <sub>LDO6</sub> ,<br>V <sub>LDO7</sub> , V <sub>LDO8</sub> ,<br>V <sub>LDO9</sub> , V <sub>LDO10</sub>    | Output voltage for general purpose (GP) LDOs <sup>(1)</sup>                                                                                 | 0.8 |     | 3.3 | V    |

| V <sub>LDO4,</sub> V <sub>LDO5,</sub>                                                                                                                                         | Output voltage for RF-LDOs                                                                                                                  | 1.6 |     | 3.3 | V    |

| C <sub>INLD01210</sub> ,<br>C <sub>INLD03</sub> ,<br>C <sub>INLD04</sub> ,<br>C <sub>INLD05</sub> ,<br>C <sub>INLD067</sub> ,<br>C <sub>INLD08</sub> ,<br>C <sub>INLD08</sub> | Input capacitance on LDO supply pins                                                                                                        | 0.5 |     |     | μF   |

| C <sub>OUTDO4,</sub><br>C <sub>OUTLDO5</sub>                                                                                                                                  | Output capacitance on LDO4 and LDO5                                                                                                         | 2.2 |     | 10  | μF   |

| C <sub>OUTLDO1</sub> ,<br>C <sub>OUTLDO2</sub> ,<br>C <sub>OUTLDO3</sub> ,<br>C <sub>OUTLDO6</sub> ,<br>C <sub>OUTLDO7</sub> ,<br>C <sub>OUTLDO8</sub>                        | Output capacitance LDO1, LDO2, LDO3, LDO6, LDO7, LDO8<br>These LDOs are <i>capless</i> , the required capacitance can be placed at the load | 0.5 |     | 10  | μF   |

| C <sub>OUTLDO9,</sub><br>C <sub>OUTLDO10</sub>                                                                                                                                | Output capacitance LDO9 and LDO10<br>These LDOs are <i>capless</i> , the required capacitance can be placed at the load                     | 1   |     | 10  | μF   |

| C <sub>OUTLDOAO</sub>                                                                                                                                                         | Output capacitance on LDOAO                                                                                                                 | 0.5 |     | 10  | μF   |

| C <sub>VINDCDC_ANA</sub>                                                                                                                                                      | Input capacitance on VINDCDC_ANA                                                                                                            | 100 |     |     | nF   |

| C <sub>VCC</sub>                                                                                                                                                              | Input capacitance on VCC                                                                                                                    | 100 |     |     | nF   |

| C <sub>VDDIO</sub>                                                                                                                                                            | Input capacitance on VDDIO                                                                                                                  | 100 |     |     | nF   |

| C <sub>VREF</sub>                                                                                                                                                             | Output capacitance on VREF1V25                                                                                                              | 100 |     |     | nF   |

| T <sub>A</sub>                                                                                                                                                                | Operating ambient temperature                                                                                                               | -40 |     | 85  | °C   |

| TJ                                                                                                                                                                            | Operating junction temperature                                                                                                              | -40 |     | 125 | °C   |

(1) The maximum output voltage of DCDC1 to DCDC4 and LDO1 to LDO4 can be reduced by an OTP setting to adopt the maximum voltage to the requirements (or maximum ratings) of the load powered. This setting helps protect the processor from exceeding the maximum ratings for the core voltage. The value is set in nonvolatile memory (OTP) by TI upon customer request with sufficient business case.

#### **6.4 Thermal Characteristics**

|                     |                                              | TPS659128   |      |

|---------------------|----------------------------------------------|-------------|------|

|                     | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                     |                                              | 81 PINS     |      |

| R <sub>0JA</sub>    | Junction-to-ambient thermal resistance       | 41.3        | °C/W |

| R <sub>0JCtop</sub> | Junction-to-case (top) thermal resistance    | 0.1         | °C/W |

| R <sub>θJB</sub>    | Junction-to-board thermal resistance         | 5.2         | °C/W |

| ΨJT                 | Junction-to-top characterization parameter   | 0.7         | °C/W |

| Ψјв                 | Junction-to-board characterization parameter | 5.2         | °C/W |

(1) For more information about traditional and new thermal metrics, see *Semiconductor and IC Package Thermal Metrics* application report.

## 6.5 Electrical Characteristics – DCDC1, DCDC2, and DCDC3

–40°C ≤  $T_A$  ≤ 85°C, typical values are at  $T_A$  = 25°C (unless otherwise noted)

| P                                        | ARAMETER                                                                                                                                                                                                                                                                                               | TEST CONDITION                                                                                             | MIN | TYP | MAX    | UNIT |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----|--------|------|

| V <sub>IN</sub>                          | Input voltage range                                                                                                                                                                                                                                                                                    |                                                                                                            | 2.3 |     | 5.5    | V    |

|                                          |                                                                                                                                                                                                                                                                                                        | Option1; in 12.5-mV steps; RANGE[1:0] = 00b                                                                | 0.5 |     | 1.2875 | V    |

| V <sub>DCDC1</sub>                       | DCDCx output                                                                                                                                                                                                                                                                                           | Option2; in 12.5-mV steps; RANGE[1:0] = 01b                                                                | 0.7 |     | 1.4875 | V    |

| V <sub>DCDC2</sub><br>V <sub>DCDC3</sub> | voltage Range                                                                                                                                                                                                                                                                                          | Option3; in 25-mV steps; RANGE[1:0] = 10b                                                                  | 0.5 |     | 2.075  | V    |

|                                          |                                                                                                                                                                                                                                                                                                        | Option4; in 50-mV steps; RANGE[1:0] = 11b                                                                  | 0.5 |     | 3.80   | V    |

|                                          |                                                                                                                                                                                                                                                                                                        | DCDC1 (VINDCDC1 $\geq$ 2.8 V)                                                                              |     |     | 2500   |      |

| 1                                        | Continuous output                                                                                                                                                                                                                                                                                      | DCDC2 (VINDCDC2 $\geq$ 2.8 V)                                                                              |     |     | 750    | mA   |

| OUT(DCDCx)                               | current                                                                                                                                                                                                                                                                                                | DCDC3 (VINDCDC3 $\geq$ 2.8 V)                                                                              |     |     | 1200   | ШA   |

|                                          |                                                                                                                                                                                                                                                                                                        | DCDC3 for 2.8 V $\leq$ V <sub>IN</sub> $\leq$ 4.5 V; VDCDC3(max) = 1.4875 V                                |     |     | 1600   |      |

|                                          | $I_{LOAD} = 0 \text{ mA, DCDCx_MODE} = 0b, \text{ Device not switching,} \\ for DCDC1 \\ I_{LOAD} = 0 \text{ mA, DCDCx_MODE} = 1b, \text{ Device switching, for} \\ DCDC1 \\ I_{LOAD} < 1 \text{ mA, Device not switching, ECO} = 1b \text{ AND} \\ DCDCx_MODE = 0b, \text{ for DCDC1} \\ \end{array}$ |                                                                                                            |     | 26  | 55     | μA   |

|                                          |                                                                                                                                                                                                                                                                                                        |                                                                                                            |     | 8   |        | mA   |

|                                          |                                                                                                                                                                                                                                                                                                        | 9                                                                                                          |     | μA  |        |      |

| IQ                                       | Quiescent current                                                                                                                                                                                                                                                                                      | I <sub>LOAD</sub> = 0 mA, DCDCx_MODE = 0b, Device not switching,<br>for DCDC2 or DCDC3                     |     | 26  | 40     | μA   |

|                                          |                                                                                                                                                                                                                                                                                                        | I <sub>LOAD</sub> = 0 mA, DCDCx_MODE = 1b, Device switching, for<br>DCDC2 or DCDC3                         |     | 8   |        | mA   |

|                                          |                                                                                                                                                                                                                                                                                                        | I <sub>LOAD</sub> < 1 mA, Device not switching; ECO = 1b <i>AND</i><br>DCDCx_MODE = 0b, for DCDC2 or DCDC3 |     | 3   |        | μA   |

## 6.5 Electrical Characteristics – DCDC1, DCDC2, and DCDC3 (continued)

| P                      | ARAMETER                                 | TEST CONDITION                                                                                                                                                                            | MIN   | TYP  | MAX  | UNIT  |

|------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

|                        |                                          | DCDCx_MODE = 1b, VINDCDCx = 3.6 V, $I_{LOAD}$ = 0 mA,<br>T <sub>A</sub> = 25°C, ECO = 0                                                                                                   | -2%   |      |      |       |

|                        | Accuracy                                 | $\label{eq:DCDCx_MODE = 1b, VINDCDCx = 3.6 V, I_{LOAD} = 0 mA, - 40^{\circ}C \leq T_A \leq 85^{\circ}C, ECO = 0$                                                                          | -2.5% |      |      |       |

|                        |                                          | DCDCx_MODE = 0b, VINDCDCx = $3.6 \text{ V}$ , $I_{LOAD} = 0 \text{ mA}$ ,<br>T <sub>A</sub> = $25^{\circ}$ C, ECO = $0$                                                                   | -3%   |      |      |       |

|                        | ECO mode accuracy                        | $\label{eq:VINDCDCx} \begin{array}{l} VINDCDCx = 3.6 \; V, \; I_{LOAD} = 0 \; mA, \; -40^\circ C \leq T_A \leq 85^\circ C; \\ ECO = 1 b \; \textit{AND} \; DCDCx\_MODE = 0 b \end{array}$ | -5%   |      | 5%   |       |

| V <sub>DCDC1/2/3</sub> |                                          | DCDCx_MODE = 1b, VINDCDCx = 3.6 V, 120 mA $\leq$ I <sub>LOAD</sub> $\leq$ 1080 mA, for DCDC1                                                                                              |       | 0.01 |      |       |

|                        | Load regulation                          | DCDCx_MODE = 1b, VINDCDCx = $3.6 \text{ V}$ , $120 \text{ mA} \le I_{LOAD}$<br>$\le$ to 1080 mA, for DCDC3                                                                                |       | 0.01 |      | %/A   |

|                        |                                          | DCDCx_MODE = 1b, VINDCDCx = 3.6 V, 50 mA $\leq$ I <sub>LOAD</sub> $\leq$ 450 mA, for DCDC2                                                                                                |       | 0.01 |      |       |

|                        | Line regulation                          | DCDCx_MODE = 1b, 2.5 V $\leq$ VINDCDCx $\leq$ 5.5 V, I <sub>LOAD</sub> = 0 mA, for DCDC1                                                                                                  |       | 0.01 |      | %/V   |

|                        |                                          | DCDCx_MODE = 1b, 2.5 V $\leq$ VINDCDCx $\leq$ 5.5 V, I <sub>LOAD</sub> = 0 mA, for DCDC2 or DCDC3                                                                                         |       | 0.01 |      | 707 V |

|                        |                                          | DCDCx_MODE = 0b                                                                                                                                                                           |       |      | 3500 | kHz   |

| f <sub>SW</sub>        | Switching frequency                      | DCDCx_MODE = 1b, VINDCDCx = 3.6 V, VDCDCx = 1.8<br>V                                                                                                                                      |       | 2800 |      | kHz   |

|                        |                                          | for DCDC1 with VINDCDCx = 3.6 V, D = 100%                                                                                                                                                 |       | 60   | 100  | mΩ    |

| R <sub>DS(ON)</sub>    | High-side FET on-<br>resistance          | for DCDC2 and DCDC3 with VINDCDCx = 3.6 V, D = 100%                                                                                                                                       |       | 120  | 190  | mΩ    |

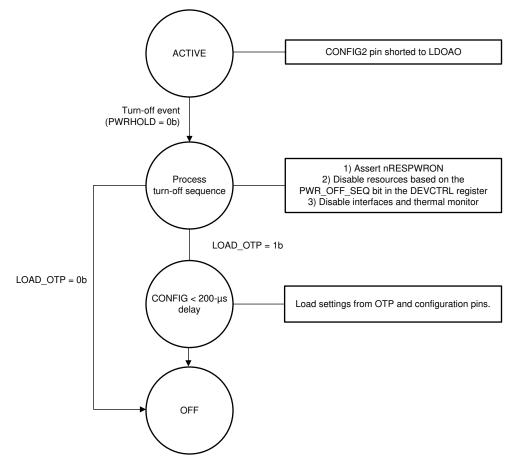

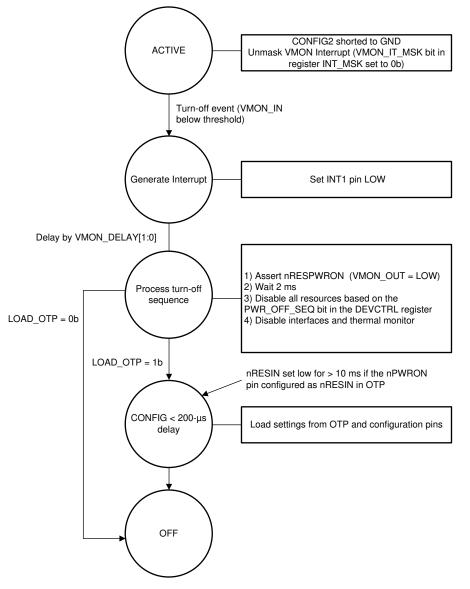

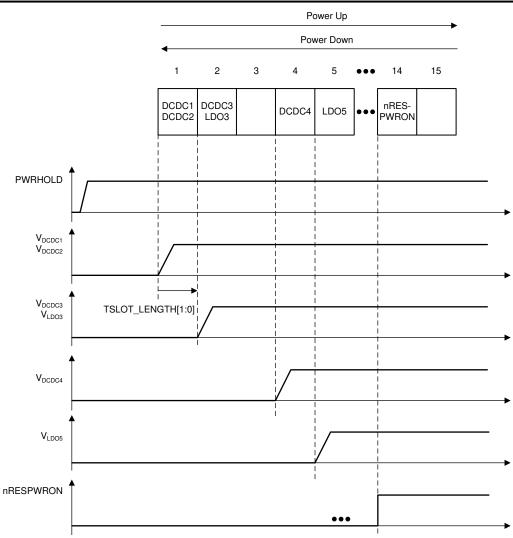

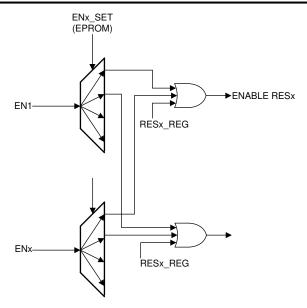

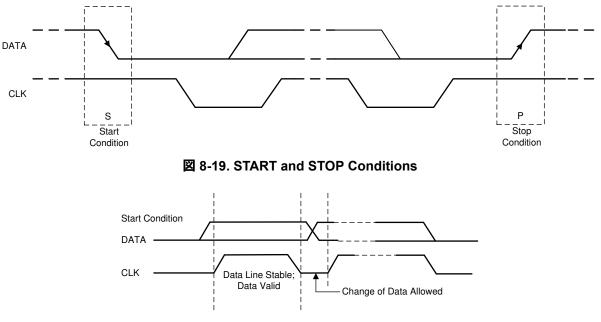

|                        |                                          | for DCDC1 with VINDCDCx = 3.6 V, D = 100%                                                                                                                                                 |       | 60   | 100  | mΩ    |