TPSF12C1-Q1 JAJSOC4A - NOVEMBER 2022 - REVISED APRIL 2023

# TPSF12C1-Q1 単相、AC、車載用電源システムの同相ノイズ低減用スタンドア ロン、アクティブ、EMI フィルタ

### 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- デバイス温度グレード 1:動作時周囲温度範 囲:-40℃~+125℃

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可

- 電圧センス、電流注入アクティブ EMI フィルタ

- CISPR 25 Class 5 車載用 EMI 要件に最適化

- 同相放射に対して低インピーダンス

- チョーク・サイズ、重量、コストを **50%** 以上低減

- ピーク注入電流 ±80mA (標準値)

- 広い電源電圧範囲:8V~16V

- 接合部温度範囲:-40℃~150℃

- 単相 AC システムのシンプルな構成

- センシング・フィルタと加算ネットワークを内蔵

- ライン周波数での低リーク電流

- 簡略化された補償ネットワーク

- 堅牢な設計のための本質的な保護機能

- 最小限の外付け部品で 6kV のサージ (IEC) 61000-4-5) に対応

- イネーブル・ピンによりリモートでオン / オフ制御

- ヒステリシス付きの VDD 電圧 UVLO 保護

- ヒステリシス付きのサーマル・シャットダウン保護

- 4.2mm × 2mm SOT-23 14 ピン (DYY) パッケージ

# 2 アプリケーション

- BEV と PHEV 向けのオンボード・チャージャ

- 車載絶縁型 DC/DC レギュレータ

- HVAC モーター制御、航空宇宙、防衛

### 3 概要

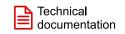

TPSF12C1-Q1 は、単相 AC 電源システムの同相 (CM) 電磁干渉 (EMI) を低減するよう設計されたアクティブ・フィ ルタIC です。

電圧センスと電流注入 (VSCI) を使用して構成されたアク ティブ EMI フィルタ (AEF) は、容量性マルチプライヤ回 路を使用して、従来型のパッシブ・フィルタ設計で Y コン デンサをエミュレートします。このデバイスは、一連のセン ス・コンデンサを使用して各電力線の高周波数ノイズを検 出し、注入コンデンサを使用してノイズ・キャンセル電流を 電力線に戻します。実効アクティブ容量は、回路のゲイン と注入容量によって設定されます。 AEF センシングおよび 注入インピーダンスは、小さい部品フットプリントで比較的 小さい容量値を使用します。このデバイスには、フィルタリ ング、補償および保護回路、イネーブル入力が内蔵され ています。

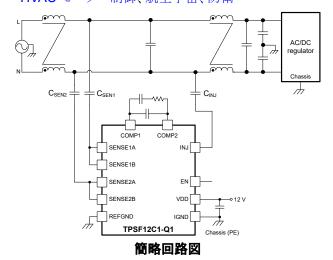

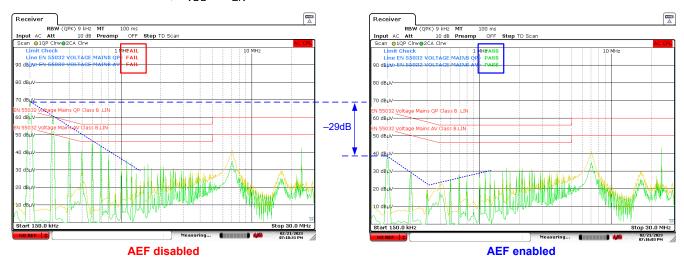

TPSF12C1-Q1 は、EMI 測定の対象となる周波数範囲 で、CM ノイズに対して非常に低いインピーダンス・パスを 実現します。仕様の周波数範囲の下限 (150kHz~3MHz など) で最大 30dB の CM ノイズ低減を実現すると、CM フィルタ実装のサイズ、重量、コストを大幅に削減できま

#### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup>  | 本体サイズ (公称)      |

|-------------|-----------------------|-----------------|

| TPSF12C1-Q1 | DYY (SOT-23-THIN, 14) | 4.20mm × 2.00mm |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

## **Table of Contents**

| 1 特長1                                               | 8.3 Feature Description                 | 10   |

|-----------------------------------------------------|-----------------------------------------|------|

| 2 アプリケーション1                                         | 8.4 Device Functional Modes             |      |

| 3 概要                                                | 9 Applications and Implementation       | 13   |

| 4 Revision History                                  | 9.1 Application Information             | 13   |

| 5 Device Comparison Table 3                         | 9.2 Typical Applications                |      |

| 6 Pin Configuration and Functions                   | 9.3 Power Supply Recommendations        |      |

| 7 Specifications                                    | 9.4 Layout                              |      |

| 7.1 Absolute Maximum Ratings                        | 10 Device and Documentation Support     |      |

| 7.2 ESD Ratings                                     | 10.1 Device Support                     | 24   |

| 7.3 Recommended Operating Conditions4               | 10.2 Documentation Support              |      |

| 7.4 Thermal Information                             | 10.3ドキュメントの更新通知を受け取る方法                  |      |

| 7.5 Electrical Characteristics                      | 10.4 サポート・リソース                          |      |

| 7.6 System Characteristics7                         | 10.5 Trademarks                         |      |

| 7.7 Typical Characteristics8                        | 10.6 静電気放電に関する注意事項                      |      |

| 8 Detailed Description9                             | 10.7 用語集                                |      |

| 8.1 Overview9                                       | 11 Mechanical, Packaging, and Orderable | 20   |

| 8.2 Functional Block Diagram9                       | Information                             | 25   |

| 4 Revision History                                  |                                         |      |

| Changes from Revision * (November 2022) to Revision | on A (April 2023)                       | Page |

- ステータスを「事前情報」から「量産データ」に変更......1

# **5 Device Comparison Table**

| DEVICE      | ORDERABLE PART NUMBER | PHASES | GRADE      | JUNCTION TEMPERATURE RANGE |

|-------------|-----------------------|--------|------------|----------------------------|

| TPSF12C1-Q1 | TPSF12C1QDYYRQ1       | 1      | Automotive | –40°C to 150°C             |

| TPSF12C3-Q1 | TPSF12C3QDYYRQ1       | 3      | Automotive | –40°C to 150°C             |

| TPSF12C1    | TPSF12C1DYYR          | 1      | Commercial | –40°C to 150°C             |

| TPSF12C3    | TPSF12C3DYYR          | 3      | Commerical | –40°C to 150°C             |

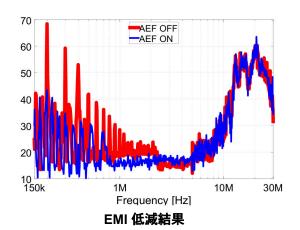

# **6 Pin Configuration and Functions**

図 6-1. 14-Pin SOT-23-THIN DYY Package (Top View)

表 6-1. Pin Functions

|          | PIN     | TYPE(1) | DESCRIPTION                                                            |

|----------|---------|---------|------------------------------------------------------------------------|

| NO.      | NAME    | 1166    | DESCRIFTION                                                            |

| 1, 3, 12 | NC      | _       | No internal connection. Tie to the GND plane on the PCB.               |

| 2        | VDD     | Р       | Power supply for IC. Bypass to IGND with a 1-µF X7R ceramic capacitor. |

| 4        | SENSE1A | I       | Sense input (power line or neutral)                                    |

| 5        | SENSE1B | I       | Sense input (power line or neutral)                                    |

| 6        | SENSE2A | I       | Sense input (power line or neutral)                                    |

| 7        | SENSE2B | I       | Sense input (power line or neutral)                                    |

| 8        | EN      | I       | Enable signal to activate noise cancellation                           |

| 9        | REFGND  | G       | Reference ground (Kelvin connected to IGND)                            |

| 10       | COMP1   | I       | Connection 1 for external compensation circuit                         |

| 11       | COMP2   | I       | Connection 2 for external compensation circuit                         |

| 13       | INJ     | 0       | Injection signal output                                                |

| 14       | IGND    | G       | Injection ground                                                       |

(1) P = Power, G = Ground, I = Input, O = Output

# 7 Specifications

## 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)(1)

|                  |                                              | MIN  | MAX       | UNIT |

|------------------|----------------------------------------------|------|-----------|------|

| Pin voltage      | VDD to IGND and REFGND                       | -0.3 | 18        | V    |

| Pin voltage      | SENSE1A, SENSE1B, SENSE2A, SENSE2B to REFGND | -5.5 | 5.5       | V    |

| Pin voltage      | COMP1 to IGND and REFGND                     | -0.3 | 5.5       | V    |

| Pin voltage      | COMP2 to IGND and REFGND                     | -0.3 | 15        | V    |

| Pin voltage      | INJ to IGND                                  | -0.3 | $V_{VDD}$ | V    |

| Pin voltage      | EN to IGND and REFGND                        | -0.3 | 18        | V    |

| Pin voltage      | IGND to REFGND                               | -0.3 | 0.3       | V    |

| Sink current     | INJ                                          |      | 150       | mA   |

| Source current   | INJ                                          |      | 150       | mA   |

| T <sub>J</sub>   | Operating junction temperature               | -40  | 150       | °C   |

| T <sub>stg</sub> | Storage temperature                          | -55  | 150       | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 7.2 ESD Ratings

|                    |               |                                                                                           |                               | VALUE | UNIT |

|--------------------|---------------|-------------------------------------------------------------------------------------------|-------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD classification level 2 |                               | ±2000 | .,   |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per AEC Q100-011                                              | Corner pins (1, 7, 8, and 14) | ±750  | V    |

|                    |               | CDM ESD classification level C4B                                                          | Other pins                    | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)

|                    |                               |                           | MIN | NOM | MAX                  | UNIT |

|--------------------|-------------------------------|---------------------------|-----|-----|----------------------|------|

| $V_{VDD}$          | VDD voltage range             | VDD voltage range         |     | 12  | 16                   | V    |

| V <sub>INJ</sub>   | Output voltage range          | Output voltage range      |     |     | V <sub>VDD</sub> – 2 | V    |

| V <sub>SENSE</sub> | Sense voltage range           |                           | -5  |     | 5                    | V    |

| V <sub>EN</sub>    | Pin voltage                   |                           | 0   |     | 16                   | V    |

| I <sub>INJ</sub>   | Output current range          | Source and sink magnitude |     |     | 80                   | mA   |

| T <sub>A</sub>     | Operating ambient temperature |                           | -40 |     | 105                  | °C   |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

### 7.4 Thermal Information

|                        | THERMAL METRIC <sup>(1)</sup>                | DYY (SOT-23-THIN) | UNIT |

|------------------------|----------------------------------------------|-------------------|------|

| THERMAL METRIC         |                                              | 14 PINS           | ONII |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 94                | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 43                | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 30                | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 1.3               | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 28                | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see Semiconductor and IC Package Thermal Metrics application report.

### 7.5 Electrical Characteristics

Limits apply over the junction temperature ( $T_J$ ) range of  $-40^{\circ}$ C to 150°C, unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{VDD} = 12$   $V^{(1)}$ .

|                         | PARAMETER                                                | TEST CONDITIONS                                                                                 | MIN  | TYP  | MAX  | UNIT |

|-------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY                  |                                                          |                                                                                                 |      |      | 1    |      |

| 1                       | VDD quiescent current                                    | SENSE1A, SENSE1B, SENSE2A, and SENSE2B grounded, $V_{EN}$ = 5 V, 8 V $\leq$ $V_{VDD} \leq$ 16 V | 6.25 | 13.2 | 25.5 | mA   |

| IQ                      | VDD quiescent current                                    | SENSE1A, SENSE1B, SENSE2A, and SENSE2B grounded, $V_{EN}$ = 5 V, $V_{VDD}$ = 12 V, $T_J$ = 25°C | 11   | 13.2 | 15.5 | IIIA |

| I <sub>SD</sub>         | VDD shutdown supply current                              | V <sub>EN</sub> = 0 V                                                                           |      | 55   |      | μA   |

| SUPPLY VOLT             | AGE UVLO                                                 |                                                                                                 |      |      | •    |      |

| V <sub>VDD-UV-R</sub>   | UVLO rising threshold                                    | V <sub>VDD</sub> rising                                                                         | 7.35 | 7.7  | 7.95 | V    |

| V <sub>VDD-UV-F</sub>   | UVLO falling threshold                                   | V <sub>VDD</sub> falling                                                                        | 6.4  | 6.7  | 7.0  | V    |

| V <sub>VDD-UV-HYS</sub> | UVLO hysteresis                                          |                                                                                                 |      | 0.97 |      | V    |

| ENABLE                  |                                                          |                                                                                                 |      |      |      |      |

| V <sub>EN-H</sub>       | EN voltage high                                          |                                                                                                 | 2.2  |      |      | V    |

| V <sub>EN-L</sub>       | EN voltage low                                           |                                                                                                 |      |      | 0.8  | V    |

| R <sub>EN</sub>         | EN pin pull-up resistance to VDD                         | V <sub>EN</sub> = 0 V                                                                           |      | 850  |      | kΩ   |

| I <sub>EN-LKG</sub>     | EN input leakage current                                 | V <sub>EN</sub> = 12 V                                                                          |      | 840  |      | nA   |

| INPUT FILTER            | NETWORK                                                  |                                                                                                 |      |      | '    |      |

|                         |                                                          | $C_{SEN} = 2 \mu F^{(2)}, 60 \text{ Hz}$                                                        |      | -44  |      |      |

| A <sub>CM</sub>         | Gain from shorted power lines through                    |                                                                                                 |      | -4   |      | -ID  |

|                         | single sense cap, C <sub>SEN</sub> , to COMP1 vs. REFGND | $C_{SEN} = 2 \mu F^{(2)}, 500 \text{ kHz}^{(3)}$                                                |      | -2   | dB   |      |

|                         |                                                          | $C_{SEN} = 2 \mu F^{(2)}, 1 \text{ MHz}^{(3)}$                                                  |      | -1   |      |      |

### 7.5 Electrical Characteristics (continued)

Limits apply over the junction temperature ( $T_J$ ) range of  $-40^{\circ}$ C to 150°C, unless otherwise stated. Minimum and maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$  = 25°C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{VDD}$  = 12  $V^{(1)}$ .

|                         | PARAMETER                                                                | TEST CONDITIONS                                                                                                                                    | MIN                  | TYP        | MAX | UNIT |

|-------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------------|-----|------|

|                         |                                                                          | SENSE1A shorted to SENSE1B,<br>SENSE2A shorted to SENSE2B,<br>$C_{SEN1} = C_{SEN2} = 1 \mu F^{(2)}$ , 60 Hz                                        |                      | <b>-71</b> |     |      |

| A <sub>DM</sub>         |                                                                          | SENSE1A shorted to SENSE1B,<br>SENSE2A shorted to SENSE2B,<br>$C_{SEN1} = C_{SEN2} = 1 \mu F^{(2)}$ , 1 kHz                                        |                      | -59        |     |      |

|                         | Gain from differential signal applied to SENSE lines to COMP1 vs. REFGND | SENSE1A shorted to SENSE1B,<br>SENSE2A shorted to SENSE2B,<br>C <sub>SEN1</sub> = C <sub>SEN2</sub> = 1 µF <sup>(2)</sup> , 500 kHz <sup>(3)</sup> |                      | -42        |     | dB   |

|                         |                                                                          | SENSE1A shorted to SENSE1B,<br>SENSE2A shorted to SENSE2B,<br>$C_{SEN1} = C_{SEN2} = 1 \mu F^{(2)}, 1 \text{ MHz}^{(3)}$                           |                      | -43        |     |      |

|                         |                                                                          | SENSE1A shorted to SENSE1B,<br>SENSE2A shorted to SENSE2B,<br>$C_{SEN1} = C_{SEN2} = 1 \mu F^{(2)}$ , 10 MHz <sup>(3)</sup>                        |                      | -35        |     |      |

| AMPLIFIER               |                                                                          |                                                                                                                                                    |                      |            | ·   |      |

| A <sub>DC</sub>         | DC gain                                                                  |                                                                                                                                                    | 52                   | 58         | 69  | dB   |

| f <sub>BW</sub>         | Unity gain bandwidth <sup>(3)</sup>                                      |                                                                                                                                                    |                      | 113        |     | MHz  |

| f <sub>BW40</sub>       | 40 dB gain frequency                                                     |                                                                                                                                                    |                      | 1          |     | MHz  |

| V <sub>OFST</sub>       | COMP1 offset voltage                                                     |                                                                                                                                                    |                      | 2          |     | V    |

| V <sub>INJ-MAX</sub>    | Maximum output voltage for linear operation <sup>(3)</sup>               | COMP2 to INJ gain > 36 dB                                                                                                                          | V <sub>VDD</sub> – 2 |            |     | V    |

| V <sub>INJ-MIN</sub>    | Minimum output voltage for linear operation <sup>(3)</sup>               | COMP2 to INJ gain > 36 dB                                                                                                                          |                      |            | 2.5 | V    |

| I <sub>INJ-MAX-OP</sub> | INJ current at linearity limits <sup>(3)</sup>                           | $V_{INJ} = V_{VDD} - 2 V$                                                                                                                          | 80                   |            |     | mA   |

| 'INJ-WAX-OP             | into current at inicarity infine                                         | $V_{INJ} = V_{IGND} + 2.5 V$                                                                                                                       |                      |            | -80 | mA   |

| PSRR                    |                                                                          |                                                                                                                                                    |                      |            |     |      |

| PSRR <sub>10</sub>      |                                                                          | 10 pF in parallel with the series combination of 10 nF and 2 k $\Omega$ between COMP1 and COMP2, 10 kHz                                            |                      | 0          |     |      |

| PSRR <sub>100</sub>     |                                                                          | 10 pF in parallel with the series combination of 10 nF and 2 k $\Omega$ between COMP1 and COMP2, 100 kHz                                           |                      | 6          |     | dB   |

| STARTUP                 |                                                                          |                                                                                                                                                    |                      |            |     |      |

| t <sub>W</sub>          | Startup delay <sup>(3)</sup>                                             | Time from VDD = EN applied until output valid                                                                                                      |                      | 43         |     | ms   |

| t <sub>SU</sub>         | EN high to valid output                                                  |                                                                                                                                                    |                      | 42         |     | ms   |

| t <sub>SD</sub>         | EN low to stop output signal                                             |                                                                                                                                                    |                      | 0.32       |     | μs   |

| THERMAL SH              | UTDOWN                                                                   |                                                                                                                                                    |                      |            | 1   |      |

| T <sub>J-SHD</sub>      | Thermal shutdown threshold <sup>(3)</sup>                                | Temperature rising                                                                                                                                 |                      | 175        |     | °C   |

| T <sub>J-HYS</sub>      | Thermal shutdown hysteresis <sup>(3)</sup>                               |                                                                                                                                                    |                      | 20         |     | °C   |

|                         |                                                                          |                                                                                                                                                    |                      |            |     |      |

<sup>(1)</sup> MIN and MAX limits are 100% production tested at 25°C unless otherwise specified. Limits over the operating temperature range verified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> Capacitance chosen for effective test only. Do not use this capacitance in applications.

<sup>(3)</sup> Parameter specified by design, statistical analysis and production testing of correlated parameters.

### 7.6 System Characteristics

The following specifications apply only to the typical applications circuit, with nominal component values. Specifications in the typical (TYP) column apply to  $T_J$  = 25°C and  $V_{VDD}$  = 12 V only. Specifications in the minimum (MIN) and maximum (MAX) columns apply to the case of typical components over the temperature range of  $T_J$  = -40°C to 150°C. These specifications are not ensured by production testing.

| PARAMETER           |                                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------------------|-----------------|-----|-----|-----|------|

| SUPPLY              |                                      |                 |     |     |     |      |

| I <sub>SUPPLY</sub> | Input supply current with INJ loaded |                 |     | 15  |     | mA   |

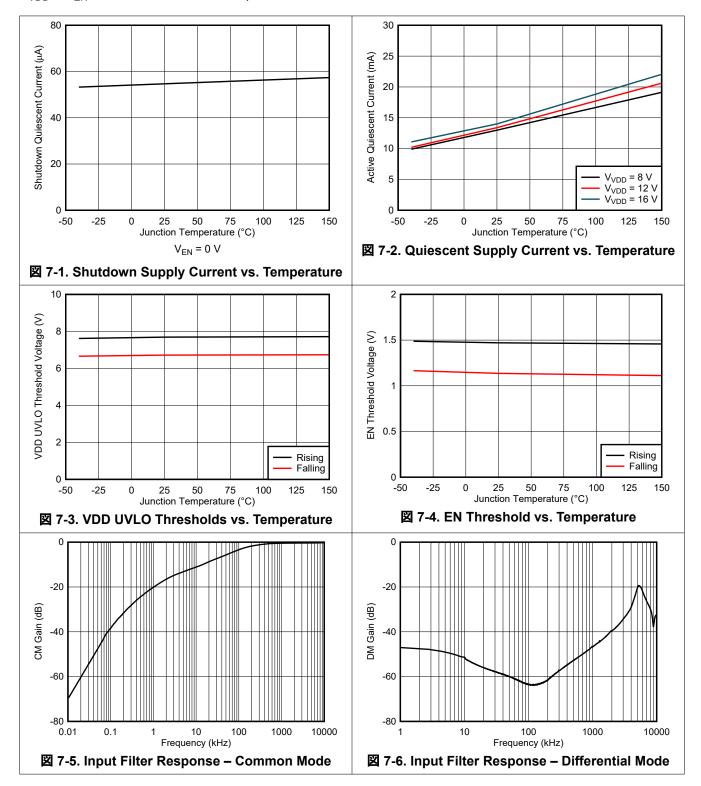

## 7.7 Typical Characteristics

$V_{VDD} = V_{EN} = 12 \text{ V}$ , unless otherwise specified.

English Data Sheet: SNVSCB7

### 8 Detailed Description

### 8.1 Overview

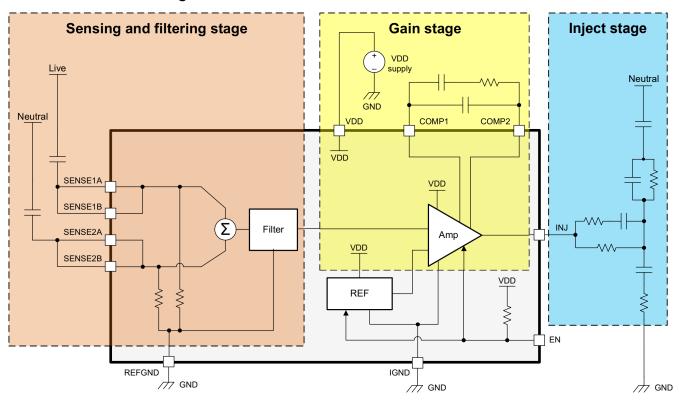

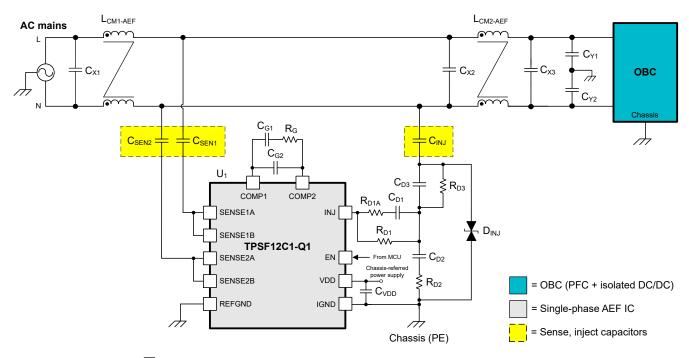

The TPSF12C1-Q1 is an active electromagnetic interference (EMI) filter that is designed to reduce common-mode (CM) conducted emissions in off-line power converter systems. Using a VSCI architecture, the device senses the high-frequency noise on each power line using a set of Y-rated capacitors,  $C_{SEN1}$  and  $C_{SEN2}$ , then injects noise-canceling currents back into the power lines using a Y-rated capacitor,  $C_{INJ}$ , along with a damping circuit that ensures stability. The device includes integrated filtering, compensation and protection circuitry.

The TPSF12C1-Q1 provides a low-impedance shunt path for CM noise in the frequency range of interest for EMI measurement. This feature can achieve approximately 15 to 30 dB of CM attenuation over the applicable frequency range (for example, 100 kHz to 3 MHz) helping to reduce the size of CM chokes, typically the largest components in the filter.

The TPSF12C1-Q1 operates over a supply voltage range of 8 V to 16 V and can withstand 18 V. The device features include:

- · Internal circuitry that simplifies compensation and design

- Built-in supply voltage UVLO to ensure proper operation

- · Built-in thermal shutdown protection

- An EN input that allows power saving when the system is idling

The active EMI filter circuit significantly reduces EMI filter cost, size, and weight, while helping to meet CISPR 25 Class 5 limits for conducted emissions. Leveraging a pin arrangement designed for simple layout that requires relatively few external components, the TPSF12C1-Q1 is specified for maximum ambient and junction temperatures of 105°C and 150°C, respectively.

### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Active EMI Filtering

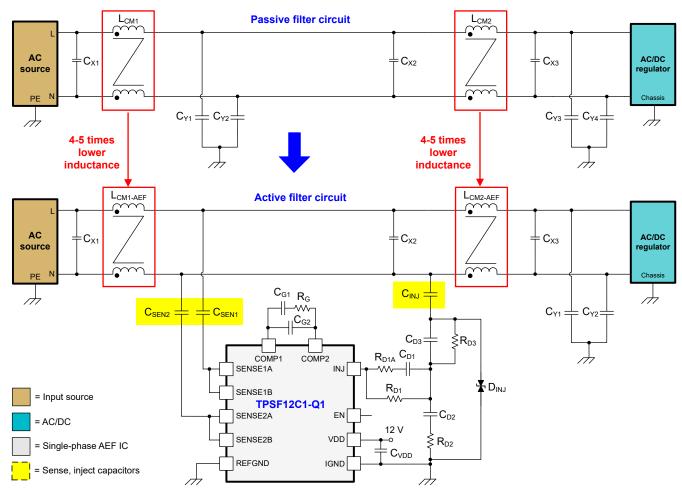

A compact and efficient design of the input EMI filter is one of the main challenges in high-density switching regulator design and is critical to achieving the full benefits of electrification in highly constrained system environments such as automotive. For AC-input applications in general, CM chokes and Y-capacitors provide CM filtering, whereas the leakage inductance of the CM chokes and the X-capacitors provide DM filtering. However, CM filters for such applications may have limited Y-capacitance due to touch-current safety requirements and thus require large-sized CM chokes to achieve the requisite attenuation – ultimately resulting in filter designs with bulky, heavy and expensive passive components. Fortunately, the deployment of active filter circuits enable more compact filter solutions for next-generation power conversion systems.

#### 8.3.1.1 Schematics

⊠ 8-1 shows a schematic of a conventional two-stage passive EMI filter in kilowatt-scale, grid-connected applications. L, N and PE refer to the respective live, neutral and protective earth connections. Multistage filters as shown provide high roll-off and are widely used in high-power AC line applications where CM noise is often more challenging to mitigate than DM noise. The low-order switching harmonics usually dictate the size of the reactive filter components based on the required corner frequency (or multiple corner frequencies in multistage designs).

☑ 8-1. Circuit Schematic of a Single-Phase Passive Filter and Corresponding Active Filter Solution for CM Attenuation

Also included in 🗵 8-1 is the corresponding active filter design. The active circuit replaces the two Y-capacitors positioned between the CM chokes with a single-phase AEF circuit using the TPSF12C1-Q1 to provide a lower impedance shunt path for CM currents. The sense pins of the TPSF12C1-Q1 interface with the power lines using a set of Y-rated sense capacitors, typically 680 pF, and feed into an internal high-pass filter and signal combiner. The IC rejects both line-frequency (50-Hz or 60-Hz) AC voltage as well as DM disturbances, while amplifying high-frequency CM disturbances and maintaining closed-loop stability using an external tunable damping circuit.

The X-capacitor placed between the two CM chokes in Z 8-1 effectively provide a low-impedance path between the power lines from a CM standpoint, typically up to low-MHz frequencies. This allows current injection onto one power line (usually neutral or the power line routed closest to the IC) using only one inject capacitor.

#### 8.3.2 Capacitive Amplification

An AEF circuit for CM noise mitigation fundamentally either amplifies the apparent inductance of a CM choke or the apparent capacitance of a Y-capacitor over the frequency range of interest. A VSCI AEF circuit configured for CM attenuation uses an amplifier stage as a capacitive multiplier of the inject capacitor, C<sub>IN.I</sub>. This higher value of the active capacitance supports lower values for the CM chokes to achieve a target attenuation. More specifically, the amplified Y-capacitance enables a reduction of each CM choke inductance by up to 80% (while keeping the filter corner frequencies effectively unchanged), resulting in lower size, weight, and cost of the CM chokes.

Capacitive multiplication of the inject capacitance occurs over a relevant frequency range for low- and midfrequency emissions, while not impacting the value at low frequency applicable for touch current measurement. The total capacitance of the sense and inject capacitors (highlighted in yellow in 🗵 8-1) is kept less than or equal to that of the replaced Y-capacitors in the equivalent passive filter, which results in the total line-frequency leakage current remaining effectively unchanged or reduced.

#### 8.3.3 Integrated Line Rejection Filter

The TPSF12C1-Q1 has a built-in input line filter. The high-pass filter stage attenuates the large line-frequency (50 Hz or 60 Hz) components of the power-line voltages, both line-to-line and line-to-earth, thus maximizing the useful voltage range of the low-voltage output at INJ.

The circuit also sums the signals in a CM combiner, rejecting the DM components of the voltages and extracting a signal that represents the CM noise signature without line-frequency components. Combined with the action of the high-pass filter, the net result is that the COMP1 pin voltage represents the sensed high-frequency CM noise that the device attempts to cancel. Because the entire filter is integrated in the device, matching is better than what can be achieved using discrete components.

#### 8.3.4 Compensation

The TPSF12C1-Q1 contains partial internal compensation that, when combined with two capacitors and a resistor between COMP1 and COMP2, forms a lead-lag network. This internal network allows fewer external components to be used.

#### 8.3.5 Remote Enable

The TPSF12C1-Q1 has an enable input, EN, that allows the device to be shut down, drastically reducing power consumption during intervals when EMI mitigation is not required. The typical quiescent current consumption is 13.2 mA and 55 µA when the device is enabled and disabled, respectively. Because many designs may not use this feature, a 850-k $\Omega$  pullup resistor connects internally between VDD and EN, allowing the EN pin to be left

In addition, INJ is pulled low when the device is disabled to reduce the effective resistance in series with C<sub>IN.I</sub>.

#### 8.3.6 Supply Voltage UVLO Protection

To ensure that the TPSF12C1-Q1 operates safely while VDD is powered on and off as well as during brownout conditions, this device has a built-in UVLO protection to provide predictable behavior while VDD is below its operating voltage. UVLO releases when the VDD voltage exceeds 7.7 V (typical), allowing normal operation. UVLO engages if the VDD voltage falls below approximately 6.7 V (typical). There is approximately 1 V of UVLO hysteresis.

#### 8.3.7 Thermal Shutdown Protection

The TPSF12C1-Q1 provides built-in overtemperature protection that shuts down the device if the junction temperature exceeds approximately 175°C. After the junction temperature decreases by approximately 20°C, the device restarts. This process is repeated until the ambient temperature or power dissipation is reduced. The device has a relatively low thermal time constant and can cycle into and out of thermal shutdown at a high rate during a sustained overtemperature condition.

#### 8.4 Device Functional Modes

#### 8.4.1 Shutdown Mode

The EN pin provides ON and OFF control for the TPSF12C1-Q1. When the EN voltage is below approximately 0.8 V, the device is in shutdown mode. Most internal circuitry is shutdown. The quiescent current in shutdown mode drops to 55  $\mu$ A (typical). The TPSF12C1-Q1 also employs VDD internal undervoltage protection. If the VDD voltage is below its UVLO threshold, the device remains off. The INJ output pulls to ground while in shutdown mode.

#### 8.4.2 Active Mode

The TPSF12C1-Q1 is in active mode when  $V_{VDD}$  is above its UVLO threshold, EN is high, and there is no overtemperature fault. The simplest way to enable operation is to connect EN to VDD, which allows startup when the applied supply voltage exceeds the UVLO threshold voltage. In this mode, the device amplifies signals on COMP2 and outputs the amplified signal on the INJ pin.

Product Folder Links: TPSF12C1-Q1

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 9 Applications and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

### 9.1 Application Information

The TPSF12C1-Q1 common-mode AEF IC helps to improve the CM EMI signature of single-phase power systems. The device provides a very low impedance path for CM noise in the frequency range of interest for EMI measurement and helps to meet prescribed limits for EMI standards, such as:

- CISPR 11, EN 55011 Industrial, Scientific and Medical (ISM) applications

- CISPR 25, EN 55025 Automotive applications

- CISPR 32, EN 55032 Multimedia applications

To expedite and streamline the process of designing of a TPSF12C1-Q1-based solution, a comprehensive TPSF12C1-Q1 quickstart calculator is available by download to assist the system designer with component selection for a given application.

### 9.2 Typical Applications

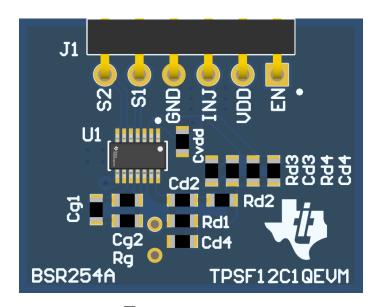

For the circuit schematic, bill of materials, PCB layout files, and test results of a TPSF12C1-Q1-powered implementation, see the TPSF12C1-Q1 EVM.

## 9.2.1 Design 1 - AEF Circuit for High-Density On-Board Charger (OBC) in Electric Vehicles (EVs)

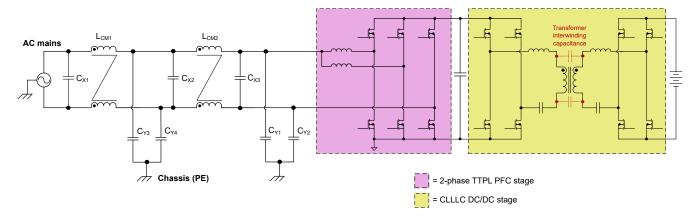

☑ 9-1 shows a schematic diagram of a 7.4-kW high-density OBC with conventional two-stage passive EMI filter. The CM chokes and Y-capacitors provide CM filtering, whereas the leakage inductance of the CM chokes and the X-capacitors provide DM filtering. Similar to TI reference designs TIDM-02013 and PMP22650, the circuit uses a two-phase totem-pole (TTPL) power-factor correction (PFC) front-end followed by a full-bridge CLLLC topology with active synchronous rectification.

The TTPL PFC stage runs at a fixed switching frequency of 100 kHz. The CLLLC isolated DC/DC stage runs at a variable frequency from 200 kHz to 800 kHz (500-kHz nominal) and provides galvanic isolation in addition to battery voltage and current regulation. Even though the use of LMG3522-Q1 GaN switches enables an open-frame power density of 3.8 kW/L, the conventional passive EMI filter occupies over 20% of the total solution size.

図 9-1. Circuit Schematic of an OBC With a Conventional Two-Stage EMI Filter

Note that the DC/DC stage in particular increases the CM EMI signature based on the high dv/dt of the GaN power switches, the transformer interwinding capacitance as well as the various switch-node parasitic capacitances to chassis ground.

This application example replaces the two Y-capacitors, designated as  $C_{Y3}$  and  $C_{Y4}$  in  $\boxtimes$  9-1, with a single-phase AEF circuit using the TPSF12C1-Q1. See  $\boxtimes$  9-2. The AEF circuit provides capacitive multiplication, which reduces the inductance value and thus the size, weight, and cost of the CM chokes, now designated as  $L_{CM1-AEF}$  and  $L_{CM2-AEF}$ . The total capacitance of the sense and inject capacitors is kept less than or equal to that of the replaced Y-capacitors, which results in the total line-frequency leakage current remaining effectively unchanged or reduced.

図 9-2. Circuit Schematic of an OBC With AEF Circuit Connected

#### 9.2.1.1 Design Requirements

表 9-1 shows the intended operating parameters for this application example. Also included is the total Y-rated filter capacitance that is allowed in order to meet the applicable touch current fault specification.

| DESIGN PARAMETER                           | VALUE              |

|--------------------------------------------|--------------------|

| AC input voltage range                     | 85 V to 265 V RMS  |

| AC input line frequency                    | 47 Hz to 63 Hz     |

| Input RMS current (maximum)                | 32 A               |

| DC output voltage range                    | 250 V to 450 V     |

| Rated output power                         | 7.4 kW             |

| Output current (maximum)                   | 20 A               |

| AC/DC stage switching frequency (fixed)    | 100 kHz            |

| DC/DC stage switching frequency (variable) | 200 kHz to 800 kHz |

| Total Y-rated filter capacitance (maximum) | 10 nF              |

表 9-1. Design Parameters

#### 9.2.1.2 Detailed Design Procedure

表 9-2 gives the selected component values, which are the same as those used in the TPSF12C1-Q1 EVM. This design uses a TVS diode placed at the low-voltage side of the inject capacitor for clamping during input surge conditions.

表 9-2. AEF Circuit Components for Application Circuit 1

| REFERENCE<br>DESIGNATOR                   | QTY | SPECIFICATION                                                    | MANUFACTURER <sup>(1)</sup> | PART NUMBER        |  |

|-------------------------------------------|-----|------------------------------------------------------------------|-----------------------------|--------------------|--|

| C <sub>SEN1</sub> , C <sub>SEN2</sub> (2) | 2   | Capacitor, ceramic, 680 pF, 300 VAC, Y2                          | MuRata                      | DE2B3SA681KN3AX02F |  |

| C <sub>INJ</sub> (2)                      | 1   | Capacitor, ceramic, 4.7 nF, 300 VAC, Y2                          | MuRata                      | DE2E3SA472MA3BX02F |  |

| C <sub>D1</sub> (2)                       | 1   | Capacitor, ceramic, 4.7 nF, 50 V, 0603                           | Various                     | _                  |  |

| C <sub>D2</sub> (2)                       | 1   | Capacitor, ceramic, 22 nF, 50 V, 0603                            | Various                     | _                  |  |

| C <sub>D3</sub>                           | 1   | Capacitor, ceramic, 4.7 nF, 50 V, 0603                           | Various                     | _                  |  |

| C <sub>G1</sub>                           | 1   | Capacitor, ceramic, 10 nF, 50 V, 0603                            | Various                     | _                  |  |

| C <sub>G2</sub>                           | 1   | Capacitor, ceramic, 10 pF, 50 V, 0603                            | Various                     | _                  |  |

| C <sub>VDD</sub>                          | 1   | Capacitor, ceramic, 1 µF, 25 V, X7R, 0603                        | Various                     | _                  |  |

| D <sub>INJ</sub>                          | 1   | TVS diode, bidirectional, 24 V, SOD-323                          | Eaton                       | STS321240B301      |  |

| R <sub>D1</sub>                           | 1   | Resistor, 1 kΩ, 0.1 W, 0603                                      | Various                     | _                  |  |

| R <sub>D1A</sub>                          | 1   | Resistor, 50 Ω, 0.1 W, 0603                                      | Various                     | _                  |  |

| R <sub>D2</sub>                           | 1   | Resistor, 200 Ω, 0.1 W, 0603                                     | Various                     | _                  |  |

| R <sub>D3</sub>                           | 1   | Resistor, 698 Ω, 0.1 W, 0603                                     | Various                     | _                  |  |

| R <sub>G</sub>                            | 1   | Resistor, 1.5 kΩ, 0.1 W, 0603                                    | Various                     | -                  |  |

| U <sub>1</sub>                            | 1   | TPSF12C1-Q1 common-mode AEF IC for single-phase AC power systems | Texas Instruments           | TPSF12C1QDYYRQ1    |  |

<sup>(1)</sup> See the Third-Party Products Disclaimer.

More generally, the TPSF12C1-Q1 AEF IC is designed to operate with a wide range of passive filter components and system parameters.

#### 9.2.1.2.1 Sense Capacitors

The sense pins of the TPSF12C1-Q1 feed into a high-pass filter and signal combiner within the IC, which rejects the line-frequency and DM components of the power line voltages, extracting the high-frequency CM component. These sense pins operate in pairs: SENSE1A and SENSE2A connect to SENSE1B and SENSE2B, respectively.

The sense pins externally interface to the power lines using Y-rated capacitors, designated as  $C_{SEN1}$  and  $C_{SEN2}$  in Figure 9-2. Choose Y2-rated sense capacitors of 680 pF, 300 VAC in this application to establish voltages at the SENSE pins of less than 1-V peak-to-peak when operating at maximum line voltage.

### 9.2.1.2.2 Inject Capacitor

The INJ node interfaces to a power line using a Y-rated capacitor, designated as  $C_{\text{INJ}}$  in Figure 9-2. Choose a Y2-rated inject capacitor of 4.7 nF, 300 VAC in this design to accommodate an AC voltage swing at INJ with at least a 2.5-V margin of headroom from the positive and negative supply rails. The INJ pin biases at half the VDD supply voltage. Assuming a 12-V supply rail and allowing 2.5 V of upper and lower headroom, this implies that a swing of  $\pm 3.5$  V is available around the DC operating midpoint.

<sup>(2)</sup> Check the effective capacitance value based on the applied voltage and operating temperature.

注

Many commercially available Y-rated capacitors yield an effective capacitance that derates significantly with operating temperature. The effective capacitance value can be much lower than the nameplate capacitance, particularly when operating near the boundaries of the rated operating temperature range. Select the dielectric of the sense and inject capacitors to meet the required temperature range. Depending on the implementation, lower than expected sense and inject capacitances can affect the stability performance.

#### 9.2.1.2.3 Compensation Network

The CM noise signal derived from the internal sensing filter and summation network of the TPSF12C1-Q1 is internally inverted and amplified by a gain stage. The components between the COMP1 and COMP2 pins of the IC, designated as as  $R_G$ ,  $C_{G1}$  and  $C_{G2}$  in Figure 9-2, set the gain characteristic.

More specifically, resistor  $R_G$  establishes a high midband AEF gain at frequencies where EMI filtering is required. Capacitor  $C_{G1}$  increases the impedance of that branch at low frequencies, which sets a lower AEF amplifer gain to further reject line-frequency components appearing at the INJ output. Capacitor  $C_{G2}$  preserves gain at high frequencies, which extends the AEF bandwidth.

Choose a value for  $R_G$  between 1 k $\Omega$  and 2 k $\Omega$ . A resistance of 1.5 k $\Omega$  is a common choice and selected in this example to set a midband gain of 50 dB. Choose capacitances for  $C_{G1}$  and  $C_{G2}$  of 10 nF and 10 pF, respectively, which establishes a gain rolloff below approximately 10 kHz for line- and low-frequency attenuation.

#### 9.2.1.2.4 Injection Network

The components connected between the INJ pin and inject capacitor establish a damped injection network. Damping is specifically required to manage resonance between the CM choke inductance and inject capacitance, which manifests in the AEF loop gain as a pair of complex zeros.

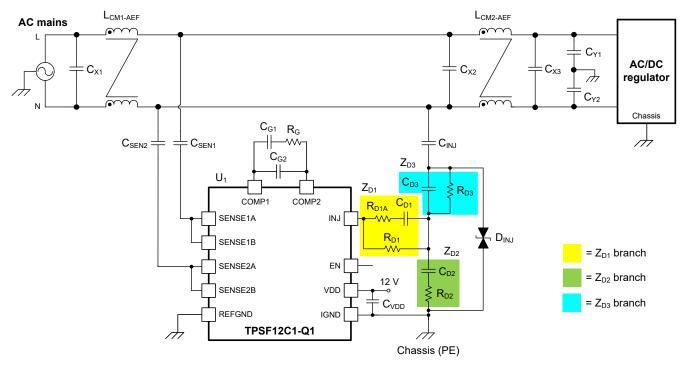

$\boxtimes$  9-3 highlights three specific RC branches:  $R_{D1}$ ,  $R_{D1A}$  and  $C_{D1}$  form one branch from the INJ pin;  $R_{D2}$  and  $C_{D2}$  in series connect to GND;  $R_{D3}$  and  $C_{D3}$  in parallel connect to the inject capacitor.

図 9-3. Injection Network

Based on the injection mechanism, the AEF circuit presents a low shunt impedance to CM noise. Given the three damping impedance branches highlighted in 図 9-3, 式 1 approximates the AEF impedance as:

$$Z_{AEF}(s) \approx \frac{Z_{INJ}(s) + Z_{D3}(s) + \left(Z_{D1}(s) \middle\| Z_{D2}(s)\right)}{1 - G_{AEF}(s) \cdot \frac{Z_{D2}(s)}{Z_{D1}(s) + Z_{D2}(s)}}$$

(1)

where the term  $G_{AEF}$  is the gain from the power lines to the INJ node (see the TPSF12C1-Q1 quickstart calculator for related detail).

$\pm$  1 shows that the impedance  $Z_{INJ}$  appears in series with  $Z_{D3}$  and a parallel combination of  $Z_{D1}$  and  $Z_{D2}$ . Furthermore, the gain  $G_{AEF}$  is reduced by the voltage divider ratio between  $Z_{D2}$  and  $Z_{D1}$ . These effects combine to increase the effective impedance of the AEF and hence reduce its attenuation performance, thus illustrating a trade-off between performance and stability.

So while an injection network is needed for stability, it also adds impedance in series with the inject capacitor, thus compromising EMI mitigation. As shown below, the user can minimize the impact on performance with careful and appropriate design.

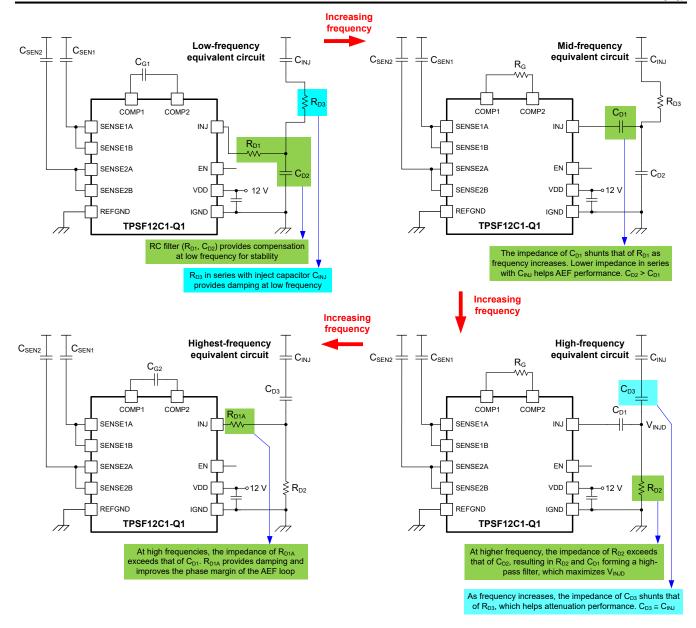

図 9-4. Dominant Components of the Injection Network vs Frequency

Illustrated in  $\boxtimes$  9-4, at low frequencies in the range of 5 kHz to 50 kHz, components R<sub>D1</sub> and C<sub>D2</sub> provide compensation and R<sub>D3</sub> damps the effects of LC resonance. At higher frequencies (above 10 kHz), the dominant component impedance of each branch transitions to enable better attenuation performance:

- R<sub>D1</sub> transitions to C<sub>D1</sub>

- C<sub>D2</sub> transitions to R<sub>D2</sub>

- R<sub>D3</sub> transitions to C<sub>D3</sub>

Finally,  $C_{D1}$  transitions to  $R_{D1A}$  if needed for phase margin of the AEF loop at high frequencies, typically above 100 kHz. When viewed in a clockwise direction,  $\boxtimes$  9-4 shows these transitions in sequence as frequency increases.

Below are basic guidelines to select the component values for the injection network:

1. The undamped loop gain characteristic is likely to be unstable within the range of 5 kHz to 50 kHz, which, as mentioned previously, relates to an LC resonance between CM choke inductance and inject capacitance.

Observe from circuit simulation – or by using the TPSF12C1-Q1 quickstart calculator – the frequency,  $f_{LFstability}$ , at which the phase crosses –180° with positive gain, indicating negative gain margin.

2. Choose a corner frequency with  $R_{D1}$  and  $C_{D2}$  equal to one fifth of the instability frequency:

$$\frac{1}{2\pi \cdot \mathsf{R}_{\mathsf{D1}} \cdot \mathsf{C}_{\mathsf{D2}}} = \frac{\mathsf{f}_{\mathsf{LFstability}}}{\mathsf{5}} \tag{2}$$

Assigning  $R_{D1}$  = 1 kΩ and assuming instablity at 35 kHz, use  $\pm$  3 to find a value for the capacitance of  $C_{D2}$ :

$$C_{D2}[nF] = \frac{5000}{2\pi \cdot R_{D1}[k\Omega] \cdot f_{LFstability}[kHz]} = \frac{5000}{2\pi \cdot 1 \cdot 35} = 22nF$$

(3)

- 3. Select  $C_{D1} < C_{D2}$ , where a typical choice is  $C_{D1} = C_{D2}/5 = 4.7$  nF.

- 4. Choose the resistance of  $R_{D2}$  such that the  $R_{D2}$ ,  $C_{D2}$  corner frequency is equal to that of  $R_{D1}$ ,  $C_{D1}$ :

$$R_{D2} \left[\Omega\right] = \frac{R_{D1} \left[\Omega\right] \cdot C_{D1} \left[nF\right]}{C_{D2} \left[nF\right]} = \frac{R_{D1} \left[\Omega\right]}{5} = \frac{1000}{5} = 200 \Omega \tag{4}$$

- 5. Select the resistance of R<sub>D3</sub> to damp the resonance around the instability frequency, f<sub>LFstability</sub>.

- A typical choice for R<sub>D3</sub> is 500 Ω to 1 kΩ.

- Assign C<sub>D3</sub> equal to C<sub>INJ</sub> or a suitable value such that the R<sub>D3</sub>, C<sub>D3</sub> corner frequency is less than switching frequency.

- A lower resistance for R<sub>D3</sub> results in more damping but at the penalty of reduced high-frequency attenuation (or forces a higher value for C<sub>D3</sub> to maintain the applicable corner frequency below the switching frequency).

- 6. Select a resistance for  $R_{D1A}$  of 50  $\Omega$  to improve the phase margin of the AEF loop (if needed).

#### 9.2.1.2.5 Surge Protection

EMI filter designs, both passive and active, typically use MOVs connected from the power lines to chassis ground to clamp surge voltage transients. While the sense pins of the TPSF12C1-Q1 have internal clamp protection, the higher value of inject capacitance produces larger currents during surge events and thus requires external protection. Place a bidirectional TVS diode on the low-voltage side of the inject capacitor with standoff voltage of 24 V. Using the SOD-323 packaged device given in 表 9-2, clamping occurs at 40 V and 50 V with surge currents of 1 A and 8 A, respectively.

English Data Sheet: SNVSCB7

### 9.2.1.3 Application Curves

Unless otherwise indicated,  $V_{VDD} = V_{EN} = 12 \text{ V}$ .

注

A high DM noise signature may mask improvement in CM noise performance related to AEF. A reduction of CM choke inductance may also reduce leakage inductance, which could impact DM noise attenuation. Install higher X-capacitance or a discrete DM filter inductor to manage DM attenuation as needed. Also, use a DM-CM noise splitter to isolate the CM component of the measured total noise.

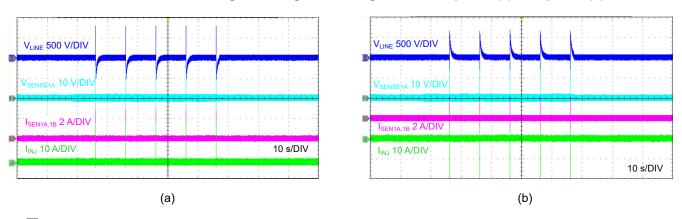

## 図 9-5. EMI Mitigation Result with AEF On and Off (EN Tied High and Low)

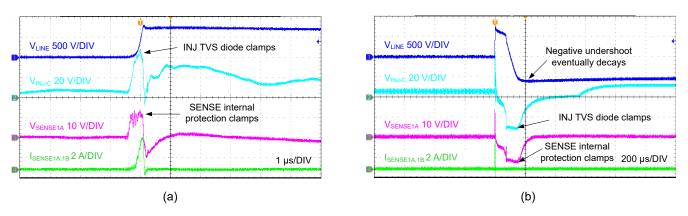

図 9-6. IEC 61000-4-5 Positive Surge, 5-kV Single Strike – 1 μs/div (a), 200 μs/div (b)

図 9-7. IEC 61000-4-5 Negative Surge, 5-kV Single Strike – 1 μs/div (a), 200 μs/div (b)

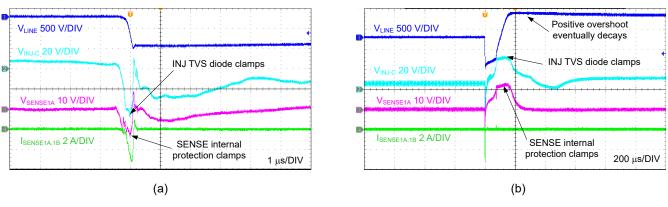

図 9-8. IEC 61000-4-5 Surge, 5-kV Repetitive Strike at 10-Second Intervals – Positive (a), Negative (b)

注

The surge test circuit used MOVs (Littelfuse V20E300P) connected from line and neutral filter inputs to chassis ground. See ☑ 9-11.

### 9.3 Power Supply Recommendations

The TPSF12C1-Q1 AEF IC operates over a wide supply voltage range of 8 V to 16 V (typically 12 V) and is referenced to chassis ground of the system. The characteristics of this VDD bias supply must be compatible with the *Absolute Maximum Ratings* and *Recommended Operating Conditions* in this data sheet. In addition, the VDD supply must be capable of delivering the required supply current to the loaded AEF circuit.

The supply rail can already be present in the system or can be derived using a low-cost solution with an auxiliary winding from an isolated flyback regulator. Connect a ceramic capacitor of at least 1 µF close to the VDD and IGND pins of the TPSF12C1-Q1. Ensure that the ripple voltage at VDD is less than 20 mV peak-to-peak to avoid low-frequency noise amplification.

### 9.4 Layout

Proper PCB design and layout is important in active EMI circuits (where high regulator voltage and current slew rates exist) to achieve reliable device operation and design robustness. Furthermore, the EMI performance of the design depends to a large extent on PCB layout.

#### 9.4.1 Layout Guidelines

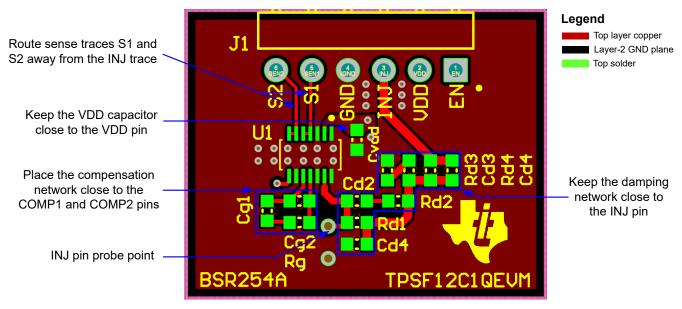

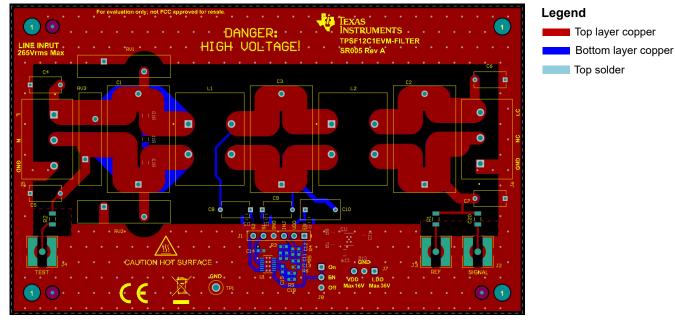

The following list summarizes the essential guidelines for PCB layout and component placement to optimze AEF performance.  $\boxtimes$  9-9 and  $\boxtimes$  9-10 show a recommended layout for the TPSF12C1-Q1 circuit specifically with optimized placement and routing of the IC and small-signal components.  $\boxtimes$  9-11 shows an example of a single-phase filter board design with with CM chokes, X-capacitors, Y-capacitors, protection components (such as

varistors and X-capacitor discharge resistors), and AEF circuit. The filter board includes a receptacle for easy connection of a single-phase AEF daughtercard EVM (instead of using the AEF components on the PCB).

- Position the sense and inject capacitors between the CM chokes near the X-capacitor that couples the injected signal to the other power line. Avoid placement close to the CM choke windings that may result in parasitic coupling to the sense and inject capacitors.

- Maintain adequate clearance spacing between high-voltage and low-voltage traces. As an example, ⊠ 9-11 has 150 mils (3.8 mm) copper-to-copper spacing from power lines (live and neutral) to chassis ground.

- Route the sense lines S1 and S2 away from the INJ line. Avoid coupling between the sense and inject traces.

- Use a solid ground connection between the TPSF12C1-Q1 and the filter board. Minimize parasitic inductance from the AEF circuit return to the chassis ground connections on the board.

- Place a ceramic capacitor close to VDD and IGND. Minimize the loop area to the VDD and IGND pins.

- Place the compensation network copponents close to the COMP1 and COMP2 pins. Reduce noise

sensitivity of the feedback compensation network path by placing components R<sub>G</sub>, C<sub>G1</sub> and C<sub>G2</sub> close to the

COMP pins. COMP2 is the inverting input to the AEF anplifier and represents a high-impedance node

sensitive to noise.

- Provide enough PCB area for proper heatsinking. Use sufficient copper area to acheive a low thermal impedance. Provide adequate heatsinking for the TPSF12C1-Q1 to keep the junction temperature below 150°C. A top-side ground plane is an important heat-dissipating area. Use several heat-sinking vias to connect REFGND (pin 9) and IGND (pin 14) to ground copper on other layers.

### 9.4.2 Layout Example

図 9-9. Typical Layout

図 9-10. Typical Top-Layer Design

図 9-11. Typical Single-Phase Filter Board Design With AEF

# 10 Device and Documentation Support

# 10.1 Device Support

### 10.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 10.1.2 Development Support

All AEF devices from the family shown in 表 10-1 are rated for a maximum junction temperature of 150°C and are functional safety-capable. See the Texas Instruments power-supply filter ICs landing page for more detail.

表 10-1. Common-mode AEF IC Family

|    | DEVICE    | ORDERABLE PART NUMBER | PHASES | GRADE      | JUNCTION TEMPERATURE RANGE |

|----|-----------|-----------------------|--------|------------|----------------------------|

| TP | SF12C1-Q1 | TPSF12C1QDYYRQ1       | 1      | Automotive | –40°C to 150°C             |

| TP | SF12C3-Q1 | TPSF12C3QDYYRQ1       | 3      | Automotive | -40°C to 150°C             |

| 7  | ΓPSF12C1  | TPSF12C1DYYR          | 1      | Commercial | -40°C to 150°C             |

| ٦  | ΓPSF12C3  | TPSF12C3DYYR          | 3      | Commercial | –40°C to 150°C             |

#### For development support see the following:

- TPSF12C1-Q1 quickstart calculator

- TPSF12C1-Q1 EVM Altium layout source files

- TPSF12C1-Q1 PSPICE for TI and SIMPLIS simulation models

- TPSF12C1-Q1 EVM user's guide

- For TI's reference design library, visit TI Reference Design library

- To design a low-EMI power supply, review TI's comprehensive EMI Training Series

- TI Reference Designs:

- 3-kW, 180-W/in3 single-phase totem-pole bridgeless PFC reference design with 16-A max input

- 1-kW reference design with CCM totem pole PFC and current-mode LLC realized by C2000™ and GaN

- 7.4-kW on-board charger reference design with CCM totem pole PFC and CLLLC DC/DC using C2000™ MCU

- GaN-based, 6.6-kW, bidirectional, onboard charger reference design

- 10-kW, bidirectional three-phase three-level (T-type) inverter and PFC reference design

- Technical Articles:

- Texas Instruments, How a stand-alone active EMI filter IC shrinks common-mode filter size

- Texas Instruments, How device-level features and package options can help minimize EMI in automotive designs

- Texas Instruments, How to use slew rate for EMI control

- White Papers:

- Texas Instruments, How Active EMI Filter ICs Mitigate Common-Mode Emissions and Save PCB Space in Single- and Three-Phase Systems

- Texas Instruments, An Overview of Conducted EMI Specifications for Power Supplies

- Texas Instruments, An Overview of Radiated EMI Specifications for Power Supplies

- Video:

- Texas Instruments, Single- and three-phase active EMI filter ICs mitigate common-mode EMI, save space and reduce cost

- To view a related device of this product, see the TPSF12C3-Q1 three-phase active EMI filter for common-mode noise mitigation or refer to the Texas Instruments power-supply filter ICs landing page

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# **10.2 Documentation Support**

#### 10.2.1 Related Documentation

For related documentation, see the following:

- Texas Instruments, TI pioneers the industry's first stand-alone active EMI filter ICs, supporting high-density power supply designs press release

- Texas Instruments, An Engineer's Guide To EMI In DC/DC Regulators e-book

- Texas Instruments, Reduce Buck Converter EMI and Voltage Stress by Minimizing Inductive Parasitics ADJ article

- Texas Instruments, Designing High Performance, Low-EMI, Automotive Power Supplies application report

- Texas Instruments, EMI Filter Components And Their Nonidealities For Automotive DC/DC Regulators technical brief

### 10.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.4 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 10.5 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 10.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.7 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# 11 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this datasheet, refer to the left-hand navigation.

www.ti.com 14-Jul-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|----------------------|---------|

| TPSF12C1QDYYRQ1  | ACTIVE | SOT-23-THIN  | DYY                | 14   | 3000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 150   | TPSF12C1Q1           | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF TPSF12C1-Q1:

# **PACKAGE OPTION ADDENDUM**

www.ti.com 14-Jul-2023

NOTE: Qualified Version Definitions:

• Catalog - TI's standard catalog product

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated