Design Guide: TIDA-020073

# Jacinto<sup>™</sup> 7 プロセッサ向け、100Base-T1 車載イーサネット拡張 のリファレンス デザイン

## 概要

このリファレンス デザインは、シリアル イーサネット拡張コネクタ経由で、Jacinto™ 7 プロセッサの評価基板 (EVM) に接続します。 車載イーサネット接続は、テキサス・インスツルメンツの車載イーサネット PHY を使用して追加されています。このデザインは、テキサス・インスツルメンツのDP83TC813S-Q1 100Mbps SPE (シングルペアイーサネット) PHY を使用して実装されています。12V をデータラインにカップリングするには、カップリングネットワークを使用します。

## リソース

TIDA-020073 デザイン フォルダ DP83TC813S-Q1 プロダクト フォルダ TPS629210-Q1、TPS7B82-Q1 プロダクト フォルダ

テキサス・インスツルメンツの **E2E™** サポート エキスパートにお問い合わせください。

## 特長

- SGMII を使用して Jacinto™ 7 プロセッサに接続された 100Base-T1 車載イーサネット

- 12V 電源カップリングに対応できる、車載認定取得済 みのフィルタネットワーク

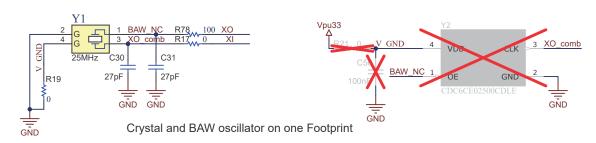

- テキサス・インスツルメンツの BAW 発振器 CDC6CEx-Q1 を 実装するオプション

- 識別用のボード ID EEPROM

## アプリケーション

- 先進運転支援システム (ADAS)

- ボディエレクトロニクスおよび照明

- インフォテインメントおよびクラスタ

- ソフトウェア定義自動車

## 1システムの説明

Jacinto™ 7 評価基板は、開発および評価用のプラットフォームであり、Jacinto™ 7 プロセッサ ファミリを利用したソフトウェア記述とハードウェア開発を可能にします。システムの主な要素は評価基板に搭載されています。これにより、Jacinto™ 7 プロセッサを含むほとんどの汎用型プロジェクトに必要な基本リソースを利用できます。基本リソース以外に、拡張カードを使用して機能を追加できます。

このリファレンス デザインは、テキサス・インスツルメンツの車載イーサネット PHY を使用して車載イーサネット コネクティビティを追加します。DP83TC813S-Q1 車載イーサネット PHY は、100Mbps リンク速度をサポートし、IEEE 802.3bw および OA 100BASE-T1 に準拠しており、小型フォームファクタの 28 ピン VQFN (5mm x 4mm) で供給されます。

#### 1.1 主なシステム仕様

TIDA-020073 の主な特長は次のとおりです。

- 100Base-T1 車載イーサネット

- デフォルト PHY アドレスを 15 に設定

- 12V を車載イーサネット ケーブルに接続可能

- テキサス・インスツルメンツの BAW 発振器を実装するオプション

- ボード識別用のボード ID EEPROM

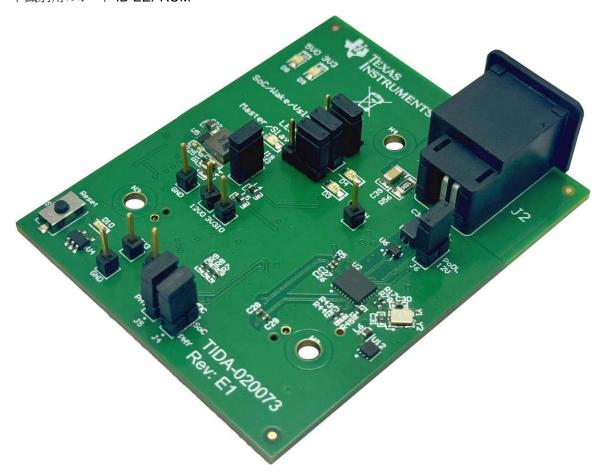

図 1-1. TIDA-020073 基板の外観

www.ti.com/ja-jp システム概要

## 2 システム概要

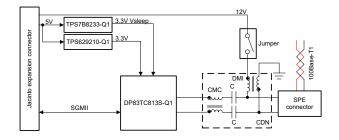

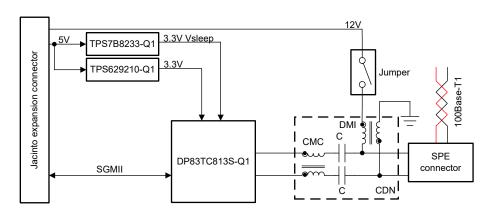

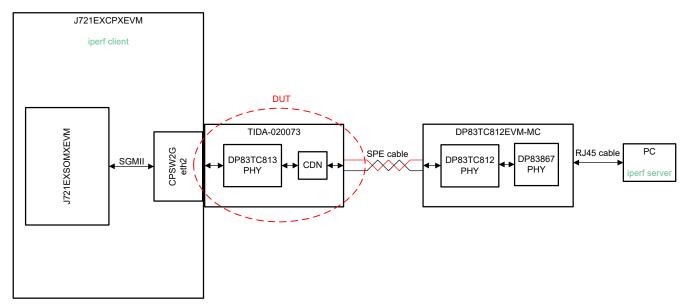

このシステムは、このリファレンスデザインで構成されており、図 2-1 に示すように、一方の側は拡張コネクタ経由で Jacinto 7 プロセッサ評価基板に接続され、もう一方の側は 1 本のツイストペア ケーブル経由でリンク パートナーに接続されています。

Jacinto 7 評価基板は、拡張コネクタを介して 5V の電力を降圧コンバータと 3.3V V<sub>SLEEP</sub> LDO に供給します。また、このデバイスは 12V をジャンパ J6 を介して差動モード インダクタ L7 に供給し、車載イーサネット ケーブルに電力をカップリングします。

#### 2.1 ブロック図

図 2-1. TIDA-020072 のブロック図

## 2.2 設計上の考慮事項

このリファレンス デザインでは、シングルペア イーサネット (SPE) PHY で構成されるイーサネット インターフェイスを実装する例と、同じケーブルでリンク パートナーに電力を供給するオプションを示します。これは、PoDL (データライン経由の電力供給) の一部です。PoDL は IEEE802.3bu で 100/1000Base-T1 用に標準化されていますが、このリファレンス デザインは、車載要件を満たすため IEEE802.3bu には準拠していません。車載分野では、自動車 OEM がシステムで使用される ECU とセンサ モジュールを定義するため、検出や分類は不要です。この想定は、車両の耐用年数を通じてネットワークが変化しないという事実に基づいています。これらのボードは、コスト効率と重量効率の高い実装に関する車載要件を満たすように設計されています。

電力をデータと同じケーブルで転送する場合、従来型のヒューズは使用できません。そのため、リンク パートナーの損傷を防ぐためにハイサイド スイッチ (HSS) を内蔵することを強くお勧めします。 データ ラインに電力をカップリングするための 12V 電源は、Jacinto 7 評価基板上で LM5175 昇降圧コンバータを使用して生成されます。 このデバイスは、サイクル単位の電流制限、出力過電圧保護 (OVP)、サーマル シャットダウンなどの保護機能をすでにサポートしています。

#### 2.3 主な使用製品

このセクションでは、本リファレンス デザインの主要なデバイスを紹介します。詳細については、各デバイスの製品ページ とデータシートをご覧ください。

## 2.3.1 DP83TC813S-Q1 (車載用 SPE PHY)

DP83TC813-Q1 デバイスは、IEEE 802.3bw 準拠の車載用 PHYTER™ イーサネット物理層トランシーバで、シールドなしツイストペア ケーブルに対応しています。この PHY は、TC10 スリープおよびウェイク機能をサポートしています。シールドなしの単一ツイストペア ケーブル上でデータを送受信するために必要な、すべての物理層機能が搭載されています。このデバイスは xMII の柔軟性があり、標準の MII、RMII、RGMII、SGMII MAC インターフェイスをサポートします。また、PHY の MDI 側にローパス フィルタが内蔵されており、放射を低減します。

このデバイスには診断ツールキットが含まれており、広範なリアルタイム監視ツール、デバッグツール、テストモードが用意されています。ツールキットには、初めて内蔵された静電放電 (ESD) 監視ツールが含まれています。このキットを使用すると、MDI上のESDイベントをカウントでき、プログラム可能な割り込みを使用してリアルタイム監視も行えます。さら

に、DP83TC813-Q1 には疑似ランダム バイナリシーケンス (PRBS) フレーム生成ツールが含まれており、内部ループバックと完全に互換で、MAC を使用せずデータを送受信します。本デバイスは、5.00mm × 4.00mm、28 ピンの VQFN ウェッタブル フランク パッケージに収容されています。

## 2.3.2 TPS629210-Q1 (3.3V レール降圧コンバータ)

車載認定済みの TPS6292xx-Q1 デバイスファミリは、使いやすく、高効率、小型、フレキシブルな同期整流式降圧 DC/DC コンバータです。入力電圧範囲が 3V~17V と広いため、12V、5V、3.3V の電源レールまたはシングル セル / マルチセルリチウムイオン バッテリで動作する各種システムに対応できます。 TPS629210-Q1 は、2.5MHz または 1MHz の強制 PWM モードまたは可変周波数 (自動 PFM) モードで動作するように構成できます。自動 PFM モードでは、軽負荷になると自動的にパワーセーブ モードに移行して高い効率を維持します。静止電流が 4μA (標準値) と低いことも、最小の負荷まで高い効率が得られる理由です。 テキサス・インスツルメンツの自動効率拡張 (AEE) モードを使うと、入力と出力の電圧に基づいてスイッチング周波数が自動的に調整されるため、同じインダクタを使っても動作範囲全域で高い変換効率を維持できます。 MODE/S-CONF 入力ピンは、スイッチング周波数の挙動の選択に加えて、外部および内部帰還分圧器の各種組み合わせと出力電圧放電機能のイネーブル / ディセーブルの選択にも使えます。 内部帰還構成では、FB/VSET ピンと GND の間に接続する抵抗の値によって 18 種類の出力電圧を選択できます。

#### 2.3.3 TPS7B8233-Q1 (3.3V V<sub>SLEEP</sub> 超低 I<sub>O</sub> 低ドロップアウト レギュレータ)

車載用のバッテリ接続アプリケーションでは、消費電力を削減し、バッテリ駆動時間を延長するため、静止電流 (IQ) が低いことが重要です。常時オンのシステムには超低静止電流 IQ が不可欠です。

TPS7B82-Q1 は低ドロップアウトのリニア レギュレータであり、3V~40V の広い入力電圧範囲 (45V の負荷ダンプ保護) で動作するよう設計されています。 TPS7B82-Q1 は最低 3V で動作するため、コールド クランクおよび始動 - 停止状態 の間も動作を継続できます。 軽負荷時の標準静止電流がわずか 2.7μA なので、スタンバイ システムのマイクロコントローラ (MCU) や CAN および LIN トランシーバの電源として最適です。

このデバイスには、短絡および過電流保護機能が内蔵されています。このデバイスは -40℃~+125℃の周囲温度、-40℃~+150℃の接合部温度で動作します。また、このデバイスは高放熱パッケージを採用しているため、デバイスの電力消費が大きくても持続的に動作できます。これらの特長から、このデバイスは各種の車載アプリケーションの電源として設計されていると言えます。

## 2.3.4 CDC6CE025000-Q1 (BAW 発振器)

テキサス・インスツルメンツのバルク弾性波 (BAW) は、超低ジッタ クロック回路を使用して高精度 BAW 共振器をパッケージに直接統合できるマイクロ共振器テクノロジーです。 BAW は、シリコン ベースのその他の製造プロセスと同様に TI の工場で全面的に設計および製造されています。

CDC6x デバイスは、共振器源として BAW を採用した超低ジッタ固定周波数発振器です。本デバイスは、特定の動作モードごとに、周波数、電圧、出力タイプ、機能ピンを含めて工場出荷時にプログラムされています。高性能フラクショナル分周器を備えた CDC6x は、規定された範囲内の任意の周波数を生成することが可能です。1 つのデバイス ファミリで、あらゆる周波数のニーズに対応することが可能となります。

このデバイスの高性能クロック供給、機械的安定性、フレキシビリティ、小型パッケージの選択肢は、通信、データおよびエンタープライズネットワーク、産業用アプリケーションで使用される高速 SERDES のリファレンスおよびコア クロック向けに設計されています。

www.ti.com/ja-jp システム設計理論

## 3システム設計理論

このセクションでは、本リファレンスデザインの各種ブロックの詳細について説明します。

#### 3.1 イーサネット PHY

このボードには、DP83TC813S-Q1 車載イーサネット PHY が搭載されています。この機能により、100Base-T1 を使用して車載イーサネットを評価できます。

#### 3.1.1 イーサネット PHY 電源

DP83TC813S-Q1 は、広い I/O 電源電圧範囲 (3.3V、2.5V、1.8V) で動作できます。このボードは 3.3V の I/O 電源電圧を供給して、3.3V の I/O 電圧に対応できる各種ベースボードとのインターフェイスを提供します。電源シーケンス制御は不要です。最新の電源デバイスに関する推奨事項については、『DP83TC813x-Q1 TC-10 準拠、小型フォームファクタ 100BASE-T1 車載用イーサネット PHY』データシートを参照してください。

#### 3.1.2 イーサネット PHY クロック ソース

図 3-1 に、水晶振動子の代わりにテキサス・インスツルメンツの BAW 発振器を使用するための、リファレンス デザインの 回路図とレイアウトを示します。 BAW 発振器 Y2 を使用するには、Y1、R19、R78、C30、C31 を取り外し、Y2、R21、C56 を取り付けてください。

図 3-1. イーサネット PHY クロック供給の回路図

#### 3.2 電源カップリング ネットワーク

カップリング ネットワークを選択する際に考慮する必要がある 2 つの主な要素は、リンク パートナーのイーサネット データレートと消費電力です。表 3-1 に、各イーサネット PHY と、対応するイーサネット規格およびデータ周波数を示します。

| 20 11 1 7 17 1 II 17 14 14 15 1 |             |            |          |  |  |

|---------------------------------|-------------|------------|----------|--|--|

| イーサネット PHY                      | IEEE 規格     | データレート     | シンボル レート |  |  |

| _                               | 10Base-T1S  | 10MBit/s   | 12.5MHz  |  |  |

| DP83TC812-Q1                    |             | 100MBit/s  | 66.6MHz  |  |  |

| DP83TC813-Q1                    | 100Base-T1  |            |          |  |  |

| DP83TC814-Q1                    | 1000ase-11  |            |          |  |  |

| DP83TC817-Q1                    |             |            |          |  |  |

| DP83TG720-Q1                    | 1000Base-T1 | 1000MBit/s | 750MHz   |  |  |

| DP83TG721-Q1                    | 1000Dase-11 |            |          |  |  |

表 3-1. イーサネット信号周波数

各カップリング ネットワークには、部品の飽和特性に基づいて必要なインピーダンスを維持しながらサポートできる最大電流があります。インダクタは理想的に動作するわけではなく、熱を放散し、非常に高い周波数を通過させ、過大な電流が流れると飽和します。回路全体にわたり、すべての部品とケーブルには、寄生容量と寄生インダクタンスがあります。リンクパートナーが消費する最大電力を把握すること、そして特定の電圧に対してその電力を供給できる部品デザインを選択することが重要です。リンクパートナー側の消費電力に関するワーストケースシナリオにおける最大電力を計算します。

表 3-2 に、カップリング ネットワークの設計例を示します。テキサス・インスツルメンツでは、目的の周波数範囲、電流定格、および温度に基づいて、いずれかのネットワークを選択することを推奨しています。

表 3-2. PoDL 用の CDN フィルタ設計

| メーカー | イーサネット<br>速度 | 部品                                      | 電流定格  | 温度<br>定格 |

|------|--------------|-----------------------------------------|-------|----------|

| TDK  | 100Base-T1   | CMC: ACT1210L-201<br>DMI: ADL32VHR-180M | 370mA | 150°C    |

## 4 ハードウェア、ソフトウェア、テスト要件、テスト結果

このセクションでは、最小限のセットアップで車載イーサネットを実証するための、ハードウェアとソフトウェアの基本的な要件について説明します。このセットアップでは、IP ネットワーク上で達成可能な最大帯域幅を測定できます。

## 4.1 ハードウェア要件

表 4-1 に、必要なハードウェアを示します。

デバイスの説明 部品番号 数量 1 × DP83TC813S-Q1 100Base-T1 車載イーサネット拡 TIDA-020073 張のリファレンス デザイン J721EXSOMXEVM 1 × Jacinto™ 7 システム オン モジュール (SoM) ボード J721EXCPXEVM 1 × Jacinto™ 7 プロセッサ向け共通プロセッサ ボード 1 × 100Mbps 向け、車載イーサネットから標準イーサネ DP83TC812EVM-MC ット メディア コンバータ 1 × TE 接続 MATEnet SPE ケーブル 1 × RJ45 ケーブル 12V、5A 電源

表 4-1. 最小限のセットアップに必要なハードウェア

## 4.2 ソフトウェア要件

このセクションでは、最小限のセットアップのソフトウェア要件について説明します。Jacinto™ 7 プロセッサ向けのソフトウェア開発キット (SDK) を使用すると、テスト中にこのリファレンス デザイン (図 4-1) のイーサネット PHY を制御および監視できます。

Jacinto™ 7 プロセッサでイーサネット PHY を識別できるようにするため、Linux SDK に車載イーサネット PHY ドライバを 追加する必要があります。『Linux ドライバをシステムに統合する方法』アプリケーション ノートを参照してください。

以下のコード ブロックは Jacinto™ 7 SDK v10 用で、PHY アドレス 15 用に構成されたこのボードの Linux デバイス ツリー オーバーレイを示しています。他の SDK バージョンについては、SDK の資料を参照してください。

```

/dts-v1/;

/plugin/;

#include <dt-bindings/gpio/gpio.h>

#include <dt-bindings/phy/phy.h>

#include <dt-bindings/phy/phy-cadence.h>

#include "k3-pinctrl.h"

#include "k3-serdes.h"

&{/} {

aliases {

ethernet2 = "/bus@100000/ethernet@c000000/ethernet-ports/port@2";

};

};

&cpsw0 {

status = "okay";

};

&cpsw0_port2 {

status = "okay";

}

```

```

phy-handle = <&cpsw9g_phy15>;

phy-mode = "sgmii";

pag address

mac-address = [00 00 00 00 00 00];

phys = <&cpsw0_phy_gmii_sel 2>;

};

&cpsw9g_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio0_pins_default>;

reset-gpios = <&exp2 17 GPIO_ACTIVE_LOW>;

reset-post-delay-us = <120000>;

\#address-cells = <1>;

#size-cells = <0>;

cpsw9g_phy15: ethernet-phy@15 {

reg = <15>;

};

};

&exp2 {

qsgmii-line-hog {

gpio-hog;

gpios = <16 GPIO_ACTIVE_HIGH>;

output-low;

line-name = "qsgmii-pwrdn-line";

};

};

&main_pmx0 {

mdio0_pins_default: mdio0-pins-default {

pinctrl-single,pins = <</pre>

J721E_IOPAD(0x1bc, PIN_OUTPUT, 0) /* (V24) MDIO0_MDC */

J721E_IOPAD(0x1b8, PIN_INPUT, 0) /* (V26) MDIO0_MDIO */

};

};

&serdes_ln_ctrl {

idle-states = <J721E_SERDESO_LANEO_PCIEO_LANEO>, <J721E_SERDESO_LANE1_QSGMII_LANE2>,

<J721E_SERDES1_LANEO_PCIE1_LANEO>, <J721E_SERDES1_LANE1_PCIE1_LANE1>,

<J721E_SERDES2_LANEO_PCIE2_LANEO>, <J721E_SERDES2_LANE1_PCIE2_LANE1>,

<J721E_SERDES3_LANE0_USB3_0_SWAP>, <J721E_SERDES3_LANE1_USB3_0>,

<J721E_SERDES4_LANE0_EDP_LANE0>, <J721E_SERDES4_LANE1_EDP_LANE1>,

<J721E_SERDES4_LANE2_EDP_LANE2>, <J721E_SERDES4_LANE3_EDP_LANE3>;

};

&serdes_wiz0 {

status = "okay";

};

&serdes0 {

status = "okay";

assigned-clocks = <&serdes0 CDNS_SIERRA_PLL_CMNLC>, <&serdes0 CDNS_SIERRA_PLL_CMNLC1>;

assigned-clock-parents = <&wiz0_pll1_refclk>, <&wiz0_pll1_refclk>;

#address-cells = <1>;

#size-cells = <0>;

serdes0_qsgmii_link: phy@1 {

reg = \langle 1 \rangle;

cdns,num-lanes = <1>;

#phy-cells = <0>;

cdns,phy-type = <PHY_TYPE_SGMII>;

resets = <&serdes_wiz0 2>;

};

};

```

PHY ドライバの追加に加えて、デバイス ツリーを調整し、SGMII インターフェイスをイネーブルにするため次の操作を行う必要があります。

ファイル: SDK\_Install\_Directory/board-support/ti-u-boot-<version>/configs/j721e\_evm\_a72\_defconfig

以下に示すように、次の2行を"#"でコメントアウトします。

# CONFIG\_PHY\_CADENCE\_SIERRA=y # CONFIG\_PHY\_J721E\_WIZ=y

その後、最上位の make コマンドを使用して u-boot を構築します。

make u-boot

ビルド バイナリ u-boot.img と tispl.bin を SD カードのブート パーティションにコピーします。

sudo cp SDK\_Install\_Directory/board-support/ti-u-boot-x/build/a72/u-boot.img /media/\$USER/boot sudo cp SDK\_Install\_Directory/board-support/ti-u-boot-x/build/a72/tispl.bin /media/\$USER/boot

次のコマンドを使用して、r5f0\_0-fw のリンクされたファームウェアを変更します。

$\label{limits} \begin{tabular}{ll} ln -sfn /usr/lib/firmware/ti-ipc/j721e/ipc\_echo\_test\_mcu2\_0\_release\_strip.xer5f /lib/firmware/j7-main-r5f0\_0-fw \end{tabular}$

ボードの電源を入れた状態で、次のターミナル コマンドを使用して PHY アドレス (phy[x]) と eth ポート (eth[y]) を確認します。

dmesg | grep mdio

davinci\_mdio c000f00.mdio: phy[15]: device c000f00.mdio:0f, driver TI DP83TC813CS2.0 am65-cpsw-nuss c000000.ethernet eth1: PHY [c000f00.mdio:0f] driver [TI DP83TC813CS2.0] (irq=POLL)

## 4.3 テスト構成

図 4-1 に、テスト構成のブロック図を示します。このセットアップは、Jacinto™ 7 プロセッサ評価基板、TIDA-020073、DP83TC812EVM-MC、標準的な PC、ケーブル アセンブリで構成されています。

図 4-1. IP ネットワーク帯域幅のテスト構成

ネットワークの性能と帯域幅を測定するオープンソースツールである iPerf3 はテキサス・インスツルメンツの SDK にすでに統合されており、イーサネットポートに IP アドレスを割り当てた後に次のコマンドで使用できます。

PC (サーバー) 上で次のコマンドを実行します。

iperf3 -s

さらに、Jacinto™ 7 (クライアント) 上で次のコマンドを実行します。

```

iperf3 -c 192.168.1.1 (the IP address of the server)

```

#### 4.4 テスト結果

次のターミナル メッセージは、Jacinto™ 7 評価基板でキャプチャされたものです。100Mbps 接続では、114MB (112MB) のデータが正常に転送され、帯域幅がネットワークポートの公表速度 (100Mbps) に非常に近いことを確認できます。

```

root@j721e-evm:~# iperf3 -c 192.168.1.1

Connecting to host 192.168.1.1, port 5201

[ 5] local 192.168.1.237 port 32836 connected to 192.168.1.1 port 5201

ID] Interval

Transfer

Bitrate

Retr

Cwnd

0.00-1.00

sec

12.6 MBytes

106 Mbits/sec

249 KBytes

10.9 MBytes

5]

1.00-2.00

sec

91.7 Mbits/sec

249 KBytes

11.4 MBytes

5]

2.00-3.00

95.9 Mbits/sec

249 KBytes

sec

249 KBytes

3.00-4.00

10.9 MBytes

91.7 Mbits/sec

5]

0

sec

5]

5]

4.00-5.00

sec

11.4 MBytes

95.9 Mbits/sec

0

249 KBytes

5.00-6.00

11.4 MBytes

95.9 Mbits/sec

249 KBytes

sec

5]

5]

6.00-7.00

10.9 MBytes

91.7 Mbits/sec

249 KBytes

sec

11.4 MBytes

249 KBytes

7.00-8.00

95.9 Mbits/sec

sec

10.9 MBytes

5]

8.00-9.00

sec

91.7 Mbits/sec

0

249 KBytes

5]

9.00-10.00

sec

11.4 MBytes

95.9 Mbits/sec

249 KBytes

ID]

Interval

Transfer

Bitrate

Retr

95.2 Mbits/sec

93.8 Mbits/sec

0.00-10.00 sec

114 MBytes

sender

0.00-10.05 sec

112 MBytes

receiver

iperf Done.

```

## 5 設計とドキュメントのサポート

## 5.1 デザイン ファイル

#### 5.1.1 回路図

回路図をダウンロードするには、TIDA-020073 のデザイン ファイルを参照してください。

#### 5.1.2 BOM

部品表 (BOM) をダウンロードするには、TIDA-020073 のデザイン ファイルを参照してください。

## 5.2 ツールとソフトウェア

#### ツール

ETHERNET-SW (イーサネット - SW) イーサネット PHY Linux ドライバおよびツール J721EXCPXEVM Jacinto™ 7 プロセッサ向け共通プロセッサ ボード

J721EXSOMXEVM TDA4VM および DRA829V システム オン モジュール (SoM)

#### ソフトウェア

PROCESSOR-SDK-J721E DRA829 と TDA4VM の各 Jacinto™ プロセッサ向けソフトウェア開発キット (SDK)

#### 5.3 ドキュメントのサポート

- 1. テキサス・インスツルメンツ、『Linux ドライバをシステムに統合する方法』アプリケーション ノート

- 2. テキサス・インスツルメンツ、『DP83TC813x-Q1 TC-10 準拠、 小型フォーム ファクタ 100BASE-T1 車載イーサネット PHY』データシート

- 3. テキサス・インスツルメンツ、『TDA4:カスタム ボード立ち上げガイド』アプリケーション ノート

- 4. テキサス・インスツルメンツ、『高速インターフェイスのレイアウト ガイドライン』アプリケーション ノート

#### 5.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパ ートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要 な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕 様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツ ルメンツの使用条件を参照してください。

#### 5.5 商標

Jacinto<sup>™</sup>. E2E<sup>™</sup>. テキサス・インスツルメンツ E2E<sup>™</sup>. and FPD-Link<sup>™</sup> are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

## 6 著者について

YANNIK MUENDLER は、テキサス・インスツルメンツのシステム エンジニアで、 車載 ADAS システム エンジニアリング チームに所属しており、車載分野のリファレンス デザインの開発において中心的な役割を果たしています。テキサス・イン スツルメンツ Jacinto™ 7 プロセッサを使用した高性能コンピューティング、シングルペア イーサネットや FPD-Link™ テク ノロジーといった通信インターフェイスなどの分野において豊富な専門知識を有しており、その職務に深い知識と経験を 活かしています。

Yannik は、ドイツのランツフート応用科学大学で電気工学の修士号を取得しています。

10

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated