# TPS27S100x IEC 61000-4-x Testing Using EVM Board

Mahmoud Harmouch, Kenneth Du

#### ABSTRACT

The IEC 61000-4-X set of standards are used to test system-level transient immunity. Many system designs used in an industrial environment specify one or more of the tests listed within the IEC 61000-4-X specification to comply with reliability standards for end customers. This document covers the TI high side switch TPS27S100 device immunity tests under the three most common industrial market requirements: System ESD Immunity (IEC 6100-4-2), Electrical Fast Transient Immunity (EFT) (IEC 61000-4-4), Lightning and Surge Immunity (IEC 61000-4-5). This document provides the test setup and results for each of these tests. Refer to *IEC 61000-4-x Tests for TI's Protection Devices* (SLVA711) for more details on test setup and procedures.

#### Contents

| Application Description | 2                                                                                                                                        |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| TPS27S100x EVM Board    | 3                                                                                                                                        |

| List of Equipment       | 3                                                                                                                                        |

|                         |                                                                                                                                          |

|                         |                                                                                                                                          |

|                         |                                                                                                                                          |

| References              |                                                                                                                                          |

|                         | List of Equipment<br>IEC 61000-4-2 System ESD Immunity<br>EMC IEC 61000-4-4 BURST Immunity Test<br>EMC IEC 61000-4-5 Surge Immunity Test |

#### List of Figures

| 1 | TPS27S100x EVM Schematic                 | 2 |

|---|------------------------------------------|---|

| 2 | TPS27S100x EVM Board (Standard) Top View | 3 |

| 3 | ESD Test Bench Setup                     | 5 |

| 4 | EFT Immunity Test Setup                  | 7 |

| 5 | Surge Immunity Test Setup                | 9 |

#### List of Tables

| 1  | List of Equipment                             | 3  |

|----|-----------------------------------------------|----|

| 2  | ESD Stress Levels                             | 4  |

| 3  | ESD Testing Contact Discharge Results         | 5  |

| 4  | ESD Testing Air Discharge Results             | 5  |

| 5  | EFT Stress Levels                             | 6  |

| 6  | EFT Testing Results of Supply Voltage Lines   | 7  |

| 7  | EFT Testing Results of Output Port            | 7  |

| 8  | Surge Stress Levels                           | 8  |

| 9  | Surge Testing Results of Supply Voltage Lines | 9  |

| 10 | Surge Testing Results of Output Port          | 10 |

|    |                                               |    |

#### Trademarks

All trademarks are the property of their respective owners.

#### Application Description

#### www.ti.com

#### 1 Application Description

These tests are based on TPS27S100 standard evaluation board TPS27S100x EVM.

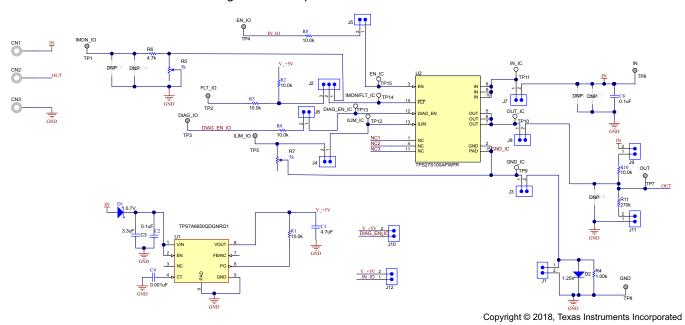

Figure 1 shows the schematic of the TPS27S100x EVM. The following will list some modifications of the board to survive the EMC tests and indicate the working status of the board:

- Add a 47 µF capacitor between supply voltage IN to GND

- Add a 0.1 µF at C7 position

- Add a TVS diode(SM15T30A) at C6 position

- Add a 22 nF ceramic capacitor at C9 position

- · Connect a LED with limiting resistor output to GND

Figure 1. TPS27S100x EVM Schematic

### 2 TPS27S100x EVM Board

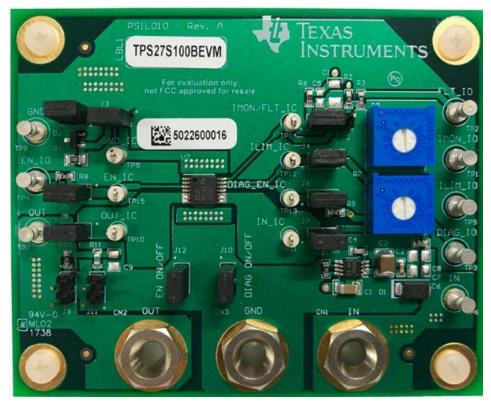

Figure 2 is the top view of the standard EVM board.

Figure 2. TPS27S100x EVM Board (Standard) Top View

#### 3 List of Equipment

Table 1 shows the list of required equipment.

#### Table 1. List of Equipment

| Qty | Equipment      | Description                                 |

|-----|----------------|---------------------------------------------|

| 1   | Transient 2000 | EFT and Surge generator, up to 4.4 kV       |

| 2   | CN-EFT1000     | Capacitive coupling clamp used for EFT test |

| 3   | 40 Ω, 0.5 μF   | Coupling module used for Surge test         |

| 4   | YOKOGAWA       | Power Supply                                |

| 5   | ESS-2000       | ESD generator                               |

| 6   | Fluke 189      | Multimeter                                  |

| 7   | TPS27S100x EVM | Standard EVM board with modifications       |

# 4 IEC 61000-4-2 System ESD Immunity

## 4.1 IEC61000-4-2 (ESD) Stress Levels

See Table 2 for levels specified by the IEC 61000-4-2 standard.

### Table 2. ESD Stress Levels

| Level | Contact Discharge   | Air Discharge       |

|-------|---------------------|---------------------|

| Level | Test Voltage (± kV) | Test Voltage (± kV) |

| 1     | 2                   | 2                   |

| 2     | 4                   | 4                   |

| 3     | 6                   | 8                   |

| 4     | 8                   | 15                  |

| X     | Custom              | Custom              |

# 4.2 Test Conditions

The following test conditions exist for IEC61000-4-2 system ESD immunity:

- Supply voltage: 24 V DC, always ON

- Inputs High → Outputs High (ON)

- Outputs not loaded (floating)

# 4.3 Test Signals

According to the IEC 61000-4-2:

- Contact discharge and air discharge

- Polarity: positive and negative

- Discharge unit: 150 pF, 330 Ω

- Applied to: TPS27S100x EVM output port

# 4.4 Test Setup

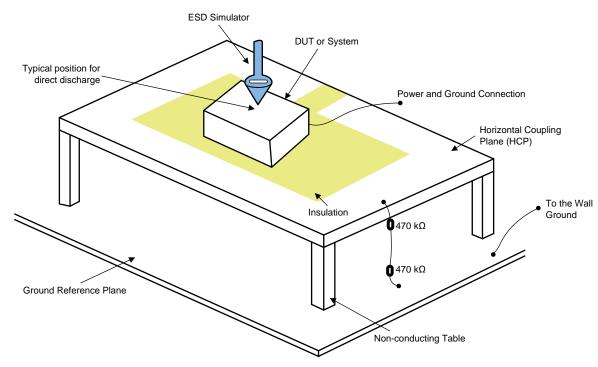

The TI ESD test bench setup complies with the IEC standard and is shown in Figure 3. The TPS27S100x EVM is placed on a horizontal coupling plane (HCP) with insulation in between. Any power connections are made on the non-conductive table and two 470-k $\Omega$  resistors are used to connect the HCP to the ground reference plane (GRP).

The ESD contact and air discharge pulses have been applied to the board output port. The EVM board is always supplied during the test. Input of the board has connected to 5 V output of the board, and output is ON as indicated by the added LED.

Testing is performed by charging the 150 pF discharge capacitor and discharging it through a  $330-\Omega$  resistor into the strike tip. Contact discharge is performed by touching the discharge tip directly to the pin under test then triggering the strike. Conversely, air discharge is performed by triggering the gun then moving the discharge tip towards the pin under test until arcing occurs.

Figure 3. ESD Test Bench Setup

#### 4.5 Classification of The Test

(A) Normal performance within the limits specified by the manufacturer, requester or purchaser.

(B) Temporary loss of function or temporary degradation of performance not requiring an operator.

(C) Temporary loss of function or degradation of performance, the correction of which requires operator intervention.

(D) Loss of function or degradation of performance which is not recoverable, owing to damage of the hardware or software, or loss of data.

#### 4.6 Test Results

Test results are listed in Table 3 and Table 4:

| Table 3. | ESD | Testing | Contact | Discharge | Results |

|----------|-----|---------|---------|-----------|---------|

|----------|-----|---------|---------|-----------|---------|

| ESD Test Signal Amplitude, Test Result At Polarity (±) |      |      |      |      |       |       |       |       |       |       |

|--------------------------------------------------------|------|------|------|------|-------|-------|-------|-------|-------|-------|

| Applied To                                             | 2 kV | 4 kV | 6 kV | 8 kV | 10 kV | 12 kV | 15 kV | 17 kV | 20 kV | 25 kV |

| Output<br>(Floating)                                   | A/A  | A/A  | A/A  | A/A  | A/A   | A/A   | A/A   | A/A   | A/A   | A/A   |

#### Table 4. ESD Testing Air Discharge Results

| ESD Test Signal Amplitude, Test Result At Polarity (±) |      |      |      |      |       |       |       |       |       |       |

|--------------------------------------------------------|------|------|------|------|-------|-------|-------|-------|-------|-------|

| Applied To                                             | 2 kV | 4 kV | 6 kV | 8 kV | 10 kV | 12 kV | 15 kV | 17 kV | 20 kV | 25 kV |

| Output<br>(Floating)                                   | A/A  | A/A  | A/A  | A/A  | A/A   | A/A   | A/A   | A/A   | A/A   | A/A   |

#### 4.7 Conclusion

The tested TPS27S100x EVM passed all of the ESD immunity tests against ESD applied to output in contact and air discharge mode. According to Section 4.1, it passed all specified levels of IEC standard. From Section 4.6, ESD applied to output had no influence on the performance of the board up to 20 kV (contact discharge) and 25 kV (air discharge).

### 5 EMC IEC 61000-4-4 BURST Immunity Test

#### 5.1 IEC61000-4-4 (EFT) Stress Levels

See Table 5 for levels specified by the IEC 61000-4-4 standard.

|       | Peak Amplitude         |                        |  |  |  |  |

|-------|------------------------|------------------------|--|--|--|--|

| Level | Power Supply Port      | I/O, Signal, Data      |  |  |  |  |

|       | V <sub>Peak</sub> (kV) | V <sub>Peak</sub> (kV) |  |  |  |  |

| 1     | 0.5                    | 0.25                   |  |  |  |  |

| 2     | 1                      | 0.5                    |  |  |  |  |

| 3     | 2                      | 1                      |  |  |  |  |

| 4     | 4                      | 2                      |  |  |  |  |

#### Table 5. EFT Stress Levels

### 5.2 Test Conditions

The following test conditions exist for IEC61000-4-4 BURST immunity:

- Supply voltage: 24 V DC, always ON

- Inputs High  $\rightarrow$  Outputs High (ON)

- Outputs floating and loaded with 1 k $\Omega$  resistor

#### 5.3 Test Signals

According to the IEC 61000-4-4:

- Polarity: positive and negative

- Burst duration: 15 ms ± 20 % at 5 kHz

- Burst period: 300 ms ± 20 %

- Duration time: 1 minute

- Applied to: Supply voltage line (V<sub>CC</sub>), output line

#### 5.4 Test Setup

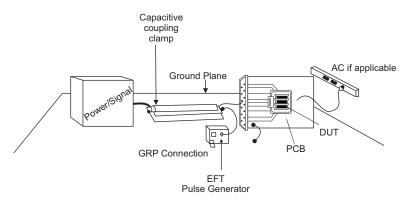

The IEC 61000-4-4 standard defines the EFT immunity tests, set-up procedures, and test levels. The EFT immunity test setup for I/O ports is shown in Figure 4. A burst signal from a burst generator is sent through the test cable (inside a capacitive trench) and is measured through a coupled data cable (inside the same trench) which is connected to the test board. Power port tests are intrinsically coupled with a tester and applied to the power port of TPS27S100x EVM board.

Figure 4. EFT Immunity Test Setup

### 5.5 Classification of the Test

(A) Normal performance within the limits specified by the manufacturer, requester or purchaser.

(B) Temporary loss of function or temporary degradation of performance not requiring an operator.

(C) Temporary loss of function or degradation of performance, the correction of which requires operator intervention.

(D) Loss of function or degradation of performance which is not recoverable, owing to damage of the hardware or software, or loss of data.

#### 5.6 Test Results

Test results are listed in Table 6 and Table 7:

#### Table 6. EFT Testing Results of Supply Voltage Lines

| EFT Test Signal Amplitude, Test Result At Polarity (±) |      |      |      |      |        |  |  |

|--------------------------------------------------------|------|------|------|------|--------|--|--|

| Applied to                                             | 1 kV | 2 kV | 3 kV | 4 kV | 4.4 kV |  |  |

| V <sub>cc</sub>                                        | A/A  | A/A  | A/A  | A/A  | A/A    |  |  |

#### Table 7. EFT Testing Results of Output Port

| EFT Test Signal Amplitude, Test Result At Polarity (±) |      |      |      |      |        |  |

|--------------------------------------------------------|------|------|------|------|--------|--|

| Applied to                                             | 1 kV | 2 kV | 3 kV | 4 kV | 4.4 kV |  |

| V <sub>cc</sub>                                        | A/A  | A/A  | A/A  | A/A  | A/A    |  |

#### 5.7 Conclusion

The tested TPS27S100x EVM system survived all the burst tests without silicon degradation. Bursts applied to  $V_{cc}$  and OUT have no influence on performance of the application in the TPS27S100x EVM up to ±4.4 kV amplitude. According to Section 5.1, the test board passes all the specific levels.

#### 6 EMC IEC 61000-4-5 Surge Immunity Test

#### 6.1 IEC61000-4-5 (Surge) Stress Levels

TI's surge tests are compliant with the IEC 61000-4-5 standard. Depending on what environment a system is designed for, the IEC 61000-4-5 specifies several levels of tests in association with an environment.

Table 8. Surge Stress Levels

| Level | Open-Circuit Test Voltage ±10% kV |

|-------|-----------------------------------|

| 1     | 0.5                               |

| 2     | 1                                 |

| 3     | 2                                 |

| 4     | 4                                 |

| Х     | Custom                            |

- Class 1: Partly protected electrical environment.

- Class 2: Electrical environment where the cables are well-separated, even at short runs.

- Class 3: Electrical environment where cables run in parallel.

- Class 4: Electrical environment where the interconnections are run as outdoor cables along with power cables used for both electronic and electric circuits.

- Class X: Special conditions specified in the product specification.

### 6.2 Test Conditions

- Supply voltage: 24 V DC, always ON

- Inputs High  $\rightarrow$  Outputs High (ON)

- Outputs floating

### 6.3 Test Signals

According to the IEC 61000-4-4:

- 5 positive and 5 negative surges

- Repetition rate: 1 minute

- Coupling: 42 Ω, 0.5 μF

- Applied to: Supply voltage line (V<sub>CC</sub>), output line

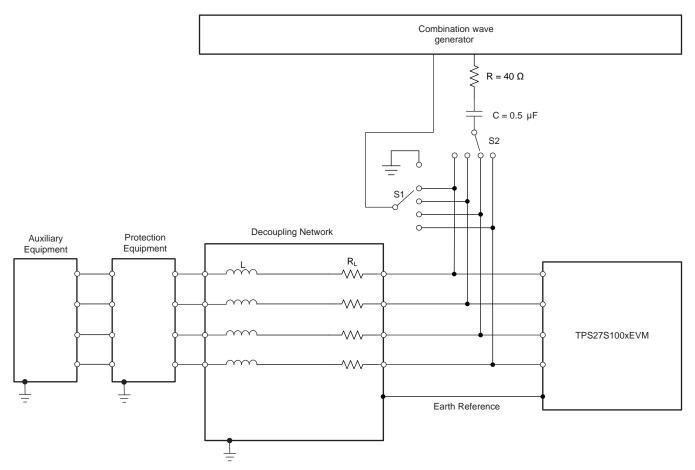

### 6.4 Test Setup

8

For the surge imposed between all other kinds of lines and ground (unshielded unsymmetrical interconnection lines; line-to-line and line-to-ground coupling), a 40  $\Omega$  resistance and a 0.5  $\mu$ F capacitor are used in the coupling network. Together with the 2  $\Omega$  from the combinational waveform generator (CWG), the total source impedance of the surge pulse is 42  $\Omega$ .

Figure 5. Surge Immunity Test Setup

#### 6.5 Classification of the Test

(A) Normal performance within the limits specified by the manufacturer, requester or purchaser.

(B) Temporary loss of function or temporary degradation of performance not requiring an operator.

(C) Temporary loss of function or degradation of performance, the correction of which requires operator intervention.

(D) Loss of function or degradation of performance which is not recoverable, owing to damage of the hardware or software, or loss of data.

### 6.6 Test Results

Test results are listed in Table 9 and Table 10:

| Configuration                     | Applied To      | REQ  | Surge Test Signal Amplitude, Test Result At Polarity (±) |         |         |         |

|-----------------------------------|-----------------|------|----------------------------------------------------------|---------|---------|---------|

|                                   |                 |      | Class 1                                                  | Class 2 | Class 3 | Class 4 |

|                                   |                 |      | 500 V                                                    | 1 kV    | 2 kV    | 4 kV    |

| Standard EVM<br>board             | V <sub>cc</sub> | 42 Ω | A/A                                                      | D/D     | D/D     | -       |

| Input clamped<br>with<br>SM15T30A |                 |      | A/A                                                      | A/A     | A/A     | D/D     |

Table 9. Surge Testing Results of Supply Voltage Lines

| Table 10. Surge | Testing Results | of Output Port |

|-----------------|-----------------|----------------|

|-----------------|-----------------|----------------|

| Configuration      | Applied To | REQ  | Surge Test Signal Amplitude, Test Result At Polarity (±) |         |         |         |

|--------------------|------------|------|----------------------------------------------------------|---------|---------|---------|

|                    |            |      | Class 1                                                  | Class 2 | Class 3 | Class 4 |

|                    |            |      | 500 V                                                    | 1 kV    | 2 kV    | 4 kV    |

| Standard EVM board | OUT        | 42 Ω | A/A                                                      | A/A     | D/D     | -       |

#### 6.7 Conclusion

Without protection of TVS diode, the standard TPS27S100x EVM could survive 500 V stress at V<sub>CC</sub> and 1 kV stress at output port. After using SM15T30A to clamp the input voltage, the test board can survive as high as 2 kV stress on V<sub>CC</sub> while performing normally. Additional external protection circuits need to be added if the system is required to pass class 4 level for both V<sub>CC</sub> and output ports.

#### 7 References

- Texas Instruments, TPS27S100, 40-V, 100 mΩ Single-Channel Smart High-Side Power Switch

- Texas Instruments, TPS27S100A 40-V, 100 mΩ Single-Channel High-Side Switch Evaluation Module

- Texas Instruments, TPS27S100B 40-V, 100 mΩ Single-Channel High-Side Switch Evaluation Module

- Texas Instruments, IEC 61000-4-x Tests for TI's Protection Devices Application Report

- M. Lutz and R. Casanova (2017) User Manual EMC Test System TRANSIENT-2000 and Versions

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your noncompliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated