## IBISモデルを使用したタイミング解析

アプリケーション技術統括部

#### アブストラクト

今日のハイスピード・インターフェースでは、厳密なタイミングおよび正確なシステム設計が必要とされます。与えられたシステムに対して必要なタイミングを満たすために、IBIS (input/output buffer information specification) モデルを使用する必要があります。これらのモデルは、様々なプロセス状態でのデバイス・ドライバを正確に表現したものです。インピーダンス、負荷、配線長、ノード数などのボードの特徴は、デバイス・ドライバの振る舞いに影響を及ぼします。このアプリケーション・レポートでは、与えられたシステムに

対して正確なタイミング解析を行うために、どのようにIBIS モデルを使うかについて述べます。このレポートでは、 TMS320C6000™DSPとSDRAMにフォーカスしています が、セットアップおよびホールド・パラメータを持つすべて のインターフェースに適用可能です。

このアプリケーション・レポートは、『Using IBIS Models for Timing Analysis』 (文献番号 SPRA839A) を翻訳しています。

この資料は日本テキサス・インスツルメンツ(日本TI)が、お客様がTIおよび日本TI製品を理解するための一助としてお役に立てるよう、作成しております。製品に関する情報は随時更新されますので最新版の情報を取得するようお勧めします。

TIおよび日本TIは、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。また、TI及び日本TIは本ドキュメントに記載された情報により発生した問題や障害等につきましては如何なる責任も負いません。

## 目次

| 1                   | 1 はじめに4                                                                      |    |  |  |  |

|---------------------|------------------------------------------------------------------------------|----|--|--|--|

| 2                   | リファレンス・ポイントの確立4                                                              |    |  |  |  |

| 3                   | 3 テスタについての理解                                                                 |    |  |  |  |

|                     | 3.1 テスタ負荷調整                                                                  |    |  |  |  |

|                     | 3.2 実システム・ボード上でのデータシート・タイミングの使用                                              | 8  |  |  |  |

|                     | 3.3 デバイス・ピン間のバリエーション                                                         | 9  |  |  |  |

| 4                   | リファレンス電圧                                                                     | 9  |  |  |  |

|                     | 4.1 テスタと実ボードでの V <sub>ref</sub> 測定についての理解                                    | 10 |  |  |  |

|                     | 4.2 データシート上のリファレンス電圧V <sub>ref</sub> からV <sub>IL</sub> /V <sub>IH</sub> への変換 | 11 |  |  |  |

| 5                   | ノイズ・マージン                                                                     | 12 |  |  |  |

| 6                   | IBIS 計算手法                                                                    | 13 |  |  |  |

|                     | 6.1 SDRAM の入力セットアップ                                                          | 13 |  |  |  |

|                     | 6.2 SDRAM の入力ホールド                                                            | 14 |  |  |  |

|                     | 6.3 DSP の入力セットアップ                                                            | 15 |  |  |  |

|                     | 6.4 DSP の入力ホールド                                                              | 17 |  |  |  |

| 7                   | ACタイミング解析手順のまとめ                                                              | 18 |  |  |  |

|                     | 7.1 情報の収集                                                                    | 18 |  |  |  |

|                     | 7.2 IBIS シミュレーション                                                            | 18 |  |  |  |

|                     | 7.3 計算                                                                       | 18 |  |  |  |

| 8                   | まとめ                                                                          | 18 |  |  |  |

|                     |                                                                              |    |  |  |  |

|                     | 図                                                                            |    |  |  |  |

| 図1 DS               | SPライト(制御信号およびデータ信号)                                                          | 5  |  |  |  |

|                     | SPリード(データ信号のみ)                                                               |    |  |  |  |

|                     | ボード配線/負荷とテスタ配線/負荷                                                            |    |  |  |  |

|                     | ・スタ負荷よりも高負荷時の信号ディレイ(C <sub>0</sub> < A <sub>0</sub> )                        |    |  |  |  |

|                     | ・スタ負荷よりも低負荷時の信号ディレイ(Co > Ao)                                                 |    |  |  |  |

|                     | ・ータシート・タイミング                                                                 |    |  |  |  |

| 図7. SE              | DRAMでのタイミングを得るためにテスタ負荷調整を加算                                                  | 9  |  |  |  |

| 図8. V <sub>re</sub> | <sub>ref</sub> を使った補間                                                        | 10 |  |  |  |

| 図9. ボ               | 。<br>『一ド上のきれいでない波形を用いた単一箇所t <sub>ref</sub> , V <sub>ref</sub> 定義の困難性         | 11 |  |  |  |

| 図10. V              | V <sub>IL</sub> /V <sub>IH</sub> リファレンス電圧への入力要求の変換                           | 12 |  |  |  |

|                     | 典型的な信号に対するノイズ・マージン                                                           |    |  |  |  |

| 図12. S              | SDRAMの入力セットアップ                                                               | 14 |  |  |  |

| 図13. S              | SDRAMの入力ホールド                                                                 | 15 |  |  |  |

| 図14. 🗅              | DSPの入力セットアップ                                                                 | 16 |  |  |  |

| 図15. 🗅              | DSPの入力ホールド                                                                   | 18 |  |  |  |

| 図16. 🗅              | DSP-SDRAMインターフェースのボード特性の例                                                    | 18 |  |  |  |

|                     | ボード上でのDSP出力のIBIS表現                                                           |    |  |  |  |

| 図18. ラ              | テスト負荷を使用したDSP出力のIBIS表現                                                       | 18 |  |  |  |

| 図19. 7              | ボード上でのSDRAM出力のIBIS表現                                                         | 18 |  |  |  |

| 図20. 元              | テスト負荷を使用したSDRAM出力のIBIS表現                                                     | 18 |  |  |  |

|                     |                                                                              |    |  |  |  |

|                     | 表                                                                            |    |  |  |  |

| 表1 50               | <br>DRAM入力セットアップ・タイム・パラメータ                                                   | 13 |  |  |  |

|                     | DRAM入力ホールド・タイム・パラメータ                                                         |    |  |  |  |

|                     |                                                                              |    |  |  |  |

| 表3. DSP入力セットアップ・タイム・パラメータ | . 16 |

|---------------------------|------|

| 表4. DSP入力ホールド・タイム・パラメータ   | .17  |

## 1 はじめに

デジタル・シグナル・プロセッサ(DSP)やメモリは、それぞれのデータシートで与えられる仕様に対してテストされています。これらのテストは、データシートで示される特定の動作条件のもとで行われています。これらの特定の動作条件と異なった条件は、その振る舞いにデバイス・テスト時からの変化を引き起こすことがあります。これらの動作条件には、温度、電圧、周波数、容量性負荷、インピーダンスなどが含まれています。

IBIS (input/output buffer information specification) は、すべてのプロセス状態におけるバッファの振る舞いを、素早く正確にモデリングする手法です。IBISモデルは、回路シミュレーションおよび実験での V/I 特性に基づいて生成されたものです。IBISモデルを使用するために、Hyperlynx やMentor Graphics などから販売されているシミュレーション・パッケージを購入する必要があります。これらのシミュレーション・パッケージによって、システムやボード、部品レベルの特性に起因して生じうるシグナル・インテグリティ問題に対する正確な情報を得ることができます。

例えば、DSPテスタはあるテスト負荷を持っています。ボードが、テスタ負荷に比べて多いもしくは少ない負荷であった場合、タイミングは元来のものからずれることになります。どの方向にタイミングがずれるかは、どのパラメータに着目しているかに依存しますが、これは、システムを悪化もしくは改善させます。

このアプリケーション・レポートで着目しているのは、インピーダンスや負荷についてです。周波数は固定されており、電圧はデータシートで規定されている範囲にあり、温度は室温(規定限度、通常0℃から90℃内)付近と仮定します。

バス幅を満たすために複数のSDRAM(synchronous dynamic random-access memory)チップを使用するシステムでは、各部品についてIBISシミュレーションを行う必要があります。 DSPとSDRAM間はポイント・ツー・ポイント接続ではなくなるので、これを行わなければなりません。トレース長の違いが、複数部品間のタイミングに変化をもたらします。ユーザは、シグナル・インテグリティを確保するためにIBISシミュレーションを行わなければなりません。

このアプリケーション・レポートでは、DSPとSDRAMの両方にとって重要なタイミングに対するリファレンス・ポイントについて述べます。3章では、DSPおよびSDRAMのテストに使用するテスタの概要を、テスタと典型的なボード間で

の様々なタイミングについて説明と共に述べます。リファレンス電圧とノイズ・マージンは、テスタと典型的なボードの両方に現れるタイミングに影響を与えます。なぜこのような影響が生じるかについて、4章と5章で述べます。このアプリケーション・レポートの6章では、IBISシミュレーションにおいて、DSPとSDRAM両方のセットアップおよびホールド・タイムを算出する式も含んでいます。7章では、ACタイミング解析手順についてまとめます。

## 2 リファレンス・ポイントの確立

データシートのタイミングは、テスト・ボードに接続されたデバイスのピンに対して、与えられたテスタ負荷と共に測定されています。実システム・ボードでは、これらのタイミングは、テスタ・ボードに比べて負荷の増加または減少により変化します。実システム・ボードとテスト・ボードでタイミングがどのように変化するかという詳細(3章)に進む前に、この章では、リファレンス・ポイントをどのように確立するかについて述べます。テスト・ボード・モデルとは異なるボードをモデリングするとき、リファレンス・ポイントを確立しなければなりません。簡単のために、リファレンス・ポイントをマスター・デバイスであるDSP内にとります。リファレンス・ポイントは、DSP出力バッファが有効な場合の、時間を表します。

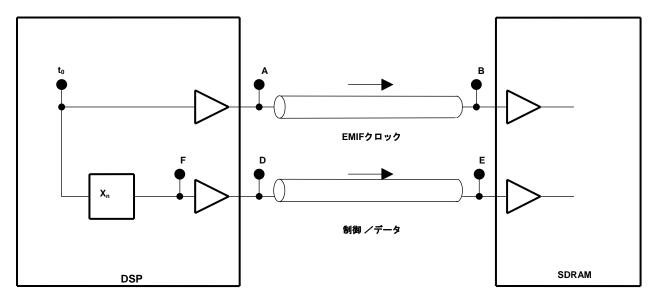

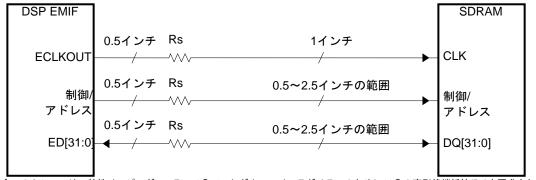

図1はDSPからSDRAMへのライトを抽象的に描いており、 また実システム・ボードを表しています。toで示される点 は、すべてのタイミングのリファレンス・ポイントです。A, B, D および E点は、DSPとSDRAMそれぞれのピンで測定 されます。F点は、toに対して出力バッファをオンにする点 です。Xnは、内部タイミング・ディレイで、DSPの設計で 決められる定数値を表しています。DSPの設計で、 $X_n$ が-3.1nsに設定されていると仮定します。またAの出力バッ ファは、内部ディレイが0.2nsで、Dの出力バッファは、内 部ディレイが0.3nsと仮定します。計算により、A点での時 刻は、 $(t_0 + 0.2)$  ns、または単に $t_0$ に対して0.2nsとなりま す。同様に計算により、D点での時刻は、 $(t_0 + X_n + 0.3)$  ns =  $(t_0 - 3.1 + 0.3)$  ns、または単に $t_0$ に対して-2.8nsとなりま す。DSPの出力セットアップ・タイムは、D点でのデータ遷 移からA点でのクロック遷移までとして計算されます。この 場合、出力セットアップ・タイムは、[0.2 - (-2.8)] ns = 3 nsです。

ホールド・タイムに対しての $X_n$ は、バッファをゲートする内部ロジックが異なるので、異なった値になります。

図1. DSPライト (制御信号およびデータ信号)

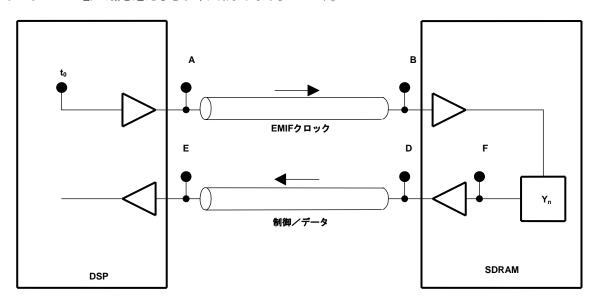

DSPリードの場合、図1のようにDSPはクロック、制御、アドレス信号を出力します。リード・コマンドを受け取ると、SDRAMはデータ信号を出力します。図2は、DSPからのクロックに対してSDRAMがデータをどのように出力するかを抽象的に描いたものです。SDRAMは、デバイスのピンでの入出力タイミングをクロック信号に対して測定します。例えば、SDRAMの出力ホールド・タイムは、B点でクロック信号がリファレンス電圧 $V_{ref}$ を超えるとすぐに始まります。

ホールド・タイムは、D点で信号が $V_{ref}$ を超えるとすぐに終わります。SDRAMの出力ホールド設計で、 $Y_n$ が1.8nsと設定されていると仮定します。またBの入力バッファは、ディレイが0.3nsであり、Dの出力バッファは、ディレイが0.4ns と仮定します。図2の計算により、B点に対するD点の時間は、 $[0.3+Y_n+0.4]$  ns = [0.3+1.8+0.4] = 2.5 nsであり、SDRAM出力ホールド・タイムは、この例で2.5nsとなります。

図2. DSPリード (データ信号のみ)

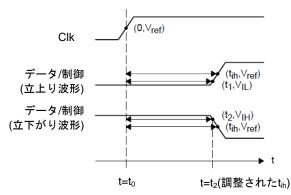

DSPとSDRAM両方で、入出力タイミングはデバイスのピンでのクロック信号に対して測定されます。出力タイムは、クロックが $V_{ref}$ を超えたときに対して、データ/制御信号が $V_{ref}$ を超えたときとして測定されます。入力タイムは、クロックが $V_{ref}$ を超えたときに対して、データ/制御信号が有効

(セットアップ・タイム) または無効 (ホールド・タイム) になったときとして測定されます。

#### 3 テスタについての理解

#### 3.1 テスタ負荷調整

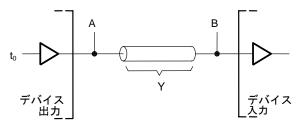

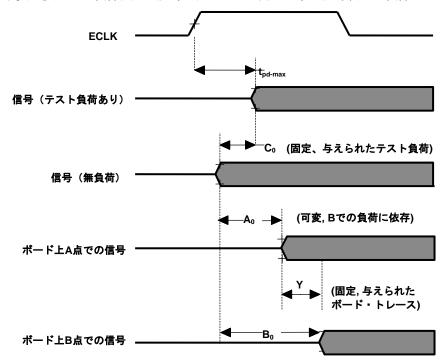

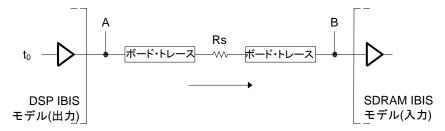

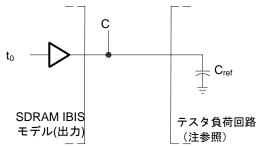

前章で触れたように、実システム・ボードのタイミング解析を行う際に、テスタ負荷を考慮しなければなりません。テスタ負荷は、負荷変化を正確に反映させるために、ボード配線

分を差し引いたものでなければなりません。図3は、テスタ 負荷によりボード配線がどのように変化するかを単純に描い たものです。

典型的なポイント・ツー・ポイント配線

典型的なテスタ配線

注:テスタ負荷回路はデバイスにより異なります。正確なテスタ負荷回路については、データシートを参照してください。

## 図3. ボード配線/負荷とテスタ配線/負荷

図3において上側の図は、典型的なポイント・ツー・ポイン トのボード配線を表しています。DSPからの出力(A点) は、伝送路とB点の負荷からなる負荷を駆動します。ライ ン・ディレイYは、ボード配線と特性の関数になります。下 側の図は、典型的なテスタ回路を示しています。実際のテス タ回路については、デバイスのデータシートを参照してくだ さい。典型的なテスタでは、ライン・ディレイが差し引か れ、テスタの容量性負荷におけるデバイスのピン(C点)で のデータシート出力タイミングが与えられます。データシー トのタイミングは、信号がC点でリファレンス電圧Vrefを超 えたときとして与えられます。C点で測定されたデータシー トのタイミングを使い、自分のボードのA点やB点のタイミ ングに適用するように仮定することは出来ません。これは、 ほとんどの場合で、ボードがテスタ回路とは異なった容量性 負荷を持っているためです。テスタ負荷より小さな負荷を 持ったシステム・ボードでは、C点で測定されたデータシー トのタイミングに比べて、B点で早いタイミングになりま す。テスタ負荷より大きな負荷を持ったシステム・ボードで は、C点で測定されたデータシートのタイミングに比べて、 B点で遅いタイミングになります。

適切なボード配線特性(Y)、DSPとSDRAMのIBISモデルを 与えることで、B点およびC点での正確なタイミングを測定 するのに、IBISシミュレーションを使うことができます。 IBISシミュレータには、絶対タイミングまたはリファレン ス・タイミングを得る機能があります。絶対タイミングは、 バッファがオンになったときtoからとして測定されます。リ ファレンス・タイミングは、テスト中の出力ピンがリファレ ンス電圧に到達したときからとして測定されます。例えば、 B点での絶対タイミングは、toからとして測定され、B点の リファレンス・タイミングは、Aの出力がリファレンス電圧 に到達したときからとして測定されます。ACタイミング解 析において、システム・ボード回路とテスト回路両方の共通 リファレンス・ポイントを確立するためにIBISシミュレー ションでは絶対タイミングを使用します。絶対タイミング は、添字0で表されます。適切なIBISモデルとボード配線特 性と共にIBISシミュレーションを行うことで、toからBまで の絶対ディレイBoを得ることができます。同様に、toからC までの絶対ディレイCoを得るためにIBISシミュレーション を行うことができます。次式は、データシートのタイミング  $(C_0)$ と実際のSDRAMのピンで観測されるタイミング $(B_0)$ と の差を与えます。

データシートとSDRAMでのタイミングの差

$$=B_0-C_0$$

図3に示すように、ボード・ディレイYはこの式で表されます。

#### $Y = B_0 - A_0$

このことは、ボード負荷がテスタ負荷と同じな場合( $C_0 = A_0$ )、データシートとSDRAMでのタイミングの差 =  $B_0 - C_0$

$=B_0-A_0$ になります。言い換えれば、テスタによるディレイとボード負荷によるディレイは同じです。ボード負荷がテスタ負荷より小さい場合( $C_0>A_0$ )、 $B_0$ は小さくなり、SDRAMでのタイミングとデータシートの差が小さくなります。逆もまた同様です。大きなボード負荷( $C_0<A_0$ )は、 $B_0$ を

大きくし、SDRAMでのタイミングとデータシートの差も大きくなります。図4と図5は、クロック信号の立ち上がりに対して負荷が、与えられたラインにどのように影響するかを示します。パラメータ $C_0$ とYは、図4と図5では固定値です。図4と図5では、B点で異なった負荷であると仮定しています。

図4. テスタ負荷よりも高負荷時の信号ディレイ( $C_0 < A_0$ )

図5. テスタ負荷よりも低負荷時の信号ディレイ( $C_0 > A_0$ )

ここで、 $B_0$ と $C_0$ は、IBISシミュレーションでの絶対タイミングから算出されたものです。差( $B_0-C_0$ )は、与えられたボード・トレースおよび入出力バッファでは定数です。 ( $B_0-C_0$ )は、下記のとおり、テスタ負荷調整として参照されます。

#### テスタ負荷調整 = $B_{\theta}$ – $C_{\theta}$

これは、あるピンに対して、C点での信号遷移時間 $t_1$ を知っているとき、B点での信号遷移時間 $t_2$ は、あるピンとトレース長に対して定数値のテスタ負荷調整を単に加算するだけで得ることができることを表します。

$$\mathbf{t}_2 = \mathbf{t}_1 + (\mathbf{B}_{\theta} - \mathbf{C}_{\theta})$$

次節では、ACタイミング解析においてテスタ負荷調整の使い方を説明します。

# 3.2 *実システム・ボード上でのデータシート・タイミングの使用*

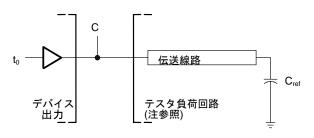

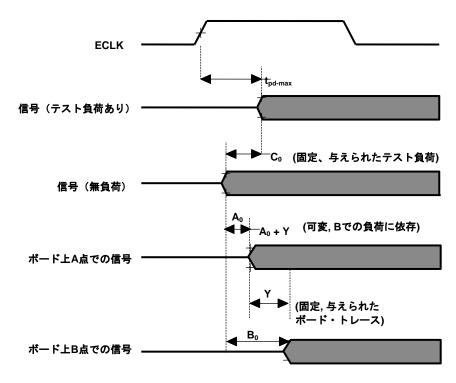

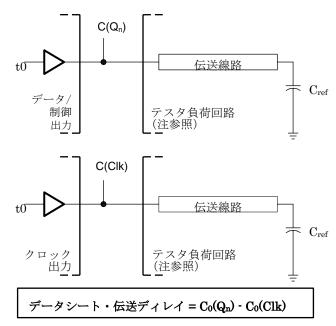

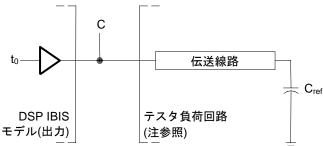

データシートでは、内部リファレンスtoと信号スイッチの絶対時間Co(図3参照)は、与えられません。そのかわりデータシートでは、テスト負荷でのデバイスのピンでのクロック信号に対するデータ/制御信号タイミングが与えられます。図6は、伝送ディレイを例として、データシートのタイミングがどのように得られるかを示したものです。

注:テスタ負荷回路はデバイスにより異なります。正確なテスタ負荷回路については、データシートを参照してください。

#### 図6. データシート・タイミング

このアプリケーション・レポートの以降で、" $t_{pd}$ "は、クロック信号からデータ/制御信号への伝送ディレイを表すために使用されます。 $t_{pd}$ は、データ/制御がスイッチしたときからクロック遷移までとして測定されます。DSPからSDRAMへのライト例で、ACタイミングについて理解するために、データシート・タイミング(テスタ負荷におけるDSPピンでの $t_{pd}$ )からSDRAMの入力ピンでの $t_{pd}$ に変換する必要があります。これは、SDRAM入力タイミング制約を実システム・ボードで満たすことができるかどうかを決定するためです。3.1節では、B点とC点(図3)での信号スイッチのタイミング上の差を表すテスタ負荷調整( $B_0$  —  $C_0$ )を与えました。データシートのタイミングからSDRAMピンでの $t_{pd}$ に変換するために、テスタ負荷調整を使う必要があります。

図6に示すように、データシートでの $t_{pd}$ は、次のように計算されます。

$$t_{pd}(\vec{r} - \beta \triangleright - 1) = C_0(Q_n) - C_0(Clk)$$

実システム・ボードでは、SDRAM入力ピンでの $t_{pd}$ は、次のようになります。

#### $t_{pd}(at SDRAM) = B_{\theta}(Q_n) - B_{\theta}(Clk)$

上式で未知なのは、 $t_{pd}$ (at SDRAM)だけです。パラメータ  $t_{pd}$ (データシート)は、データシートで与えられ、 $C_0(Q_n)$ ,  $C_0(Clk)$ ,  $B_0(Q_n)$ ,  $B_0(Clk)$ は、適切なボード・トレースとIBIS モデルを使ったIBISシミュレーションから得られます。Cでの信号スイッチ時刻 $C_0$ が与えられたとき、SDRAMピンでの信号スイッチ時刻は、3.1節の4式で示したテスタ負荷調整を加えることで算出されます。したがって、次のように得ることができます。

$B_{d}(Q_{n}) = C_{d}(Q_{n}) + [B_{d}(Q_{n}) - C_{d}(Q_{n})];$  テスタ負荷調整を加算  $B_{d}(Clk) = C_{d}(Clk) + [B_{d}(Clk) - C_{d}(Clk)];$  テスタ負荷調整を加算 これは、 $t_{pd}$  (at SDRAM)が次のように計算できることを意味します。

$t_{pd}(at SDRAM)$

$=B_0(Q_n)-B_0(Clk)$  ;  $\pm \zeta 6$

$= \{C_0(Q_n) + [B_0(Q_n) - C_0(Q_n)]\} - \{C_0(Clk) + [B_0(Clk) - C_0(Q_n)]\} - \{C_0(Clk) + [C_0(Clk) - C_0(Q_n)]\} - [C_0(Clk) + [C_0(Clk) - C_0(Q_n)]] - [C_0(Clk) + [C_0(Clk) - C_0(Q_n)]] - [C_0(Clk) + [C_0(Clk) - C_0(Q_n)]] - [C_0(Clk) + [C_0(Clk) - C_0(Clk)]] - [C_0(Cl$

*Co(Clk)]*} ; 式7,8で置換

$= C_0(Q_n) - C_0(Clk) + [B_0(Q_n) - C_0(Q_n)] \cdot [B_0(Clk) -$

Co(Clk)] ;変形

$= t_{pd}(datasheet) + [B_0(Q_n) - C_0(Q_n)] \cdot [B_0(Clk) - C_0(Clk)]$  ;式5で置換

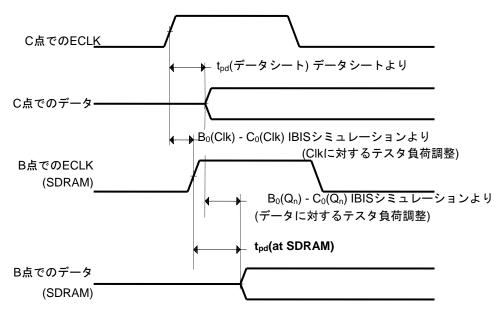

図7は、どのようにテスタ負荷調整をデータシートのタイミングに加算し、SDRAMピンでのタイミングを得るかを表すために、この計算を図式的に示したものです。

図7. SDRAMでのタイミングを得るためにテスタ負荷調整を加算

#### 3.3 デバイス・ピン間のバリエーション

すべての与えられたピン $Q_n$ で、 $C_0$ は固定値です。 $C_0(Q_n)$ は、部品パッケージ内でのバリエーションにより異なったピン間では、変化することがあります。このピン間のバリエーションは、一般的に小さなものですが、タイミングを計算するときに考慮に入れなければなりません。単純に、すべての $Q_n$ に対する $C_0$ の平均値を使用し、この簡単化を補償するためにマージンを加えることができます。より正確なタイミングを望む場合は、 $C_0(Q_n)$ をそれぞれの信号トレースに対して計算する必要があります。

それぞれのピンに対して、 $C_0$ は、データシートで与えられるテスタ負荷をそのピンに置くことで算出されます。あるピンの $C_0$ 値は、この簡単なセットアップを使ったIBISシミュレーションを行うことで求めることができます。それぞれのピンに対して、IBISファイルは3つの条件(弱、強、典型)での入出力特性を与えます。最低でも2つの独立なIBISシミュレーション(一方は弱条件を使用し、他方は強条件を使用)を実行しなければなりません。独立な弱および強での実行は、ワーストケースのシナリオを与えることになります。toから点へのディレイ $C_0$ (図3)は、データシートで与えられるリファレンス電圧に対して測定されます。リファレンス電圧については、次章で述べます。

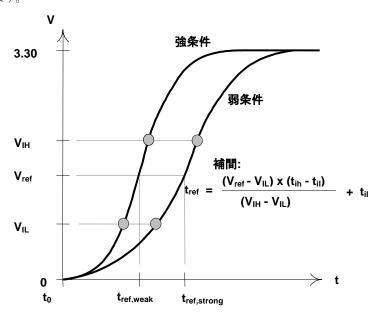

## 4 リファレンス電圧

議論が必要な点に、リファレンス電圧Vrefがあります。制御 信号とデータ信号は、クロック信号の立ち上がりエッジで ラッチされます。SDRAMまたはDSPが、VILとVIIIの間の正 確にどこでラッチするのかという疑問について、考察しなけ ればなりません。これには、正確な答えはありません。プロ セスのバリエーションが、同様にデバイス間での不一致を引 き起こします。デバイス特性を固定するために、テスタでど のように信号を測定するかを表すのに、データシートでリ ファレンス電圧が与えられます。リファレンス電圧は、セッ トアップ・タイムやホールド・タイムといったデバイス特性 を計算する開始点として使用されます。例えば、データシー トで $t_{pd}(Clk - Data) = 3 \text{ ns}$ であったとします。これは、C点 (図3) でのクロックの $V_{ref}$ のクロスと、C点でのデータの $V_{ref}$ のクロスのディレイが3nsであることを意味します。いくつ かのIBISパッケージでは、バッファが有効になってから  $(t_0)$ 、デバイスが有効ロジック・レベル $(V_{IL} \geq V_{IH})$ に到達した までの時刻のみを計算します。データシートのVrefとこれら の時間をあわせて使用するには、Vrefになった時刻を補間し ます。図8は、どのようにしてこれを行うかを示します。 図8は、特定のデバイス・ピンのIBISシミュレーションの例 を示しています。はじめのIBISシミュレーションが左側の波

形 (バッファは強条件) を生成し、2番目のIBISシミュレー

ションが右側の波形(バッファは弱条件)を生成したとします。 $V_{ref}$ ,  $V_{IL}$ ,  $V_{IH}$ は、データシートからのパラメータです。タイミング・パラメータ $t_{ref}$ ,  $t_{il}$ ,  $t_{ih}$ は、 $V_{ref}$ ,  $V_{IL}$ ,  $V_{IH}$ とれぞれの点でのIBISシミュレーションから得られたものです。図8に示すように、波形はきれいで $(t_{il}$ ,  $V_{IL}$ )から $(t_{ref}$ ,  $V_{ref}$ )かの傾きが $(t_{ref}$ ,  $V_{ref}$ )から $(t_{ih}$ ,  $V_{IH}$ )への傾きと同じであると仮定できるので、補間式を適用します。この仮定は、それぞれの強波形と弱波形に対して適用します。

データシートで述べているように、ACタイミングは $V_{ref}$ から 計算されています。したがって、与えられたボードでのDSP またはSDRAMによって生成されるタイミングを推定すると きは、 $V_{ref}$ を使用しなければなりません。 $V_{ref}$ を補間すると き、強バッファと弱バッファの使用を混在させてはいけません。

図8. Vrefを使った補間

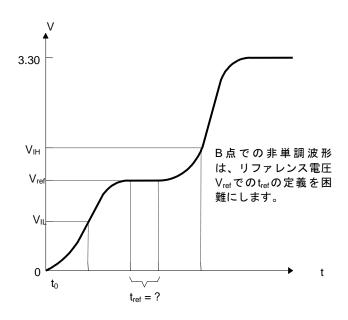

# 4.1 テスタと実ボードでの V<sub>ref</sub> 測定についての理解

データシートでは、図3のC点でリファレンス電圧 $V_{ref}$ を定義しており、すべてのACタイミングはこれから算出されます。対応するタイミング・リファレンス $t_{ref}$ は、IBISシミュレーションを使って算出することができます。これは、テスタ上で信号はポイント・ツー・ポイント接続(テスト中のデバイスはテスタに接続されています)であり、その結果、図

8に示すような $V_{IL}$ と $V_{IH}$ の遷移がスムーズで単調な、きれいな波形となるために可能となります。したがって、 $V_{ref}$ に対応する一つの $t_{ref}$ を、容易に確認することができます。しかし、実システム・ボードでは、きれいなポイント・ツー・ポイント接続ではないかもしれません。その結果、B点(図3)における $V_{ref}$ に対応する $t_{ref}$ を定義するのが困難となります。図9は、 $V_{IL}$  と $V_{IH}$  の間が単調でない場合の、この問題を示しています。

図9. ボード上のきれいでない波形を用いた単一箇所tref, Vref定義の困難性

正確な動作のために、実システム・ボード上でB点 (SDRAM入力) のクロック信号が $V_{IL}$ と $V_{IH}$ の間で、図8の信号のような単調なものとなるように、IBISシミュレーションを行わなければなりません。クロック信号は単調であることが必要とされるので、リファレンス電圧 $V_{ref}$ は図8のように容易に識別することができます。しかし、データ信号および制御信号は、単調であることを要求されません。データ/制御信号に対する唯一の要求は、エンド・デバイスでの入力セットアップ・タイムおよびホールド・タイムを満たすことです。したがって、図9はデータ/制御信号に適用されるかもしれません。実システム・ボードのB点において、 $V_{ref}$ 以外の電圧をリファレンス電圧として使用する必要があります。これについては、次節で述べます。

# 4.2 データシート上のリファレンス電圧 $V_{ref}$ から $V_{ll}/V_{ll}$ への変換

4.1節で示したように、B点(エンド・デバイスの入力)でのデータ/制御信号は、きれいではないかもしれません。リファレンス電圧として、 $V_{ref}$ の使用から $V_{II}/V_{IH}$ の使用へデータシートの入力要求を調整する必要があります。データ/制御信号の立ち上がりにおいて、立ち上がり信号が $V_{IL}$ を超えるともはやローとは見なされないので、新たなリファレンス電圧として $V_{IL}$ を使用します。同様にデータ/制御信号の立ち下がりにおいて、立ち下がり信号が $V_{IH}$ を下まわるとハイとは見なされないので、新たなリファレンス電圧として $V_{IH}$ を使用します。図10では、異なったリファレンス電圧に対して入力ホールド要求をどのように変換するかを示していま

す。入力ホールド要求(t<sub>ih</sub>)は、デバイスの入力ピンで測定を行い、 $V_{ref}$  でのクロック・スイッチングから $V_{ref}$  でのデータ・スイッチングまでとして測定されます。これは図10で、(t<sub>ih</sub>,  $V_{ref}$ )として示されています。立ち上がりデータ信号において、(t<sub>1</sub>,  $V_{II}$ )点で示される、新たなリファレンス電圧t<sub>1</sub>へt<sub>ih</sub>を変換する必要があります。立ち下がりデータ信号において、(t<sub>2</sub>,  $V_{IH}$ )点で示される、新たなリファレンス電圧t<sub>2</sub>へt<sub>ih</sub>を変換する必要があります。テスト時、テスタはデバイスに対して、図10で傾きmとして示される特定の入力スルー・レート(単位は、ボルト毎ナノセカンド( $V_{IR}$ ))で入力信号を供給します。図中の代数方程式は、テスタ入力スルー・レートm,  $V_{ref}$ ,  $V_{II}$ ,  $V_{IH}$ およびデータシート値t<sub>ih</sub> から、t<sub>1</sub>, t<sub>2</sub>の算出方法を示しています。

データ信号は立ち下がりと立ち上がりの両方あるので、 $t_1$ 、 $t_2$  のワースト側を新たな入力ホールド要求として定義する必要があります。より大きな入力ホールド要求は、より厳しいものとなるので、新たなリファレンス電圧 $V_{IL}$ 、 $V_{IH}$ それぞれについて、 $t_1$ 、 $t_2$ の大きい側を新たな入力ホールド要求として採用します。典型的な場合として、 $V_{ref}$  = 1.5 V、 $V_{IL}$  = 0.8 V、 $V_{IH}$  = 2.0 Vの場合、 $t_1$ に比べて $t_2$ が大きい(より、厳しい)ので、これが新たな入力ホールド要求になります。4.1節で触れたように、クロック信号は単調です。したがって、 $V_{ref}$  リファレンスを使用することができます。データ/制御信号だけは、 $V_{II}/V_{IH}$ 電圧リファレンスを使用するために変換する必要があります。

調整されたtih(これはt1またはt2)の計算

$t_{ih}$  = データシートからの入力ホールド要求  $t_1$  =  $t_{ih}$  - (1/m) \*  $(V_{ref} - V_{IL})$  ここでmは正  $t_2$  =  $t_{ih}$  - (1/m) \*  $(V_{ref} - V_{IH})$  ここでmは負

新たな入力ホールド要求はt<sub>1</sub>またはt<sub>2</sub>の大きいほう

注: すべての傾き(入力スルー・レートまたは伝送時間)は、データシートで指定されています (m V/ns)。 すべての信号は、テスト時にデバイスの入力で測定されます。 図中のすべての点は、(タイム、電圧)としてラベルづけされます。

#### 図10. VII/VIIIリファレンス電圧への入力要求の変換

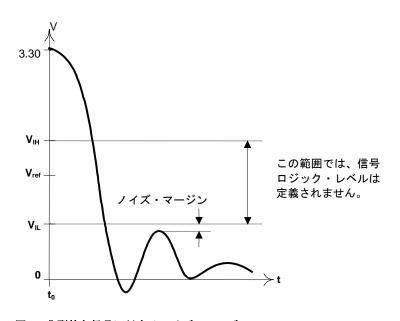

## 5 ノイズ・マージン

IBISシミュレーションは、システム中のノイズ・レベルをモデル化しません。クロストークのような特定のノイズ・レベルは、考慮されていますが、グランド・バウンス、電磁干渉(EMI)や一般的な電源ノイズはモデル化されていません。IBISモデルの解析で、これらのノイズ源を考慮しなければな

りません。図11は、典型的な緩やかな立ち上がりを持った立ち下がりエッジ信号に対する、ノイズ・マージンを示したものです。適切な動作のために、ボード設計者は信号が有効ハイ・レベルまたはロー・レベルに収まることを保証しなければなりません。

図11. 典型的な信号に対するノイズ・マージン

散発ノイズは、ボードの動作環境に依存して、容易に  $100 \text{mV} \cdot 150 \text{mV}$  レベルに達します。グランド・プレーンの 150 mV のシフトは、信号の有効ロジック・レベルから無効 ロジック・レベルへの遷移を引き起こし、不定動作を引き起こす可能性があります。ノイズ・マージンを考慮する典型的 な手法は、IBISシミュレーションにおいて $V_{II.}$ ,  $V_{IH}$  を調整す

る方法です。標準的な $V_{IL}$ ,  $V_{IH}$ の電圧レベルは、それぞれ 0.8V、2.0Vです。ノイズ・マージンを調整するとき、 $V_{IL}$ として0.6V、 $V_{IH}$ として2.5Vを使用するのは、よくある数値で す。ボードは、ロー信号が $V_{IL}$  = 0.6Vより十分下まわり、ハイ信号が $V_{IH}$ より十分上回るように設計されなければなりません。これは、より厳しいボード設計要求であり、ロー信号

に対するノイズ・マージンが0.2V、ハイ信号に対するノイズ・マージンが0.5Vになります。

これを行うには、デバイスIBISモデルを編集し、 $V_{\rm inl}$ を0.8V から0.6Vに、 $V_{\rm inh}$ を2.0Vから2.5Vに変更します。その後、IBISシミュレーションを実行し、 $V_{\rm IL}$  = 0.6V,  $V_{\rm IH}$  = 2.5VでB点(図3)での絶対タイミングを取得します。

## 6 IBIS 計算手法

DSPとSDRAM共に、厳守しなければならない最低のタイミング要求があります。スイッチング特性は、最低動作条件および要求を満たす限り、保証されます。システムが正しく動作するために、ある部品のスイッチング特性は、他の部品の要求を満たさなければなりません。

ここで、タイミング要求はもちろんのことスイッチング特性 は、DSPおよびSDRAMのピンにおいて測定されている点を 強調しておくことは、重要です。

クロック線は、DSPの出力です。この線に関連する特別なセットアップ・タイム、ホールド・タイム要求はありません。DSPで与えられる遷移スペックが、SDRAMで必要とされる要求を満たすことは重要です。クロック・トレース配線が、システム設計において重要な役割をはたします。

ADDRESS, RAS, CAS, CS, WE などの制御信号は、DSPの出力です。これらの信号のスイッチング特性は、SDRAMのピンでSDRAMの入力要求に一致しなければなりません。

データ信号は、DSPの入力であり出力です。DSPデータ出力バッファは、SDRAM入力要求に一致しなければなりません。同じ信号で、SDRAMデータ出力バッファは、DSPデータ入力要求に一致しなければなりません。ほとんどのDSPで、出力データ信号は、制御信号と同じスイッチング特性を持っています。SDRAMへのハイスピード・インターフェー

制御/データ線に 対するテスタ負荷調整 スを設計するとき、4つの重要なパラメータが満たされなければなりません。この4つのパラメータとは、以下のものです。

- SDRAMのt<sub>isu</sub> (入力セットアップ・タイム)

- SDRAMのt<sub>ih</sub> (入力ホールド・タイム)

- DSPのt<sub>isu</sub> (入力セットアップ・タイム)

- DSPのt<sub>ih</sub> (入力ホールド・タイム)

これらのパラメータの計算については、6.1節から6.4節にかけて述べます。複数のデータ・ピン、制御ピンについて、 $C_0(Q_n)$ は、計算を容易にするためには平均して定数値とすることができ、または望ましくは、ワーストケースの $C_0(Q_n)$ を使うことができます。許容可能なマージンを計算するとき、これらを考慮しなければなりません。 $C_0$ ,  $B_0$ は、IBISシミュレーション・パッケージを使用して計算しなければなりません。 $B_0$ は、ボード特性やシステム環境に依存して変化することがあります。したがって、IBISシミュレーション・パッケージを使用してこれらの数値を計算するときは、ノイズおよび他のシステム・マージンの正確な見積もりが必要とされます。

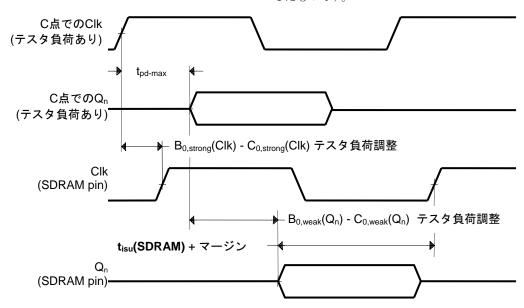

#### 6.1 SDRAM の入力セットアップ

入力セットアップ・タイムは、SDRAMへのリードおよびライト時の制御信号、同様にSDRAMへのDSPライト時のデータ信号に対して要求されます。SDRAMへのセットアップ・タイムが満たされていることを確認するために、次式で定義されるマージンがゼロより大きくなければなりません。図3のB点およびC点を参照してください。

クロック線に 対するテスタ負荷調整

マージン =  $ECLK_{Per}$  -  $(B_{0, weak}(Q_n) - C_{0, weak}(Q_n)]_{max} + t_{Pd-Max} - (B_{0, strong}(Clk) - C_{0, strong}(Clk)) - t_{isu}(SDRAM)$  上記の変数および定数については、表1に記載しています。

表1. SDRAM入力セットアップ・タイム・パラメータ

## SDRAM入力セットアップでの定数

ECLK<sub>Per</sub> : EMIFクロック周期

$t_{ ext{isu(SDRAM)}}$  : SDRAMでの入力セットアップ要求。このパラメータは、SDRAMデータシートから得たもので、 $V_{ ext{ref}}$ 電圧リファレンスから $V_{ ext{l.}}V_{ ext{l.}}$ 用電

圧リファレンスに調整されたものです(4.2節参照)。

tpd-max : DSPから与えられる最大伝送ディレイ。このパラメータは、DSPデータシートから得られたものです。

C<sub>O,weak</sub>(Q<sub>n</sub>) : 弱プロセス・バッファでのDSPデータ/制御バッファ伝送ディレイで、DSPテスト負荷のみを使用したときに、t<sub>o</sub>から信号がリファ

レンス電圧をクロスしたときまでとして測定されます。DSP IBISモデルとIBISシミュレーション・パッケージを使用して計算され

ます。

C<sub>0,strong</sub>(Clk) : 強プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、DSPテスト負荷のみを使用したときに、t<sub>0</sub>から信号がリファレンス電圧をクロストなときまでとして測定されます。DSP IRISエデルとIRISシミュレーション・パッケージを使用して計算されま

ンス電圧をクロスしたときまでとして測定されます。DSP IBISモデルとIBISシミュレーション・パッケージを使用して計算されま

9 。

#### SDRAM入力セットアップでの変数

Bo,weak(Qn) : 弱プロセス・バッファでのDSPデータ/制御バッファ伝送ディレイで、ボード上のSDRAMピン(B点)で、toから**信号が有効論理レベルに到達したときまで**として測定されます。DSPとSDRAM IBISモデルとIBISシミュレーション・パッケージを使用して計算され

ます。

B<sub>0,strong</sub>(Clk)

強プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、ボード上のSDRAMピン(B点)で、t<sub>0</sub>から**信号がリファレンス 電圧V<sub>ref</sub>をクロスしたときまで**として測定されます。DSPとSDRAM IBISモデルとIBISシミュレーション・パッケージを使用して計 算されます。

SDRAMの入力セットアップは、最低限の要求です。した がって、式の右辺の全パラメータの総和は、ゼロより大きく なければなりません。調整可能な唯一の変数は、クロックと 信号バッファ伝送ディレイ $B_0(Q_n)$ ,  $B_0(Clk)$ です。

これらは、長さやインピーダンスなどのトレース特性を変化 させることで、調整されます。つまり、図3のライン・ディ レイYを変化させることで、調整することができます。

SDRAMのセットアップ・タイムを計算するとき、あり得る 最悪のセットアップ・タイムは、クロック線が速く制御/ データ線が遅い場合です。これをシミュレーションするため に、強クロック線と弱制御/データ線をあわせて使用しま す。これは、クロック信号が単調で、反射が最小であること を仮定しています。

図12は、SDRAM入力セットアップ・タイミングを図的に表 したものです。

図12. SDRAMの入力セットアップ

複数の制御およびデータ信号があるので、ボードとテスト負 荷間の最大の差分を見つけるために、(上で述べた手法を用 いて) それぞれのトレースを計算する必要があります。この 最大差分は、SDRAMへのワーストケースのセットアップ・ タイムをもたらします。たとえ、すべてのデータ線がデバイ ス内で同種のバッファを使用しているとしても、パッケージ 特性がピン上での出力信号に変化をもたらします。ボード伝 送ディレイとテスト負荷伝送ディレイの差分を計算すると き、同一のピンを使用することは重要です。この計算を行う

のに別々のピンを使用すると、誤ったシミュレーション結果 になります。

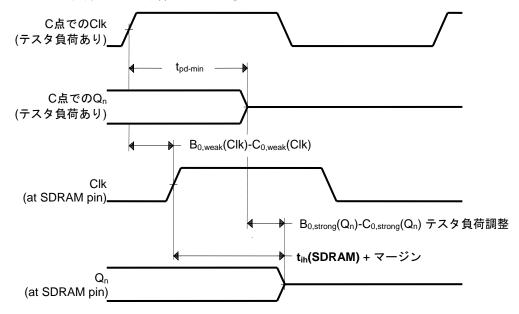

#### 6.2 SDRAM の入力ホールド

入力ホールド・タイムも、SDRAMへのリードおよびライト 時の制御信号、同様にSDRAMへのDSPライト時のデータ信 号に対して要求されます。SDRAMへのホールド・タイムが 満たされていることを確認するために、次式で定義される マージンがゼロより大きくなければなりません。

表2. SDRAM入力ホールド・タイム・パラメータ

SDRAM入力ホールドでの定数

SDRAMでの入力ホールド要求。このパラメータは、SDRAMデータシートから得たもので、 $V_{tel}$ 電圧リファレンスから $V_{tul}/V_{li}$ 電圧 tih(SDRAM)

リファレンスに調整されたものです(4.2節参照)。

DSPから与えられる最小伝送ディレイ。このパラメータは、DSPデータシートから得られたものです。 t<sub>pd-min</sub>

$C_{0,strong}(Q_n)$ 強プロセス・バッファでのDSPデータ/制御バッファ伝送ディレイで、DSPテスト負荷のみを使用したとき、toから信号がリファ レンス電圧をクロスしたときまでとして測定されます。DSP IBISモデルとIBISシミュレーション・パッケージを使用して計算さ

れます。

$C_{0,weak}(Clk)$ 弱プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、DSPテスト負荷のみを使用したとき、toから信号がリファレ

ンス電圧をクロスしたときまでとして測定されます。DSP IBISモデルとIBISシミュレーション・パッケージを使用して計算され

ます。

SDRAM入力ホールドでの変数

: 強プロセス・バッファでのDSPデータ/制御バッファ伝送ディレイで、ボード上のSDRAMピン(B点)で、もから**信号が無効論理**  $B_{0,strong}(Q_n) \\$ レベルに到達したときまでとして測定されます。DSPとSDRAM IBISモデルとIBISシミュレーション・パッケージを使用して計算

されます。

弱プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、ボード上のSDRAMピン(B点)で、t<sub>o</sub>から**信号がリファレン** B<sub>0,weak</sub>(Clk)

ス電圧V<sub>ref</sub>をクロスしたときまでとして測定されます。DSPとSDRAM IBISモデルとIBISシミュレーション・パッケージを使用し

て計算されます。

SDRAMの入力ホールドは、最低限の要求です。したがっ て、式の右辺の全パラメータの総和は、ゼロより大きくなけ ればなりません。調整可能な唯一の変数は、クロックと信号 バッファ伝送ディレイです。これらは、図3のトレース特性 (ディレイY) を変化させることで、調整されます。

クロック信号が遅く、制御/データ信号が速い場合に、ワー ストケースのSDRAMの入力ホールドを得ることができま す。クロック信号が単調で、反射が最小であることを仮定 し、このワーストケースをシミュレーションするために、弱 クロック・バッファと強制御/データ・バッファを使用しな ければなりません。

図13は、SDRAM入力セットアップ・タイミングを図的に表 したものです。

#### 図13. SDRAMの入力ホールド

複数の制御およびデータ信号があるので、ボードとテスト負 荷間の最小の差分を見つけるために、(上で述べた手法を用 いて) それぞれのトレースを計算する必要があります。この 最小差分は、SDRAMへのワーストケースのホールド・タイ ムをもたらします。

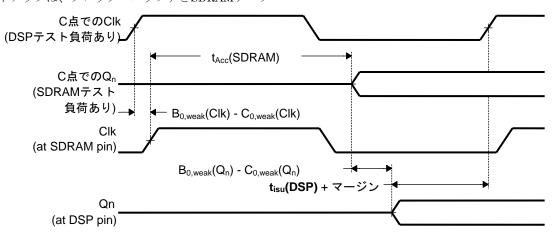

#### 6.3 DSP の入力セットアップ

DSPリードは、DSPからおよびDSPへのボード配線ディレ イと同様にSDRAMの伝送ディレイを考慮しなければならな いという意味で、ライトとは異なります。DSP入力セット アップは、SDRAMがDSPへデータを出力するときのみ要求 されます。DSPへのセットアップ・タイムを確認するため に、次式で定義されるマージンがゼロより大きくなければな りません。

表3. DSP入力セットアップ・タイム・パラメータ

| DSP入力セットアップでの定数     |   |                                                                                                                                                                    |  |  |

|---------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ECLK <sub>Per</sub> | : | EMIFクロック周期                                                                                                                                                         |  |  |

| $t_{isu}(DSP)$      | : | DSPでの入力セットアップ要求。このパラメータは、DSPデータシートから得たもので、 $V_{ref}$ 電圧リファレンスから $V_{lL}/V_{lH}$ 電圧リファレンスに調整されたものです(4.2節参照)。                                                        |  |  |

| t <sub>Acc</sub>    | : | SDRAMから与えられる最大アクセス・タイム。このパラメータは、SDRAMデータシートから得られたものです。                                                                                                             |  |  |

| $C_{0,weak}(Q_n)$   | : | 弱プロセス・バッファでのSDRAMデータ・バッファ伝送ディレイで、SDRAMテスト負荷のみを使用したとき、SDRAM出力バッファが有効/無効になったときから信号がリファレンス電圧をクロスしたときまでとして測定されます。SDRAM IBISモデルとIBISシミュレーション・パッケージを使用して計算されます。          |  |  |

| $C_{0,weak}(Clk)$   | : | 弱プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、DSPテスト負荷のみを使用したとき、toから信号がリファレンス電圧をクロスしたときまでとして測定されます。DSP IBISモデルとIBISシミュレーション・パッケージを使用して計算されます。                                    |  |  |

|                     |   | DSP入力セットアップでの変数                                                                                                                                                    |  |  |

| $B_{0,weak}(Q_n)$   | : | 弱プロセス・バッファでのSDRAMデータ・バッファ伝送ディレイで、ボード上の <b>DSPピンで</b> 、SDRAM出力バッファが有効になったときから <b>信号が有効論理レベルに到達したときまで</b> として測定されます。SDRAMとDSP IBISモデルとIBISシミュレーション・パッケージを使用して計算されます。 |  |  |

| $B_{0,weak}(Clk)$   | : | 弱プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、ボード上のSDRAMピンで、t₀から <b>信号がリファレンス電圧をクロスしたときまで</b> として測定されます。SDRAMとDSP IBISモデルとIBISシミュレーション・パッケージを使用して計算されます。                         |  |  |

DSPの入力セットアップは、最低限の要求です。したがって、式の右辺の全パラメータの総和は、ゼロより大きくなければなりません。調整可能な唯一の変数は、クロックと信号バッファ伝送ディレイです。これらは、長さやインピーダンスなどのトレース特性を変化させることで、調整されます。SDRAMからのDSPリードの場合、ワーストケースの入力セットアップは、クロック・バッファとSDRAMデータ・

バッファが遅い場合に起こります。これは、計算のために弱 バッファを使用しなければならないことを意味します。繰り 返しになりますが、反射が最小で、信号が単調であることを 仮定しています。

図14は、DSP入力セットアップ・タイミングを図的に表したものです。

図14. DSPの入力セットアップ

複数のデータ信号があるので、ボードとテスト負荷間の最大 の差分を見つけるために、(上で述べた手法を用いて)それ ぞれのトレースを計算する必要があります。この最大差分

は、DSPへのワーストケースのセットアップ・タイムをもたらします。

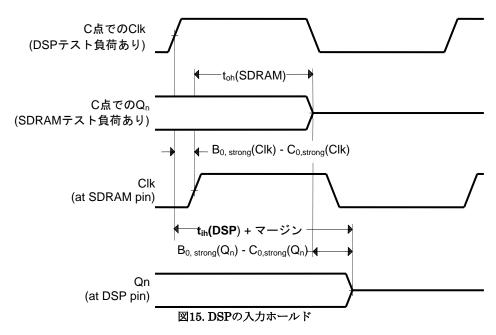

#### 6.4 DSP の入力ホールド

DSPへのホールド・タイムが満たされていることを確認する ために、次式で定義されるマージンがゼロより大きくなけれ ばなりません。

データ線に対する テスタ負荷調整

クロック線に対する テスタ負荷調整

上記の変数および定数については、表4に記載しています。

表4. DSP入力ホールド・タイム・パラメータ

####

ファが有効/無効になったときから信号がリファレンス電圧をクロスしたときまでとして測定されます。SDRAM IBISモデルと

IBISシミュレーション・パッケージを使用して計算されます。

C<sub>0,strong</sub>(Clk) : 強プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、DSPテスト負荷のみを使用したとき、t<sub>0</sub>から信号がリファレ

ンス電圧をクロスしたときまでとして測定されます。DSP IBISモデルとIBISシミュレーション・パッケージを使用して計算され

ます。

#### DSP入力ホールドでの変数

B<sub>0,strong</sub>(Q<sub>n</sub>) : 強プロセス・バッファでのSDRAMデータ・バッファ伝送ディレイで、ボード上のDSPピンで、SDRAMデータ・バッファが無効

になったときから**信号が無効論理レベルに到達したときまで**として測定されます。DSPとSDRAM IBISモデルとIBISシミュレー

ション・パッケージを使用して計算されます。

B<sub>0,strong</sub>(Clk) : 強プロセス・バッファでのDSPクロック・バッファ伝送ディレイで、ボード上のDSPピンで、t<sub>0</sub>から**信号がリファレンス電圧をク**

ロスしたときまでとして測定されます。DSPとSDRAM IBISモデルとIBISシミュレーション・パッケージを使用して計算されま

す。

DSPの入力ホールドは、最低限の要求です。したがって、式の右辺の全パラメータの総和は、ゼロより大きくなければなりません。調整可能な唯一の変数は、クロックと信号バッファ伝送ディレイです。これらは、トレース特性を変化させることで、調整されます。

クロック信号とデータ信号が速い場合に、DSPの入力ホールドが最悪値になります。したがって、DSP入力ホールド・タ

イムを計算するために強バッファを使用しなければなりません。繰り返しになりますが、反射が最小で、信号が単調であることを仮定しています。

図15は、DSP入力ホールド・タイミングを図的に表したものです。

複数のデータ信号があるので、ボードとテスト負荷間の最小の差分を見つけるために、(上で述べた手法を用いて)それぞれのトレースを計算する必要があります。この最小差分は、DSPへのワーストケースのホールド・タイムをもたらします。

## 7 AC タイミング解析手順のまとめ

この章では、このアプリケーション・レポートで述べた手法にしたがって、ACタイミング解析手順についてまとめます。各節で、情報の収集、IBISシミュレーション、解析からなる3ステップの詳細な説明を行います。

#### 7.1 情報の収集

ACタイミング解析のはじめのステップは、以下のものを含む関係する全ての情報を収集することです。

- 1. DSPとSDRAMのデータシート

- 2. DSPとSDRAMのIBIS モデル

- 3. ボード・レイアウトと特性

図16は、インターフェース例におけるボード・レイアウトとトレース特性を表したものです。図中のRsは、シグナル・インテグリティ実現のために使用される直列終端抵抗です。 実際の値は、ボードと入出力(I/O)バッファに依存して変化します。

注:この例で全てのトレースは、特性インピーダンスZ0=50 $\Omega$ で、シグナル・インテグリティのために33 $\Omega$ の直列終端抵抗(Rs)を要求されていると、仮定します。実際のRsの値は、入出力バッファ特性に依存します。

#### 図16. DSP-SDRAMインターフェースのボード特性の例

## 7.2 IBIS シミュレーション

DSP-SDRAMインターフェースのIBISシミュレーションを 行う前に、5章で述べたように、ノイズ・マージンを考慮す るためにIBISモデルの $V_{\rm IL}$ ,  $V_{\rm IH}$ レベルを、はじめに修正します。 $V_{\rm inl}$ を0.6Vに、 $V_{\rm inh}$ を2.5Vに編集します。

#### 7.2.1 ボード上での DSP 出力の IBIS シミュレーション

DSPは、ECLKOUT、制御/アドレスをSDRAMに出力します。 さらに、DSPライトでは、DSPはデータED[31:0]を出

力します。これらの信号それぞれについて、IBISパッケージ で図17に示すように表すことができます。

図17. ボード上でのDSP出力のIBIS表現

SDRAMピンB点(パラメータ $B_0$ )での絶対タイミングを得るために、IBISシミュレーションを行います。クロック信号は、B点で単調でなければならず、リファレンス電圧 $V_{\rm ref}$ で時刻 $B_0$ を測定します。データ/制御は、B点で単調でないかもしれず、4章で述べたように、新たなリファレンス電圧 $V_{\rm II}/V_{\rm IH}$ で時刻 $B_0$ を測定します。

2回シミュレーションを行わなければなりません。1つは、パラメータ $(B_{0, \text{ weak}})$ を得るために弱出力ドライブ能力を使用したもので、もう1つは、パラメータ $(B_{0, \text{ strong}})$ を得るために強出力ドライブ能力を使用したものです。ピン間のバリエーションの考慮については、3.3節を参照してください。

まとめると、このステップでこれらのパラメータを測定します。

B<sub>0, strong</sub>(Clk) 表1および表4用

B<sub>0, weak</sub>(Clk) 表2および表3用

B<sub>0, strong</sub>(制御/アドレス) 表2および表4用

B<sub>0, weak</sub>(制御/アドレス) 表1および表3用

B<sub>0, strong</sub>(Q<sub>n</sub>) 表2用

B<sub>0, weak</sub>(Q<sub>n</sub>) 表1用

#### 7.2.2 テスタ負荷を使用した DSP 出力の IBIS シミュ レーション

7.2.1節の各信号について、DSPデータシートはテスト負荷を使用した場合の測定値を提供しています。図18は、IBISパッケージ中でどのようにこれが表現されるかを示したものです

注:テスタ負荷回路は、それぞれのデバイスで異なります。正確なテスタ負荷回路については、デバイスのデータシートを参照してください。

### 図18. テスト負荷を使用したDSP出力のIBIS表現

DSPテスト負荷を使用したC点(パラメータ $C_0$ )での絶対タイミングを得るために、IBISシミュレーションを行います。データシートのリファレンス電圧 $V_{ref}$ で、時刻 $C_0$ を測定します。

2回シミュレーションを行わなければなりません。1つは、パラメータ $(C_{0, weak})$ を得るために弱出力ドライブ能力を使用したもので、もう1つは、パラメータ $(C_{0, strong})$ を得るために強出力ドライブ能力を使用したものです。ピン間のバリエーションの考慮については、3.3節を参照してください。

まとめると、このステップでこれらのパラメータを測定します。

C<sub>0, strong</sub>(Clk) 表1および表4用

C<sub>0, weak</sub>(Clk) 表2および表3用

C<sub>0, strong</sub>(制御/アドレス) 表2および表4用

Co, weak(制御/アドレス)表1および表3用

Co, strong(Qn) 表2用

C<sub>0, weak</sub>(Q<sub>n</sub>) 表1用

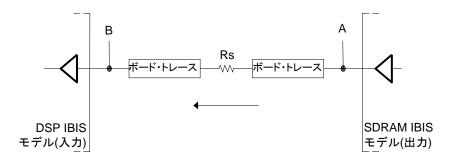

## 7.2.3 ボード上での SDRAM 出力の IBIS シミュレーショ

SDRAMは、DSPリードにおいてデータDQ[31:0]を出力します。これらの信号それぞれについて、IBISパッケージで図19に示すように表すことができます。

図19. ボード上でのSDRAM出力のIBIS表現

DSPピンB点(パラメータ $B_0$ )での絶対タイミングを得るために、IBISシミュレーションを行います。データ信号は、DSPピン(B点)で単調でないかもしれないので、4章で述べたように、新たなリファレンス電圧 $V_{IL}/V_{IH}$ で時刻 $B_0$ を測定します。

2回シミュレーションを行わなければなりません。1つは、パラメータ $(B_{0, \text{ weak}})$ を得るために弱出力ドライブ能力を使用したもので、もう1つは、パラメータ $(B_{0, \text{ strong}})$ を得るために強出力ドライブ能力を使用したものです。ピン間のバリエーションの考慮については、3.3節を参照してください。

まとめると、このステップでこれらのパラメータを測定します。

B<sub>0, strong</sub>(Q<sub>n</sub>) 表4用

B<sub>0, weak</sub>(Q<sub>n</sub>) 表3用

## 7.2.4 テスタ負荷を使用した SDRAM 出力の IBIS シミュレーション

7.2.4節の各信号について、SDRAMデータシートはテスト負荷を使用した場合の測定値を提供しています。図20は、IBISパッケージ中でどのようにこれが表現されるかを示したものです。

注:テスタ負荷回路は、それぞれのデバイスで異なります。正確なテスタ負荷回路については、デバイスのデータシートを参照してください。

## 図20. テスト負荷を使用したSDRAM出力のIBIS表現

SDRAMテスト負荷を使用したC点(パラメータ $C_0$ )での絶対タイミングを得るために、IBISシミュレーションを行います。データシートのリファレンス電圧 $V_{ref}$ で、時刻 $C_0$ を測定します。

2回シミュレーションを行わなければなりません。1つは、パラメータ $(C_{0, weak})$ を得るために弱出力ドライブ能力を使用したもので、もう1つは、パラメータ $(C_{0, strong})$ を得るために強出力ドライブ能力を使用したものです。ピン間のバリエーションの考慮については、3.3節を参照してください。

まとめると、このステップでこれらのパラメータを測定します。

C<sub>0, strong</sub>(Q<sub>n</sub>) 表4用

C<sub>0, weak</sub>(Q<sub>n</sub>) 表3用

#### 7.3 計算

これまでの節で集めたデータを使用して、6章で述べたタイミング解析を開始することができます。

### 7.3.1 SDRAM の入力セットアップ

6.1節の表1に記入します。

- 希望するEMIFクロック周期ECLK<sub>Per</sub>を入力します。

- SDRAMデータシートから得られる入力セットアップ要求を入力します。

- SDRAMデータシートからの値を直接入力してはいけません。かわりに、4章で述べたように電圧リファレンス  $V_{ref}$ から $V_{IL}/V_{IH}$ への変換によってデータシートの値を調整します。例えば、SDRAMデータシートで次のように規定していると仮定します。

- 入力ピンでテスタ入力スルー・レートまたは遷移時間が1V/ns

- リファレンス電圧(V<sub>ref</sub>)が1.5V

- $-V_{IL} = 0.8V, V_{IH} = 2.0V$

- V<sub>ref</sub>に対して、入力セットアップ要求(t<sub>isu</sub>)が2ns

$V_{\text{L}}/V_{\text{H}}$ に対して調整されたSDRAM入力セットアップ要求は、図10中の式にしたがって計算されます。

- $t_1 = t_{isu} (1/m) * (V_{ref} V_{IL}) = 2 (1/1) * (1.5 0.8) = 1.3ns$

- $t_2 = t_{isu} (1/m) * (V_{ref} V_{IH}) = 2 [1/(-1)] * (1.5 2.0) = 1.5ns$

t<sub>2</sub>の方が大きいので、より厳しい新たなt<sub>isu</sub>になります。 表1にt<sub>2</sub>を入力します。

- DSPデータシートからt<sub>pd-max</sub>を入力します。

- 7.2.1, 7.2.2節で得られたB<sub>0</sub>, C<sub>0</sub>パラメータを入力します。

6.1節の式を用いて、SDRAM入力セットアップ・マージンを算出します。

#### 7.3.2 SDRAM の入力ホールド

6.2節の表2に記入します。

- SDRAMデータシートから得られる入力ホールド要求を入力します。SDRAMデータシートからの値を直接入力してはいけません。かわりに、4章で述べたように電圧リファレンス $V_{ref}$ から $V_{IL}/V_{IH}$ への変換によってデータシートの値を調整します。

- DSPデータシートからtpd-minを入力します。

- 7.2.1, 7.2.2節で得られたB<sub>0</sub>, C<sub>0</sub>パラメータを入力します。

6.2節の式を用いて、SDRAM入力ホールド・マージンを算出します。

#### 7.3.3 DSP の入力セットアップ

6.3節の表3に記入します。

- 希望するEMIFクロック周期ECLK<sub>Per</sub>を入力します。

- DSPデータシートから得られる入力セットアップ要求を 入力します。DSPデータシートからの値を直接入力して はいけません。かわりに、4章で述べたように電圧リ ファレンスV<sub>ref</sub>からV<sub>IL</sub>/V<sub>IH</sub>への変換によってデータシート の値を調整します。

- SDRAMデータシートからt<sub>Acc</sub>を入力します。

7.2.1 から 7.2.4節で得られたB<sub>0</sub>, C<sub>0</sub>パラメータを入力します。

6.3節の式を用いて、DSP入力セットアップ・マージンを算出します。

#### 7.3.4 DSP の入力ホールド

6.4節の表4に入力します。

- DSPデータシートから得られる入力ホールド要求を入力 します。DSPデータシートからの値を直接入力してはい けません。かわりに、4章で述べたように電圧リファレ ンスV<sub>ref</sub>からV<sub>IL</sub>/V<sub>IH</sub>への変換によってデータシートの値を 調整します。

- SDRAMデータシートからtohを入力します。

- 7.2.1 から 7.2.4節で得られたB<sub>0</sub>, C<sub>0</sub>パラメータを入力します。

6.4節の式を用いて、DSP入力ホールド・マージンを算出します。

#### 8 まとめ

このアプリケーション・レポートで述べた式を使用することで、IBISモデルおよびシミュレーションをSDRAMとDSP間のポイント・ツー・ポイント接続のタイミングに反映させることができます。望まれるシグナル・インテグリティの確保や、SDRAMおよびDSPのセットアップ、ホールド両方の十分なタイミングを確保するためには、これらの式を繰り返し使用することが、必要になるかもしれません。この手法は、SDRAMやEMIFインターフェースに限られたものではありません。全てのDSP信号は、満たすべきセットアップおよびホールド・タイム特性を持っています。このアプリケーション・レポートで述べた手法を使用することで、全ての関連する信号について適切なタイミング関係を決定するために、IBIS解析を使用することができます。

信号に対する様々な負荷の補正のために、テスタについての 理解が、適切なタイミングの逆算に必要とされます。ノイ ズ・レベル・マージンは、有効論理レベルを修正することで 考慮に入れることができます。このアプリケーション・レ ポートで述べた式は、どれだけのマージンが期待できるかを 表したものになります。許容可能なマージン・レベルは、シ ステム環境や動作条件に基づいて決定されなければなりませ か。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます) 及びTexas Instruments Incorporated(TIJの親会社、以下 TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、 条件その他のパラメーターと異なる、あるいは、それを超えてなされ た説明で当該TI製品もしくはサービスを再販売することは、当該 TI製品もしくはサービスに対する全ての明示的保証、及び何らか の黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為 です。TIは、そのような説明については何の義務も責任もありません。

なお、日本テキサス・インスツルメンツ株式会社半導体集積回路 製品販売用標準契約約款もご覧下さい。

http://www.tij.co.jp/jsc/docs/stdterms.htm

Copyright © 2006, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点 を遵守して下さい。

#### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装) 又は製品単品で取り扱いを行う場合は、接地された導 電性のテーブル上で(導電性マットにアースをとったも の等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる 全ての装置類は、静電気の帯電を防止する措置を施す こと。

- 前記のリストストラップ・導電性手袋・テーブル表面 及び実装装置類の接地等の静電気帯電防止措置は、常 に管理されその機能が確認されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送 及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に 従い基板実装すること。

#### 4. 機械的衝撃

梱包品(外装、内装、個装)及び製品単品を落下させたり、 衝撃を与えないこと。

#### 5. 熱衝撃

● はんだ付け時は、最低限260℃以上の高温状態に、10 秒以上さらさないこと。(個別推奨条件がある時はそれ に従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。 (不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上