# 使用するADCの全潜在能力を引き出す方法

#### John Austin

現在の高分解能ADC(アナログ - デジタル・コンバータ)の 多くは単電源で動作し、完全差動入力を利用しています。 このことは、コモンに対してバイポーラとなるシングルエ ンド信号を扱う場合に問題となる可能性があります。この アプリケーション・レポートでは、プログラマブル・ゲイ ン・アンプ(PGA)や内部基準電圧等の最新の機能を利用し てフルスケール入力範囲を保つための回路構成について説 明します。また、これらの信号処理回路を有効利用するた めの部品選択に際し、設計者が考慮する必要のある問題に ついても論じます。

差動入力によって得られる同相電圧除去比により、入力信 号に加えられたシステム・ノイズの大半は除去されます。 多くのコンバータでは、アナログ入力信号のバイポーラ・ ゼロの位置たけでなく、フルスケールのアナログ入力範囲 も基準入力によって決まります。

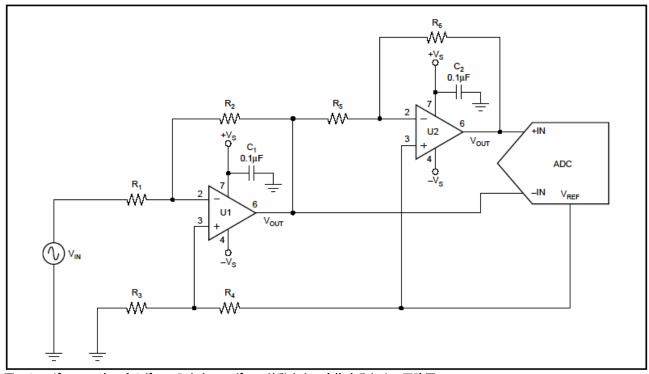

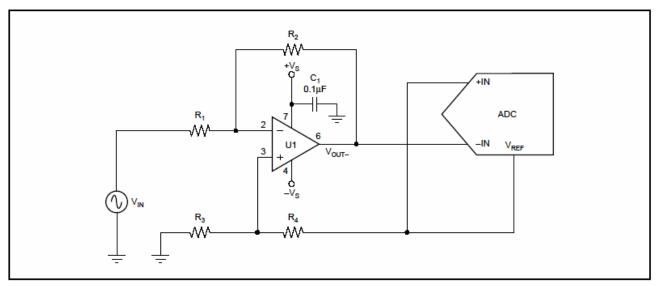

内蔵PGAを持たない真の差動入力ADC向けには、図1で提 案されているようなソリューションがあります。

伝達方程式は、基本的な回路解析と一般的なオペアンプ理 論を使用して導出できます。導出の詳細については、付録 Aを参照してください。

$$\frac{R_{2}}{R_{1}} = G_{(U1)}$$

$$\frac{R_{6}}{R_{5}} = G_{(U2)}$$

$$\frac{R_{3}}{R_{3} + R_{4}} = \frac{V_{BIAS}}{V_{REF}(G_{(U1)} + 1)} = \frac{1}{(G_{(U1)} + 1)}$$

(1)

例として、単電源5Vによって動作し、DC2.5Vを基準とす るフルスケールの差動入力2.5V<sub>p-p</sub>がコンバータに必要であ ると仮定します。DCバイアスの値が分かっているので、 ゲイン/減衰、電源、抵抗の各値は上記の式を使用して計算 されます。入力信号 $V_{IN} = 5V_{p-p}(バイポーラ)$ となります。

図1 シングルエンドのバイポーラ入力をユニポーラ差動出力に変換するための回路図

この資料は、Texas Instruments Incorporated(TI)が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本TI)が英文から和文へ翻訳して作成したものです。

(日本 II) が突火がられていい。 資料によっては正規英語版資料の更新に対応していないものがあります。日本 II による和文資料は、あくまでも II 正規英語版をご理解頂くための補助的参考資料としてご使用下さい。 製品のご検討及びご採用にあたりましては、必ず正規英語版の最新資料をご

TI 及び日本 TI は、正規英語版にて更新の情報を提供しているにも関わらず 更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責 任も負いません。

SBAA069A翻訳版

JAJA185 www.tij.co.jp

図1に対応して要求される抵抗比率は、次の式で計算されます。

$$\frac{R_2}{R_1} = G_{(U1)} = 1/2$$

$$\frac{R_6}{R_5} = G_{(U2)} = 1$$

(2)

$$\frac{R_3}{R_3 + R_4} = \frac{V_{BIAS (U1)}}{V_s(G_{(U1)} + 1)} = (2.5) / [5(1/2 + 1)] = 1/3$$

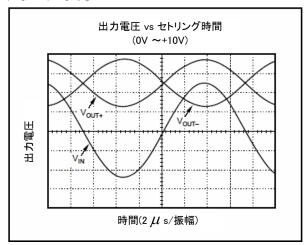

これらの比率から、抵抗値を決定できます。この例で使用される抵抗値は、 $R_1=R_4=R_5=R_6=300k\,\Omega$ 、および $R_2=R_3=150k\,\Omega$ としました。図2に示すのは、入力信号( $V_{IN}=5V_{PP}$  バイポーラ)と差動出力( $V_{OUT+}$ および  $V_{OUT-}$ )です。出力は、2.5VでDCバイアスをかけられた差動信号 $2.5V_{PP}$  になっています。

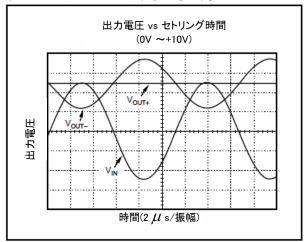

図2 オシロスコープの波形(図1の回路)、 $V_{IN} = 5V_{pp}$  (バイポーラ)、対応する差動出力( $V_{OUT+}$ 、 $V_{OUT-}$ ) = DC2.5Vでバイアスをかけられた $2.5V_{pp}$

内部基準電圧を持たないADCの場合に、ADCへの基準入力用として、電源側から単純な抵抗分圧器(resistor divider)が接続してあれば十分であると考える人もいますが、設計者が念頭に置く必要があるのは、基準電圧に変化があれば、相関的な変化がコンバータの出力に発生するということです。抵抗値はドリフトしやすい傾向にあり、不要なノイズの原因になります。高精度、低ドリフト、低ノイズの基準電圧を利用することは、常に好ましい設計実践です。

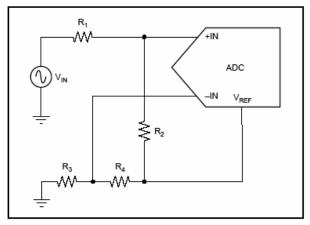

ADS7870、ADS1210/ADS1211、ADS1212、ADS1250といったTexas Instrumentsの多機能ADCの新製品には、PGAと内部基準電圧の両方が組み込まれています。 図3は、これらの機能を実装してシンプルな抵抗ネット

図3は、これらの機能を実装してシンプルな抵抗ネット ワークを作り、実現可能なソリューションとしたものです。

図3抵抗ネットワークを利用して、入力信号の減衰とDCバイアスを実現する

この構成を使用すると、より確度の高い結果が得られるようになり、また部品の点数も最小限に抑えられます。このようなことをしても確度は向上せず、同じようなゲイン回路がまたひとつADCに組み込まれるだけではないのかと思われる方もいるかもしれませんが、この回路の使用により部品点数が最小限になり、コストが下がることは間違いありません。これは、設計者にとって利点です。

伝達方程式は次の通りです。導出の詳細については、付録 Aを参照してください。

$$\frac{R_2}{R_1 + R_2} = \frac{+\ln}{V_{IN}} = 1/2$$

$$\frac{R_3}{R_3 + R_4} = \frac{R_2}{R_1 + R_2} = 1/2$$

(3)

これらの比率から抵抗値が選択され、 $R_1=R_2=R_3=R_4=150$ k $\Omega$ としました。擬似差動電圧 (+In-(-In))は2.5 $V_p$  に対応しています。PGA設定値を2にすると、フルスケール入力範囲の効率的な利用が可能になります。

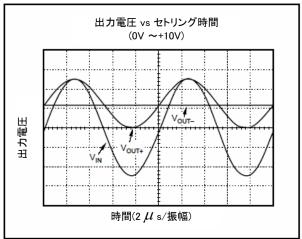

図 4 オシロスコープの波形(図4の回路)、 $V_{IN}=5V_{pp}$  (バイポーラ)、対応する出力は $V_{OUT+}=DC$  2.5Vでバイアスをかけられた $2.5V_{pp}$ 、 $V_{OUT-}=DC$  2.5V。

www.tij.co.jp JAJA185

基準電圧に負荷をかけると望ましくないドリフトが発生することがあります。設計者はADCの入力インピーダンスについても考慮する必要があります。入力インピーダンスが低いと、信号損失が発生する可能性があります。これが問題となるようであれば、図5を実装することもできます。

$R_2/R_1$  が減衰/ゲインを提供するのに対し、 $R_4/R_3$  ではDCバイアスを提供します。PGAでは差動信号(+In-(-In))を増幅し、デバイスのフルスケール入力範囲を効率的に保ちます。

$$\frac{R_2}{R_1} = G_{(U1)} = 1/2$$

$$\frac{R_3}{R_3 + R_4} = \frac{1}{G_{(U1)} + 1} = \frac{1}{\frac{1}{2} + 1} = \frac{2}{3}$$

(4)

これらの比率から抵抗値が選択され、 $R_1=R_3=100k\,\Omega$ 、  $R_2=R_4=200k\,\Omega$  としました。擬似差動電圧(+In - (- In))は、 $2.5V_{p\cdot p}$  に対応しています。PGA設定値を2にすると、このデバイスのフルスケール範囲が維持されます。PGAを使用しなければ、この回路の(+In - (- In))ではフルスケール入力範囲の半分しか利用できなくなります。

高分解能アプリケーションを扱う場合には、部品の選定が非常に重要となります。オペアンプの主な選択基準としては、オフセット電圧ドリフトやノイズ等があります。ゲイン誤差や入力オフセット電圧等のDCオフセットは、ソフトウェアの較正やADCの内部較正によって取り除くことができます。

最もドリフトの低いアンプは、チョッパ安定化アンプです。Texas Instrumentsの製品では、TLC2652等がこれに当たります。このアンプの電源電圧範囲(supply range)は $\pm 1.9 \text{V} \sim \pm 8 \text{V}$ であり、オフセット電圧が非常に低く(1 mV)なっており、またオフセット電圧ドリフトも低く( $3 \text{nV} / ^{\circ} \text{C}$ )なっています。これらのアンプの帯域幅は限られており、他のアンプのアーキテクチャよりも多くノイズを発生させます。TLC2652の最大電圧ノイズは( $1 \text{kHz} \sim 1.9 \text{MHz}$ であり、標準的なユニティゲイン帯域幅は1.9 MHzです。このアンプは、低周波数アプリケーションで使用する方が効果的です。

DIFETアンプでは、電圧ドリフトが低く(数100  $nV/^{\circ}$ C)、且つノイズも非常に低く( $10nV/\sqrt{Hz}$  以下)、ユニティゲイン帯域幅がチョッパ安定化オペアンプよりも高くなっています。これらの性質は、ノイズが電圧ドリフトよりも大きな要因となる可能性のある高周波数アプリケーションに向いています。主な短所は値段が高いことです。

バイポーラ・プロセスによるアンプでは、良好な確度と高いユニティゲイン帯域幅が得られ、また比較的低コストでノイズを低く保つことが可能です。例として、オペアンプのOPA227ファミリを挙げます。このオペアンプの電圧ドリフトは低く(最大300nV/C)、電圧ノイズは非常に低く(最大3nV/ $\sqrt{Hz}$ )なっています。このアンプのユニティゲイン帯域幅は最小8MHz、スルー・レートは最小2.3V/ $\mu$ sであり、高周波アプリケーションに向いています。また、1チャネル当たりの価格が1ドルをかなり下回る、コスト効率のよいソリューションを実現できます。

図6 オシロスコープの波形、V<sub>IN</sub> = 5V<sub>PP</sub> V<sub>IN</sub> (バイポーラ)、対応する出力はV<sub>OUT+</sub> = DC 2.5V、 V<sub>OUT-</sub> = DC 2.5V でバイアスをかけられた2.5V<sub>PP</sub>

確度はおそらく最も低いものの、コスト効率が最も良いのがCMOSアンプです。CMOSアンプは標準的な単電源アンプです。良い例が、Texas InstrumentsのOPA340シリーズです。これらは単電源2.7V~5.5Vアンプであり、入力電圧範囲は電源レールより300mV外側までになり、また出力電圧は電源レールの1mV内側までスイング可能です。これらのデバイスは、高いノイズ特性(最大25nV/ $\sqrt{H_Z}$ )と大きな電圧ドリフト(最大2.5  $\mu$  V/°C)を持つ傾向にあります。そのため、分解能よりもコストが重視される、低分解能アプリケーションで使用する必要があります。

このアプリケーション・レポートでは、シングルエンド信号源を使用する場合でも、設計者が完全差動ADCを利用することを可能にする3つの信号処理回路を紹介してきました。ここで論じられたオペアンプのアーキテクチャには長所も短所もあり、それらについては各アプリケーションの具体的な細目に応じて考慮・検討する必要があります。ここで説明した部品の選定とパラメータは、上記の回路の確度に直接関係してきます。その他には、ボードのレイアウト、電源の選定、優れたフィルタリング技術などを設計時に考慮する必要があります。

JAJA185 www.tij.co.jp

図5. プログラマブル・ゲイン・アンプと出力基準電圧を利用した回路図

### 付録 A:

図1の回路の伝達方程式は次のように導出されます。

理想オペアンプのモデルより、入力インピーダンスは無限 と仮定します。つまり、オペアンプに流れ込む電流は無い ことになります。

$$I_{R1} = I_{R2} \tag{1}$$

$$\frac{V_{IN} - V_{2(U1)}}{R_{c}} = \frac{V_{2(U1)} - V_{OUT}}{R_{c}}$$

(2)

各項を結合し、 $V_{OUT}$  について解くと、次のようになります。

$$V_{OUT-} \frac{R_2}{R_1} V_{IN} = V_{2(U1)} \left( \frac{R_2}{R_1} + 1 \right)$$

(3)

ピン2での電圧がピン3での電圧と等価であるという代入を 行うと、次のようになります。

$$V_{OUT-} = -\frac{R_2}{R_1} V_{IN} + \left( \frac{R_2}{R_1} + 1 \right) \left( V_{3(U1)} \right)$$

(4)

ピン3での電圧は、分圧方程式によって容易に計算できます。

$$V_{3(U1)} = \frac{R_3}{R_3 + R_4} (V_S)$$

(5)

式(5)を式(4)と結合すると、次のようになります。

$$V_{OUT-} = -\frac{R_2}{R_1} V_{IN} + V_s \left( \frac{R_2}{R_1} + 1 \right) \left( \frac{R_3}{R_3} \frac{R_3}{R_3 + R_4} \right)$$

(6)

ここで、DCバイアスの値は次の通りです。

$$V_{BIAS(U1)} = \left[ \left( \frac{R_2}{R_1} + 1 \right) \left( \frac{R_3}{R_3 + R_4} \right) \right] \quad V_{REF}$$

(7)

式(6)が、オペアンプU1の最終的な伝達方程式になります。入力信号は、 $(R_2/R_1)$ のゲイン/減衰と、式(7)に対応するDCバイアスとともに反転されます。 $(R_2/R_1)=G_{(U1)}$  (ゲイン)として、抵抗比率 $R_3/(R_3+R_4)$ について解くと、式(7)は次のようになります。

$$\frac{R_3}{R_3 + R_4} = \frac{V_{BIAS}}{\left(V_S \left(G_{(U1)} + 1\right)\right)} = \frac{1}{\left(G_{(U1)} + 1\right)}$$

(8)

#### 図3の回路の伝達方程式の導出

入力 +IN は次の式で計算できます。

$$+I_{N} = \frac{R_{2}}{R_{1} + R_{2}} V_{IN} + \frac{R_{1}}{R_{1} + R_{2}} V_{REF}$$

$-I_N$  には、 $+I_N$ のDCバイアス電圧と同じDC電圧が必要です。このため、抵抗比率も同じにする必要があります。

$$\frac{R_1}{R_1 + R_2} = \frac{R_3}{R_3 + R_4}$$

抵抗比率について解くと、次のようになります。

$$\frac{R_2}{R_1 + R_2} = \frac{+\ln}{V_{IN}}$$

$$\frac{R_3}{R_3 + R_4} = \frac{R_2}{R_1 + R_2}$$

## ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上