# **LMV791**

Application Note 1516 Pspice Universal Test Circuits

Literature Number: JAJA304

# AN-1516

# PSPICE 汎用テスト回路

National Semiconductor Application Note 1516 Soufiane Bendaoud 2009 年 1 月

SPICE モデルが長年にわたって主流の座を得ていることには疑いの余地はありません。IC メーカーが正確なモデルを顧客に提供しようと努力してきた一方で、回路エンジニアなら SPICE マクロモデルの技術進歩と精度の向上を実感しているでしょう。

多くの IC メーカーは、自社のモデルが一番である、あるいは画期的な機能を実現していると自画自賛していますが、マクロモデルの精度をエンジニアが検証できるような回路の提供までは多くの場合に手が回っていないのが実状です。オペアンプのマクロモデルは多分最もニーズが大きいと考えられ、精度が高ければきわめて有用になりますが、専門的な知識のないユーザーが扱った場合は特に、重大な問題を引き起こす可能性も捨て切れません。

回路エンジニアの多くは、オペアンプのマクロモデルを全体回路に組み込む前に、モデルの検証に自らの時間を費やしています。モデルの精度が十分ではないとすると、実際にモデル自体に問題がある場合、あるいは SPICE テスト環境が適切にセットアップされていない場合に、アンプが正常に動作しないとエンジニアが誤解してしまう恐れも考えられます。実際には状況はモデルごとによって異なり、一部は特定の設定条件では動作しない場合もあります。そこでこのドキュメントでは、オペアンプのマクロモデルの欠陥を調べる方法を探るのではなく、オペアンプのマクロモデルのある意味汎用的なテスト回路集としてオペアンプ・モデルのテストに適した回路例を提示します。

#### テストすべきパラメータ

オペアンプの用途に応じてマクロモデルは複雑さが異なります。オペアンプの採用が適当と考えられるアプリケーションにとって必要なパラメータを、データシートと同じようにモデルはエミュレートできなければなりません。例えば出力フルスイングのオペアンプであれば、出力飽和電圧と負荷電流の関係をテストおよび検証できなければなりません。同様に低ノイズ・アンプは、他のモデル化パラメータとともに少なくとも電圧ノイズをエミュレートできなければなりません。

オペアンプごとにマクロにはこのような違いがありますが、多くの共通項も存在します。一般に関心の高いパラメータであり、通常はシミュレーションのスタートポイントとしても使われます。これらパラメータと対応するテスト回路およびシミュレーションを次のセクションで説明します。

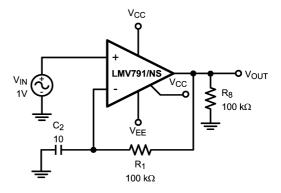

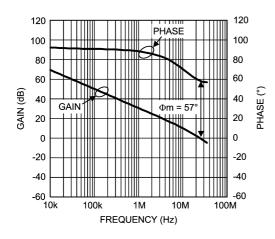

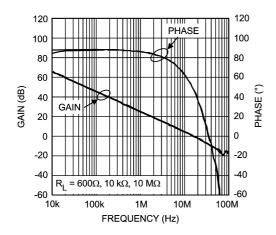

# 開ループ・ゲインと位相マージン

アンプ・マクロモデルの性能を検証するにあたってエンジニアが最初に取り組む特性は、おそらく開ループ・ゲインと周波数の関係ではないでしょうか。このテストは、DC ゲイン、- 3dB 周波数、ユニティゲイン帯域、位相マージンを示す点からも重要です。Figure 1 にテスト回路を示します。RC ネットワークによって出力に適切な DC 電圧がバイアスとして与えられます(この回路では電源レールの中間電圧)。周波数の高い領域では反転入力はコンデンサによってグラウンドに接続されるため、結果としてオペアンプは開ループとして構成されます。テスト対象のオペアンプは きわめて低い周波数領域にドミナント・ポールを持っている可能性もあるため、早めのロールオフ (f=1/2  $R_1C_2$ )が得られるように、コンデンサの容量は大きめに選びます。シミュレーション結果には滑らかな変化と 20dB/dec でのロールオフが示されています。

開ループ・ゲインと位相をテストする際には、アンプのユニティゲイン帯域以上をシミュレーションの上限周波数として設定しなければなりません。

出力フルスイング・モデルを使用する場合は、テスト回路の負荷としてデータシートに示されているのと同じ負荷を使う必要があります。そうでないと結果に実際のアンプの性能が反映されません。特に DC ゲイン  $(A_{OL}=g_mR_L)$  が該当します。

FIGURE 1. Open Loop Gain and Phase Test Circuit

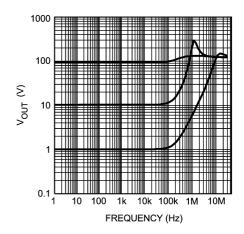

FIGURE 2. Simulated Open Loop Gain and Phase

FIGURE 3. Measured Open Loop Gain and Phase

# スルーレート

スルーレートは別の観点からアンプのスピードを定義した項目であり、ほとんどのアンプでモデル化されています。スルーレートは一般にテイル電流と補償容量(I/C)の比で決まります。

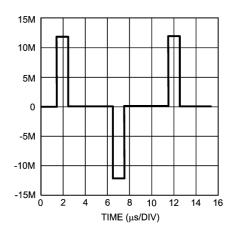

I\*dt = C\*dv の関係がすでにわかっているので、単純に Figure 4 の回路を使用し、出力の微分からスルーレートを取得します。 PSPICE のプローブ画面で挿入コマンドを使用して、出力電圧プローブの前に文字「d」を追加します。

このテスト回路で適切な結果を得るには、スルーレートで制限される様子がわかるように、入力ステップ関数に十分に大きな振幅を与える必要があります。スルーレートのシミュレーションを実行する場合は、入力信号の立ち上がり時間と立ち下がり時間をアンプの見込みスルーレートよりも短く設定してください。そのように設定するとアンプのスルーレートが支配的となったテスト結果が得られます。入力信号周波数はオペアンプのスピードに従って選択します。周波数が高すぎると収束問題を引き起こします。

FIGURE 4. Slew Rate Test Circuit

FIGURE 5. Simulated Slew Rate

#### CMRR および PSRR

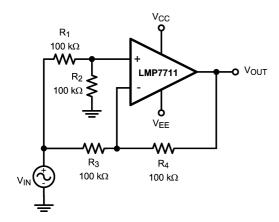

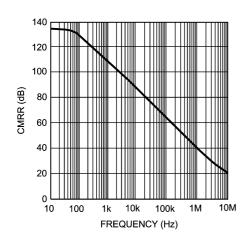

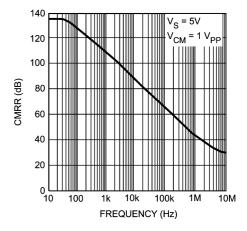

これら 2 つのパラメータは常にモデル化されるわけではありませんが、ともに重要です。通常 CMRR と PSRR は、単純な RC ネットワーク、抵抗分圧回路、電圧制御型電圧源で構成されるため、モデルへの実装は比較的簡単です。

CMRR は入力信号によって非反転入力が変調される現象なので、非反転構成の回路では特に重要です。一方の PSRR は電源が干渉の影響を受けやすいすべてのアプリケーションで重要なほか、電源電圧が大きく変動するアプリケーションでは DC PSRR が重要になります。

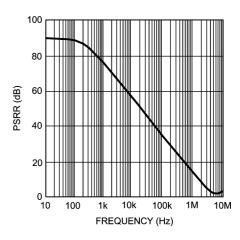

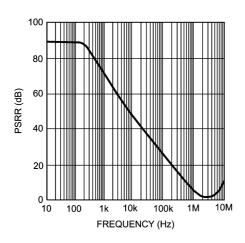

これら 2 つのパラメータのシミュレーションには Figure 6 と Figure 9 に示したテスト回路を使います。CMRR と PSRR が正しくモデル化されれば、ポール位置とゼロ位置はデータシート内のグラフに一致するはずです。

FIGURE 6. CMRR TEST CIRCUIT

FIGURE 7. SIMULATED CMRR RESPONSE vs. FREQUENCY

FIGURE 8. Measured CMRR vs. Frequency

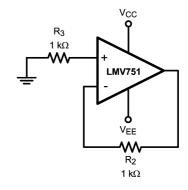

FIGURE 9. PSRR TEST CIRCUIT

FIGURE 10. SIMULATED PSRR RESPONSE vs. FREQUENCY

3

www.national.com/jpn/

FIGURE 11. Measured PSRR vs. Frequency

# 閉ループ出力インピーダンス

データシートには記載されないことが少なくない仕様項目 の1つですが、必要かつ不可欠となる場合があります。

出力インピーダンスを正しくモデル化すると、さまざまな容量性負荷環境でセトリングの振る舞いがより正確に得られます。

また、出力インピーダンスは、安定性を得る目的で補償方式を検討する場合に適切な部品定数の算出に必要です。

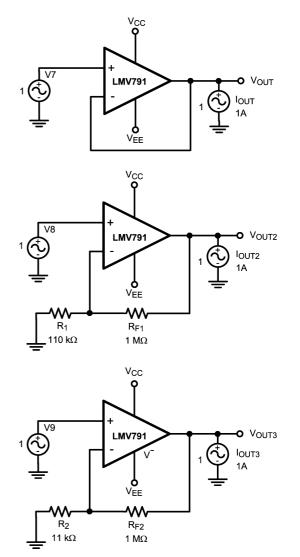

Figure 12 のテスト回路を使うと、ゲイン 1、ゲイン 10、ゲイン 100 で、出力インピーダンスと周波数の関係がそれぞれ得られます。出力インピーダンスは出力電圧と電流の比から求めます(アンプ出力に 1A 電流源を配置)。

Figure 13 のグラフは LMV791 の閉ループ出力インピーダンスを示しています。高周波数領域(グラフが平坦になっている部分)で、値はおよそ 120 です。グラフは両方の軸ともに対数で描かれている点に注意してください。

FIGURE 12. Output Impedance Test Circuits for a gain of 1, 10 and 100

FIGURE 13. Simulated Closed Loop Output Impedance

# 電圧ノイズと電流ノイズ

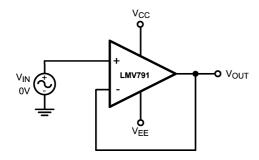

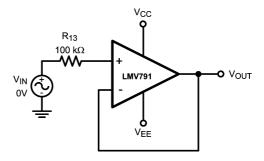

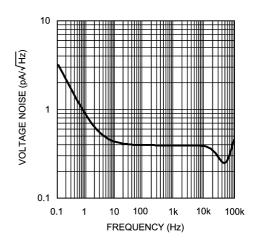

アンプのマクロモデルの技術的進歩が見られるとすれば、 電圧ノイズと電流ノイズはそのうちの 1 つでしょう。最近 の一部のモデルでは、フリッカ・ノイズ成分を含む電圧ノ イズや、優れた精度での電流ノイズのシミュレーションが 可能になっています。ノイズのモデルをマクロモデルに統 合しても演算時間あるいはシミュレーション時間がそれほ ど長くなるわけではありませんが、少なくともデータシー トを模倣した電圧ノイズ密度特性式のほか1/fコーナーを表 現した適切な式を導出しない限り、ある意味難しい作業の 1 つです。電圧ノイズ密度は電圧フォロワー (0V の電圧源 を使用)の出力を両方の軸ともに対数スケールで得ること で簡単にテストできます。電流ノイズ密度をシミュレー ションするには同じ回路を使いますが、非反転端子に 100k の抵抗を直列に挿入します。プローブ・ウィンドウ で得られた結果を選択した抵抗値(ここでは100k)で除算 してください。

電流ノイズは抵抗に連動するため、大きな抵抗値を用いると電流ノイズは支配的になり、電圧ノイズと熱ノイズは電流ノイズに比べて無視できる値に下がります。当然のことながら電流ノイズがきわめて小さい上に高いソース抵抗が必要になるような一部の例外も存在します。ノイズ源はソース・インピーダンスの関数として評価することが適切です。PSPICE は解析セットアップ・ウィンドウで出力電圧を規定してください。Figure 14 で、出力電圧を V ( $V_{OUT}$ )、入力電圧を  $V_{IN}$  として規定し、「noise enabled」をチェックした状態で結果を取得します。

FIGURE 14. Voltage Noise Density Test Circuit

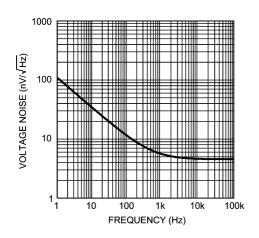

FIGURE 15. Simulated Voltage Noise Density

FIGURE 16. Current Noise Density Test Circuit

FIGURE 17. Simulated Current Noise Density

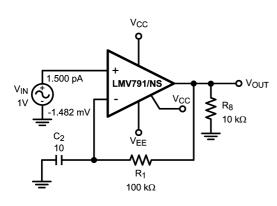

# 入力バイアス電流と入力オフセット電圧

入力バイアス電流と入力オフセット電圧の 2 つのパラメータは、おそらくモデル化が簡単な部類に入ります。入力オフセット電圧は入力端における電圧制御型電圧源として実装可能であり、その値はデータシートから取得します。

一般にバイアス電流あるいはオフセット電圧のテストには 特定のテスト回路は必要ありません。このドキュメントで 取り上げたどの回路を使っても構いません。オフセット電 圧とバイアス電流の値を見るには、SPICE で電圧ラベルと 電流ラベルをアクティブにしなければなりません。この様 子を Figure 18 に示します。入力バイアス電流は 1.5pA で、 入力オフセット電圧は 1.48mV です。

電源を流れる電流 1.15mA は待機時電流を表しています。

FIGURE 18. Offset Voltage and Input Bias Current

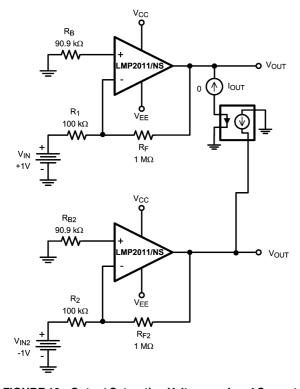

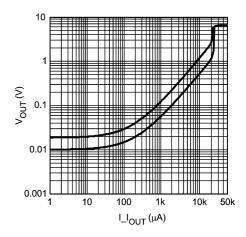

# 出力飽和電圧

出力飽和電圧パラメータはドロップアウト電圧としても知られています。出力飽和電圧は出力電圧を負荷電流の関数として表すことから、出力フルスイングのアンプ・モデルでは特に重要であり、重い負荷を駆動する場合、あるいはダイナミックレンジが課題となる場合に、適切なオペアンプを選択するために必要です。

テスト回路は単純な DC スイープを採用したもので、負荷電流のソースとシンクを再現するために反対の極性を持つ2つの等しい入力電圧を使用しています。

FIGURE 19. Output Saturation Voltage vs. Load Current Test Circuit

FIGURE 20. Simulated Output Saturation Voltage

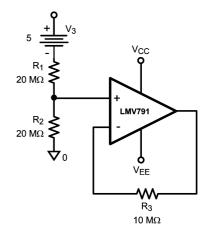

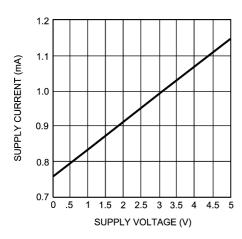

#### 電源電流と電源電圧の関係

下記の回路は、電源電流をスイープし、異なる電源電圧に てアンプがどれだけの電流を引き込むかを判定するテスト 回路です。このテストは消費電力を考慮しなければならな いアプリケーションに有効です。

電源電流グラフの傾きはモデルへの追加が簡単にできます。

FIGURE 21. Supply Current vs. Supply Voltage

FIGURE 22. Simulated Supply Current vs. Supply Voltage

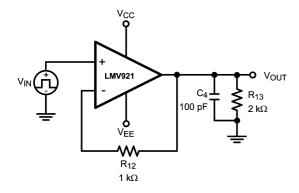

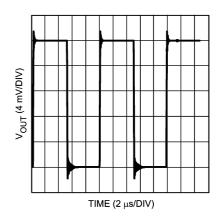

# オーバーシュートと過渡応答

このテスト回路は過渡応答のテスト(小信号と大信号)と オーバーシュートのテストに対応しています。

オーバーシュートは重要です。その理由は、アンプに容量性負荷が接続されているときに、発生するリンギング量がオーバーシュートとして示されるからです。オーバーシュートは時間領域での安定性の指標の1つであり、周波数領域に存在するピークと等価です。

一部のマクロモデルは外付けの受動部品を使って、オーバーシュートを高精度でシミュレーションします。 ただし 位相マージンの精度が高ければ、一般にオーバーシュート は本来の大きさに比較的近い値が得られます。

過渡応答もオーバーシュート用のテスト回路を使ってテストしますが、100pF コンデンサは使用しません。データシートに小容量負荷を使って小信号過渡応答を測定していることが示されている場合は、単純に同じ容量を使用してください。

FIGURE 23. Overshoot Test Circuit

FIGURE 24. Simulated Overshoot

#### コモンモード電圧範囲

コモンモード電圧範囲は、入力信号のヘッドルーム、すなわち入力信号と電源をどの程度切り離すべきかを示す点で重要なパラメータの 1 つです。

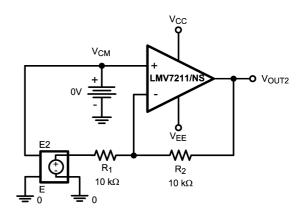

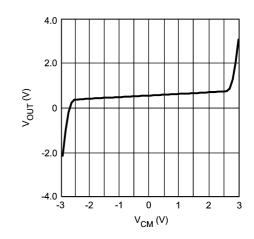

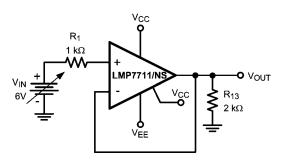

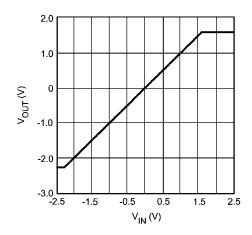

Figure 25 のテスト回路は、電圧制御型電圧源を使用しています。Figure 27 に示した 2 つめの回路では、電圧を - 2.5Vから + 2.5Vの範囲でスイープしています。

FIGURE 25. CMVR Test Circuit

FIGURE 26. Simulated CMVR

FIGURE 27. CMVR Test Circuit (optional)

FIGURE 28. Simulated CMVR

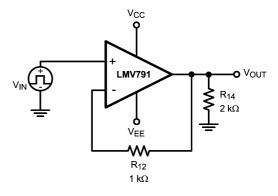

# 位相反転

入力信号が入力コモンモード電圧範囲を超えると、一部のアンプで位相反転が発生します。位相反転が起こると、出力の極性は反転してオペアンプに障害が及ぶ恐れがあるほか、結果的にシステムの誤動作に至ります。

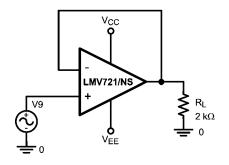

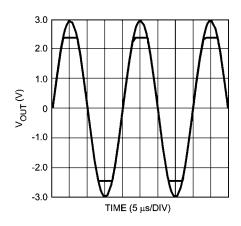

テスト回路は単純な電圧フォロワーで、アンプのコモンモード電圧範囲を超える正弦波を使います。この例では 6Vです。Figure 30 に示す出力波形から、オペアンプと同等の特性を有するマクロモデルからはいかなる位相反転も発生せず、± 2.5Vでクリッピングされていることがわかります。

FIGURE 29. No Phase Reversal Test Circuit

FIGURE 30. No Phase Reversal

#### まとめ

上述のテスト回路はベンチ上でのデバイス評価を置き換えるものではありません。 どちらかというと、マクロモデル の精度を短時間で評価できる自由度をエンジニアに提供するものです。

最後に、さまざまな示唆を与えてくれたナショナル セミコ ンダクターのアプリケーション・グループや同僚に謝意を 表します。

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

# 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

でしているとれる。 ここで、生命維持装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは 支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与 えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不 具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいい ます。

National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。その他のブランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2009 National Semiconductor Corporation

製品の最新情報については www.national.com をご覧ください。

# ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導電性マットにアースをとったもの等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

#### 2. 温·湿度環境

● 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

#### 4. 機械的衝擊

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

#### 5. 熱衝撃

はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上