## Analog Engineer's Circuit

# アナログ フロント エンド内蔵 ADC のオーバーストレス保護回路

#### Dale Li

| 入力              | ADC 入力      | デジタル出力 ADS7042 |

|-----------------|-------------|----------------|

| VinSEMin = -10V | CH_x = -10V | 8000H          |

| VinSE = 0V      | CH_x = 0V   | 0000H          |

| VinSEMax = +10V | CH_x = +10V | 7FFFH          |

#### 電源

| AVDD | DVDD  | 有効な入力 V <sub>normal</sub> | 過電圧入力 V <sub>stressed</sub> |

|------|-------|---------------------------|-----------------------------|

| 5 V  | 3.3 V | ±10V                      |                             |

#### 設計の説明

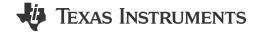

スマートグリッド市場の保護リレー アプリケーションでは、異なる電圧および電流の間で位相情報を維持するため、 ADS8588S などの同時サンプリング ADC が広く使用されています。これらのシステムの動作環境は非常に苛酷であり、 最大で振幅 ±30Vpk (60Vpp) の不要な信号が、信号チェーンに印加されることがあります。このため、過電圧による損傷 から ADC 入力を保護し、同時に良好な性能を維持することが重要です。本書では、過電圧保護の設計方法について解 説し、隣接チャネルの過電圧信号が性能に及ぼす影響についても説明します。最後に、その性能への影響を、テキサ ス・インスツルメンツ製のデバイスと、競合他社製のピン互換デバイスの間で比較します。

### 仕様

| 仕様        | 計算結果         | 測定結果                      |

|-----------|--------------|---------------------------|

| 60Vpp 過電圧 | 最大入力電流 = 1mA | SNR および THD 性能と過電圧フィードスルー |

#### デザイン ノート

1. C<sub>EXT</sub> フィルタ コンデンサには COG タイプのコンデンサを使用します。

2. アンプに対するオーバーストレスに関する理論的な説明については、『電気的オーバーストレス』ビデオシリーズを参照してください。このセクションではアンプについて触れますが、理論はデータコンバータにも同様に適用されます。

#### 部品選定

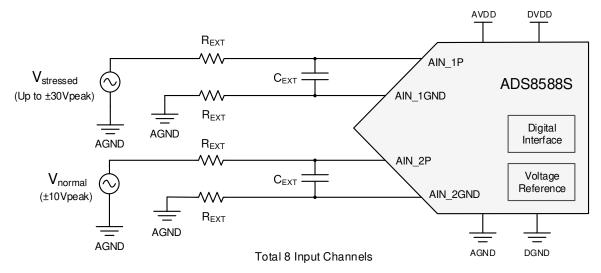

1. 電流を 1mA 未満に制限する R<sub>ext(min)</sub> を求めます。ADS8588S の入力ピンの推奨最大電流は、ADC の内部構造 に基づいて一般に要求される ±10mA です。この 10mA という値は絶対最大定格の制限なので、この値から多少の マージンを設けて、電流を 1mA 未満にすることを推奨します。この設計例の場合、最小外部抵抗は 15kΩ です。

2. 入力フィルタの帯域幅を目的の周波数に設定するために  $R_{ext}$  または  $C_{ext}$  を選択します。アプリケーションによっては、別のカットオフ周波数が必要になります。この場合、50Hz 信号の 128 次高調波を通過させるため、カットオフ周波数を 6.4kHz にする必要があります。この場合、1nF のコンデンサも必要です。1nF は産業用入力フィルタ コンデンサの一般的な容量値です。この式を適用すると、外部抵抗  $(R_{ext})$  の値は 24.9k $\Omega$  と決定されます。この手順で計算される外部抵抗は、手順 1 で求めた最小抵抗値より大きいことに注意します  $(R_{ext} > R_{ext(min)})$ 。

$$R_{EXT} = \frac{1}{2\pi \cdot f_c \cdot C_{EXT}} = \frac{1}{2\pi (6.4kHz)(1nF)} = 24.9k\Omega$$

#### テスト構成

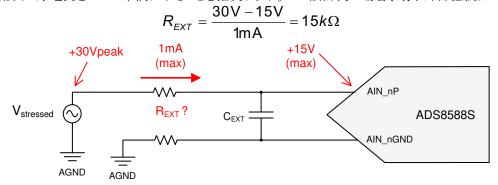

複数チャネル デバイスを使った現実のアプリケーションでは、1 つのチャネルに過電圧信号が印加され、別のチャネルには有効な信号が送られることがあります。この場合、過電圧信号が印加されるチャネルを損傷から保護すると同時に、有効な信号が入力されるチャネルで良好な性能を維持することが求められます。本書の測定はすべて、チャネル 1 に過電圧信号が印加され、その他のチャネルに有効な信号が印加された状態で行われています。すべての入力は、「部品選定」で設計した回路を使用して保護されています。下図に、テストのセットアップを示します。

Signal Generator for AC Test Signal

ADS8588SEVM with PHI controller

### デバイスの保護

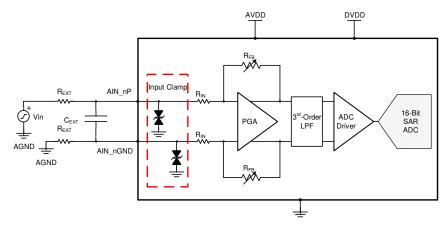

下図に、ADS8588S 内の各アナログ入力チャネルの概略回路図を示します。8 つのアナログ入力チャネルには、それぞれ内部クランプ保護回路が設計されており、各アナログ入力は最大電圧 ±15V までスイングできます。±15V を超える入力電圧の場合、内部の入力クランプ回路がオンになります。過電圧信号がさらに増大すると、保護回路に流れ込む電流が増大します(『ADS8588S 16 ビット、高速、8 チャネル同時サンプリング ADC、単一電源によるバイポーラ入力』データ

シートにある、入力クランプ保護回路の I-V 曲線を参照)。入力電流が大きくなると、破壊的になり、ADC デバイスが劣化 または損傷することがあります。これが、電流を 1mA 未満に制限する理由です (「部品選定」セクションを参照)。フォルト イベントが発生した場合、クランプ保護回路がオンになり、入力電圧を約 15V に制限して、電流を 1mA 未満に制限しま す。

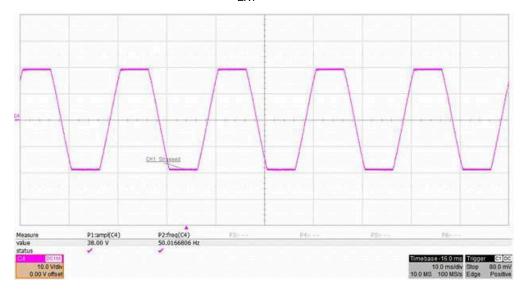

### 過電圧条件での ADC 入力 (AIN\_P)

下図に、±30Vpeak 過電圧信号が印加されたときの ADC 入力電圧を示します。クランプがオンになり、ADC 入力が ±15Vpeak に制限されることに注意します。外部抵抗 R<sub>FXT</sub> は電流を 1mA 未満に制限し、ADC を損傷から保護します。

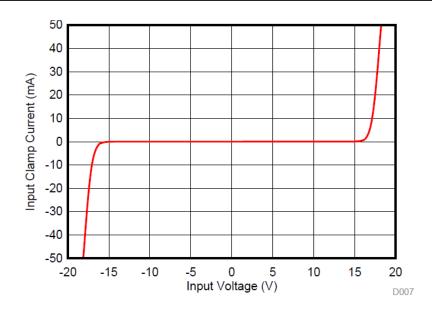

### 内部入力クランプ保護回路の I-V 曲線

下図に、内部クランプの V-I 曲線を示します。入力電圧が ±15V の範囲内である場合、クランプがオフに維持され、リーク 電流がごくわずかであることに注意します。 電圧が ±15V の範囲外になったとき、クランプがオンになり、電圧を制限しま す。

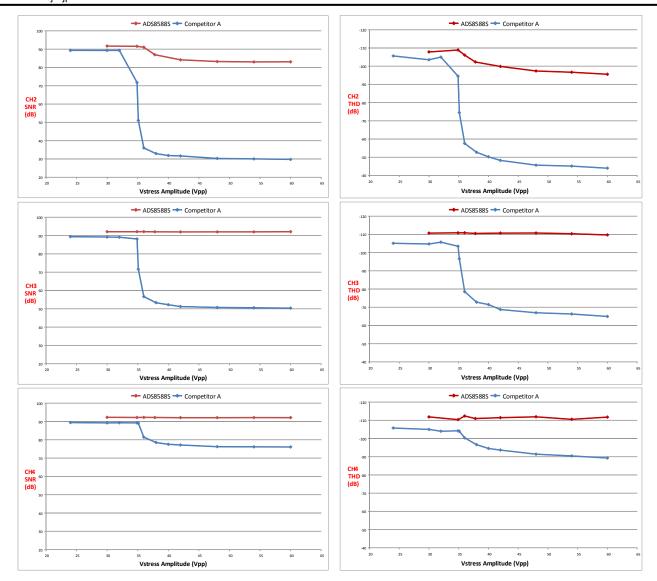

### SNR と THD (チャネル 1 = 過電圧)

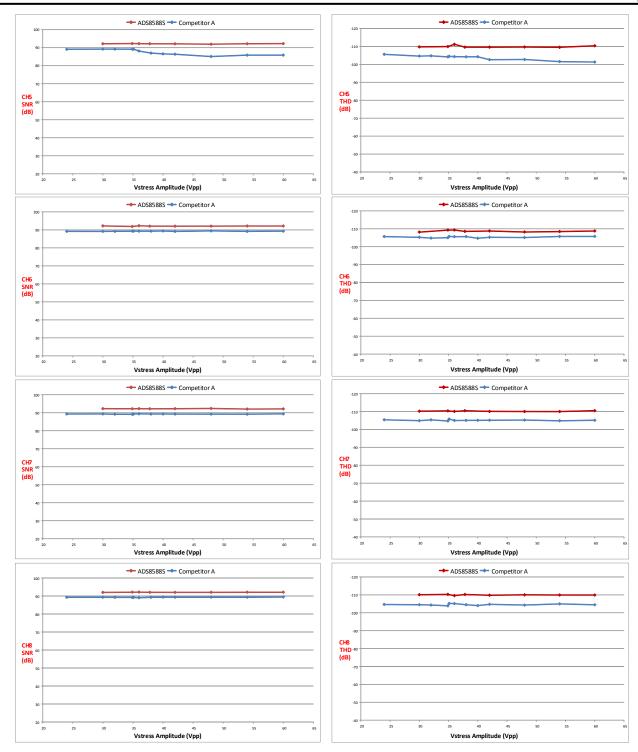

下図は、±30Vpeak (60Vpp) の電気的過大ストレス信号をチャネル 1 に印加し、その他のチャネルを有効な入力信号 (1kHz、-0.5dBFS の正弦波) に接続している状態で測定しました。チャネル 1 に過電圧信号を印加している状態で、有効な入力信号のチャネルの SNR と THD を測定しています。このテストは、ADS8588S とともに、競合他社製のピン互換デバイスについても行っています。ADS8588S の SNR と THD はフォルト信号の影響を受けないか、または影響が最小限であることに注意します。これに対して、競合他社製のデバイスでは、SNR と THD の性能がフォルト信号の影響を大きく受けています。±15Vpeak、±18Vpeak、±21Vpeak、±24Vpeak、±27Vpeak の信号でもこの回路をテストしました。予想どおり、より大きな過大ストレス信号で最悪の結果が得られます。

±30Vpeak (60Vpp) フォルト信号をチャネル 1 に印加し、その他のチャネルに有効な入力信号を印加した場合の SNR および THD 測定による性能検証について引き続き解説します。

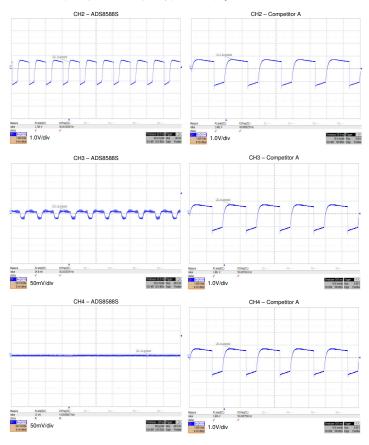

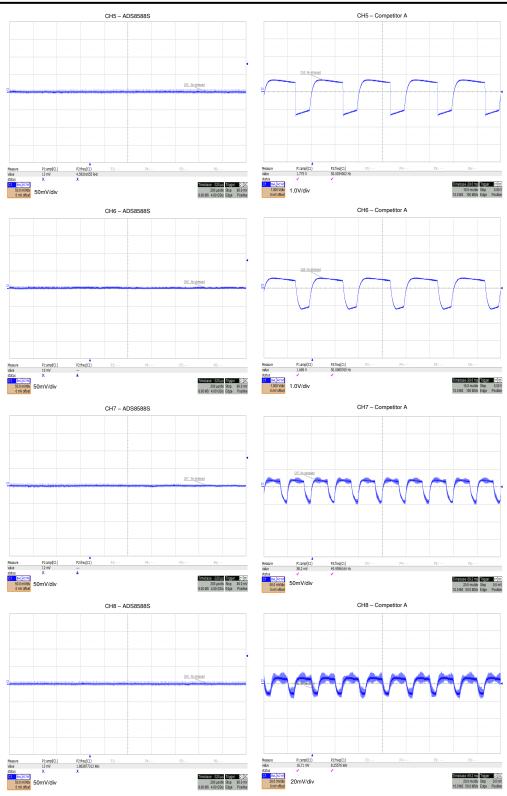

### その他のチャネルへのフォルト信号のフィードスルー

下図は、±30Vpeak (60Vpp) の電気的過大ストレス信号をチャネル 1 に印加し、その他のチャネルをフローティング状態 にして測定しました。フローティングのチャネルへの過電圧信号のフィードスルーは、オシロスコープで測定します。チャネ ル 2 については、ADS8588S と競合他社製デバイスは同様であることに注意します。 その他のチャネル (CH3~CH8) では、ADS8588S のフィードスルーは競合他社製デバイスよりもはるかに小さいです。この結果は、ADS8588S の場合、 システムの任意のチャネルに過電圧フォルトが発生しても、有効な入力信号を印加しているチャネルの動作は大きな影響 を受けないことをはっきりと示しています。一方、競合他社製デバイスの場合、すべてのチャネルがフォルトによって悪影 響を受けています。 ±15Vpeak、±18Vpeak、±21Vpeak、±24Vpeak、±27Vpeak の信号でもこの回路をテストしました。 予想どおり、より大きな過大ストレス信号で最悪の結果が得られます。

以下は、有効な入力信号を印加している ADS8588S のチャネルがフォルト チャネルの影響を受けないことを示すフィー ドスルーテストの続きです。

### 使用デバイス

| デバイス     | 主な特長                | リンク                                              | 他の使用可能デバイス   |  |  |

|----------|---------------------|--------------------------------------------------|--------------|--|--|

| ADS8588S |                     | 単一電源でバイポーラ入力に対応する 8 チャネル同時サンプリングの高速 16 ビット ADC   | 高精度 ADC      |  |  |

| REF5025  | 低ノイズ、低ドリフト、高精度の基準電圧 | 2.5V、3μVpp/V のノイズ、3ppm/°C のドリフト、高精度、シリーズ電圧リファレンス | シリーズ電圧リファレンス |  |  |

### 設計の参照資料

テキサス・インスツルメンツ、『統合アナログ フロントエンド (AFE) のゲインおよびドリフト誤差に対する外部 RC フィルタ回路の影響を低減:±10V』、アナログエンジニア向け回路

テキサス・インスツルメンツ、『統合アナログ フロントエンド (AFE) SAR ADC の入力電圧範囲を拡大する回路』、アナログエンジニア向け回路

### 商標

すべての商標は、それぞれの所有者に帰属します。

### 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated

### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated