🕳 Order

Now

#### UCC28064A

JAJSFJ9B-DECEMBER 2017-REVISED OCTOBER 2019

# UCC28064A 軽負荷時効率に優れた Natural Interleaving™遷移モードPFCコントローラ

# 1 特長

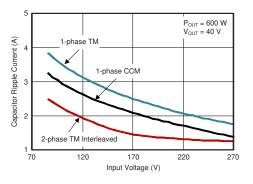

- 入力フィルタおよび出力コンデンサのリップル電流を低減

- 電流リップルの低減によるシステムの信頼性向上と バルク・コンデンサの小型化

- EMI フィルタの小型化

- 高い軽負荷効率

Texas

INSTRUMENTS

- 入力電圧補償による調整可能な位相管理

- 可変バースト・スレッショルドによるバースト・モード 動作

- EUP Lot6 Tier II、CoC Tier II および DOE Level VI 規格への準拠を支援

- センサレス電流波形整形によるボード・レイアウトの簡素化と効率の向上

- 入力ライン・フィード・フォワードにより高速な ライン過渡応答を実現

- 突入電流制限

- 突入電流時の MOSFET 導通を防止

- 出力整流器の CCM 動作および逆方向回復動作 を解消

- 動作温度範囲:-40℃~+125℃ (16ピン SOIC パッケージ)

- WEBENCH<sup>®</sup> Power Designerにより、 UCC28064Aを使用するカスタム設計を作成

# 2 アプリケーション

- HD、U-HD、およびLEDテレビ

- オールインワン PC

- ゲーム機

- アダプタ

- ホーム・オーディオ・システム

# 3 概要

UCC28064AインターリーブPFCコントローラの定格電力 は従来より高くなっています。このデバイスはNatural Interleaving™手法を採用しており、2つのチャネルが同 ー周波数に同期したマスタとして動作します(スレーブ・ チャネルなし)。この手法により応答の高速化、位相間の 優れたオン時間マッチング、各チャネルの遷移モードでの 動作が可能になります。またバースト・モード機能を搭載し ているため、軽負荷時に高い効率を実現できます。バース ト・モードでは、軽負荷動作時もPFCをオフにすることな く、スタンバイ消費電力の目標値を達成できます。この バースト・モードにより、UCC25630x LLCコントローラおよ びUCC24624同期整流コントローラと組み合わせる場合 に、補助フライバック・コンバータが不要となります。

製品情報<sup>(1)</sup>

|           | 344 66 112 114 |               |

|-----------|----------------|---------------|

| 型番        | パッケージ          | 本体サイズ(公称)     |

| UCC28064A | SOIC (16)      | 9.90mm×3.91mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

| 特長   | :                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------|

| アプ   | リケーション1                                                                                                        |

| 概要   | ·                                                                                                              |

| 改訂   | 履歴2                                                                                                            |

| 概要   | i(続き)3                                                                                                         |

| Pin  | Configuration and Functions 3                                                                                  |

| Spe  | cifications 4                                                                                                  |

| 7.1  | Absolute Maximum Ratings 4                                                                                     |

| 7.2  | ESD Ratings 4                                                                                                  |

| 7.3  | Recommended Operating Conditions 5                                                                             |

| 7.4  | Thermal Information 5                                                                                          |

| 7.5  | Electrical Characteristics 5                                                                                   |

| 7.6  | Typical Characteristics 9                                                                                      |

| Deta | ailed Description 13                                                                                           |

| 8.1  | Overview 13                                                                                                    |

| 8.2  | Functional Block Diagram 14                                                                                    |

| 8.3  | Feature Description 15                                                                                         |

| 8.4  | Device Functional Modes                                                                                        |

|      | ア概改概<br><b>Pin</b><br><b>Spe</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br><b>Deta</b><br>8.1<br>8.2<br>8.3 |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

## Revision A (October 2018) から Revision B に変更

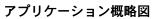

| • | アプリケーション概略図を | 変更 | 1 |

|---|--------------|----|---|

| 9  | Appl | ication and Implementation | 37   |

|----|------|----------------------------|------|

|    | 9.1  | Application Information    | 37   |

|    |      | Typical Application        |      |

| 10 | Pow  | er Supply Recommendations  | . 45 |

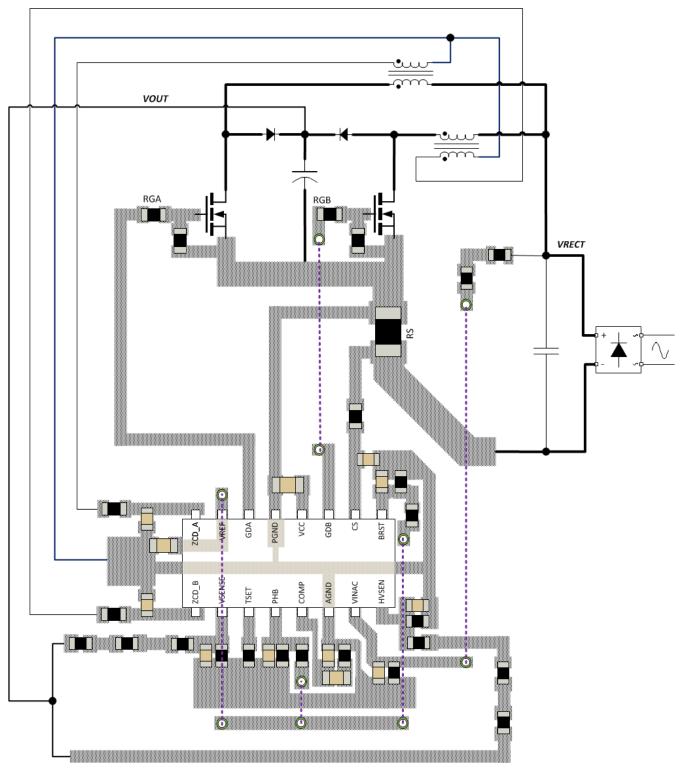

| 11 | Layo | put                        | . 46 |

|    |      | Layout Guidelines          |      |

|    |      | Layout Example             |      |

|    |      | Package Option Addendum    |      |

| 12 | デバ   | イスおよびドキュメントのサポート           | . 49 |

|    | 12.1 | デバイス・サポート                  | 49   |

|    | 12.2 | ドキュメントのサポート                | 49   |

|    | 12.3 | ドキュメントの更新通知を受け取る方法         | 49   |

|    | 12.4 | コミュニティ・リソース                | 49   |

|    | 12.5 | 商標                         | 49   |

|    | 12.6 | 静電気放電に関する注意事項              | 49   |

|    | 12.7 | Glossary                   | 49   |

| 13 | メカニ  | ニカル、パッケージ、および注文情報          |      |

www.tij.co.jp

Page

# 5 概要(続き)

システム・レベルの拡張保護機能には、入力ブラウンアウトおよびドロップアウト回復、出力過電圧、開ループ、過負荷、ソフトスタート、位相障害検出、サーマル・シャットダウンがあります。さらにフェイルセーフ過電圧保護(OVP)機能により、検出されなければ壊滅的なデバイス破壊につながりかねない中間電圧への短絡を防止します。高度な非線形ゲインにより、ライン/負荷過渡事象に対して迅速かつスムーズな応答を実現し、専用のライン・ドロップアウト処理により、重大な電流崩壊を回避できます。また、バースト・モード動作中にスイッチングしない場合にはバイアス電流を大幅に低減できるため、スタンバイ性能が向上します。

# 6 Pin Configuration and Functions

|          | 16-Piı | ckage<br>n SOIC<br>View |         |

|----------|--------|-------------------------|---------|

| ZCD_B 🖂  | 1      | 16                      | TTZCD_A |

| VSENSE 🗖 | 2      | 15                      |         |

| TSET 🗔   | 3      | 14                      | □□GDA   |

| РНВ 🗔    | 4      | 13                      | D PGND  |

| СОМР 🖂   | 5      | 12                      | ⊥⊥vcc   |

| AGND 🖂   | 6      | 11                      | GDB     |

| VINAC 🖂  | 7      | 10                      | ⊐cs     |

| HVSEN 🗔  | 8      | 9                       | ⊐ BRST  |

#### **Pin Functions**

| Р      | IN  | 1/0 | DESCRIPTION                            |

|--------|-----|-----|----------------------------------------|

| NAME   | NO. | 1/0 | DESCRIPTION                            |

| AGND   | 6   | -   | Analog ground                          |

| BRST   | 9   | I   | Burst mode threshold input             |

| COMP   | 5   | 0   | Error amplifier output                 |

| CS     | 10  | I   | Current sense input                    |

| GDA    | 14  | 0   | Phase A gate driver output             |

| GDB    | 11  | 0   | Phase B gate driver output             |

| HVSEN  | 8   | I   | High voltage output sense              |

| PGND   | 13  | -   | Power ground                           |

| PHB    | 4   | I   | Phase B enable disable threshold input |

| TSET   | 3   | I   | Timing set                             |

| VCC    | 12  | -   | Bias supply input                      |

| VINAC  | 7   | I   | Input AC voltage sense                 |

| VSENSE | 2   | I   | Error amplifier input                  |

| VREF   | 15  | 0   | Voltage reference output               |

| ZCDA   | 16  | I   | Phase A zero current detection input   |

| ZCDB   | 1   | I   | Phase B zero current detection input   |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

All voltages are with respect to GND,  $-40^{\circ}C < T_J = T_A < 125^{\circ}C$ , currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                  |                              |                                                                                                             | MIN  | MAX       | UNIT |

|------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|------|-----------|------|

|                  | VCC <sup>(1)</sup>           | -0.5                                                                                                        | 21   |           |      |

|                  |                              | COMP <sup>(2)</sup> , PHB, HVSEN <sup>(3)</sup> , VINAC <sup>(3)</sup> , VSENSE <sup>(3)</sup> , TSET, BRST | -0.5 | 7         |      |

|                  | Continuous input voltage     | ZCDA, ZCDB                                                                                                  | -0.5 | 4         | V    |

|                  |                              | CS <sup>(4)</sup>                                                                                           | -0.5 | 3         |      |

|                  |                              | GDA, GDB <sup>(5)</sup>                                                                                     | -0.5 | VCC + 0.3 |      |

|                  | Continuous input current     | VCC                                                                                                         |      | 20        |      |

|                  |                              | ZCDA, ZCDB                                                                                                  |      | ±5        | mA   |

|                  |                              | GDA, GDB <sup>(5)</sup>                                                                                     | -25  | 25        |      |

|                  |                              | VREF                                                                                                        | -2   |           |      |

|                  | Peak input current           | CS                                                                                                          | -30  |           | mA   |

| TJ               | Operating junction temperatu | ire                                                                                                         | -40  | 125       | °C   |

| T <sub>SOL</sub> | Soldering 10 s               |                                                                                                             |      | 260       | °C   |

| T <sub>stg</sub> | Storage temperature          |                                                                                                             | -65  | 150       | °C   |

(1) Voltage on VCC is internally clamped. VCC may exceed the continuous absolute maximum input voltage rating if the source is current limited below the absolute maximum continuous VCC input current level.

(2) In normal use, COMP is connected to capacitors and resistors and is internally limited in voltage swing.

(3) In normal use, VINAC, VSENSE, and HVSEN are connected to high-value resistors and are internally limited in negative-voltage swing. Although not recommended for extended use, VINAC, VSENSE, and HVSEN can survive input currents as high as -10mA from negative voltage sources, and input currents as high as +0.5mA from positive voltage sources.

(4) In normal use, CS is connected to a series resistor to limit peak input current during brief system line-inrush conditions. In these situations, negative voltage on CS may exceed the continuous absolute maximum rating.

(5) No GDA or GDB current limiting is required when driving a power MOSFET gate. However, a small series resistor may be required to damp resonant ringing due to stray inductance.

## 7.2 ESD Ratings

|                   |                           |                                                                                       | VALUE | UNIT |

|-------------------|---------------------------|---------------------------------------------------------------------------------------|-------|------|

|                   |                           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2000 |      |

| V <sub>(ESD</sub> | ) Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

All voltages are with respect to GND,  $-40^{\circ}C < T_J = T_A < 125^{\circ}C$ , currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                                | MIN  | MAX                      | UNIT |

|------------------------------------------------|------|--------------------------|------|

| VCC input voltage from a low-impedance source  | 14   | 21                       | V    |

| VCC input current from a high-impedance source | 8    | 18                       | mA   |

| VINAC input voltage                            | 0    | 6                        | V    |

| VREF load current                              | 0    | -2                       | mA   |

| ZCDA, ZCDB series resistor                     | 20   | 80                       | kΩ   |

| TSET resistor to program PWM on-time           | 66.5 | 400                      | kΩ   |

| HVSEN input voltage                            | 0.8  | 4.5                      | V    |

| PHB Phase management threshold voltage         | 0    | 2                        | V    |

| BRST Burst mode threshold voltage              | 0    | V <sub>PHB</sub> - 0.6 V | V    |

## 7.4 Thermal Information

|                       |                                                             | UCC28064A |      |

|-----------------------|-------------------------------------------------------------|-----------|------|

|                       | THERMAL METRIC                                              | SOIC (D)  | UNIT |

|                       |                                                             | 16 PINS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance <sup>(1)</sup>       | 91.6      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance <sup>(2)</sup>    | 52.1      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance <sup>(3)</sup>         | 48.6      | °C/W |

| τιΨ                   | Junction-to-top characterization parameter <sup>(4)</sup>   | 14.9      | °C/W |

| Ψјв                   | Junction-to-board characterization parameter <sup>(5)</sup> | 48.3      | °C/W |

(1) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(2) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(4) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining R<sub>0JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

(5) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

## 7.5 Electrical Characteristics

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 0V, BRST = 0V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded,  $-40^{\circ}$ C <  $T_{J}$  =  $T_{A}$  < 125°C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                         | PARAMETER                           | TEST CONDITIONS                        | MIN  | TYP   | MAX  | UNIT |

|-------------------------|-------------------------------------|----------------------------------------|------|-------|------|------|

| VCC BIAS SU             | PPLY                                |                                        |      |       |      |      |

| VCC <sub>SHUNT</sub>    | VCC shunt voltage <sup>(1)</sup>    | $I_{VCC} = 10 \text{ mA}$              | 22   | 24    | 26   | V    |

| I <sub>VCC(UVLO)</sub>  | VCC current, UVLO                   | VCC = 9.3 V prior to turn on           |      | 125   | 200  | μA   |

| I <sub>VCC(stby)</sub>  | VCC current, disabled               | VSENSE = 0 V                           |      | 150   | 210  | μA   |

| I <sub>VCC(on)</sub>    | VCC current, enabled                | VSENSE = 2 V                           |      | 5     | 8    | mA   |

| I <sub>VCC(BURST)</sub> | VCC current burst mode no switching | V <sub>COMP</sub> < V <sub>BURST</sub> |      | 650   | 850  | μA   |

| UNDERVOLT               | AGE LOCKOUT (UVLO)                  |                                        |      |       | Ľ    |      |

| VCC <sub>ON</sub>       | VCC turnon threshold                | VCC rising                             | 9.45 | 10.35 | 11.1 | V    |

| VCC <sub>OFF</sub>      | VCC turnoff threshold               | VCC falling                            | 8.8  | 9.6   | 10.7 | V    |

| $\Delta VCC_{UVLO}$     | UVLO Hysteresis                     | VCC <sub>ON</sub> - VCC <sub>OFF</sub> | 0.68 | 0.8   | 0.9  | V    |

| REFERENCE               |                                     | · ·                                    |      |       |      |      |

(1) Excessive VCC input voltage and current will damage the device. This clamp will not protect the device from an unregulated bias supply. If an unregulated bias supply is used, a series-connected Fixed Positive-Voltage Regulator such as the UA78L15A is recommended. See the Absolute Maximum Ratings table for the limits on VCC voltage, current, and junction temperature.

# **Electrical Characteristics (continued)**

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 0V, BRST = 0V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded,  $-40^{\circ}$ C <  $T_{J}$  =  $T_{A}$  < 125°C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                   | PARAMETER                                                                   | TEST CONDITIONS                                           | MIN   | TYP   | MAX   | UNIT |

|-----------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|-------|-------|-------|------|

| V <sub>REF</sub>                  | VREF output voltage, no load                                                | I <sub>VREF</sub> = 0 mA                                  | 5.82  | 6.00  | 6.18  | V    |

| ∆V <sub>REF_LOAD</sub>            | VREF change with load                                                       | $0 \text{ mA} \le I_{VREF} \le -2 \text{ mA}$             | -6    | -1    |       | mV   |

| VREF_VCC                          | VREF change with VCC                                                        | $12 \text{ V} \leq \text{VCC} \leq 20 \text{ V}$          |       | 2     | 10    | mV   |

| ERROR AMPLI                       | FIER                                                                        |                                                           |       |       |       |      |

| VSENSEreg25                       | VSENSE input regulation voltage                                             | $T_A = 25^{\circ}C$                                       | 5.85  | 6     | 6.15  | V    |

| VSENSEreg                         | VSENSE input regulation voltage                                             |                                                           | 5.82  | 6     | 6.18  | V    |

| VSENSE                            | VSENSE input bias current                                                   | In regulation                                             | 50    | 100   | 150   | nA   |

| V <sub>ENAB</sub>                 | VSENSE enable threshold, rising                                             |                                                           | 1.15  | 1.25  | 1.35  | V    |

|                                   | VSENSE enable hysteresis                                                    |                                                           | 0.02  | 0.07  | 0.15  | V    |

| COMP_CLMP                         | COMP high voltage, clamped                                                  | VSENSE = VSENSEreg - 0.3 V                                | 4.70  | 4.95  | 5.10  | V    |

| V <sub>COMP_SAT</sub>             | COMP low voltage, saturated                                                 | VSENSE = VSENSEreg + 0.3 V                                |       | 0.03  | 0.125 | V    |

| 9m1                               | VSENSE to COMP<br>transconductance, small signal                            | 0.99(VSENSEreg) < VSENSE <<br>1.01(VSENSEreg), COMP = 3 V | 40    | 55    | 70    | μS   |

| V <sub>SENSE_gM2_SIN</sub>        | VSENSE high-going threshold<br>to enable COMP large signal<br>gain, percent | Relative to VSENSEreg, COMP = 3 V                         | 3.25  | 5     | 6.75  | %    |

| V <sub>SENSE_gM2_SO</sub><br>JRCE | VSENSE low-going threshold to<br>enable COMP large signal gain,<br>percent  | Relative to VSENSEreg, COMP = 3 V                         | -6.75 | -5    | -3.25 | %    |

| 9m2_source                        | VSENSE to COMP<br>transconductance, large signal                            | VSENSE = VSENSEreg - 0.4 V , COMP = 3 V                   | 210   | 290   | 370   | μS   |

| 9m2_sink                          | VSENSE to COMP<br>transconductance, large signal                            | VSENSE = VSENSEreg + 0.4 V, COMP =<br>3 V                 | 210   | 290   | 370   | μS   |

| COMP_SOURCE_                      | COMP maximum source current                                                 | VSENSE = 5 V, COMP = 3 V                                  | -170  | -125  | -80   | μA   |

| R <sub>COMPDCHG</sub>             | COMP discharge resistance                                                   | HVSEN = 5.2 V, COMP = 3 V                                 | 1.6   | 2     | 2.4   | kΩ   |

| DODCHG                            | COMP discharge current during<br>Dropout                                    | VSENSE = 5 V, VINAC = 0.3 V, COMP =<br>1V                 | 3.2   | 4     | 4.8   | μA   |

| V <sub>LOW_OV</sub>               | VSENSE overvoltage threshold, rising                                        | Relative to VSENSEreg                                     | 6.5   | 8     | 9.5   | %    |

| ΔV <sub>LOW_OV_HYS</sub><br>Γ     | VSENSE overvoltage hysteresis                                               | Relative to V <sub>LOW_OV</sub>                           | -3    | -2    | -1.5  | %    |

| V <sub>HIGH_OV</sub>              | VSENSE 2nd overvoltage threshold, rising                                    | Relative to VSENSEreg                                     | 9.3   | 11    | 12.7  | %    |

| SOFT START                        | Γ                                                                           |                                                           |       |       |       |      |

| V <sub>SSTHR</sub>                | COMP Soft-Start threshold, falling                                          | VSENSE = 1.5 V                                            | 10    | 23    | 35    | mV   |

| SS,FAST                           | COMP Soft-Start current, fast                                               | SS-state, V <sub>ENAB</sub> < VSENSE < VREF/2             | -170  | -125  | -80   | μA   |

| SS,SLOW                           | COMP Soft-Start current, slow                                               | SS-state, VREF/2 < VSENSE < 0.88VREF                      | -20   | -16   | -11.5 | μA   |

| < <sub>EOSS</sub>                 | VSENSE End-of-Soft-Start<br>threshold factor                                | Percent of VSENSEreg                                      | 96.5% | 98.3% | 99.8% |      |

| OUTPUT MONI                       | TORING                                                                      |                                                           |       |       |       |      |

| V <sub>HV_OV_FLT</sub>            | HVSEN threshold to<br>overvoltage fault                                     | HVSEN rising                                              | 4.64  | 4.87  | 5.1   | V    |

| V <sub>HV_OV_CLR</sub>            | HVSEN threshold to<br>overvoltage clear                                     | HVSEN falling                                             | 4.45  | 4.67  | 4.8   | V    |

| GATE DRIVE                        | •                                                                           | · I                                                       |       |       | 1     |      |

## **Electrical Characteristics (continued)**

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 0V, BRST = 0V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded,  $-40^{\circ}$ C <  $T_{J}$  =  $T_{A}$  < 125°C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                          | PARAMETER                                       | TEST CONDITIONS                                                                            | MIN    | TYP    | MAX    | UNIT |

|--------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------|--------|--------|--------|------|

| V <sub>GDx_H</sub>       | GDA, GDB output voltage, high                   | $I_{GDA}, I_{GDB} = -100 \text{ mA}$                                                       | 10.7   | 12.4   | 15     | V    |

| R <sub>GDx_H</sub>       | GDA, GDB on-resistance, high                    | $I_{GDA}$ , $I_{GDB} = -100 \text{ mA}$                                                    |        | 8.8    | 16.7   | Ω    |

| V <sub>GDx_L</sub>       | GDA, GDB output voltage, low                    | $I_{GDA}$ , $I_{GDB} = 100 \text{ mA}$                                                     |        | 0.18   | 0.32   | V    |

| R <sub>GDx_L</sub>       | GDA, GDB on-resistance, low                     | $I_{GDA}$ , $I_{GDB} = 100 \text{ mA}$                                                     |        | 2      | 3.2    | Ω    |

| V <sub>GDx_H_VCCH</sub>  | GDA, GDB output voltage high, clamped           | VCC = 20 V, $I_{GDA}$ , $I_{GDB}$ = -5 mA                                                  | 11.8   | 13.5   | 15     | V    |

| V <sub>GDx_H_VCCL</sub>  | GDA, GDB output voltage high,<br>low VCC        | VCC = 12 V, $I_{GDA}$ , $I_{GDB}$ = -5 mA                                                  | 10     | 10.5   | 11.5   | V    |

| V <sub>GDx_L_UVLO</sub>  | GDA, GDB output voltage,<br>UVLO                | VCC = 3.0 V, I <sub>GDA</sub> , I <sub>GDB</sub> = 2.5 mA                                  |        | 100    | 200    | mV   |

| t <sub>GDx_RISE</sub>    | Rise time                                       | 1 V to 9 V, C <sub>LOAD</sub> = 1 nF                                                       |        | 18     | 30     | ns   |

| t <sub>GDx_FALL</sub>    | Fall time                                       | 9 V to 1 V, C <sub>LOAD</sub> = 1 nF                                                       |        | 12     | 25     | ns   |

| ZERO CURRE               | NT DETECTOR                                     | •                                                                                          |        |        |        |      |

| V <sub>ZCDx_TRIG</sub>   | ZCDA, ZCDB voltage threshold, falling           |                                                                                            | 0.8    | 1      | 1.2    | V    |

| V <sub>ZCDx_ARM</sub>    | ZCDA, ZCDB voltage threshold, rising            |                                                                                            | 1.5    | 1.7    | 1.9    | V    |

| V <sub>ZCDx_CLMP_H</sub> | ZCDA, ZCDB clamp, high                          | $I_{ZCDA} = +2 \text{ mA}, I_{ZCDB} = +2 \text{ mA}$                                       | 2.6    | 3      | 3.4    | V    |

| V <sub>ZCDx_CLMP_L</sub> | ZCDA, ZCDB clamp, low                           | $I_{ZCDA} = -2 \text{ mA}, I_{ZCDB} = -2 \text{ mA}$                                       | -0.40  | -0.2   | 0      | V    |

| I <sub>ZCDx</sub>        | ZCDA, ZCDB input bias current                   | ZCDA = 1.4 V, ZCDB = 1.4 V                                                                 | -0.5   | 0      | 0.5    | μA   |

| t <sub>ZCDx_DEL</sub>    | ZCDA, ZCDB delay to GDA, GDB outputs            | From ZCDx input falling to 1 V to respective gate drive output rising 10%                  |        | 50     | 100    | ns   |

| t <sub>ZCDx_BLNK</sub>   | ZCDA, ZCDB blanking time                        | From GDx rising to GDx falling                                                             |        | 100    |        | ns   |

| CURRENT SEI              | NSE                                             |                                                                                            |        |        |        |      |

| I <sub>CS</sub>          | CS input bias current, dual-<br>phase           | At rising threshold                                                                        | -200   | -166   | -120   | μA   |

| $V_{CS_DPh}$             | CS current-limit rising threshold, dual-phase   |                                                                                            | -0.22  | -0.2   | -0.18  | V    |

| $V_{CS\_SPh}$            | CS current-limit rising threshold, single-phase | PHB = 6 V                                                                                  | -0.183 | -0.166 | -0.149 | V    |

| V <sub>CS_RST</sub>      | CS current-limit reset falling threshold        |                                                                                            | -0.025 | -0.015 | -0.002 | V    |

| t <sub>CS_DEL</sub>      | CS current-limit response time                  | From CS exceeding threshold-0.05 V to GDx dropping 10%                                     |        | 60     | 100    | ns   |

| t <sub>CS_BLNK</sub>     | CS blanking time                                | From GDx rising and falling edges                                                          |        | 100    |        | ns   |

| VINAC INPUT              |                                                 |                                                                                            |        |        |        |      |

| I <sub>VINAC</sub>       | VINAC input bias current, above brownout        | VINAC = 2 V                                                                                | -0.5   | 0      | 0.5    | μA   |

| V <sub>BOTHR</sub>       | VINAC brownout threshold                        |                                                                                            | 1.33   | 1.45   | 1.6    | V    |

| t <sub>BODLY</sub>       | VINAC brownout filter time                      | VINAC below the brownout threshold for the brownout filter time                            | 500    | 640    | 810    | ms   |

| t <sub>BORST</sub>       | VINAC brownout reset time                       | VINAC above the brownout threshold for<br>the brownout reset time after Brown out<br>event | 300    | 450    | 600    | ms   |

| I <sub>BOHYS</sub>       | VINAC brownout hysteresis current               | VINAC = 1 V for > $t_{BODLY}$                                                              | 1.6    | 1.95   | 2.25   | μΑ   |

| V <sub>DODET</sub>       | VINAC dropout detection threshold               | VINAC falling                                                                              | 0.310  | 0.35   | 0.38   | V    |

| t <sub>DODLY</sub>       | VINAC dropout filter time                       | VINAC below the dropout detection threshold for the dropout filter time                    | 3.5    | 5      | 7      | ms   |

## **Electrical Characteristics (continued)**

At VCC = 16 V, AGND = PGND = 0 V, VINAC = 3 V, VSENSE = 6 V, HVSEN = 3 V, PHB = 0V, BRST = 0V,  $R_{TSET}$  = 133 k $\Omega$ , all voltages are with respect to GND, all outputs unloaded,  $-40^{\circ}$ C <  $T_{J}$  =  $T_{A}$  < 125°C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                   | PARAMETER                                                 | TEST CONDITIONS                                                                                                    | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>DOCLR</sub>                | VINAC dropout clear threshold                             | VINAC rising                                                                                                       | 0.67 | 0.71 | 0.75 | V    |

| PULSE-WIDTH                       | MODULATOR                                                 |                                                                                                                    |      |      |      |      |

| K <sub>TL</sub>                   | On-time factor, two phases operating, low VINAC_PK        | VINAC=1.6V, VCOMP=4V <sup>(2)</sup>                                                                                | 3.0  | 4.15 | 5.3  | µs/V |

| K <sub>TH</sub>                   | On-time factor, two phases operating, high VINAC_PK       | VINAC= 5V, VCOMP = $4V^{(2)}$                                                                                      | 0.36 | 0.43 | 0.5  | µs/V |

| K <sub>TSL</sub>                  | On-time factor, single-phase<br>operating, low VINAC_PK   | VINAC=1.6V, VCOMP = 1.5V, PHB = 2V <sup>(2)</sup>                                                                  | 6.1  | 8.3  | 10.5 | µs/V |

| K <sub>TSH</sub>                  | On-time factor, single-phase<br>operating, high VINAC_PK  | VINAC= 5V, VCOMP = 1.5V, PHB=2V <sup>(2)</sup>                                                                     | 0.73 | 0.87 | 1.01 | μs/V |

| t <sub>zcc_l</sub>                | Zero-crossing distortion correction additional on time    | COMP = 0.5 V, VINAC = 0.1 V                                                                                        | 15   | 23.6 | 32.2 | μs   |

| t <sub>zcc_II</sub>               | Zero-crossing distortion correction additional on time    | COMP = 0.5 V, VINAC = 1.6 V                                                                                        | 0.7  | 1.1  | 1.5  | μs   |

| t <sub>MIN</sub>                  | Minimum Switching period                                  | $ \begin{array}{l} R_{TSET} = 133 \text{ k}\Omega, \text{ VCOMP} = 0.3, \text{ VINAC} = 3 \\ V^{(2)} \end{array} $ | 1.9  | 2.7  | 3.5  | μs   |

| t <sub>START</sub>                | PWM restart time                                          | $ZCDA = ZCDB = 2 V^{(3)}$                                                                                          | 160  | 210  | 265  | μs   |

| t <sub>ONMAX_L</sub>              | Maximum FET on time at low VINAC                          | VSENSE = 5.8 V, VINAC=1.6V                                                                                         | 15.1 | 20.4 | 26.2 | μs   |

| t <sub>ONMAX_H</sub>              | Maximum FET on time at High VINAC                         | VSENSE = 5.8 V, VINAC= 5V                                                                                          | 1.5  | 2    | 2.4  | μs   |

| t <sub>ONMAX_SL</sub>             | Maximum FET on time at low VINAC, Single Phase operation. | VSENSE = 5.8V, VINAC=1.6V, PHB = 6V                                                                                | 11.8 | 16   | 20.2 | μs   |

| t <sub>ONMAX_SH</sub>             | Maximum FET on time at hgih VINAC, single phase operation | VSENSE = 5.8V, VINAC=5 V, PHB = 6V                                                                                 | 1.37 | 1.66 | 1.95 | μs   |

| $\Delta t_{ONMAX\_AB\_L}$         | Phase B to phase A on-time matching error                 | VSENSE = 5.8 V, VINAC=1.6V                                                                                         | -6   |      | 6    | %    |

| $\Delta t_{ONMAX\_AB\_H}$         | Phase B to phase A on-time<br>matching error              | VSENSE = 5.8 V, VINAC= 5V                                                                                          | -6   |      | 6    | %    |

| $\Delta V_{BRST_HYST}$            | BRST Hysteresis, COMP voltage rising                      | BRST = 1V, VINAC = 1.5 V                                                                                           | 30   | 50   | 70   | mV   |

| $\Delta V_{PHB_HYST}$             | PHB Hysteresis COMP voltage rising                        | PHB = 3V, VINAC = 2.5 V                                                                                            | 80   | 150  | 210  | mV   |

| I <sub>PHB_RANGE</sub>            | PHB pin sourced current when<br>high input voltage        | VINAC = 3.75V, PHB = 2V                                                                                            | 2    | 3    | 4.1  | μA   |

| I <sub>BRST_RANGE</sub>           | BRST pin sourced current when high input voltage          | VINAC = 3.75V, BRST = 2V                                                                                           | 2    | 3    | 4.1  | μA   |

| V <sub>VINAC</sub> _<br>RANGE_THF | VINAC range falling threshold                             | PHB = 2V, BRST = 2V                                                                                                | 2.95 | 3.15 | 3.3  | V    |

| $\Delta V_{INAC\_RANGE}$          | VINAC range Hysteresis at<br>rising edge                  | PHB = 2V, BRST=2V                                                                                                  | 300  | 350  | 400  | mV   |

| THERMAL SHU                       | JTDOWN                                                    |                                                                                                                    |      |      |      |      |

| TJ                                | Thermal shutdown temperature                              | Temperature rising <sup>(4)</sup>                                                                                  |      | 160  |      | °C   |

| TJ                                | Thermal restart temperature                               | Temperature falling <sup>(4)</sup>                                                                                 |      | 140  |      | °C   |

(2) Gate drive on-time is proportional to (VCOMP – 0.125 V). The on-time proportionality factor, KT, scales linearly with the value of RTSET and is different in two-phase and single-phase modes. The minimum switching period is proportional to RTSET.

(3) An output on-time is generated at both GDA and GDB if both ZCDA and ZCDB negative-going edges are not detected for the restart time. In single-phase mode, the restart time applies for the ZCDA input and the GDA output.

(4) Thermal shutdown occurs at temperatures higher than the normal operating range. Device performance above the normal operating temperature is not specified or assured.

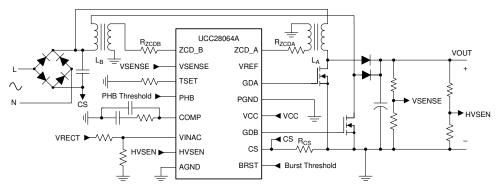

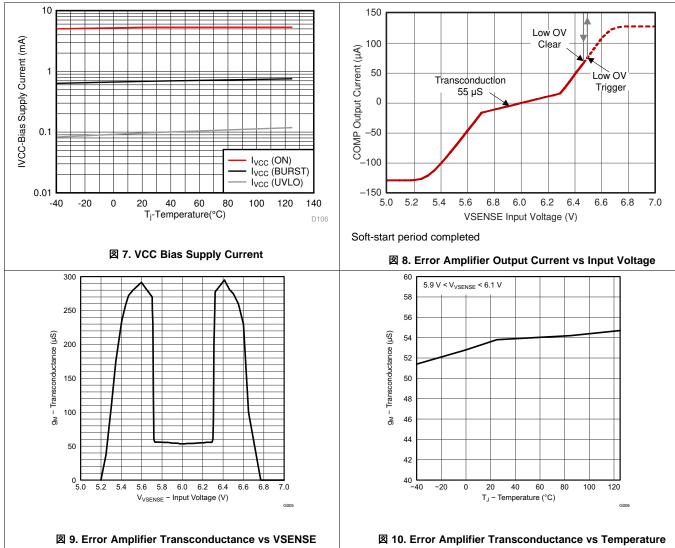

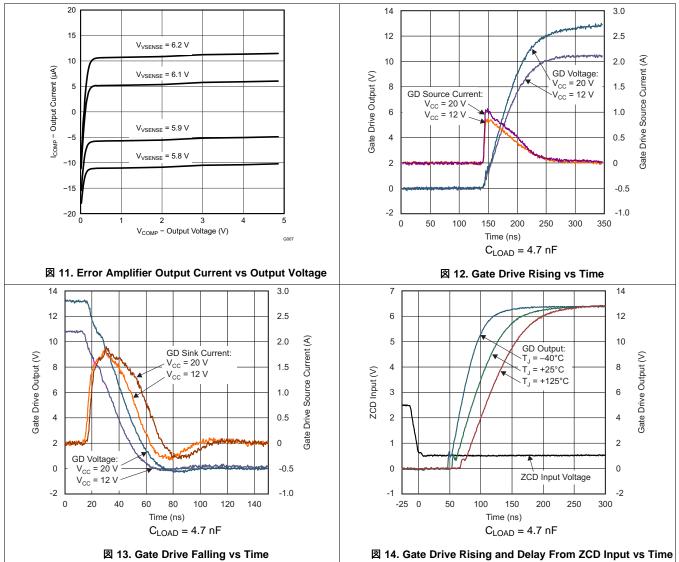

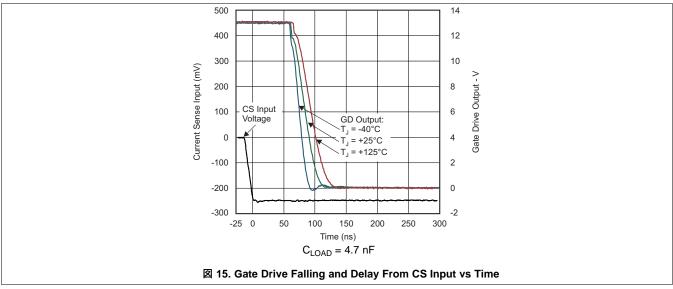

## 7.6 Typical Characteristics

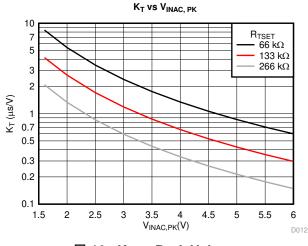

$V_{VCC} = 16 \text{ V}, V_{AGND} = V_{PGND} = 0 \text{ V}, V_{VINAC} = 3 \text{ V}, V_{VSENSE} = 6 \text{ V}, V_{HVSEN} = 3 \text{ V}, V_{PHB} = 0 \text{ V}, R_{TSET} = 133 \text{ k}\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = 25^{\circ}$ C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

Copyright © 2017-2019, Texas Instruments Incorporated

## **Typical Characteristics (continued)**

$V_{VCC}$  = 16 V,  $V_{AGND}$  =  $V_{PGND}$  = 0 V,  $V_{VINAC}$  = 3 V,  $V_{VSENSE}$  = 6 V,  $V_{HVSEN}$  = 3 V,  $V_{PHB}$  = 0 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J$  = 25°C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

## **Typical Characteristics (continued)**

$V_{VCC}$  = 16 V,  $V_{AGND}$  =  $V_{PGND}$  = 0 V,  $V_{VINAC}$  = 3 V,  $V_{VSENSE}$  = 6 V,  $V_{HVSEN}$  = 3 V,  $V_{PHB}$  = 0 V,  $R_{TSET}$  = 133 k $\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J$  = 25°C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

## **Typical Characteristics (continued)**

$V_{VCC} = 16 \text{ V}, V_{AGND} = V_{PGND} = 0 \text{ V}, V_{VINAC} = 3 \text{ V}, V_{VSENSE} = 6 \text{ V}, V_{HVSEN} = 3 \text{ V}, V_{PHB} = 0 \text{ V}, R_{TSET} = 133 \text{ k}\Omega$ ; all voltages are with respect to GND, all outputs unloaded,  $T_J = 25^{\circ}$ C, and currents are positive into and negative out of the specified terminal, unless otherwise noted.

# 8 Detailed Description

# 8.1 Overview

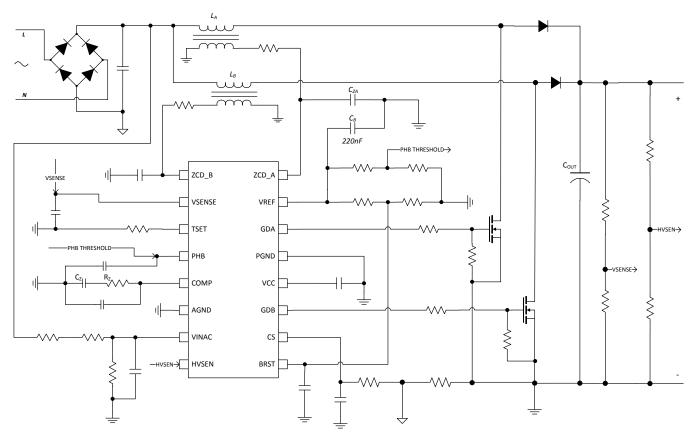

Transition mode (TM) control is a popular choice for the boost power factor correction topology at lower power levels. Some advantages of this control method are its lower complexity in achieving high power factor and because lower cost boost diode with higher reverse recovery current specification may be used. In TM control MOSFET is turned on always when no current is flowing into diode. Interleaved Transition Mode Control retains this benefit and generally extends the applicability up to much higher power levels while simultaneously conferring the interleaving benefits of reduced input and output ripple current and system thermal optimization.

In UCC28064A, burst mode was introduced respect its predecessor (UCC28063) to achieve higher efficiency in light load conditions. Input voltage feed-forward and threshold adjustment is also available to ensure the user can optimize performance across line and load conditions. When operating single phase on time of the switching phase is doubled with the purpose of compensating the missing power from the not switching phase. In this way for the same COMP value the converter should provide the same output power regardless if operating single phase mode or dual phase mode. Unfortunately this is not always the case. Component variations and MOSFETs turn-off delay can lead to big differences (for the same COMP voltage) in the output power delivery. The *Phase Management and Light-Load Operation* section will discuss some ways to deal with the variations.

Line voltage feed-forward compensation provides several benefits: it maintains constant bandwidth of the control loop versus line voltage variation, avoids high current in the MOSFETs, inductors, and line filter when line transitions from low to high happens, and helps to keep simple Phase Management control because the COMP pin voltage is almost proportional to Load. Burst Mode enables high efficiency at light load and soft-on and soft-off in burst mode reduces risk of audible noise. The optimal load current at which the converter should enter burst mode can be different for different input voltages. These thresholds can be customized by the user.

Interleaving control and phase management facilitates high efficiency 80+ and Energy Star designs with reduced input and output ripple. The Natural Interleaving method allows TM operation and achieves 180 degrees between the phases by On-time management. Moreover Natural interleaving method does not rely on tight tolerance requirements on the inductors. Negative current sensing is implemented on the total input current instead of just the MOSFET current which prevents MOSFET switching during inrush surges or in any mode where the inductor current may enter in continuous conduction mode (CCM). This prevents reverse recovery conduction events between the MOSFET and output rectifier.

Independent output voltage sense circuits with their separate fault management behaviors provide a high degree of redundancy against PFC stage over-voltage. Brownout, over voltage protection on HVSEN pin (HVSENSE OV), under voltage lockout (UVLO), and device over-temperature faults will all cause a complete Soft-Start cycle. Other faults such as short duration AC Drop-Out, minor over-voltage or cycle-by-cycle over-current cause a live recovery process to initiate by pulling down the COMP pin or by terminating the pulses early.

The error amplifier transconductance is designed to allow smaller compensation components and optimum transient response for large changes in line or load. The Soft-Start process is carefully optimized. A complete Soft-Start is implemented. It is dependent on the output voltage sense to speed up start-up from low AC line and to minimize the effect of excessive capacitance on the COMP pin during start-up into no-load. If some faults events are triggered COMP pin is fast pulled down to zero. This complete discharge of COMP aids with preventing excessive currents on recovery from an AC Brown-Out event.

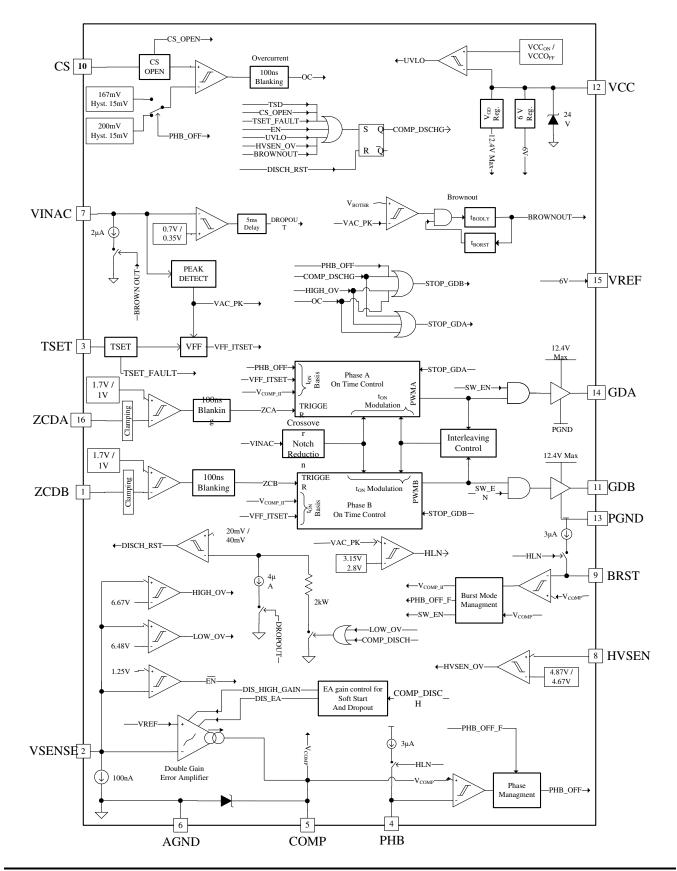

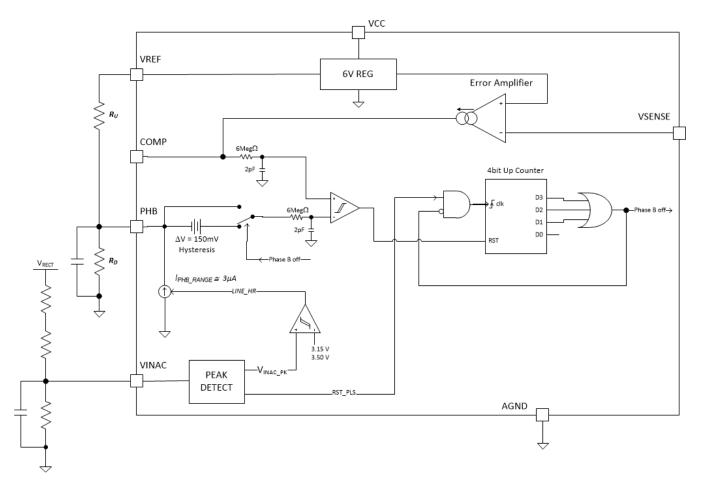

# 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Principles of Operation

The UCC28064A device contains the control circuits for two parallel-connected boost pulse-width modulated (PWM) power converters. The boost PWM power converters ramp current in the boost inductors for a time period proportional to the voltage on the error amplifier output (COMP pin). Each power converter then turns off the power MOSFET until current in the boost inductor decays to zero (as sensed on the zero current detection inputs, ZCDA and ZCDB). After the inductor demagnetizes, the power converter starts another cycle. This cycle process produces a triangular waveform of current, with peak current set by the on-time and the instantaneous power mains input voltage,  $V_{IN}(t)$  value, as shown in  $\vec{\pm}$  1.

$$I_{PEAK} = \frac{V_{IN} \times t_{ON}}{L}$$

(1)

The average line current is exactly equal to half of the peak line current, as shown in  $\pm 2$ .

$$I_{PEAK} = \frac{V_{IN} \times t_{ON}}{2 \times L}$$

(2)

When the  $t_{ON}$  and L values are essentially constant during an AC-line period, the resulting triangular current waveform during each switching cycle has an average value proportional to the instantaneous value of the rectified AC-line voltage. This architecture results in a resistive input impedance characteristic at the line frequency and a near-unity power factor.

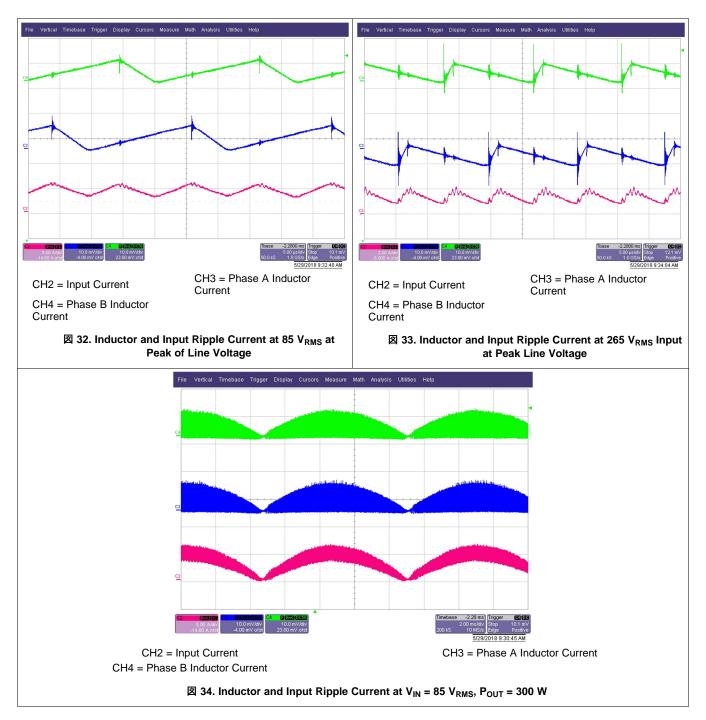

#### 8.3.2 Natural Interleaving

Under normal operating conditions, the UCC28064A device regulates the relative phasing of the channel A and channel B inductor currents to be approximately 180°. This greatly reduces the switching-frequency ripple currents seen at the line-filter and output capacitors, compared to the ripple current of each individual converter. This design allows a reduction in the size and cost of input and output filtering. The phase-control function differentially modulates the on-times of the A and B channels based on their phase and frequency relationship. The Natural Interleaving method allows the converter to achieve 180° phase-shift and transition-mode operation for both phases without tight requirements on boost inductor tolerance.

Ideally, the best current-sharing is achieved when both inductors are exactly the same value. Typically the inductances are not the same, so the current-sharing of the A and B channels is proportional to the inductor tolerance. Also, switching delays and resonances of each channel typically differ slightly, and the controller allows some necessary phase-error deviation from 180° to maintain equal switching frequencies. Optimal phase balance occurs if the individual power stages and the on-times are well matched. Mismatches in inductor values do not affect the phase relationship.

Interleaving may not be ideal under all conditions. In particular a loss of interleaving may be experienced at light loads near the zero crossings. In some cases there may be insufficient current to trigger a large enough signal to trip the zero crossing detectors. In addition the turn off delay in the MOSFET may dominate the overall on-time at very light loads. This creates a very limited ability for the controller to correct for phase errors in the system.

#### Feature Description (continued)

# 8.3.3 On-Time Control, Maximum Frequency Limiting, Restart Timer and Input Voltage Feed-Forward compensation

Gate-drive on-time varies proportionately with the error-amplifier output voltage ( $V_{COMP}$ ) and inversely proportional to the squared value of the peak of the rectified input voltage sensed through VINAC pin as stated by equation (3). In equation (3) it is shown that the on-time is inversely proportionally to the value of resistor  $R_{TSET}$  connected between pin TSET and pin AGND. In order to calculate on-time, Equation (4) can be used. Parameter  $K_T$  is function of the rectified peak input voltage sensed by pin VINAC as reported in graph of 🖾 16. In this graph 3 curves are reported for three different values of  $R_{TSET}$ . Two values of parameter  $K_T$  are reported in the electrical specs table for two values of VINAC:  $K_{TL}$  and  $K_{TH}$  corresponding at the VINAC = 1.6V and VINAC = 5V and  $R_{TSET}$  = 133k $\Omega$ . Because voltage on VINAC is proportional to the line rectified voltage, for  $t_{ON}$  calculation purposes we refer to the peak value of this voltage that is obtained through an internal peak detect.  $K_T$  is inversely proportional to the squared value of VINAC peak value so it is the  $t_{ON}$  time realizing the so called voltage feed-forward compensation. The Voltage Feed-forward function modifies the MOSFET on time according to line voltage so, ideally output power delivered does not change if line voltage changes. When operating in single phase mode  $K_T$  is called  $K_{TS}$  and its value is doubled.

$$t_{\rm ON} = \propto \frac{(V_{\rm COMP} - 125 \text{ mV})}{V_{\rm INAC_{PK}}^2 \times R_{\rm TSET}}$$

(3)

(4)

The COMP pin voltage value is clamped at 4.95 V, so the maximum on time can be calculated by 式 4.

$$t_{ON} = (V_{COMP} - 125 \text{ mV}) \times K_{T}(V_{INAC})$$

$\boxtimes$  16 shows the values of K<sub>T</sub> versus the peak voltage value on VINAC pin.

The maximum switching frequency of each phase is limited by minimum-period timers. If the inductor current decays to zero before the minimum-period timer elapses, the next turn on will be delayed, resulting in discontinuous phase current.

A restart timer ensures starting under all circumstances by restarting both phases if the ZCD input of either phase has not transitioned from high-to-low within approximately 210 µs.

The minimum switching period,  $T_{(MIN)}$ , is inversely proportional to the time-setting resistor  $R_{TSET}$  (the resistor from the TSET pin to ground).

図 16. K<sub>T</sub> vs Peak Voltage

#### Feature Description (continued)

#### 8.3.4 Distortion Reduction

Due to the parasitic resonance between the drain-source capacitance of the switching MOSFET and the boost inductor, conventional transition-mode PFC circuits may not be able to absorb power from the input line when the input voltage is near zero. This limitation increases total harmonic distortion as a result of ac-line current waveform distortion in the form of flat spots. To help reduce line-current distortion, the UCC28064A increases switching MOSFET on-time when the input voltage is near 0 V to improve the power absorption capability and compensate for this effect.

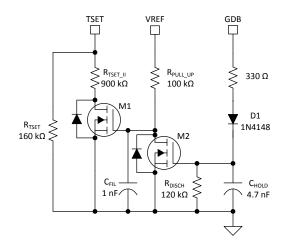

$\boxtimes$  1 in the *Typical Characteristics* section shows the increase in on-time with respect to VINAC voltage. Excessive filtering of the VINAC signal will nullify this function. In cases where small inductances are used (< 250 µH) the increased MOSFET on time can be excessive, increasing distortion instead of decreasing. If this is the case the external circuit shown in  $\boxtimes$  17 can help limit this effect.

図 17. External Circuit to improve THD in case of Low inductance

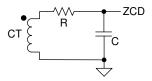

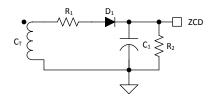

#### 8.3.5 Zero-Current Detection and Valley Switching

In transition-mode PFC circuits, the MOSFET turns on when the boost inductor current reaches zero. Because of the resonance between the boost inductor and the parasitic capacitance at the MOSFET drain node, part of the energy stored in the MOSFET junction capacitor can be recovered, reducing switching losses. Furthermore, when the rectified input voltage is less than half of the output voltage, all the energy stored in the MOSFET junction capacitor can be recovered and zero-voltage switching (ZVS) can be realized. By adding an appropriate delay, the MOSFET can be turned on at the valley of its resonating drain voltage (valley-switching). In this way, the energy recovery can be maximized and switching loss is minimized.

The optimal time delay is generally derived empirically, but a good starting point is a value equal to 25% of the resonant period of the drain circuit. The delay can be realized by a simple RC filter, as shown in  $\boxtimes$  18, but the delay time increases slightly as the input voltage nears the output voltage. Because the ZCD pin is internally clamped, a more accurate delay can also be realized by using the circuit shown in  $\boxtimes$  19.

図 18. Simple RC Delay Circuit

# Feature Description (continued)

図 19. More Accurate Time Delay Circuit

## Feature Description (continued)

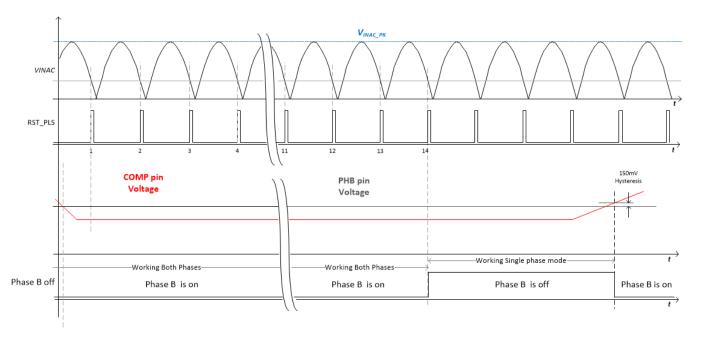

#### 8.3.6 Phase Management and Light-Load Operation

It is challenging to maintain high efficiency under all loading conditions. When operating in light-load, switching losses may dominate over conduction losses and the efficiency may be improved if one phase is turned off. Turning off a phase at light load is especially valuable for meeting light-load efficiency standards. This is a major benefit of interleaved PFC and it is especially valuable for meeting 80+ design requirements.

In order to ensure smooth operation when removing or adding a phase, some additional considerations are required. When the number of phases operating is changed from 2 to 1 the overall switching frequency is reduced by a factor of 2. If everything else is held constant this will also reduce the energy delivered to the load by a factor of 2. In order to maintain the same power delivery to the output, it is necessary to increase the on-time when performing such a transition. A similar situation exists when a phase is added. In other words, when going from 1 phase to 2 phases, the on-time should decrease in order to have smooth continuous power delivery. If everything is ideal, the amount by which the system has to increase/decrease the on-time is a factor of 2. Since 1 phase needs to deliver twice the energy as each phase when both phases are operating, doubling the on-time would seem to make the most sense (or cutting it in half if going from 1 phase to 2 phases). While this works well in many cases there are real world examples where this fails to provide a sufficiently smooth phase shedding/adding operation. In order to resolve this conflict the circuit in  $\aleph$  20 can be utilized to program a custom on-time for both 1 phase and 2 phase operation. The circuit operates by monitoring the gate drive of phase 2 (GDB). When this signal is active the resistor  $R_{TSET}$  configures the on-time. When the gate drive is absent the on-time is configured by the parallel combination of  $R_{TSET}$  and  $R_{TSET}$ . The capacitors  $C_{FIL}$  and  $C_{HOLD}$  can be adjusted to set up custom delays in the phase shedding/adding process.

20. External circuit for Enhanced Phase Shedding

In the case where the 2x factor is sufficient, the UCC28064A can manage this phase shedding/adding process without the need of the circuit in 2 20. The PHB input can be used to set the load value when the UCC28064A has to operate in single-phase mode. The UCC28064A internally compares the voltage fed to PHB pin with the COMP pin voltage. If COMP is below PHB channel B will stop switching and the channel A on-time will automatically double to compensate the missing power from channel B. When operating in single phase mode in order to avoid risk of inductor saturation an internal clamp ensures the on time never can exceed the maximum on-time you will have when operating in dual phase mode. The device will resume dual-phase mode when the COMP pin voltage exceeds PHB voltage plus the PHB hysteresis. In order to avoid voltage ripple on the COMP pin causing the system to oscillate between one and two phases a time delay filter is present. In order to change from normal operation to single phase mode the COMP voltage should stay below PHB pin voltage for 14 line half cycles. The filter does not apply for the opposite transition. When the COMP pin voltage exceeds PHB pin voltage plus the hysteresis, channel B is immediately turned on and the channel A on-time is halved.

At start up, the output voltage can be very close to the peak line voltage. The inductor current value during the off time will decrease very slowly and it is possible systems will operate in CCM for a few switching cycles. In order to avoid high current, during soft start, the system is forced to work with both phases on even if the COMP pin voltage is below PHB pin voltage. In two phase mode the on-time of each phase is one half of the on time of phase A when Phase B is off so this mitigates the risk of high CCM currents.

Copyright © 2017-2019, Texas Instruments Incorporated

# Feature Description (continued)

22. Phase Management Time Diagram

### Feature Description (continued)

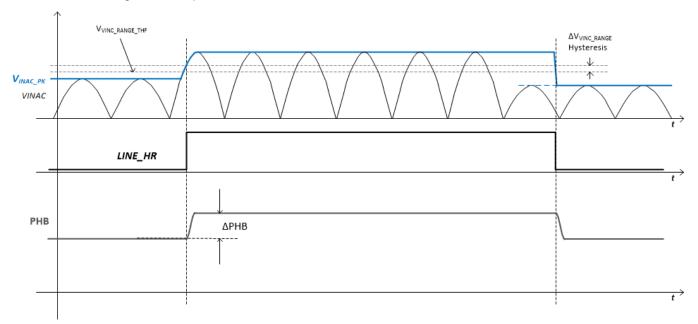

The voltage on the PHB pin can be set using a simple resistor divider connected to the V<sub>REF</sub> pin. Another important feature, that allows optimization of phase management is that it is possible to set different thresholds wether the PFC input voltage is in the range of 90 to 132 V<sub>RMS</sub> (US mains) or in the range of 180 to 265 V<sub>RMS</sub> (European mains). If the peak voltage sensed by the V<sub>INAC</sub> pin exceeds 3.5V the converter assumes that the input voltage is in the range of 180 to 265 V<sub>RMS</sub> and starts sourcing from PHB a small current (3µA typically) that increases the voltage on PHB pin.

Use  $\pm 5$  and  $\pm 6$  to calculate PHB thresholds.

$$V_{\text{PHB}\_\text{LR}} = \frac{R_{\text{D}}}{R_{\text{U}} + R_{\text{D}}} \times V_{\text{REF}}$$

(5)

$$V_{PHB_{HR}} = \frac{R_D}{R_U + R_D} \times V_{REF} + \frac{R_D \times R_U}{R_U + R_D} \times I_{PHB_RANGE}$$

(6)

The load value at which the system moves between single phase and dual phase modes of operation is part of the system specification. The formulas to calculate resistor divider resistance values that allows us to get the desired thresholds are reported below.

$$R_{U} = \frac{\Delta V_{PHB} \times V_{REF}}{V_{PHB} LR} \times I_{PHB} RANGE}$$

$$= \frac{\Delta V_{PHB} \times V_{REF}}{\Delta V_{PHB} \times V_{REF}}$$

(7)

$$R_{\rm D} = \frac{1}{(V_{\rm REF} - V_{\rm PHB}_{\rm LR}) \times I_{\rm PHB}_{\rm RANGE}}$$

where

# Feature Description (continued)

- R<sub>D</sub> is the lower resistor of the resistor divider that provides voltage to PHB pin that is supplied by V<sub>REF</sub>

- R<sub>u</sub> is the upper resistor of the resistor divider.

$$\Delta V_{\text{PHB}} = V_{\text{PHB} HR} - V_{\text{PHB} LR}$$

(9)

(8)

PHB thresholds are selected by the user according to the load value where they want to turn off Phase B. So assuming we want to turn off Phase B when the load goes below  $P_{OUT\_PHB}$  we can calculate the threshold using equation (10). We can use the same equation in order to calculate the two thresholds  $V_{PHB\_HR}$  and  $V_{PHB\_LR}$  once provided the two different load values, for US range and EU range where Phase B has to be turned off. Of course main EU range PHB\_OFF load value has to be greater than main US range PHB\_OFF load value. A reasonable range of load values is from 20% to 30% of converter rated power.

$$V_{PHB} = \frac{(4.825 \text{ V})}{V_{REF}} \times \frac{P_{OUT (PHB)}}{P_{OUT (MAX)}} + 125 \text{ mV}$$

(10)

When the COMP voltage goes below the burst mode threshold the device is forced to work in single phase mode so if the COMP pin voltage drops below the burst threshold it is possible that the time delay filtering is not respected. Moreover it is recommended that PHB pin voltage is at least 600mV higher than BRST pin voltage.

www.tij.co.jp

#### Feature Description (continued)

#### 8.3.7 Burst Mode Operation

To further improve light load efficiency burst mode operation can be used. In this case the burst mode threshold is fed to BRST pin by an external source that could be a simple resistor divider connected to the  $V_{REF}$  pin. If COMP pin voltage goes below the BRST pin voltage the converter stops switching. When the COMP voltage exceeds BRST pin voltage plus hysteresis, the converter restarts switching.

In order to have a smooth transition between switching and not switching and vice-versa burst soft-on and burst soft-off features are added. So when the COMP voltage goes below BRST voltage switching is not stopped immediately, but there will be eight additional switching cycles where FET on time is decreased gradually. In similar way when COMP voltage exceeds BRST voltage plus hysteresis a soft-on period occurs where the on time is increased gradually to a value that corresponds to the present COMP voltage in eight switching cycles.

When the load decreases the device is intended to operate in single phase mode starting from 35% to 15% of rated load and goes to burst mode at lower load values when single phase operation is activated. If the PHB threshold is lower than the Burst mode threshold, single phase operation is forced during soft-on and soft-off periods of burst mode.

Similar to the PHB feature the burst mode threshold has two different levels depending if the PFC input voltage is in the range of 90 to 132  $V_{RMS}$  (US main) or in the range of 180 to 265  $V_{RMS}$  (European main). If the peak voltage on VINAC pin peak voltage exceeds 3.5 V (typ.) a small current (3  $\mu$ A typically) is provided from BRST pin. If a resistor divider is used to set the BRST pin voltage this current will raise the voltage.

Use  $\pm$  11 and  $\pm$  12 to calculate the resistor divider that sets the Burst Mode thresholds. These equations are identical to the equations used to calculate the PHB resistor divider.

R<sub>U</sub> and R<sub>D</sub> are the upper and the lower resistence of the resistor divider connected to VREF pin.

$$R_{\rm U} = \frac{\Delta V_{\rm PHB} \times V_{\rm REF}}{V_{\rm PHB} _{\rm LR} \times I_{\rm PHB} _{\rm RANGE}}$$

(11)

$$R_{D} = \frac{\Delta V_{BRST} \times V_{REF}}{(V_{REF} - V_{BRST (LR)}) \times I_{BRST (RANGE)}}$$

(12)

#### 8.3.8 External Disable

The UCC28064A can be externally disabled by pulling the VSENSE pin to ground with an open-drain or opencollector driver. When disabled, the device supply current drops significantly and COMP is actively pulled low. This disable method forces the device into standby mode and minimizes its power consumption. When VSENSE is released, the device enters soft-start mode. VREF

VSENSE

## Feature Description (continued)

#### 8.3.9 Improved Error Amplifier

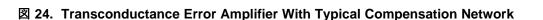

The voltage error amplifier is a transconductance amplifier. Voltage-loop compensation is connected from the error amplifier output, COMP, to analog ground, AGND. The recommended Type-II compensation network is shown in  $\boxtimes$  24. For loop-stability purposes, the compensation network values are calculated based on small-signal perturbations of the output voltage using the nominal transconductance (gain) of 55 µS.

gm D

COMP

$C_Z$

$\mathsf{R}_\mathsf{Z}$

$\leq$

CP

4.95V

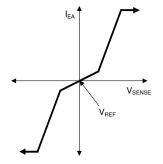

To improve the transient response to large perturbations, the error amplifier gain increases by a factor of around 5X when the error amplifier input deviates more than  $\pm 5\%$  from the nominal regulation voltage, VSENSEreg. This increase allows faster charging and discharging of the compensation components following sudden load-current increases or decreases.

Basic voltage error amplifier transconductance curve showing small-signal and large-signal gain sections, with maximum current limitations.

#### 図 25. Basic Voltage-Error Amplifier Transconductance Curve

24

## UCC28064A JAJSFJ9B – DECEMBER 2017 – REVISED OCTOBER 2019

## Feature Description (continued)

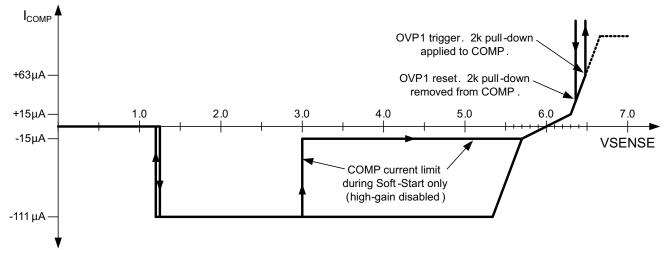

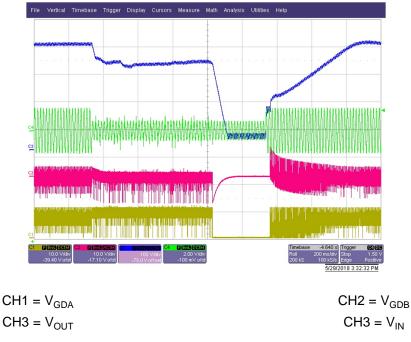

## 8.3.10 Soft Start

Soft-start is a process for boosting the output voltage of the PFC converter from the peak of the ac-line input voltage to the desired regulation voltage under controlled conditions. Instead of a dedicated soft-start pin, the UCC28064A uses the voltage error amplifier as a controlled current source to increase the PWM duty-cycle by way of increasing the COMP voltage. To avoid excessive start-up time-delay when the ac-line voltage is low, a higher current is applied until VSENSE exceeds 3 V at which point the current is reduced to minimize the tendency for excess COMP voltage at no-load start-up.

The PWM gradually ramps from zero on-time to normal on-time as the compensation capacitor from COMP to AGND charges from zero to near its final value. This process implements a soft-start, with timing set by the output current of the error amplifier and the value of the compensation capacitors. Soft-start ends when VSENSE pin voltage exceeds 95% of VSENSEreg. During soft-start the device will operate with both phases on and even if the COMP voltage is below the BRST pin voltage the device will not stop switching. In the event of a HVSEN failsafe OVP, brownout, external-disable, UVLO fault, or other protection faults, COMP is actively discharged and the UCC28064A will soft-start after the triggering event is cleared. Even if a fault event happens very briefly, the fault is latched into the soft-start state and soft-start is delayed until COMP is fully discharged to 20 mV and the fault is cleared. See 26 for details on the COMP current. See 27 which illustrates an example of typical system behavior during soft-start.

Expanded COMP output current curve including voltage error amplifier transconductance and modifications applicable to soft-start and overvoltage conditions.

#### 26. Expanded COMP pin Output Current Curve

# Feature Description (continued)

図 27. Soft-Start Timing with System Behavior

#### **Feature Description (continued)**

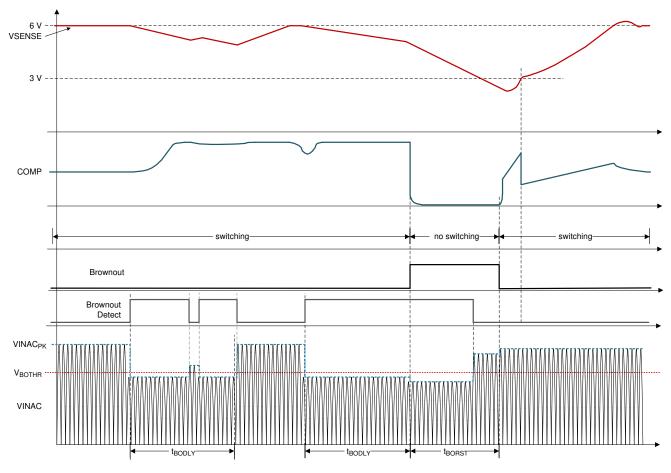

#### 8.3.11 Brownout Protection

As the power line RMS voltage decreases, RMS input current must increase to maintain a constant output voltage for a specific load. Brownout protection helps prevent excess system thermal stress (due to the higher RMS input current) from exceeding a safe operating level. Power-line voltage is sensed at VINAC pin. When the VINAC fails to exceed the brownout threshold for the brownout filter time ( $t_{BODLY}$ ), a brownout condition is detected and both gate drive outputs are turned off. During brownout, COMP is actively pulled low and soft-start condition is initiated. When VINAC rises above the brownout threshold, the power stage soft-starts as COMP rises with controlled current.

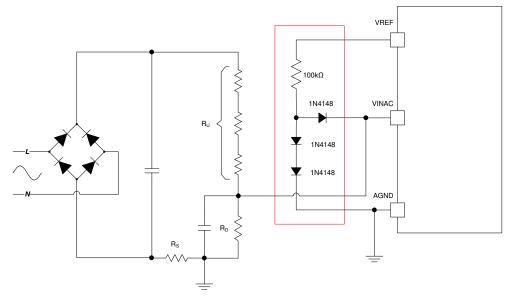

The brownout threshold and its hysteresis are set by the voltage-divider ratio and resistor values. Brownout protection is based on VINAC peak voltage; the threshold and hysteresis are also based on the line peak voltage. Hysteresis is provided by a 2- $\mu$ A current-sink (I<sub>BOHYS</sub>) enabled whenever Brownout protection is activated. As soon as the Brownout protection is activated an additional timer is started that counts the t<sub>BORST</sub> time. During this time the device is forced to stay in a Brownout condition. So, during t<sub>BORST</sub> time, the device is not allowed to switch, COMP is pulled low and the 2-uA current sink (I<sub>BOHYS</sub>) is active regardless of the voltage on VINAC pin. After t<sub>BORST</sub> is elapsed the device can exit from Brownout condition only if VINAC pin exceeds V<sub>BOTHR</sub> threshold. When the device operates in burst mode, several blocks inside the IC are turned off to reduce IC current consumption. The Brownout management block is also turned off. Each time the system stops switching, because of burst mode, the Brownout filter timer is reset. So if the system is operating in burst mode, the Brownout protection, generally is not triggered. The main purpose of Brownout is to avoid thermal stress. The peak VINAC voltage can be easily translated into an RMS value. Example resistor values for the voltage divider are 8.61 M $\Omega \pm 1\%$  from the rectified input voltage to VINAC and 133 k $\Omega \pm 1\%$  from VINAC to ground. These resistors set the typical thresholds for RMS line voltages, as shown in  $\mathbf{a}$  1.

| THRESHOLD | AC-LINE VOLTAGE (RMS) |

|-----------|-----------------------|

| Falling   | 67 V                  |

| Rising    | 81 V                  |

式 13 and 式 14 can be used to calculate the VINAC divider-resistors values based on desired brownout and brown-in voltage levels.  $V_{AC_OK}$  is the desired RMS turnon voltage,  $V_{AC_BO}$  is the desired RMS turnoff brownout voltage, and  $V_{LOSS}$  is total series voltage drop due to wiring, EMI-filter, and bridge-rectifier impedances at  $V_{AC_BO}$ .  $V_{BOTHR}$ , and  $I_{BOHYS}$  are found in the data-tables of this datasheet.

$$R_{A} = \left[\frac{\sqrt{2} \times (V_{AC_{OK}} - V_{AC_{BO}})}{I_{BOHYS}}\right]$$

(13)

$$R_{B} = \frac{R_{A}}{\left(\frac{\sqrt{2} \times V_{AC_{BO}} - V_{LOSS}}{V_{BOTHR}} - 1\right)}$$

(14)

When standard values for the VINAC divider-resistors  $R_A$  and  $R_B$  are selected, the actual turn-on and brownout threshold RMS voltages for the ac-line can be back-calculated with  $\pm$  15 and  $\pm$  16:

$$V_{AC_{BO}} = \frac{1}{\sqrt{2}} \times \left[ \left( 1 + \frac{R_A}{R_B} \right) \times V_{BOTHR} + V_{LOSS} \right]$$

$$1 \qquad [R_B + R_A \qquad ]$$

(15)

$$V_{AC_{OK}} = \frac{1}{\sqrt{2}} \times \left[ \frac{R_B + R_A}{R_B} \times V_{BOTHR} + R_A \times I_{BOHYS} \right]$$

(16)

An example of the timing for the brownout function is illustrated in  $\boxtimes$  28.

( n

1

www.tij.co.jp

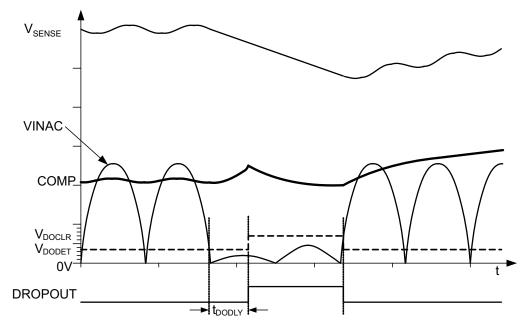

### 8.3.12 Line Dropout Detection

It is often the case that the AC-line voltage momentarily drops to zero or nearly zero, due to transient abnormal events affecting the local AC-power distribution network. Referred to as AC-line dropouts (or sometimes as linedips) the duration of such events usually extends to only 1 or 2 line cycles. During a dropout, the down-stream power conversion stages depend on sufficient energy storage in the PFC output capacitance, which is sized to provide the ride-through energy for a specified hold-up time. Typically while the PFC output voltage is falling, the voltage-loop error amplifier output rises in an attempt to maintain regulation. As a consequence, excess duty-cycle is commanded when the AC-line voltage returns and high peak current surges may saturate the boost inductors with possible overstress and audible noise.

The UCC28064A incorporates a dropout detection feature which suspends the action of the error amplifier for the duration of the dropout. If the VINAC voltage falls below 0.35 V for longer than 5 ms, a dropout condition is detected and the error amplifier output is turned off. In addition, a  $4-\mu$ A pull down current is applied to COMP to gently discharge the compensation network capacitors. In this way, when the AC-line voltage returns, the COMP voltage (and corresponding duty-cycle setting) remains very near or even slightly below the level it was before the dropout occurred. Current surges due to excess duty-cycle, and their undesired attendant effects, are avoided. The dropout condition is cancelled and the error amplifier resumes normal operation when VINAC rises above 0.71 V.

Based on the VINAC divider-resistor values calculated for Brownout in the previous section, the input RMS voltage thresholds for dropout detection  $V_{AC_{DO}}$  and dropout clearing  $V_{DO_{CLR}}$  can be determined using  $\pm$  17 and  $\pm$  18, below.

$$V_{AC\_DO} = \frac{V_{DODET} \left(\frac{R_A}{R_B} + 1\right) + V_{LOSS}}{\sqrt{2}}$$

$$V_{DO\_CLR} = \frac{V_{DOCLR} \left(\frac{R_A}{R_B} + 1\right) + V_{LOSS}}{\sqrt{2}}$$

(17)

(17)

(18)

Avoid excessive filtering of the VINAC signal, or dropout detection may be delayed or defeated. An RC timeconstant of  $\leq$  100 s. should provide good performance.  $\boxtimes$  29 shows an example of the timing for the dropout function.

図 28. AC-Line Brownout Timing and System Behavior

29. AC-Line Dropout Timing With Illustrative System Behavior

## 8.3.13 VREF

VREF is an output which supplies a well-regulated reference voltage to circuits within the device as well as serving as a limited source for external circuits. This output must be bypassed to GND with a low-impedance 0.1- $\mu$ F or larger capacitor placed as close to the VREF and GND pins as possible. Current draw by external circuits should not exceed 2mA and should not be pulsing.

The VREF output is disabled under the following conditions: when VCC is in UVLO, or when VSENSE is below the Enable threshold. This output can only source current and is unable to accept current into the pin.

## 8.3.14 VCC

VCC is usually connected to a bias supply of between 14 V and 21 V. To minimize switching ripple voltage on VCC, it should be bypassed with a low-impedance capacitor as close to the VCC and GND pins as possible. The capacitance should be sized to adequately decouple the peak currents due to gate-drive switching at the highest operating frequency. When powered from a poorly-regulated low-impedance supply, an external zener diode is recommended to prevent excessive current into VCC.

The undervoltage-lockout (UVLO) condition is when VCC voltage has not yet reached the turn-on threshold or has fallen below the turn-off threshold, having already been turned on. While in UVLO, the VREF output and most circuits within the device are disabled and VCC current falls significantly below the normal operating level. The same situation applies when VSENSE is below its Enable threshold. This helps minimize power loss during pre-power up and standby conditions.

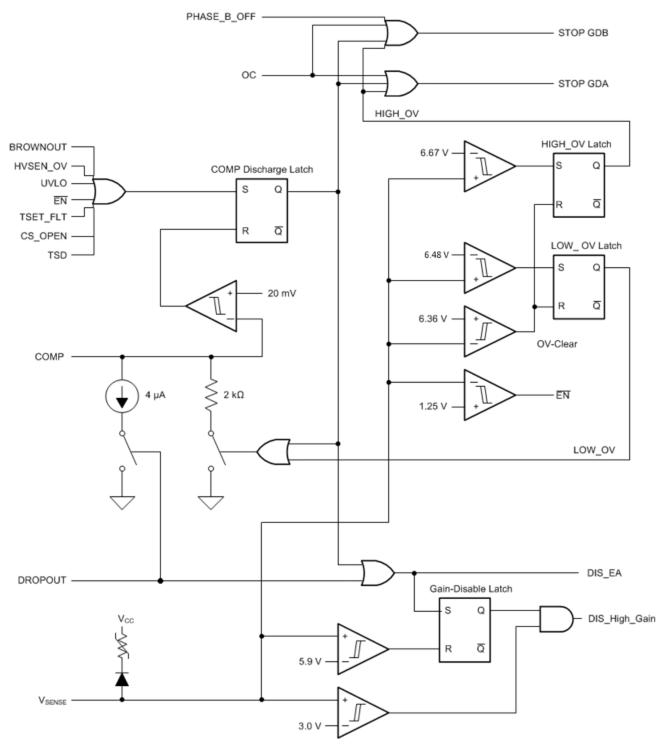

#### 8.3.15 System Level Protections

#### 8.3.15.1 Failsafe OVP - Output Over-voltage Protection

Failsafe OVP prevents any single failure from allowing the output to boost above safe levels. Redundant paths for output voltage sensing provide additional protection against output over-voltage. Over-voltage protection is implemented through two independent paths: VSENSE and HVSEN.

VSENSE pin voltage is compared with two levels of over-voltage. If the lower one,  $V_{LOW_OV}$ , is exceeded the COMP pin is discharged by an internal 2-k $\Omega$  resistance until the output voltage falls below  $V_{LOW_OV}$  reduced of 2% to provide hysteresis ( $\Delta V_{LOW_OV_HYST}$ ). If also the higher over-voltage threshold is exceeded in addition to activate the 2-k $\Omega$  pull down switching is soon disabled. In order to re-enable the switching the sensed voltage has to fall below  $V_{LOW_OV}$  reduced of 2%. Additional over-voltage protection can be implemented on HVSEN pin through a separate resistor divider to monitor output voltage. An over-voltage is detected if HVSEN pin voltage exceeds  $V_{HV_OV_FLT}$  an as consequence device stops switching and the 2-k $\Omega$  pull down is activated. The pull down 2-k $\Omega$  pull down is removed only if HVSEN pin goes below  $V_{HV_OV_CLR}$  threshold and the COMP pin is fully discharged to 20 mV. Both conditions needs to be true before the soft-start can begin.

The converter shuts down if either input senses a severe over-voltage condition. The output voltage can still remain below a safe limit if either sense path fails. The device is re-enabled when both sense inputs fall back into their normal ranges. At that time, the gate drive outputs will resume switching under PWM control. A low-level over-voltage on VSENSE does not trigger soft-start, an higher-level over voltage on VSENSE additionally shuts off the gate-drive outputs until the OV clears, but still does not trigger a soft-start. However, an over-voltage detected on HVSEN does trigger a full soft-start and the COMP pin is fully discharged to 20 mV before the soft-start can begin.

#### 8.3.15.2 Overcurrent Protection

Under certain conditions (such as inrush, brownout-recovery, and output over-load) the PFC power stage sees large currents. It is critical that the power devices be protected from switching during these conditions.