🕳 Order

Now

#### ADS8860

Reference

E Design

JAJSH03B-MAY 2013-REVISED FEBRUARY 2019

# ADS8860 16 ビット、1MSPS、シリアル・インターフェイス、 micropower、小型、シングルエンド入力の SAR アナログ/デジタル・コ ンバータ

# 1 特長

Texas

INSTRUMENTS

- サンプル・レート:1MHz

- レイテンシなしの出力

- ユニポーラ、シングルエンド入力範囲: 0~+V<sub>REF</sub>

- SPI™互換のシリアル・インターフェイス デイジー・チェーン・オプション付き

- 非常に優れた AC および DC 性能

- SNR:93dB、THD:-108dB

- INL:±1.0 LSB (標準値)、±2.0 LSB (最大値)

- DNL:±1.0 LSB (最大値)、16ビット NMC

- 幅広い動作範囲

- AVDD: 2.7V~3.6V

- DVDD:1.65V~3.6V

(AVDD にかかわらず)

- REF:2.5V~5V (AVDD にかかわらず)

- 動作温度範囲:-40℃~+85℃

- 低消費電力

- 1MSPS で 5.5mW

- 100kSPS で 0.55mW

- 10kSPS で 55µW

- 電源オフ時電流 (AVDD): 50 nA

- フルスケール・ステップでの 16 ビットへのセト リング: 290ns

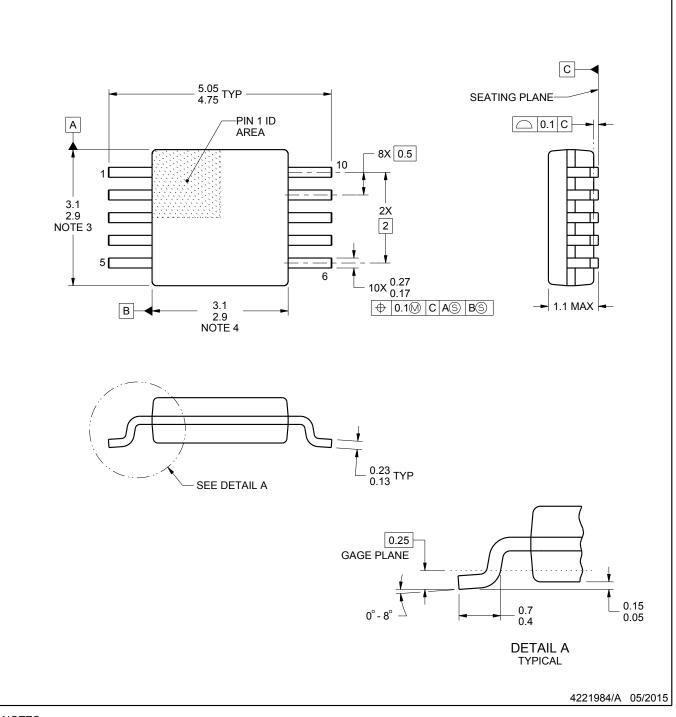

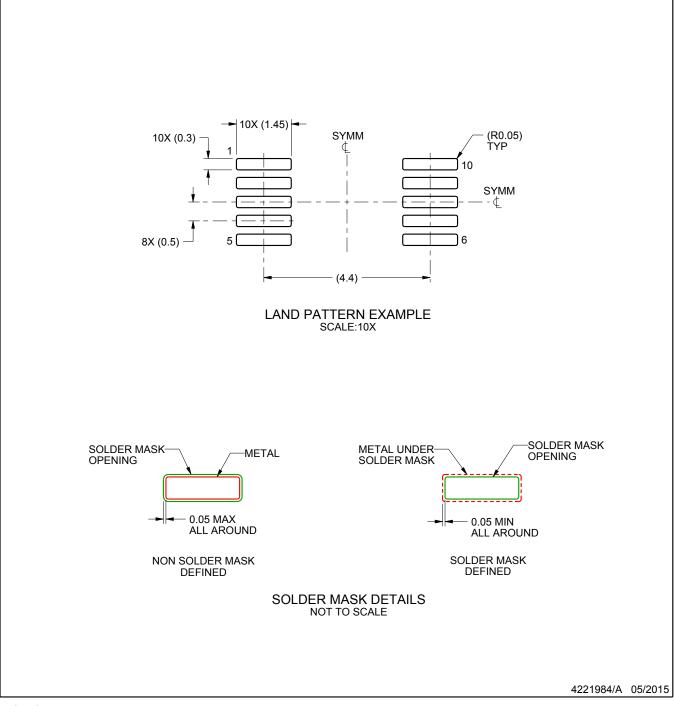

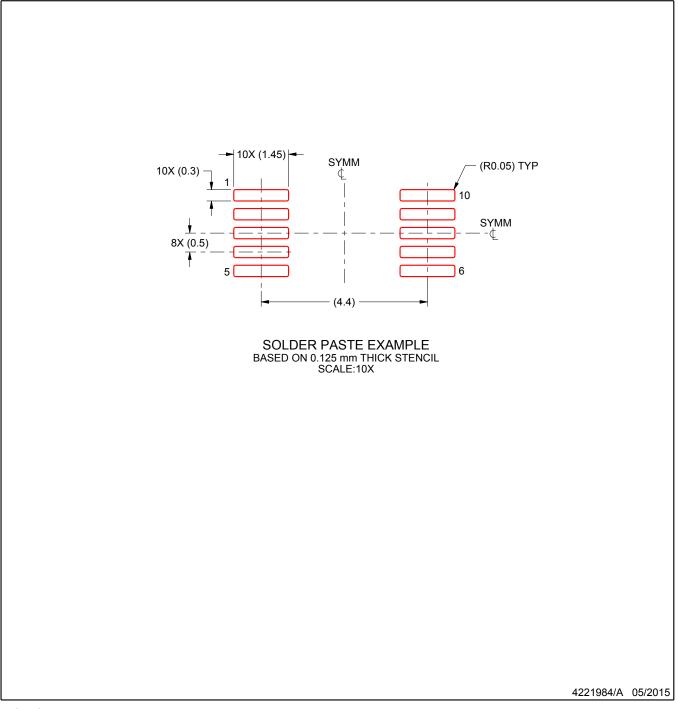

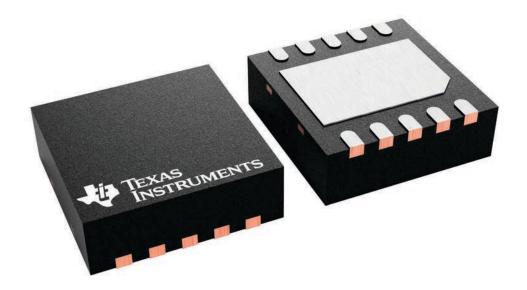

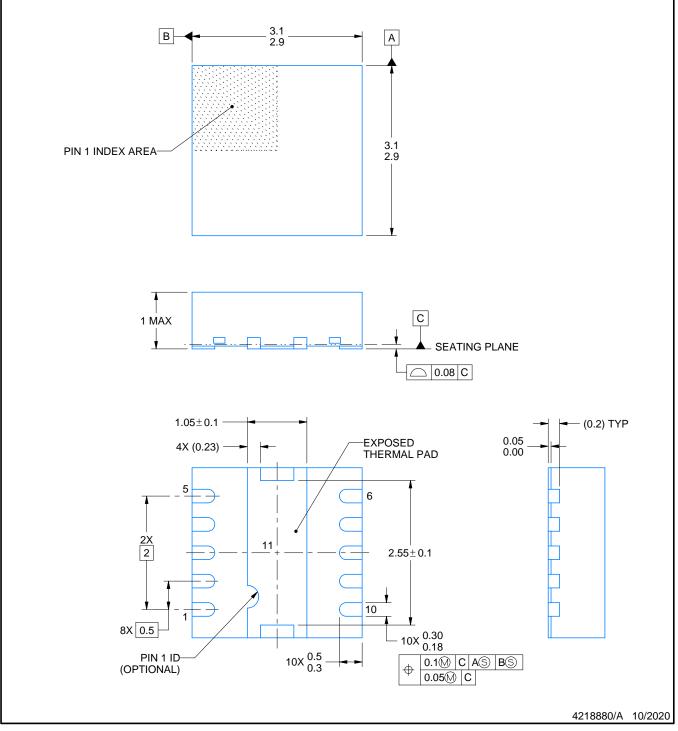

- パッケージ: VSSOP-10 および VSON-10

- 2 アプリケーション

- 自動試験装置 (ATE)

- 計装およびプロセス制御

- 高精度の医療機器

- 低消費電力のバッテリ駆動計測器

# 3 概要

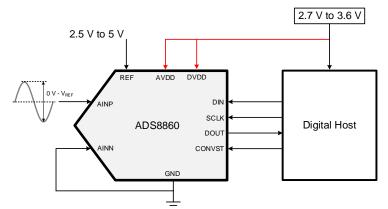

ADS8860 は 16 ビット、1MSPS、シングルエンド入力の アナログ/デジタル・コンバータ (ADC) です。このデバイス は 2.5V~5V の外部基準電圧を使用して動作し、追加の 入力信号スケーリングなしに、広範な信号範囲を選択でき ます。基準電圧設定はアナログ電源電圧 (AVDD) と無関 係で、AVDD を超えることができます。

このデバイスは、複数のデバイスをカスケード接続するためのデイジー・チェーン動作もサポートする SPI 互換シリアル・インターフェイスを備えています。ビジー・インジケータ・ビットを追加すると、デジタル・ホストとの同期を簡単に行えます。

#### 製品情報(1)

| 型番      | パッケージ      | 本体サイズ(公称)     |  |  |  |

|---------|------------|---------------|--|--|--|

|         | VSSOP (10) | 3.00mm×3.00mm |  |  |  |

| ADS8860 | VSON (10)  | 3.00mm×3.00mm |  |  |  |

<sup>(1)</sup> 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

# ADC 電源用に別個の LDO が不要

53

# 目次

| 1  | 特長   |                                       |

|----|------|---------------------------------------|

| 2  | アプ   | リケーション1                               |

| 3  | 概要   |                                       |

| 4  | 改訂   | 履歴2                                   |

| 5  | 概要   | (続き)                                  |

| 6  | Dev  | ice Comparison Table5                 |

| 7  | Pin  | Configuration and Functions 5         |

| 8  | Spe  | cifications6                          |

|    | 8.1  | Absolute Maximum Ratings 6            |

|    | 8.2  | ESD Ratings 6                         |

|    | 8.3  | Recommended Operating Conditions 6    |

|    | 8.4  | Thermal Information 6                 |

|    | 8.5  | Electrical Characteristics7           |

|    | 8.6  | Timing Requirements: 3-Wire Operation |

|    | 8.7  | Timing Requirements: 4-Wire Operation |

|    | 8.8  | Timing Requirements: Daisy-Chain 10   |

|    | 8.9  | Typical Characteristics 12            |

| 9  | Para | ameter Measurement Information 19     |

|    | 9.1  | Equivalent Circuits 19                |

| 10 | Deta | ailed Description 20                  |

# 4 改訂履歴

٠

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Revision A (December 2013) から Revision B に変更

|   | 機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デ                                            |    |

|---|-------------------------------------------------------------------------------------------------------------|----|

|   | バイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクション 追加                                                       | 1  |

| • | ドキュメント全体を通して、アナログ入力を擬似差動からシングルエンドに変更                                                                        | 1  |

| • | 「特長」セクションで DVDD の値を 2.7V~3.6V から 1.65V~3.6V に 変更                                                            | 1  |

| • | ドキュメント全体で MSOP を VSSOP に 変更                                                                                 | 1  |

| • | Changed title of Device Comparison Table from Family Information                                            | 5  |

| • | Changed footnotes of Family Information table                                                               | 5  |

| • | Changed LSB footnote in Electrical Characteristics table to include how to convert LSB to ppm               | 7  |

| • | Added more information about validity of data on SCLK edges in all interface modes                          | 23 |

| • | Changed diagrams and text for better explanation of the daisy-chain feature in the Daisy-Chain Mode section | 28 |

| • | Changed Equation 1 and Equation 2                                                                           | 32 |

| • | Changed Charge-Kickback Filter section title and functionality description                                  | 33 |

「製品情報」表、「ESD 定格」表、「推奨動作条件」表、「パラメータ測定情報」セクション、「機能説明」セクション、「デバイスの

#### 2013年5月発行のものから更新

| • | 「特長」の「AC および DC 性能」箇条書きの副項目を 変更                                                    | 1 |

|---|------------------------------------------------------------------------------------|---|

|   | 「特長」のフルスケール・ステップでのセトリングの箇条書き項目を変更                                                  |   |

|   | 「アプリケーション」の最後の箇条書き項目 2 つを 削除                                                       |   |

| • | 「概要」セクション 変更                                                                       | 1 |

| • | 最初のページの図 変更                                                                        | 4 |

| • | Added Family Information, Absolute Maximum Ratings, and Thermal Information tables | 5 |

| • | Added Pin Configurations section                                                   | 5 |

#### XAS STRUMENTS

www.tij.co.jp

|    | 10.1 | Overview 20                 |

|----|------|-----------------------------|

|    | 10.2 | Functional Block Diagram 20 |

|    | 10.3 | Feature Description         |

|    | 10.4 | Device Functional Modes 22  |

| 11 | Appl | ication and Implementation  |

|    | 11.1 | Application Information 32  |

|    | 11.2 | Typical Applications        |

| 12 | Powe | er Supply Recommendations   |

|    | 12.1 | Power-Supply Decoupling     |

|    | 12.2 | Power Saving                |

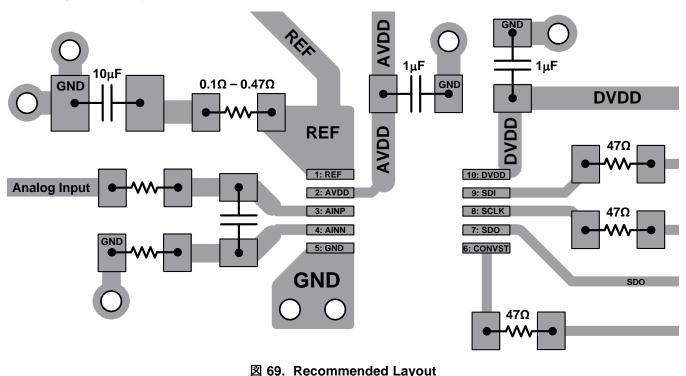

| 13 | Layo | ut                          |

|    | 13.1 | Layout Guidelines           |

|    | 13.2 | Layout Example 39           |

| 14 | デバ   | イスおよびドキュメントのサポート            |

|    | 14.1 | ドキュメントのサポート40               |

|    | 14.2 | ドキュメントの更新通知を受け取る方法40        |

|    | 14.3 | コミュニティ・リソース40               |

|    | 14.4 | 商標 40                       |

|    | 14.5 | 静電気放電に関する注意事項 40            |

|    | 14.6 | Glossary 41                 |

| 15 | メカニ  | カル、パッケージ、および注文情報            |

# Page

### Page

2

#### www.tij.co.jp

| • | Added Electrical Characteristics table | 7  |

|---|----------------------------------------|----|

| • | Added Timing Characteristics section   | 9  |

| • | Added Typical Characteristics section  | 12 |

JAJSH03B-MAY 2013-REVISED FEBRUARY 2019

www.ti.com

# 5 概要(続き)

このデバイスは、-0.1V~V<sub>REF</sub> + 0.1V の範囲のユニポーラ・シングルエンド・アナログ入力をサポートしています。

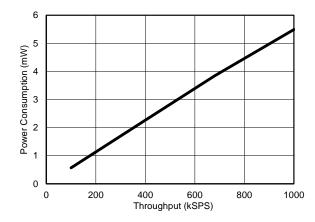

デバイスは、非常に低い消費電力で動作するよう最適化されています。消費電力は速度に正比例します。この特長から、 ADS8860 は低速度のアプリケーションに最適です。

# 6 Device Comparison Table

| THROUGHPUT | 18-BIT, TRUE-DIFFERENTIAL | 16-BIT, SINGLE-ENDED   | 16-BIT, TRUE-DIFFERENTIAL |  |

|------------|---------------------------|------------------------|---------------------------|--|

| 100 kSPS   | ADS8887                   | ADS8866                | ADS8867                   |  |

| 250 kSPS   | SPS —                     |                        | —                         |  |

| 400 kSPS   | ADS8885                   | ADS8864                | ADS8865                   |  |

| 500 kSPS   | —                         | ADS8319 <sup>(1)</sup> | ADS8318 <sup>(1)(2)</sup> |  |

| 680 kSPS   | ADS8883                   | ADS8862                | ADS8863                   |  |

| 1 MSPS     | ADS8881                   | ADS8860                | ADS8861                   |  |

Pin-to-pin compatible device with AVDD = 5 V. Supports standard for fully-differential input. (1)

(2)

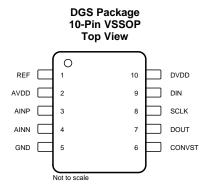

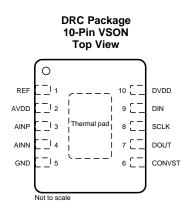

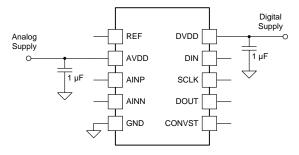

# 7 Pin Configuration and Functions

#### **Pin Functions**

| PIN                                                                                |                                                                                                               |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |  |  |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.                                                                           |                                                                                                               | TYPE                                                                                                                                                                                                | DESCRIPTION                                                                                                                                                                                                                                                                       |  |  |

| AINN                                                                               | 4                                                                                                             | Analog input                                                                                                                                                                                        | Inverting analog signal input                                                                                                                                                                                                                                                     |  |  |

| AINP                                                                               | 3                                                                                                             | Analog input                                                                                                                                                                                        | Noninverting analog signal input                                                                                                                                                                                                                                                  |  |  |

| AVDD                                                                               | 2                                                                                                             | Analog                                                                                                                                                                                              | Analog power supply. This pin must be decoupled to GND with a 1-µF capacitor.                                                                                                                                                                                                     |  |  |

| CONVST                                                                             | 6                                                                                                             | Digital input                                                                                                                                                                                       | Convert input. This pin also functions as the $\overline{CS}$ input in 3-wire interface mode; see the<br><i>Description</i> and <i>Timing Requirements</i> sections for more details.                                                                                             |  |  |

| DIN                                                                                | 9                                                                                                             | Digital input                                                                                                                                                                                       | Serial data input. The DIN level at the start of a conversion selects the mode of operation (such as CS or daisy-chain mode). This pin also serves as the CS input in 4-wire interface mode; see the <i>Description</i> and <i>Timing Requirements</i> sections for more details. |  |  |

| DOUT                                                                               | OUT 7 Digital output Serial data output                                                                       |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |  |  |

| DVDD                                                                               | DVDD 10 Power supply Digital interface power supply. This pin must be decoupled to GND with a 1-µF capacitor. |                                                                                                                                                                                                     | Digital interface power supply. This pin must be decoupled to GND with a 1-µF capacitor.                                                                                                                                                                                          |  |  |

| Device ground. Note that this pin is a common ground pin for both the analog power |                                                                                                               | Device ground. Note that this pin is a common ground pin for both the analog power supply (AVDD) and digital I/O supply (DVDD). The reference return line is also internally connected to this pin. |                                                                                                                                                                                                                                                                                   |  |  |

| REF 1 Analog                                                                       |                                                                                                               | Analog                                                                                                                                                                                              | Positive reference input. This pin must be decoupled with a 10-µF or larger capacitor.                                                                                                                                                                                            |  |  |

| SCLK 8 Digital input                                                               |                                                                                                               | Digital input                                                                                                                                                                                       | Clock input for serial interface. Data output (on DOUT) are synchronized with this clock.                                                                                                                                                                                         |  |  |

| Thermal pad —                                                                      |                                                                                                               | _                                                                                                                                                                                                   | Exposed thermal pad <b>(only for the DRC package option)</b> . Texas Instruments recommends connecting the thermal pad to the printed circuit board (PCB) ground.                                                                                                                 |  |  |

# 8 Specifications

#### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                             | MIN  | MAX        | UNIT |

|---------------------------------------------|------|------------|------|

| AINP to GND or AINN to GND                  | -0.3 | REF + 0.3  | V    |

| AVDD to GND or DVDD to GND                  | -0.3 | 4          | V    |

| REF to GND                                  | -0.3 | 5.7        | V    |

| Digital input voltage to GND                | -0.3 | DVDD + 0.3 | V    |

| Digital output to GND                       | -0.3 | DVDD + 0.3 | V    |

| Input current to any pin except supply pins | -10  | 10         | mA   |

| Operating temperature, T <sub>A</sub>       | -40  | 85         | °C   |

| Storage temperature, T <sub>stg</sub>       | -65  | 150        | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 8.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 8.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                      | MIN | NOM | MAX | UNIT |

|------------------|----------------------|-----|-----|-----|------|

| AVDD             | Analog power supply  |     | 3   |     | V    |

| DVDD             | Digital power supply |     | 3   |     | V    |

| V <sub>REF</sub> | Reference voltage    |     | 5   |     | V    |

#### 8.4 Thermal Information

|                       |                                              | ADS         | ADS8860    |      |  |  |

|-----------------------|----------------------------------------------|-------------|------------|------|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGS (VSSOP) | DRC (VSON) | UNIT |  |  |

|                       |                                              | 10 PINS     | 10 PINS    |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 151.9       | 111.1      | °C/W |  |  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 45.4        | 46.4       | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 72.2        | 45.9       | °C/W |  |  |

| ΨJT                   | Junction-to-top characterization parameter   | 3.3         | 3.5        | °C/W |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 70.9        | 45.5       | °C/W |  |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | N/A        | °C/W |  |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 8.5 Electrical Characteristics

all minimum and maximum specifications are at AVDD = 3 V, DVDD = 3 V,  $V_{REF}$  = 5 V, and  $f_{SAMPLE}$  = 1 MSPS over the operating free-air temperature range (unless otherwise noted); typical specifications are at  $T_A$  = 25°C, AVDD = 3 V, and DVDD = 3 V

|                   | PARAMETER                                       | TEST CONDITIONS                                    | MIN   | TYP    | MAX                    | UNIT               |

|-------------------|-------------------------------------------------|----------------------------------------------------|-------|--------|------------------------|--------------------|

| ANALO             | G INPUT                                         |                                                    |       |        |                        |                    |

|                   | Full-scale input span <sup>(1)</sup>            | AINP – AINN                                        | 0     |        | V <sub>REF</sub>       | V                  |

|                   |                                                 | AINP                                               | -0.1  |        | V <sub>REF</sub> + 0.1 | V                  |

|                   | Operating input range <sup>(1)</sup>            | AINN                                               | -0.1  |        | + 0.1                  | V                  |

| CI                | Input capacitance                               | AINP and AINN terminal to GND                      |       | 59     |                        | pF                 |

|                   | Input leakage current                           | During acquisition for dc input                    |       | 5      |                        | nA                 |

| EXTERN            | IAL REFERENCE INPUT                             |                                                    |       |        |                        |                    |

| $V_{REF}$         | Input range                                     |                                                    | 2.5   |        | 5                      | V                  |

|                   | Reference input current                         | During conversion, 1-MHz sample rate, mid-<br>code |       | 300    |                        | μA                 |

|                   | Reference leakage current                       |                                                    |       | 250    |                        | nA                 |

| $C_{REF}$         | Decoupling capacitor at the REF input           |                                                    | 10    | 22     |                        | μF                 |

| SYSTEM            | I PERFORMANCE                                   |                                                    |       |        |                        |                    |

|                   | Resolution                                      |                                                    |       | 16     |                        | Bits               |

| NMC               | No missing codes                                |                                                    | 16    |        |                        | Bits               |

| DNL               | Differential linearity                          |                                                    | -0.99 | ±0.6   | 1                      | LSB <sup>(2)</sup> |

| INL               | Integral linearity <sup>(3)</sup>               |                                                    | -2    | ±0.8   | 2                      | LSB <sup>(2)</sup> |

| Eo                | Offset error <sup>(4)</sup>                     |                                                    | -4    | ±1     | 4                      | mV                 |

|                   | Offset error drift with temperature             |                                                    |       | ±1.5   |                        | µV/°C              |

| E <sub>G</sub>    | Gain error                                      |                                                    | -0.01 | ±0.005 | 0.01                   | %FSR               |

|                   | Gain error drift with temperature               |                                                    |       | ±0.15  |                        | ppm/°C             |

| CMRR              | Common-mode rejection ratio                     | With common-mode input signal = 5 $V_{PP}$ at dc   | 90    | 100    |                        | dB                 |

| PSRR              | Power-supply rejection ratio                    | At mid-code                                        |       | 80     |                        | dB                 |

|                   | Transition noise                                |                                                    |       | 0.5    |                        | LSB                |

| SAMPLI            | NG DYNAMICS                                     |                                                    |       |        |                        |                    |

| t <sub>conv</sub> | Conversion time                                 |                                                    | 500   |        | 710                    | ns                 |

| t <sub>ACQ</sub>  | Acquisition time                                |                                                    | 290   |        |                        | ns                 |

|                   | Maximum throughput rate with or without latency |                                                    |       |        | 1000                   | kHz                |

|                   | Aperture delay                                  |                                                    |       | 4      |                        | ns                 |

|                   | Aperture jitter, RMS                            |                                                    |       | 5      |                        | ps                 |

|                   | Step response                                   | Settling to 16-bit accuracy                        |       | 290    |                        | ns                 |

|                   | Overvoltage recovery                            | Settling to 16-bit accuracy                        |       | 290    |                        | ns                 |

(1) Ideal input span, does not include gain or offset error.

(2) LSB = least significant bit. 1 LSB at 16-bits is approximately 15.26 ppm.

(3) This parameter is the endpoint INL, not best-fit.

(4) Measured relative to actual measured reference.

# **Electrical Characteristics (continued)**

all minimum and maximum specifications are at AVDD = 3 V, DVDD = 3 V,  $V_{REF}$  = 5 V, and  $f_{SAMPLE}$  = 1 MSPS over the operating free-air temperature range (unless otherwise noted); typical specifications are at  $T_A$  = 25°C, AVDD = 3 V, and DVDD = 3 V

|                  | PARAMETER                                   |                                       | TEST CONDITIONS                                                                 | MIN        | TYP  | MAX        | UNIT |  |

|------------------|---------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------|------------|------|------------|------|--|

| DYNAM            | IC CHARACTERIST                             | ICS                                   |                                                                                 |            |      |            |      |  |

|                  |                                             |                                       | At 1 kHz, V <sub>REF</sub> = 5 V                                                | 90.5       | 92.9 |            |      |  |

| SINAD            | Signal-to-noise + distortion <sup>(5)</sup> |                                       | At 10 kHz, V <sub>REF</sub> = 5 V                                               |            | 92.9 |            | dB   |  |

|                  |                                             |                                       | At 100 kHz, V <sub>REF</sub> = 5 V                                              |            | 88.2 |            |      |  |

| SNR              |                                             |                                       | At 1 kHz, V <sub>REF</sub> = 5 V                                                | 92         | 93   |            |      |  |

|                  | Signal-to-noise ratio <sup>(5)</sup>        |                                       | At 10 kHz, V <sub>REF</sub> = 5 V                                               |            | 93   |            | dB   |  |

|                  |                                             |                                       | At 100 kHz, V <sub>REF</sub> = 5 V                                              |            | 88.5 |            |      |  |

|                  |                                             |                                       | At 1 kHz, V <sub>REF</sub> = 5 V                                                |            | -108 |            |      |  |

| THD              | Total harmonic dis                          | stortion <sup>(5)(6)</sup>            | At 10 kHz, V <sub>REF</sub> = 5 V                                               |            | -108 |            | dB   |  |

|                  |                                             |                                       | At , V <sub>REF</sub> = 5 V                                                     |            | -101 |            |      |  |

|                  |                                             |                                       | At 1 kHz, V <sub>REF</sub> = 5 V                                                |            | 108  |            |      |  |

| SFDR             | Spurious-free dyn<br>range <sup>(5)</sup>   | amic                                  | At 10 kHz, V <sub>REF</sub> = 5 V                                               |            | 108  |            | dB   |  |

|                  | Tange                                       |                                       | At 100 kHz, V <sub>REF</sub> = 5 V                                              |            | 101  |            |      |  |

| BW_3dB           | –3-dB small-signa                           | l bandwidth                           |                                                                                 |            | 30   |            | MHz  |  |

| POWER            | -SUPPLY REQUIRE                             | MENTS                                 | +                                                                               |            |      |            |      |  |

|                  |                                             | AVDD                                  | Analog supply                                                                   | 2.7        | 3    | 3.6        |      |  |

|                  | Power-supply                                | Digital supply range for SULK > 40 IV | Digital supply range for SCLK > 40 MHz                                          | 2.7        | 3    | 3.6        | V    |  |

|                  | voltage                                     | DVDD                                  | Digital supply range for SCLK < 40 MHz                                          | 1.65       | 1.8  | 3.6        |      |  |

|                  | Supply current                              | AVDD                                  | 1-MHz sample rate, AVDD = 3 V                                                   |            | 1.8  | 2.4        | mA   |  |

|                  |                                             | ł                                     | 1-MHz sample rate, AVDD = 3 V                                                   |            | 5.5  | 7.2        |      |  |

| P <sub>VA</sub>  | Power dissipation                           |                                       | 100-kHz sample rate, AVDD = 3 V                                                 |            | 0.55 |            | mW   |  |

|                  |                                             |                                       | 10-kHz sample rate, AVDD = 3 V                                                  |            | 55   |            | μW   |  |

| IA <sub>PD</sub> | Device power-dov<br>current <sup>(7)</sup>  | vn                                    |                                                                                 |            | 50   |            | nA   |  |

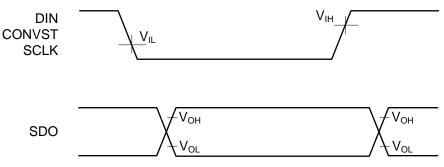

| DIGITAL          | INPUTS: LOGIC F                             | AMILY (CMC                            | DS)                                                                             |            |      |            |      |  |

|                  |                                             |                                       | 1.65 V < DVDD < 2.3 V                                                           | 0.8 × DVDD |      | DVDD + 0.3 |      |  |

| V <sub>IH</sub>  | High-level input ve                         | oltage                                | 2.3 V < DVDD < 3.6 V                                                            | 0.7 × DVDD |      | DVDD + 0.3 | V    |  |

|                  |                                             |                                       | 1.65 V < DVDD < 2.3 V                                                           | -0.3       |      | 0.2 × DVDD |      |  |

| VIL              | Low-level input vo                          | ltage                                 | 2.3 V < DVDD < 3.6 V                                                            | -0.3       |      | 0.3 × DVDD | V    |  |

| I <sub>LK</sub>  | Digital input leaka                         | ge current                            |                                                                                 |            | ±10  | ±100       | nA   |  |

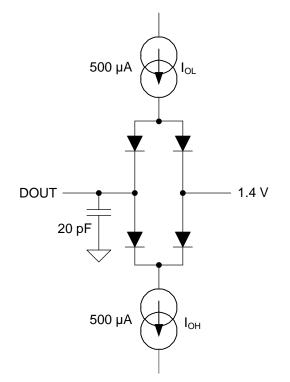

|                  | OUTPUTS: LOGIC                              | -                                     | MOS)                                                                            |            |      |            |      |  |

| V <sub>OH</sub>  | High-level output                           |                                       | $I_{O} = 500 \mu A$ source, $C_{LOAD} = 20 pF$                                  | 0.8 × DVDD |      | DVDD       | V    |  |

| V <sub>OL</sub>  | Low-level output voltage                    |                                       | $I_{O} = 500 \text{-}\mu\text{A} \text{ sink}, C_{\text{LOAD}} = 20 \text{ pF}$ | 0          |      | 0.2 × DVDD | V    |  |

|                  | RATURE RANGE                                |                                       |                                                                                 |            |      |            |      |  |

| T <sub>A</sub>   | Operating free-air temperature              |                                       |                                                                                 | -40        |      | 85         | °C   |  |

(5) All specifications expressed in decibels (dB) refer to the full-scale input (FSR) and are tested with an input signal 0.5 dB below full-scale, unless otherwise specified.

(6) Calculated on the first nine harmonics of the input frequency.

(7) The device automatically enters a power-down state at the end of every conversion, and remains in power-down during the acquisition phase.

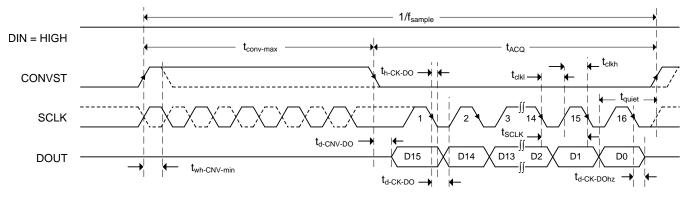

# 8.6 Timing Requirements: 3-Wire Operation

| all specifications are at AVDD = 3 V | DVDD = 3 V and over         | the operating free-air temperature | range (unless otherwise noted) |

|--------------------------------------|-----------------------------|------------------------------------|--------------------------------|

|                                      | , D , D , D = 0 , and 0 , 0 |                                    |                                |

|                         |                                                                               | MIN  | TYP MA |                      |

|-------------------------|-------------------------------------------------------------------------------|------|--------|----------------------|

| t <sub>ACQ</sub>        | Acquisition time                                                              | 290  |        | ns                   |

| t <sub>conv</sub>       | Conversion time                                                               | 500  | 7      | 10 ns                |

| 1/f <sub>sample</sub>   | Time between conversions                                                      | 1000 |        | ns                   |

| t <sub>wh-CNV</sub>     | Pulse duration: CONVST high                                                   | 10   |        | ns                   |

| f <sub>SCLK</sub>       | SCLK frequency                                                                |      | 66     | .6 MHz               |

| t <sub>SCLK</sub>       | SCLK period                                                                   | 15   |        | ns                   |

| t <sub>ciki</sub>       | SCLK low time                                                                 | 0.45 | 0.     | 55 t <sub>SCLK</sub> |

| t <sub>clkh</sub>       | SCLK high time                                                                | 0.45 | 0.     | 55 t <sub>SCLK</sub> |

| t <sub>h-CK-DO</sub>    | SCLK falling edge to current data invalid                                     | 3    |        | ns                   |

| t <sub>d-CK-DO</sub>    | SCLK falling edge to next data valid delay                                    |      | 13     | .4 ns                |

| t <sub>d-CNV-DO</sub>   | Enable time: CONVST low to MSB valid                                          |      | 12     | .3 ns                |

| t <sub>d-CNV-DOhz</sub> | Disable time: CONVST high or last SCLK falling edge to DOUT 3-state (CS mode) |      | 13     | .2 ns                |

| t <sub>quiet</sub>      | Quiet time                                                                    | 20   |        | ns                   |

# 8.7 Timing Requirements: 4-Wire Operation

all specifications are at AVDD = 3 V, DVDD = 3 V, and over the operating free-air temperature range (unless otherwise noted)

|                        |                                                                | MIN  | TYP MAX | UNIT |

|------------------------|----------------------------------------------------------------|------|---------|------|

| t <sub>ACQ</sub>       | Acquisition time                                               | 290  |         | ns   |

| t <sub>conv</sub>      | Conversion time                                                | 500  | 710     | ns   |

| 1/f <sub>sample</sub>  | Time between conversions                                       | 1000 |         | ns   |

| t <sub>wh-DI</sub>     | Pulse duration: DIN high                                       | 10   |         | ns   |

| t <sub>wl-CNV</sub>    | Pulse width: CONVST low                                        | 20   |         | ns   |

| t <sub>d-DI-DO</sub>   | Delay time: DIN low to MSB valid                               |      | 12.3    | ns   |

| t <sub>d-DI-DOhz</sub> | Delay time: DIN high or last SCLK falling edge to DOUT 3-state |      | 13.2    | ns   |

| t <sub>su-DI-CNV</sub> | Setup time: DIN high to CONVST rising edge                     | 7.5  |         | ns   |

| t <sub>h-DI-CNV</sub>  | Hold time: DIN high from CONVST rising edge (see Figure 61)    | 0    |         | ns   |

NSTRUMENTS

**EXAS**

# 8.8 Timing Requirements: Daisy-Chain

| all specifications are at AVDD = 3 V, DVDD = 3 V, and over the operating free-air temperature range (unless otherwise notec |                  |     |     |     |      |  |

|-----------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|--|

|                                                                                                                             |                  | MIN | TYP | MAX | UNIT |  |

| t <sub>ACQ</sub>                                                                                                            | Acquisition time | 290 |     |     | ns   |  |

|                                                                                                                             |                  |     |     |     | 1    |  |

| t <sub>conv</sub>      | Conversion time                                            | 500  | 710 | ns |

|------------------------|------------------------------------------------------------|------|-----|----|

| 1/f <sub>sample</sub>  | Time between conversions                                   | 1000 |     | ns |

| t <sub>su-CK-CNV</sub> | Setup time: SCLK valid to CONVST rising edge               | 5    |     | ns |

| t <sub>h-CK-CNV</sub>  | Hold time: SCLK valid from CONVST rising edge              | 5    |     | ns |

| t <sub>su-DI-CNV</sub> | Setup time: DIN low to CONVST rising edge (see Figure 2)   | 7.5  |     | ns |

| t <sub>h-DI-CNV</sub>  | Hold time: DIN low from CONVST rising edge (see Figure 61) | 0    |     | ns |

| t <sub>su-DI-CK</sub>  | Setup time: DIN valid to SCLK falling edge                 | 1.5  |     | ns |

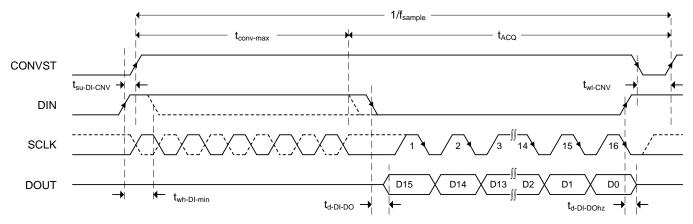

NOTE: Figure 1 shows the timing diagram for the 3-Wire CS Mode Without a Busy Indicator interface option. However, the timing parameters specified in *Timing Requirements: 3-Wire Operation* table are also applicable for the 3-Wire CS Mode With a Busy Indicator interface option, unless otherwise specified; see the Device Functional Modes section for specific details for each interface option.

Figure 2. 4-Wire Operation: DIN Functions as Chip Select

NOTE: Figure 2 shows the timing diagram for the 4-Wire CS Mode Without a Busy Indicator interface option. However, the timing parameters specified in *Timing Requirements:* 4-Wire Operation table are also applicable for the 4-Wire CS Mode With a Busy Indicator interface option, unless otherwise specified; see the Device Functional Modes section for specific details for each interface option.

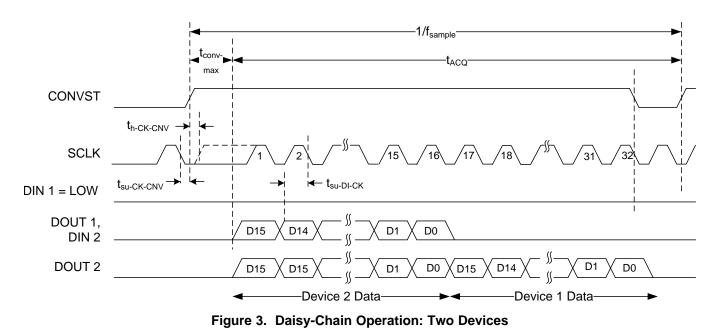

NOTE: Figure 3 shows the timing diagram for the *Daisy-Chain Mode Without a Busy Indicator* interface option. However, the timing parameters specified in *Timing Requirements: Daisy-Chain* table are also applicable for the *Daisy-Chain Mode With a Busy Indicator* interface option, unless otherwise specified; see the *Device Functional Modes* section for specific details for each interface option.

Copyright © 2013–2019, Texas Instruments Incorporated

**INSTRUMENTS**

Texas

ADS8860 JAJSH03B – MAY 2013 – REVISED FEBRUARY 2019

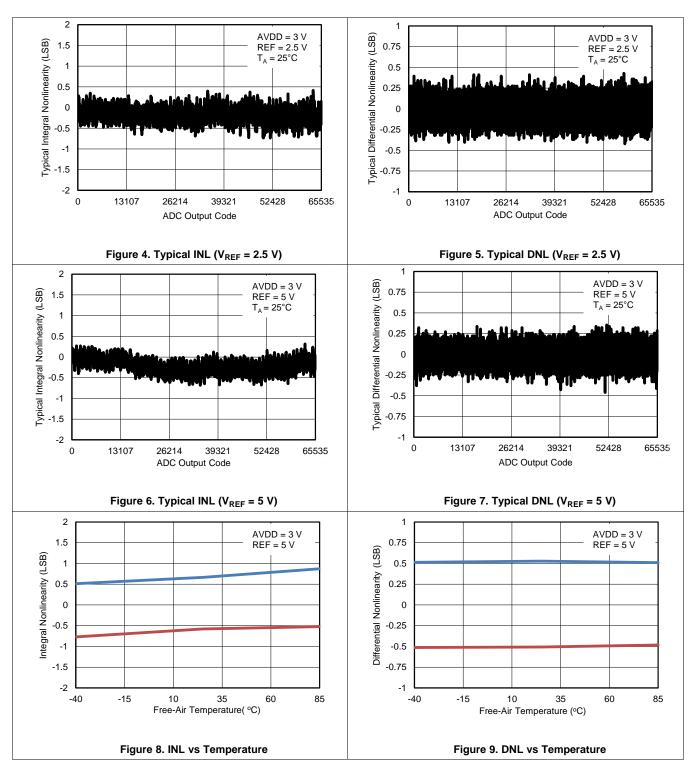

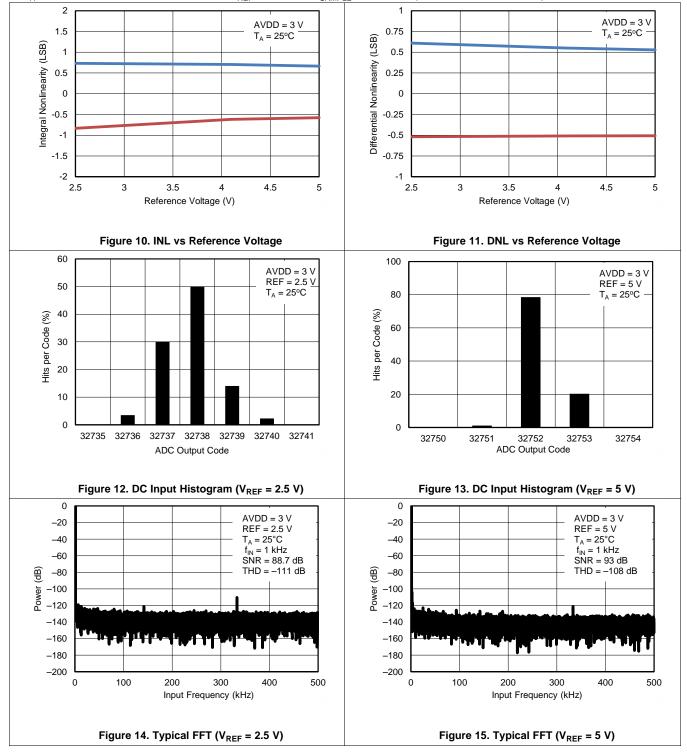

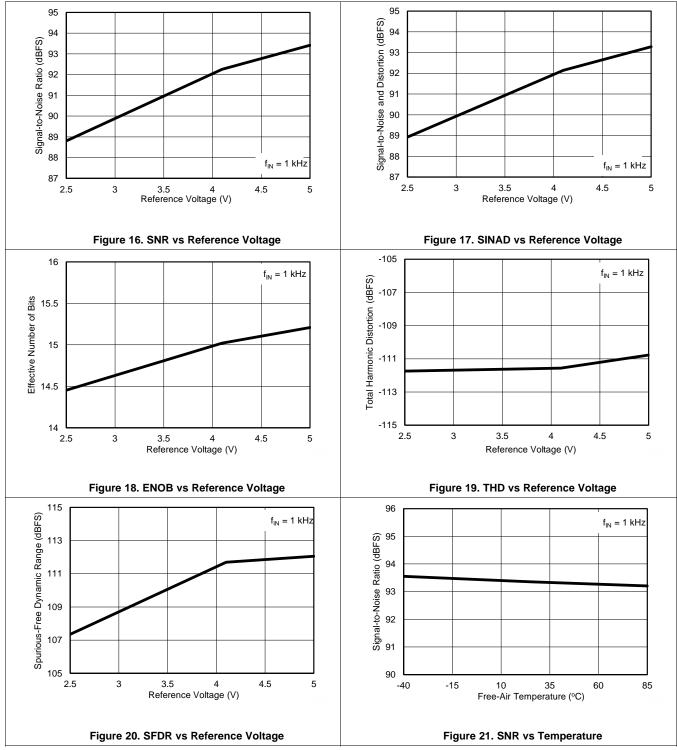

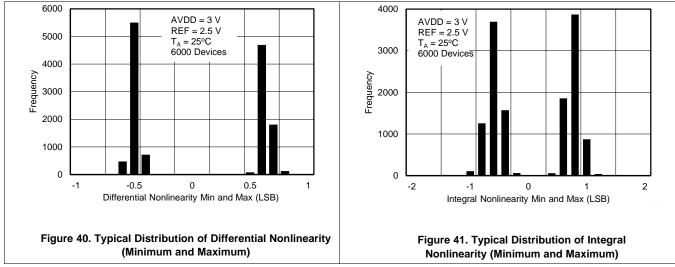

# 8.9 Typical Characteristics

at  $T_A = 25$ °C, AVDD = 3 V, DVDD = 3 V,  $V_{REF} = 5$  V, and  $f_{SAMPLE} = 1$  MSPS (unless otherwise noted)

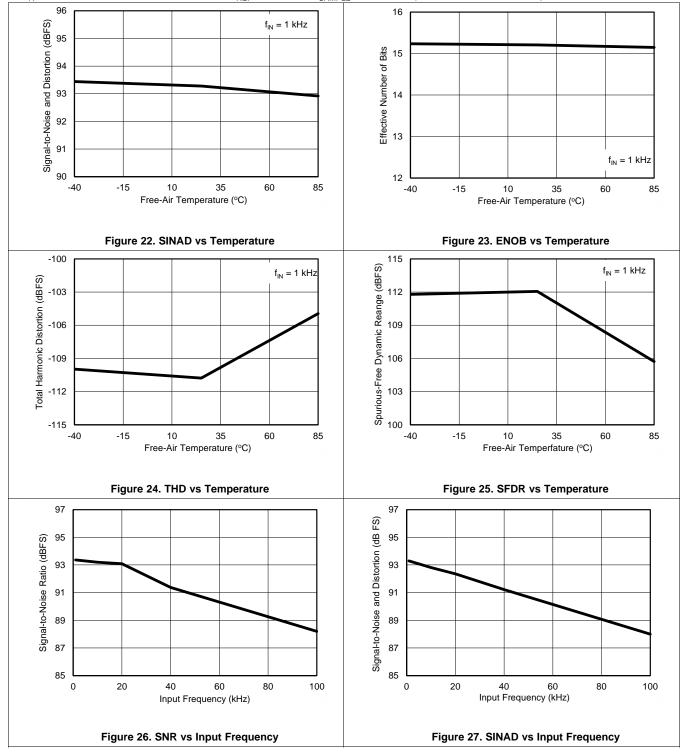

#### **Typical Characteristics (continued)**

ADS8860 JAJSH03B – MAY 2013 – REVISED FEBRUARY 2019

www.ti.com

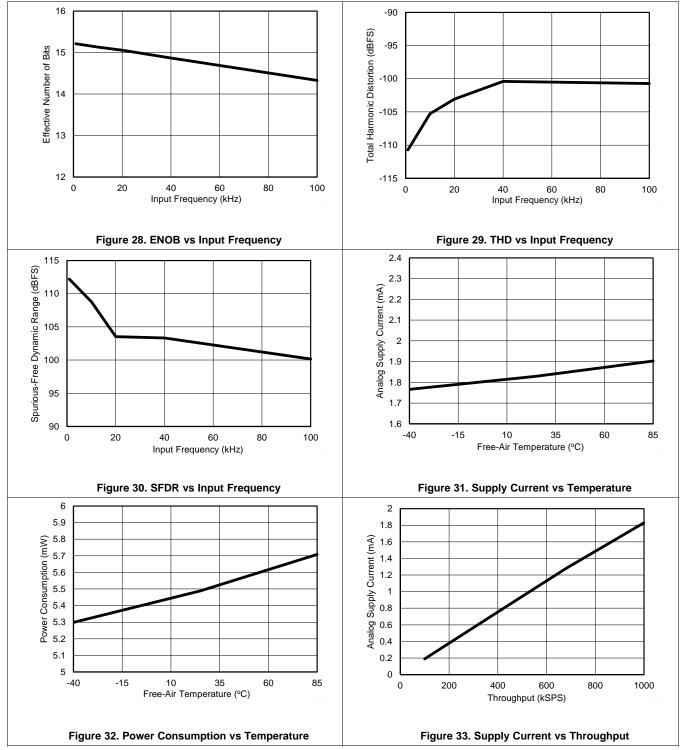

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

ADS8860 JAJSH03B – MAY 2013 – REVISED FEBRUARY 2019

www.ti.com

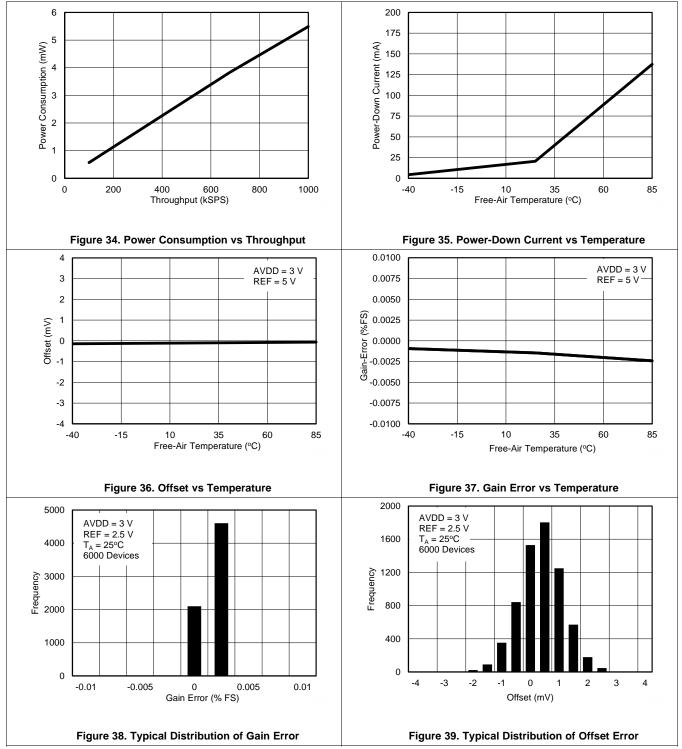

# **Typical Characteristics (continued)**

#### **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

# 9 Parameter Measurement Information

# 9.1 Equivalent Circuits

Figure 42. Load Circuit for Digital Interface Timing

Figure 43. Voltage Levels for Timing

TEXAS INSTRUMENTS

www.ti.com

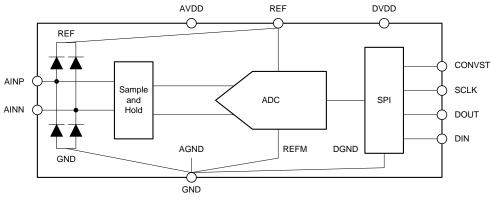

# **10** Detailed Description

#### 10.1 Overview

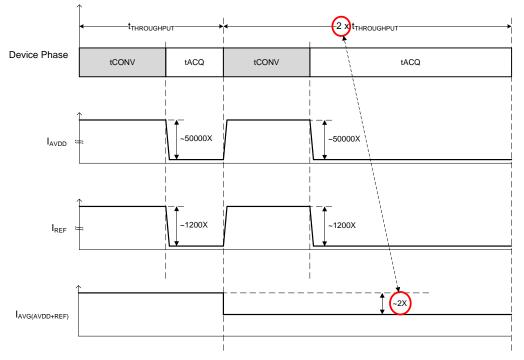

The ADS8860 is a high-speed, successive approximation register (SAR), analog-to-digital converter (ADC) from a 16- and 18-bit device family. This compact device features high performance. Power consumption is inherently low and scales linearly with sampling speed. The architecture is based on charge redistribution that inherently includes a sample-and-hold (S/H) function.

The ADS8860 supports a single-ended analog input across two pins (INP and INN). When a conversion is initiated, the differential input on these pins is sampled on the internal capacitor array. While a conversion is in progress, both the INP and INN inputs are disconnected from the internal circuit.

The ADS8860 uses an internal clock to perform conversions. The device reconnects the sampling capacitors to the INP and INN pins after conversion and then enters an acquisition phase. During the acquisition phase, the device is powered down and the conversion result can be read.

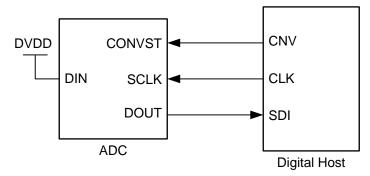

The device digital output is available in SPI-compatible format, thus making interfacing with microprocessors, digital signal processors (DSPs), or field-programmable gate arrays (FPGAs) easy.

#### **10.2 Functional Block Diagram**

Figure 44 shows the detailed functional block diagram for the device.

Figure 44. Detailed Block Diagram

#### **10.3 Feature Description**

#### 10.3.1 Analog Input

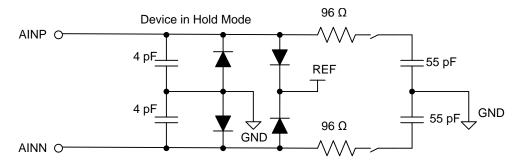

As shown in Figure 44, the device features a single-ended analog input. AINP can swing from GND – 0.1 V to  $V_{REF}$  + 0.1 V and AINN can swing from GND – 0.1 V to GND + 0.1 V. Both positive and negative inputs are individually sampled on 55-pF sampling capacitors and the device converts for the voltage difference between the two sampled values:  $V_{INP} - V_{INN}$ . The single-ended signal range is 0 V to  $V_{REF}$ .

#### Feature Description (continued)

Figure 45 shows an equivalent circuit of the input sampling stage. The sampling switch is represented by a 96- $\Omega$  resistance in series with the ideal switch; see the *ADC Input Driver* section for more details on the recommended driving circuits.

Figure 45. Input Sampling Stage Equivalent Circuit

Figure 44 and Figure 45 illustrate electrostatic discharge (ESD) protection diodes to REF and GND from both analog inputs. Make sure that these diodes do not turn on by keeping the analog inputs within the specified range.

#### 10.3.2 Reference

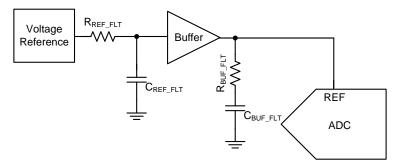

The device operates with an external reference voltage and switches binary-weighted capacitors onto the reference terminal (REF pin) during the conversion process. The switching frequency is proportional to the internal conversion clock frequency but the dynamic charge requirements are a function of the absolute value of the input voltage and reference voltage. This dynamic load must be supported by a reference driver circuit without degrading the noise and linearity performance of the device. During the acquisition process, the device automatically powers down and does not take any dynamic current from the external reference source. The basic circuit diagram for such a reference driver circuit for precision ADCs is shown in Figure 46; see the *ADC Reference Driver* section for more details on the application circuits.

Figure 46. Reference Driver Schematic

#### 10.3.3 Clock

The device uses an internal clock for conversion. Conversion duration may vary but is bounded by the minimum and maximum value of  $t_{conv}$ , as specified in the *Timing Requirements* section. An external SCLK is only used for a serial data read operation. Data are read after a conversion completes and when the device is in acquisition phase for the next sample.

#### Feature Description (continued)

#### 10.3.4 ADC Transfer Function

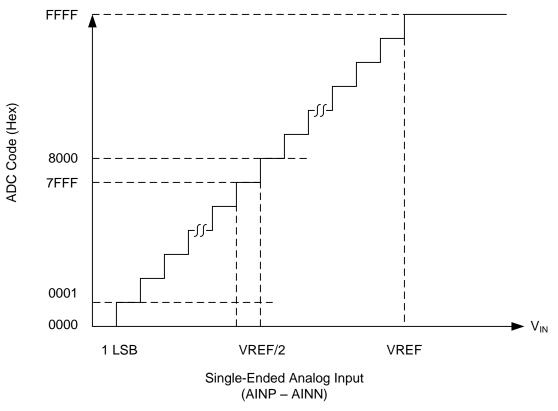

The ADS8860 is a unipolar, single-ended input device. The device output is in straight binary format.

Figure 47 shows ideal characteristics for the device. The full-scale range for the ADC input (AINP – AINN) is equal to the reference input voltage to the ADC ( $V_{REF}$ ). One LSB is equal to [( $V_{REF}$  / 2<sup>16</sup>)].

Figure 47. Single-Ended Transfer Characteristics

#### **10.4 Device Functional Modes**

The ADS8860 is a low pin-count device. However, the device offers six different options for interfacing with the digital host.

These options can be broadly classified as being either  $\overline{CS}$  mode (in either a 3- or 4-wire interface) or daisychain mode. The device operates in  $\overline{CS}$  mode if DIN is high at the CONVST rising edge. If DIN is low at the CONVST rising edge, or if DIN and CONVST are connected together, the device operates in daisy-chain mode. In both modes, the device can either operate with or without a *busy indicator*, where the busy indicator is a bit preceding the output data bits that can be used to interrupt the digital host and trigger the data transfer.

The 3-wire interface in  $\overline{CS}$  mode is useful for applications that need galvanic isolation on-board. The 4-wire interface in  $\overline{CS}$  mode allows the user to sample the analog input independent of the serial interface timing and, therefore, allows easier control of an individual device while having multiple, similar devices on-board. The daisy-chain mode is provided to hook multiple devices in a chain similar to a shift register and is useful in reducing component count and the number of signal traces on the board.

#### 10.4.1 CS Mode

CS mode is selected <u>if DIN</u> is high at the CONVST rising edge. <u>There are six different interface options available</u> in this mode: 3-wire CS mode without a busy indicator, 3-wire CS mode with a busy indicator, 4-wire CS mode without a busy indicator, and 4-wire CS mode with a busy indicator. The following sections discuss these interface options in detail.

#### ADS8860 JAJSH03B – MAY 2013 – REVISED FEBRUARY 2019

#### www.ti.com

#### **Device Functional Modes (continued)**

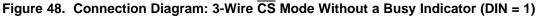

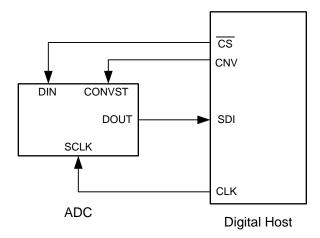

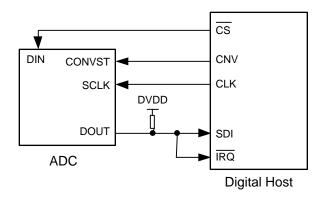

#### 10.4.1.1 3-Wire CS Mode Without a Busy Indicator

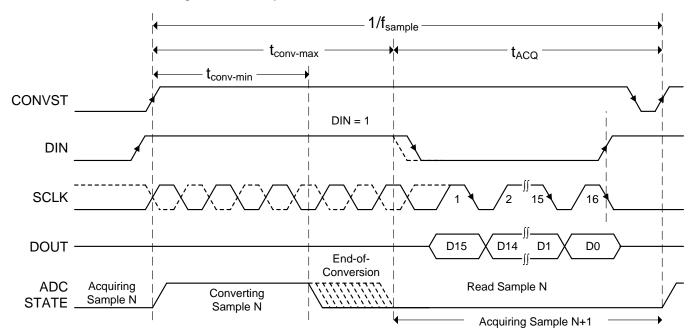

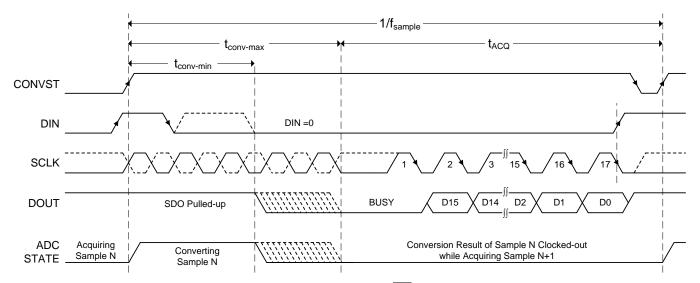

This interface option is most useful when a single ADC is connected to an SPI-compatible digital host. In this interface option, DIN can be connected to DVDD and CONVST functions as  $\overline{CS}$  (as shown in Figure 48). As shown in Figure 49, a CONVST rising edge forces DOUT to 3-state, samples the input signal, and causes the device to enter a conversion phase. Conversion is done with the internal clock and continues regardless of the state of CONVST. As a result, CONVST (functioning as  $\overline{CS}$ ) can be pulled low after the start of the conversion to select other devices on the board. However, CONVST must return high before the minimum conversion time ( $t_{conv-min}$ ) elapses and is held high until the maximum possible conversion time ( $t_{conv-max}$ ) elapses. A high level on CONVST at the end of the conversion ensures the device does not generate a busy indicator.

Figure 49. Interface Timing Diagram: 3-Wire  $\overline{CS}$  Mode Without a Busy Indicator (DIN = 1)

When conversion is complete, the device enters an acquisition phase and powers down. CONVST (functioning as  $\overline{CS}$ ) can be brought low after the maximum conversion time ( $t_{conv-max}$ ) elapses. On the CONVST falling edge, DOUT comes out of 3-state and the device outputs the MSB of the data. The lower data bits are output on subsequent SCLK falling edges. Fast sampling rates require high frequency SCLK and data must be read at SCLK falling edges. For slow sampling rates and SCLK frequency  $\leq$  36 MHz, data can be read at either SCLK falling or rising edges. Note that with any SCLK frequency, reading data at SCLK falling edge requires the digital host to clock in the data during the  $t_{h_cck_DO-min}$  time frame. DOUT goes to 3-state after the 16th SCLK falling edge or when CONVST goes high, whichever occurs first.

#### **Device Functional Modes (continued)**

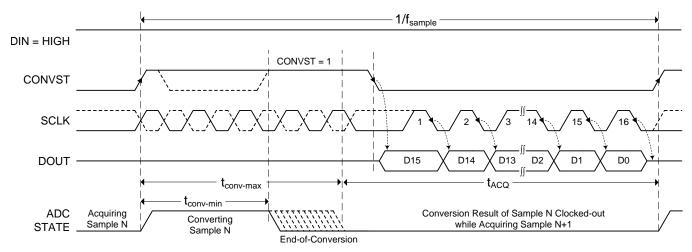

#### 10.4.1.2 3-Wire CS Mode With a Busy Indicator

This interface option is most useful when a single ADC is connected to an SPI-compatible digital host and an interrupt-driven data transfer is desired. In this interface option, DIN can be connected to DVDD and CONVST functions as  $\overline{CS}$  (as shown in Figure 50). The pull-up resistor on the DOUT pin ensures that the IRQ pin of the digital host is held high when DOUT goes to 3-state. As shown in Figure 51, a CONVST rising edge forces DOUT to 3-state, samples the input signal, and causes the device to enter a conversion phase. Conversion is done with the internal clock and continues regardless of the state of CONVST. As a result, CONVST (functioning as  $\overline{CS}$ ) can be pulled low after the start of the conversion to select other devices on the board. However, CONVST must be pulled low before the minimum conversion time ( $t_{conv-min}$ ) elapses and must remain low until the maximum possible conversion time ( $t_{conv-max}$ ) elapses. A low level on the CONVST input at the end of a conversion ensures the device generates a busy indicator.

Figure 51. Interface Timing Diagram: 3-Wire CS Mode With a Busy Indicator (DIN = 1)

When conversion is complete, the device enters an acquisition phase and powers down, DOUT comes out of 3state, and the device out<u>puts</u> a busy indicator bit (low level) on the DOUT pin. This configuration provides a highto-low transition on the IRQ pin of the digital host. The data bits are clocked out, MSB first, on the subsequent SCLK falling edges. Fast sampling rates require high frequency SCLK and data must be read at SCLK falling edges. For slow sampling rates and SCLK frequency  $\leq$  36 MHz, data can be read at either SCLK falling or rising edges. Note that with any SCLK frequency, reading data at SCLK falling edge requires the digital host to clock in the data during the t<sub>h\_CK\_DO-min</sub> time frame. DOUT goes to 3-state after the 17th SCLK falling edge or when CONVST goes high, whichever occurs first.

#### **Device Functional Modes (continued)**

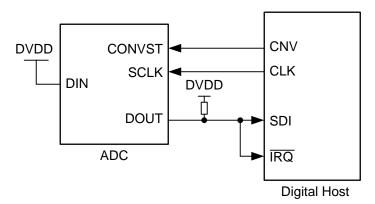

#### 10.4.1.3 4-Wire CS Mode Without a Busy Indicator

This interface option is useful when one or more ADCs are connected to an SPI-compatible digital host. Figure 52 shows the connection diagram for single ADC; see Figure 54 for the connection diagram for two ADCs.

Figure 52. Connection Diagram: Single ADC With 4-Wire CS Mode Without a Busy Indicator

In this interface option, DIN is controlled by the digital host and functions as  $\overline{CS}$ . As shown in Figure 53, with DIN high, a CONVST rising edge selects  $\overline{CS}$  mode, forces DOUT to 3-state, samples the input signal, and causes the device to enter a conversion phase. In this interface option, CONVST must be held at a high level from the start of the conversion until all data bits are read. Conversion is done with the internal clock and continues regardless of the state of DIN. As a result, DIN (functioning as  $\overline{CS}$ ) can be pulled low to select other devices on the board. However, DIN must be pulled high before the minimum conversion time ( $t_{conv-min}$ ) elapses and remains high until the maximum possible conversion time ( $t_{conv-max}$ ) elapses. A high level on DIN at the end of the conversion ensures the device does not generate a busy indicator.

Figure 53. Interface Timing Diagram: Single ADC With 4-Wire CS Mode Without a Busy Indicator

When conversion is complete, the device enters acquisition phase and powers down. DIN (functioning as  $\overline{CS}$ ) can be brought low after the maximum conversion time ( $t_{conv-max}$ ) elapses. On the DIN falling edge, DOUT comes out of 3-state and the device outputs the MSB of the data. The lower data bits are output on subsequent SCLK falling edges. Fast sampling rates require high frequency SCLK and data must be read at SCLK falling edges. For slow sampling rates and SCLK frequency  $\leq$  36 MHz, data can be read at either SCLK falling or rising edges. Note that with any SCLK frequency, reading data at SCLK falling edge requires the digital host to clock in the data during the  $t_{h_{CK_DO-min}}$  time frame. DOUT goes to 3-state after the 16th SCLK falling edge or when DIN goes high, whichever occurs first.

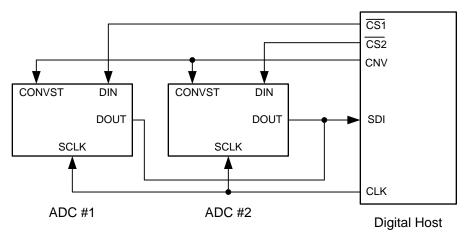

As shown in Figure 54, multiple devices can be hooked together on the same data bus. In this case, as shown in Figure 55, the DIN of the second device (functioning as CS for the second device) can go low after the first device data are read and the DOUT of the first device is in 3-state.

Care must be taken so that CONVST and DIN are not both low together at any time during the cycle.

Figure 54. Connection Diagram: Two ADCs With 4-Wire CS Mode Without a Busy Indicator

Figure 55. Interface Timing Diagram: Two ADCs With 4-Wire CS Mode Without a Busy Indicator

#### **Device Functional Modes (continued)**

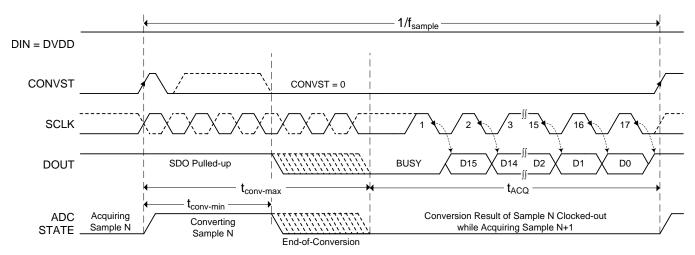

#### 10.4.1.4 4-Wire CS Mode With a Busy Indicator

This interface option is most useful when a single ADC is connected to an SPI-compatible digital host and an interrupt-driven data transfer is desired. In this interface option, the analog sample is least affected by clock jitter because the CONVST signal (used to sample the input) is independent of the data read operation. In this interface option, DIN is controlled by the digital host and functions as  $\overline{CS}$  (as shown in Figure 56). The pull-up resistor on the DOUT pin ensures that the IRQ pin of the digital host is held high when DOUT goes to 3-state. As shown in Figure 57, when DIN is high, a CONVST rising edge selects  $\overline{CS}$  mode, forces DOUT to 3-state, samples the input signal, and causes the device to enter a conversion phase. In this interface option, CONVST must be held high from the start of the conversion until all data bits are read. Conversion is done with the internal clock and continues regardless of the state of DIN. As a result, DIN (acting as  $\overline{CS}$ ) can be pulled low to select other devices on the board. However, DIN must be pulled low before the minimum conversion time ( $t_{conv-min}$ ) elapses and remains low until the maximum possible conversion time ( $t_{conv-max}$ ) elapses. A low level on the DIN input at the end of a conversion ensures the device generates a busy indicator.

Figure 56. Connection Diagram: 4-Wire CS Mode With a Busy Indicator

Figure 57. Interface Timing Diagram: 4-Wire CS Mode With a Busy Indicator

When conversion is complete, the device enters an acquisition phase and powers down, DOUT comes out of 3state, and the device outputs a busy indicator bit (low level) on the DOUT pin. This configuration provides a highto-low transition on the IRQ pin of the digital host. The data bits are clocked out, MSB first, on the subsequent SCLK falling edges. Fast sampling rates require high frequency SCLK and data must be read at SCLK falling edges. For slow sampling rates and SCLK frequency  $\leq$  36 MHz, data can be read at either SCLK falling or rising edges. Note that with any SCLK frequency, reading data at SCLK falling edge requires the digital host to clock in the data during the  $t_{h_{CK_{DO-min}}}$  time frame. DOUT goes to 3-state after the 17th SCLK falling edge or when DIN goes high, whichever occurs first. Care must be taken so that CONVST and DIN are not both low together at any time during the cycle.

#### 10.4.2 Daisy-Chain Mode

Daisy-chain mode is selected if <u>DIN</u> is low at the time of a CONVST rising edge or if DIN and CONVST are connected together. Similar to  $\overline{CS}$  mode, this mode features operation with or without a busy indicator. The following sections discuss these interface modes in detail.

#### 10.4.2.1 Daisy-Chain Mode Without a Busy Indicator

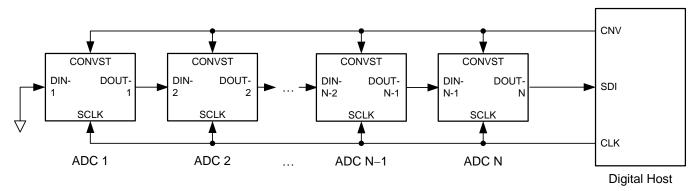

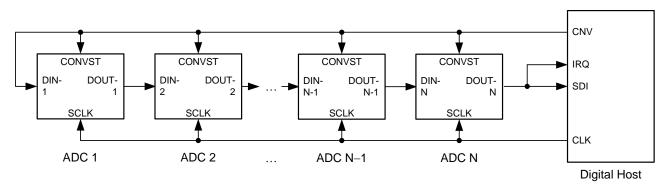

This interface option is most useful in applications where multiple ADC devices are used but the digital host has limited interfacing capability. Figure 58 shows a connection diagram with *N* ADCs connected in the daisy-chain. The CONVST pins of all ADCs in the chain are connected together and are controlled by a single pin of the digital host. Similarly, the SCLK pins of all ADCs in the chain are connected together and are controlled by a single pin of the digital host. The DIN pin for ADC 1 (DIN-1) is connected to GND. The DOUT pin of ADC 1 (DOUT-1) is connected to the DIN pin of ADC 2 (DIN-2), and so on. The DOUT pin of the last ADC in the chain (DOUT-N) is connected to the SDI pin of the digital host.

Figure 58. Connection Diagram: Daisy-Chain Mode Without a Busy Indicator (DIN = 0)

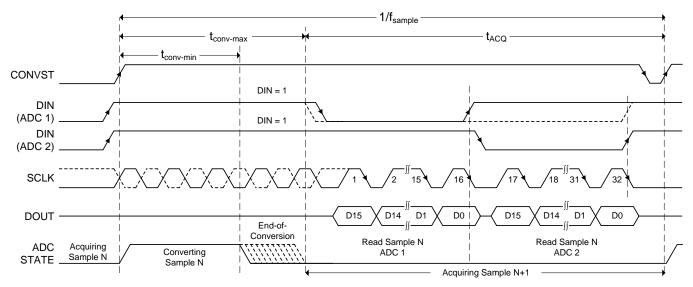

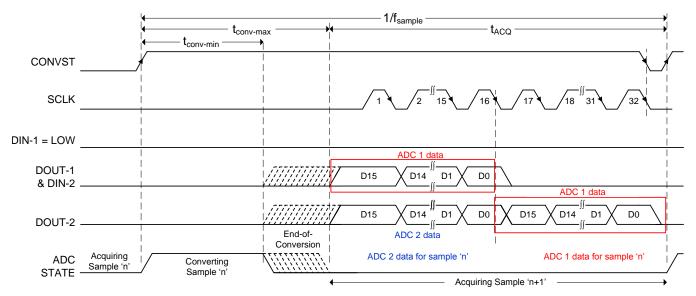

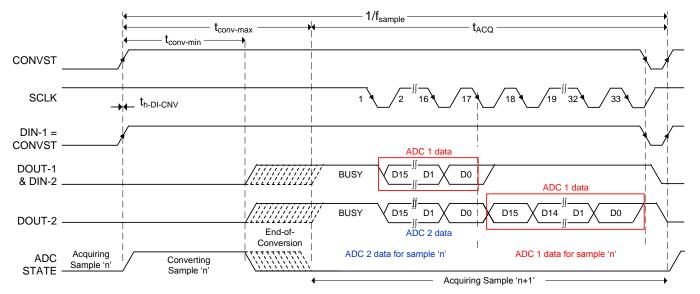

As shown in Figure 59, the device DOUT pin is driven low when DIN and CONVST are low together. With DIN low, a CONVST rising edge selects daisy-chain mode, samples the analog input, and causes the device to enter a conversion phase. In this interface option, CONVST must remain high from the start of the conversion until all data bits are read. When started, the conversion continues regardless of the state of SCLK, however SCLK must be low at the CONVST rising edge so that the device does not generate a busy indicator at the end of the conversion.

Figure 59. Interface Timing Diagram: For Two Devices in Daisy-Chain Mode Without a Busy Indicator

At the end of conversion, every ADC in the chain loads its own conversion result into the internal, 16-bit, shift register and also outputs the MSB bit of this conversion result on its own DOUT pin. All ADCs enter an acquisition phase and power-down. On every subsequent SCLK falling edge, the internal shift register of each ADC latches the data available on its DIN pin and shifts out the next bit of data on its DOUT pin. Therefore, the digital host receives the data of ADC N, followed by the data of ADC N–1, and so on (in MSB-first fashion). A total of 16 x N SCLK falling edges are required to capture the outputs of all N devices in the chain. Fast sampling rates require high frequency SCLK and data must be read at SCLK falling edges. For slow sampling rates and SCLK frequency  $\leq$  36 MHz, data can be read at either SCLK falling or rising edges. Note that with any SCLK frequency, reading data at SCLK falling edge requires the digital host to clock in the data during the  $t_{h_{CK_DO-min}}$  time frame.

# 10.4.2.2 Daisy-Chain Mode With a Busy Indicator

This interface option is most useful in applications where multiple ADC devices are used but the digital host has limited interfacing capability and an interrupt-driven data transfer is desired. Figure 60 shows a connection diagram with *N* ADCs connected in the daisy-chain. The CONVST pins of all ADCs in the chain are connected together and are controlled by a single pin of the digital host. Similarly, the SCLK pins of all ADCs in the chain are connected together and are controlled by a single pin of the digital host. The DIN pin for ADC 1 (DIN-1) is connected to its CONVST. The DOUT pin of ADC 1 (DOUT-1) is connected to the DIN pin of ADC 2 (DIN-2), and so on. The DOUT pin of the last ADC in the chain (DOUT-N) is connected to the SDI and IRQ pins of the digital host.

Figure 60. Connection Diagram: Daisy-Chain Mode With a Busy Indicator (DIN = 0)

As shown in Figure 61, the device DOUT pin is driven low when DIN and CONVST are low together. A CONVST rising edge selects daisy-chain mode, samples the analog input, and causes the device to enter a conversion phase. In this interface option, CONVST must remain high from the start of the conversion until all data bits are read. When started, the conversion continues regardless of the state of SCLK, however SCLK must be high at the CONVST rising edge so that the device generates a busy indicator at the end of the conversion.

Figure 61. Interface Timing Diagram: For Two Devices in Daisy-Chain Mode With a Busy Indicator

At the end of conversion, every ADC in the chain loads its own conversion result into the internal, 16-bit, shift register and also forces its DOUT pin high, thereby providing a low-to-high transition on the IRQ pin of the digital host. All ADCs enter an acquisition phase and power-down. On every subsequent SCLK falling edge, the internal shift register of each ADC latches the data available on its DIN pin and shifts out the next bit of data on its DOUT pin. Therefore, the digital host receives the interrupt signal followed by the data of ADC N followed by the data of ADC N–1, and so on (in MSB-first fashion). A total of  $(16 \times N) + 1$  SCLK falling edges are required to capture the outputs of all *N* devices in the chain. Fast sampling rates require a high-frequency SCLK and data must be read at the SCLK falling edges. For slow sampling rates and SCLK frequency  $\leq$  36 MHz, data can be read at either SCLK falling or rising edges. With any SCLK frequency, reading data at the SCLK falling edge requires the digital host to clock in the data during the t<sub>h\_CK\_DO-min</sub> time frame. The busy indicator bits of ADC 1 to ADC N–1 do not propagate to the next device in the chain.

#### NOTE

For SCLK  $\leq$  36 MHz, SPI mode-3 (CPOL = 1, CPHA = 1) allows reading the conversion results of N ADCs in 18 × N SCLK cycles because the busy indicator bit is not clocked in by the host.

TEXAS INSTRUMENTS

www.ti.com

### **11** Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### **11.1** Application Information

The two primary circuits required to maximize the performance of a high-precision, successive approximation register (SAR), analog-to-digital converter (ADC) are the input driver and the reference driver circuits. This section details some general principles for designing these circuits, followed by some application circuits designed using the ADS8860.

#### 11.1.1 ADC Reference Driver

The external reference source to the ADS8860 must provide low-drift and very accurate voltage for the ADC reference input and support the dynamic charge requirements without affecting the noise and linearity performance of the device. The output broadband noise of most references can be in the order of a few hundred  $\mu V_{RMS}$ . Therefore, to prevent any degradation in the noise performance of the ADC, the output of the voltage reference must be appropriately filtered by using a low-pass filter with a cutoff frequency of a few hundred hertz.

After band-limiting the noise of the reference circuit, the next important step is to design a reference buffer that can drive the dynamic load posed by the reference input of the ADC. The reference buffer must regulate the voltage at the reference pin such that the value of  $V_{REF}$  stays within the 1-LSB error at the start of each conversion. This condition necessitates the use of a large capacitor,  $C_{BUF\_FLT}$  (see Figure 46) for regulating the voltage at the reference input of the ADC. The amplifier selected to drive the reference pin must have an extremely low offset and temperature drift with a low output impedance to drive the capacitor at the ADC reference pin without any stability issues.

#### 11.1.2 ADC Input Driver

The input driver circuit for a high-precision ADC mainly consists of two parts: a driving amplifier and a fly-wheel RC filter. The amplifier is used for signal conditioning of the input voltage and its low output impedance provides a buffer between the signal source and the switched capacitor inputs of the ADC. The RC filter helps attenuate the sampling charge injection from the switched-capacitor input stage of the ADC and functions as an antialiasing filter to band-limit the wideband noise contributed by the front-end circuit. Careful design of the front-end circuit is critical to meet the linearity and noise performance of a high-precision, 16-bit ADC such as the ADS8860.

#### 11.1.2.1 Input Amplifier Selection

Selection criteria for the input amplifiers is highly dependent on the input signal type as well as the performance goals of the data acquisition system. Some key amplifier specifications to consider while selecting an appropriate amplifier to drive the inputs of the ADC are:

• Small-signal bandwidth. Select the small-signal bandwidth of the input amplifiers to be as high as possible after meeting the power budget of the system. Higher bandwidth reduces the closed-loop output impedance of the amplifier, thus allowing the amplifier to more easily drive the low cutoff frequency RC filter (see the *Antialiasing Filter* section) at the inputs of the ADC. Higher bandwidth also minimizes the harmonic distortion at higher input frequencies. In order to maintain the overall stability of the input driver circuit, select the amplifier bandwidth as described in Equation 1:

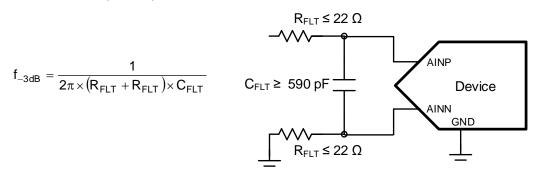

$$Unity - Gain \ Bandwidth \ge 4 \times \left(\frac{1}{2\pi \times (R_{FLT} + R_{FLT}) \times C_{FLT}}\right)$$

(1)

Noise. Noise contribution of the front-end amplifiers must be as low as possible to prevent any degradation in SNR performance of the system. As a rule of thumb, to ensure that the noise performance of the data acquisition system is not limited by the front-end circuit, the total noise contribution from the front-end circuit must be kept below 20% of the input-referred noise of the ADC. Noise from the input driver circuit is bandlimited by designing a low cutoff frequency RC filter, as explained in Equation 2.

(2)

(3)

#### **Application Information (continued)**

$$N_{G} \times \sqrt{2} \times \sqrt{\left(\frac{V_{j_{f}-AMP_{PP}}}{6.6}\right)^{2} + e_{n_{RMS}}^{2} \times \frac{\pi}{2} \times f_{-3dB}} \quad \leq \quad \frac{1}{5} \times \frac{V_{REF}}{\sqrt{2}} \times 10^{-\left(\frac{SNR(dB)}{20}\right)}$$

where:

- $V_{1/f AMP PP}$  is the peak-to-peak flicker noise in  $\mu V$ ,

- $e_{n RMS}$  is the amplifier broadband noise density in nV/ $\sqrt{Hz}$ ,

- $f_{-3dB}$  is the 3-dB bandwidth of the RC filter, and

- N<sub>G</sub> is the noise gain of the front-end circuit, which is equal to 1 in a buffer configuration.

- *Distortion.* Both the ADC and the input driver introduce nonlinearity in a data acquisition block. As a rule of thumb, to ensure that the distortion performance of the data acquisition system is not limited by the front-end circuit, the distortion of the input driver must be at least 10 dB lower than the distortion of the ADC, as shown in Equation 3.

$$\mathsf{THD}_{\mathsf{AMP}} \leq \mathsf{THD}_{\mathsf{ADC}} - 10 \, (\mathsf{dB})$$

Settling Time. For dc signals with fast transients that are common in a multiplexed application, the input signal

must settle within an 16-bit accuracy at the device inputs during the acquisition time window. This condition is

critical to maintain the overall linearity performance of the ADC. Typically, the amplifier data sheets specify

the output settling performance only up to 0.1% to 0.001%, which may not be sufficient for the desired

accuracy. Therefore, always verify the settling behavior of the input driver by TINA<sup>™</sup>-SPICE simulations

before selecting the amplifier.

#### 11.1.2.2 Charge-Kickback Filter

The charge-kickback filter is an RC filter at the input pins of the ADC that filters the broadband noise from the front-end drive circuitry and attenuates the sampling charge injection from the switched-capacitor input stage of the ADC. As shown in Figure 62, a filter capacitor ( $C_{FLT}$ ) is connected from each input pin of the ADC to ground. This capacitor helps reduce the sampling charge injection and provides a charge bucket to quickly charge the internal sample-and-hold capacitors during the acquisition process. Generally, the value of this capacitor must be at least 20 times the specified value of the ADC sampling capacitance. For the ADS8860, the input sampling capacitance is equal to 59 pF; therefore, for optimal performance, keep  $C_{FLT}$  greater than 590 pF. This capacitor must be a COG- or NPO-type. The type of dielectric used in COG or NPO ceramic capacitors provides the most stable electrical properties over voltage, frequency, and temperature changes.

Driving capacitive loads can degrade the phase margin of the input amplifier, thus making the amplifier marginally unstable. To avoid amplifier stability issues, series isolation resistors ( $R_{FLT}$ ) are used at the output of the amplifiers. A higher value of  $R_{FLT}$  helps with amplifier stability, but adds distortion as a result of interactions with the nonlinear input impedance of the ADC. Distortion increases with source impedance, input signal frequency, and input signal amplitude. Therefore, the selection of  $R_{FLT}$  requires balancing the stability of the driver amplifier and distortion performance of the design. Always verify the stability and settling behavior of the driving amplifier and charge-kickback filter by a TINA-TI<sup>TM</sup> SPICE simulation. Keep the tolerance of the selected resistors less than 1% to keep the inputs balanced.

Figure 62. Charge-Kickback Filter

#### Application Information (continued)

This section describes some common application circuits using the ADS8860. These data acquisition (DAQ) blocks are optimized for specific input types and performance requirements of the system. For simplicity, power-supply decoupling capacitors are not shown in these circuit diagrams; see the *Power-Supply Decoupling* section for suggested guidelines.

# **11.2 Typical Applications**

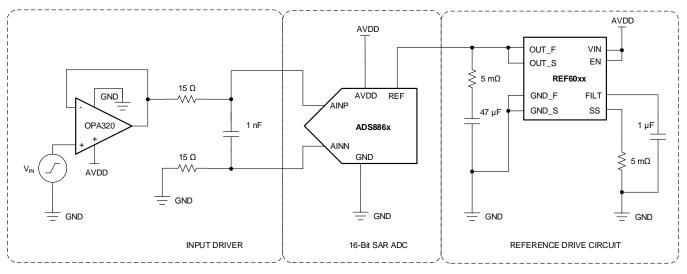

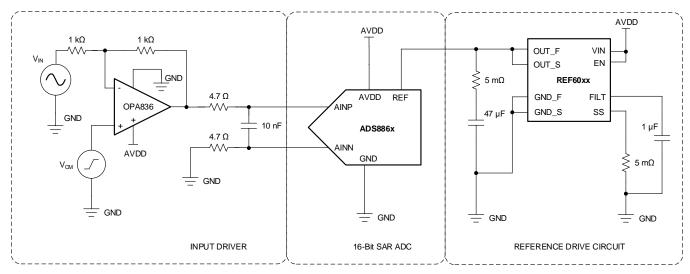

#### 11.2.1 DAQ Circuit for a 1-µs, Full-Scale Step Response

Figure 63. DAQ Circuit for a 1-µs, Full-Scale Step Response

#### 11.2.1.1 Design Requirements

Step input signals are common in multiplexed applications when switching between different channels. In the worst-case scenario, one channel is at the negative full-scale (NFS) and the other channel is at the positive full-scale (PFS) voltage, in which case the step size is the full-scale range (FSR) of the ADC when the MUX channel is switched.

Design an application circuit optimized for using the ADS8860 to achieve

- · Full-scale step input settling to 16-bit accuracy and

- INL of < ±2 LSB and

- Maximum specified throughput of 1 MSPS

#### 11.2.1.2 Detailed Design Procedure

The application circuit is shown in Figure 63.

In such applications, the primary design requirement is to ensure that the full-scale step input signal settles to 16bit accuracy at the ADC inputs. This condition is critical to achieve the excellent linearity specifications of the ADC. Therefore, the bandwidth of the charge-kickback RC filter must be large enough to allow optimal settling of the input signal during the ADC acquisition time. The filter capacitor helps reduce the sampling charge injection at the ADC inputs, but degrades the phase margin of the driving amplifier, thereby leading to stability issues. Amplifier stability is maintained by the series isolation resistor.

During the conversion process, binary-weighted capacitors are switched onto the REF pin. In order to support this dynamic load the output of the voltage reference must be buffered with a low-output impedance (high-bandwidth) buffer.

The REF60xx family of voltage references are able to maintain an output voltage within 1 LSB (16-bit) with minimal droop, even during the first conversion while driving the REF pin of the ADS8860. This feature is useful in burst-mode, event-triggered, equivalent-time sampling, and variable-sampling-rate data-acquisition systems.

#### **Typical Applications (continued)**

For the input driving amplifiers, key specifications include rail-to-rail input and output swing, high bandwidth, high slew rate, and fast settling time. The CMOS amplifier meets all these specification requirements for this circuit with a single-supply and low quiescent current. The component values of the antialiasing filter are selected to meet the settling requirements of the system as well as to maintain the stability of the input driving amplifiers.

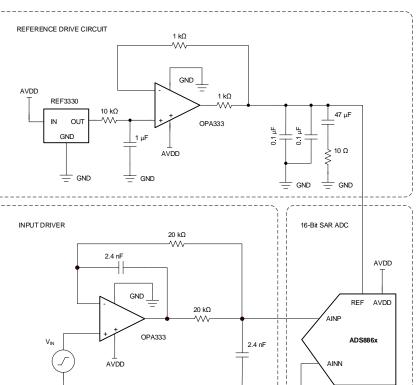

#### 11.2.2 DAQ Circuit for Lowest Distortion and Noise Performance at 1 MSPS

Figure 64. DAQ Circuit for Lowest Distortion and Noise at 1 MSPS

#### 11.2.2.1 Design Requirements

Design an application circuit optimized for using the ADS8860 to achieve

- > 94.5-dB SNR, < -110-dB THD and</li>

- ± 1-LSB linearity and

- maximum specified throughput of 1 MSPS

#### 11.2.2.2 Detailed Design Procedure