📕 Order

Now

BQ79606A-Q1

JAJSH94-APRIL 2019

# BQ79606A-Q1 車載バッテリ・パック・アプリケーション用のハードウェ ア・プロテクタ内蔵 SafeTI™ 高精度モニタ

# 1 特長

Texas

INSTRUMENTS

- 車載アプリケーションに対応

- 下記内容で AEC-Q100 認定済み

- デバイス温度グレード 2:動作時周囲温度範囲 -40℃~+105℃

- デバイス HBM ESD 分類レベル 2

- デバイス CDM ESD 分類レベル C4B

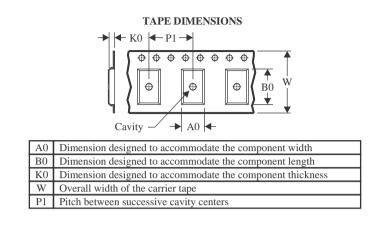

- ・ 電圧モニタ、温度モニタ、および通信機能: SafeTI<sup>™</sup>-26262 ASIL-D 準拠

- オフセット付きで ±1.1mV のセル電圧測定精度

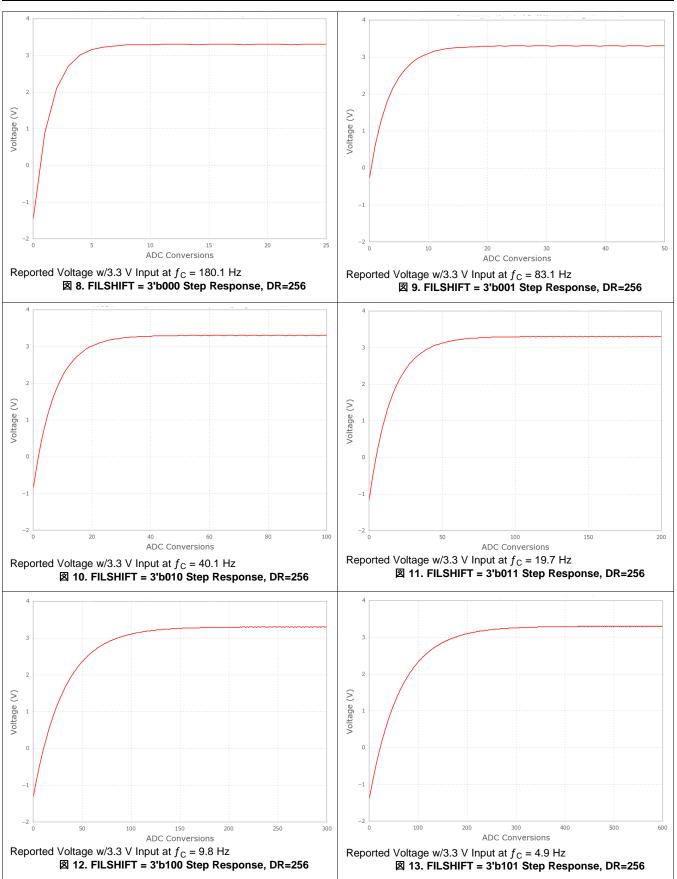

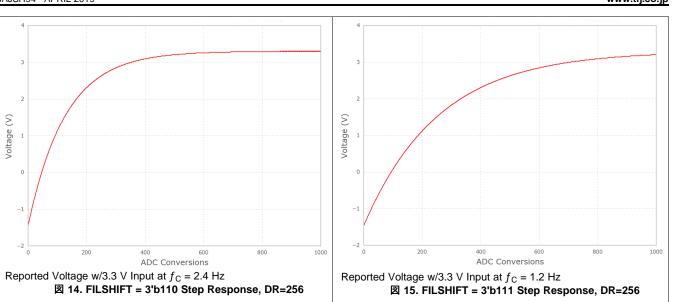

- 最小 1.2Hz の構成可能なデジタル・ローパス・ フィルタ

- セル電圧の同時測定をサポート

- 1ms 未満で完全な精度でスタックを測定 (96 セルの場合)

- オプションのリング型アーキテクチャにより、通信ケーブルが破損した場合でもスタック通信を保証

- 3~6 セルの接続と、最大 6 つの NTC/補助チャネ ルを監視

- 16 ビットのアナログ / デジタル・コンバータ (ADC) を内蔵

- 高電圧 AFE フィルタ・コンポーネントを内蔵

- 堅牢なホットプラグ性能を備えるように設計

- 最大 64 デバイスのスタック構成 (1 ベース + 63 スタック、384 直列セル)

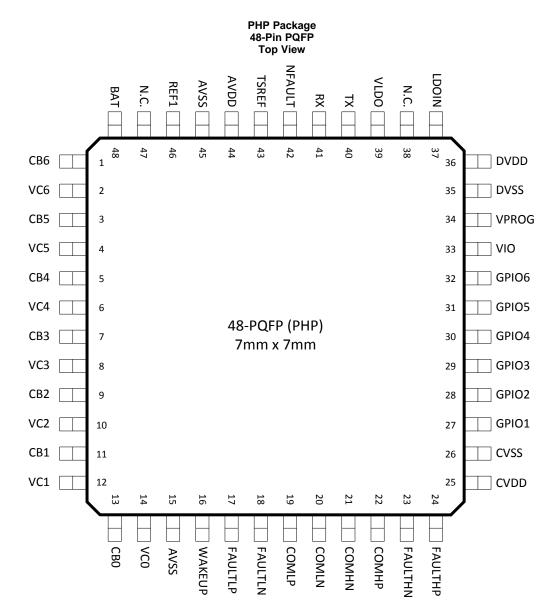

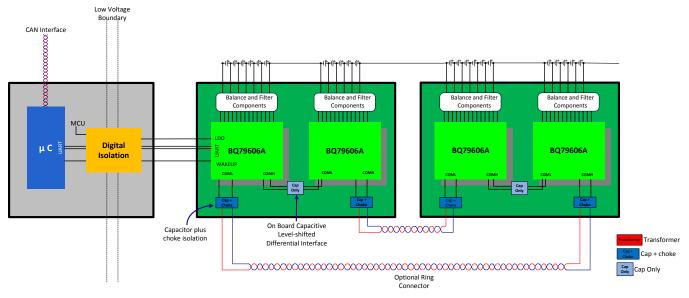

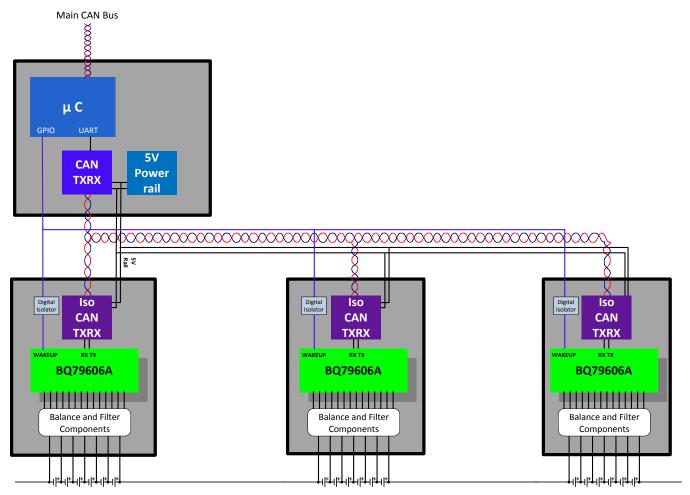

- 絶縁差動デイジー・チェーン通信

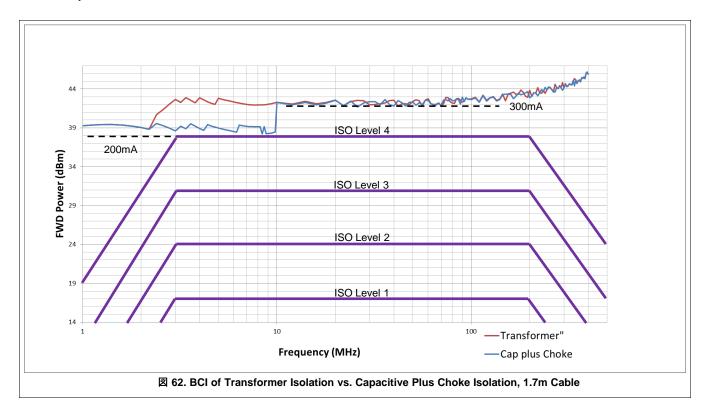

変圧器またはコンデンサ・ベースの絶縁をサポート

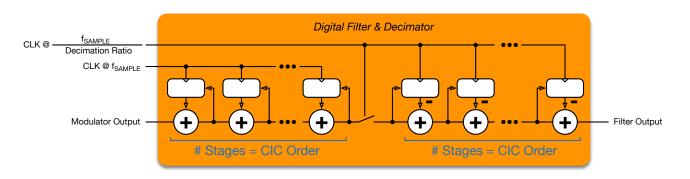

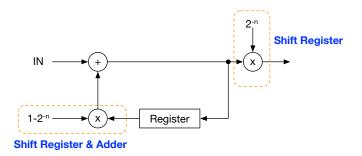

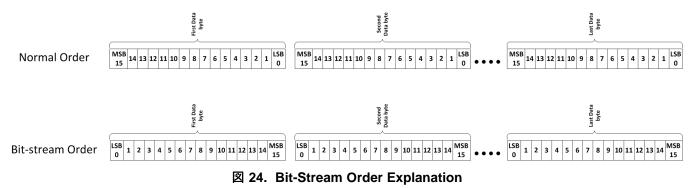

- 設定可能な SINC<sup>3</sup> デジタル・フィルタ

- ハードウェア保護機能を内蔵

- セルの過熱および低温に対する2次的保護

- セルの過電圧および低電圧に対する2次的保護

- ハードウェア保護機能:SafeTI™-26262 ASIL-B 準拠

- 最大 150mA のセル・バランス用 MOSFET を内 蔵

- BCI テストに合格するように設計

- UART ホスト・インターフェイス

- 2 アプリケーション

- 電気自動車、プラグイン・ハイブリッドおよびハ イブリッド自動車

- 車載用 12V および 48V リチウムイオン・バッテ リ・システム

- グリッド・ストレージ・バッテリ・システム

- 無停電電源 (UPS)

- 電動自転車と電動スクーター

# 3 概要

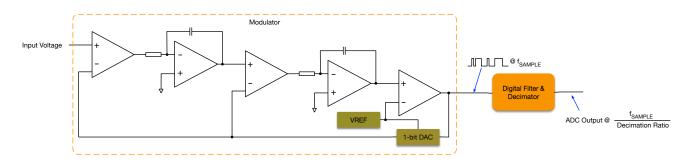

BQ79606A-Q1デバイスは3~6のバッテリ・セルについ て、同時に高精度でチャネル測定を行えます。 BQ79606A-Q1 デバイスはデイジー・チェーン通信ポート を内蔵しているため、スタック可能(最大 64 デバイス)で あり、電気自動車のドライブ・トレイン用バッテリ・パックに 見られるような大きなスタック構成に対応できます。セル入 力ごとにデルタ・シグマ・コンバータを備えているため、 BQ79606A-Q1を使うと各バッテリ電圧を同時に測定でき ます。

BQ79606A-Q1には補助ADCが内蔵されており、最大6 つまでのNTCおよび内部レールのセル温度を測定できる ため、デバイスの安全性チェックが可能です。ダイ温度の 測定用ADCも内蔵されており、温度補正によって拡張温 度範囲全体で高精度の結果が得られます。

#### 製品情報<sup>(1)</sup>

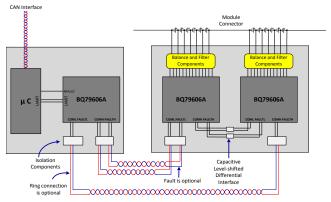

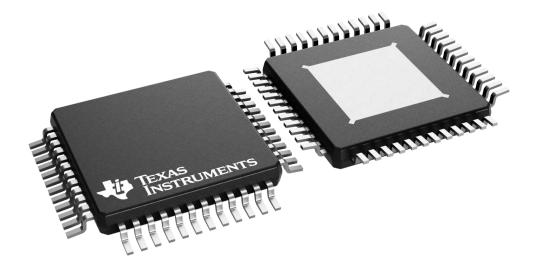

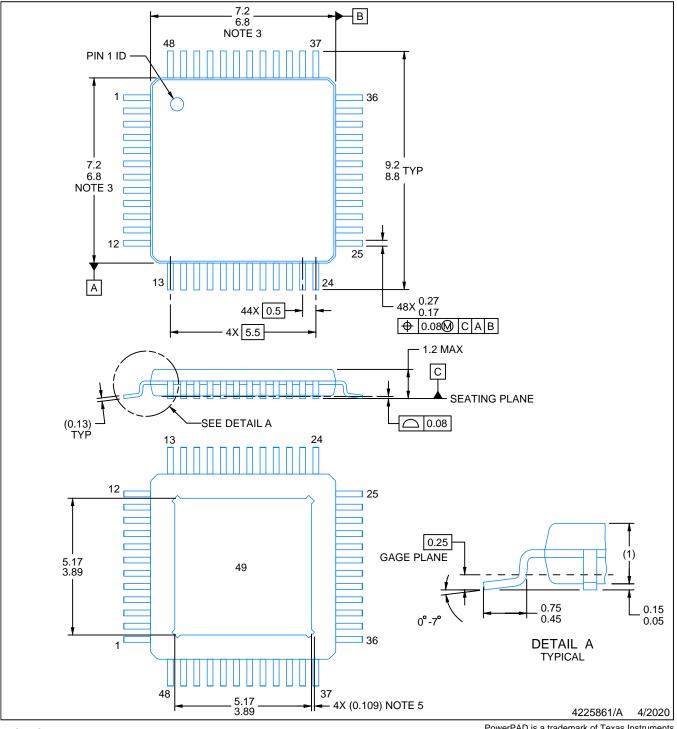

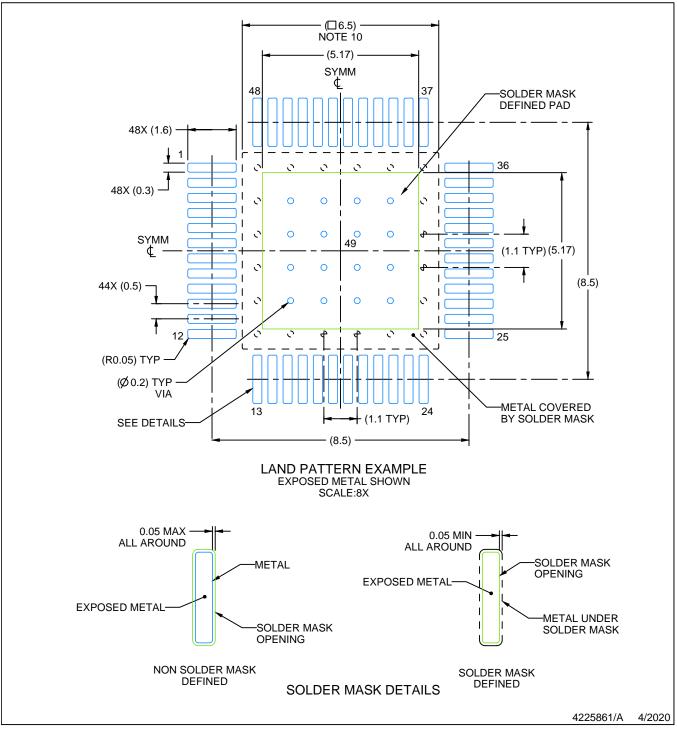

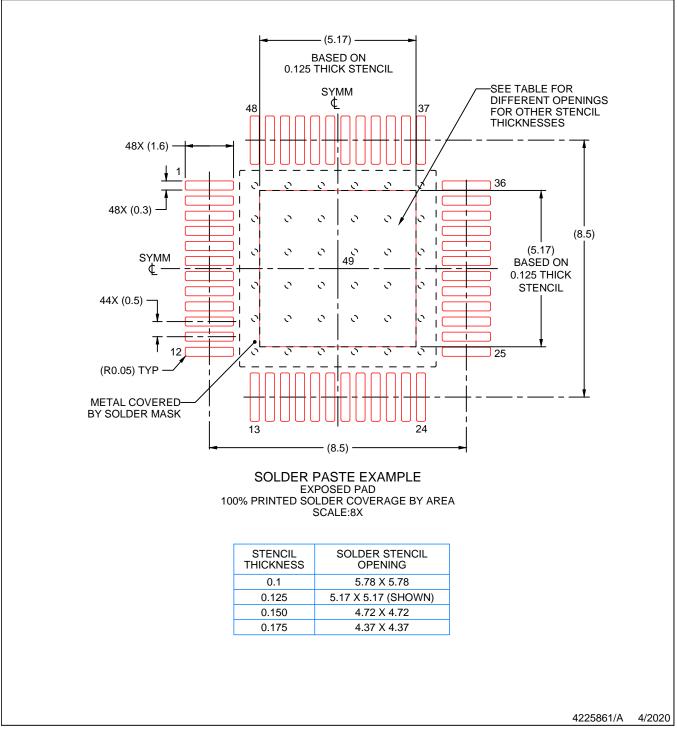

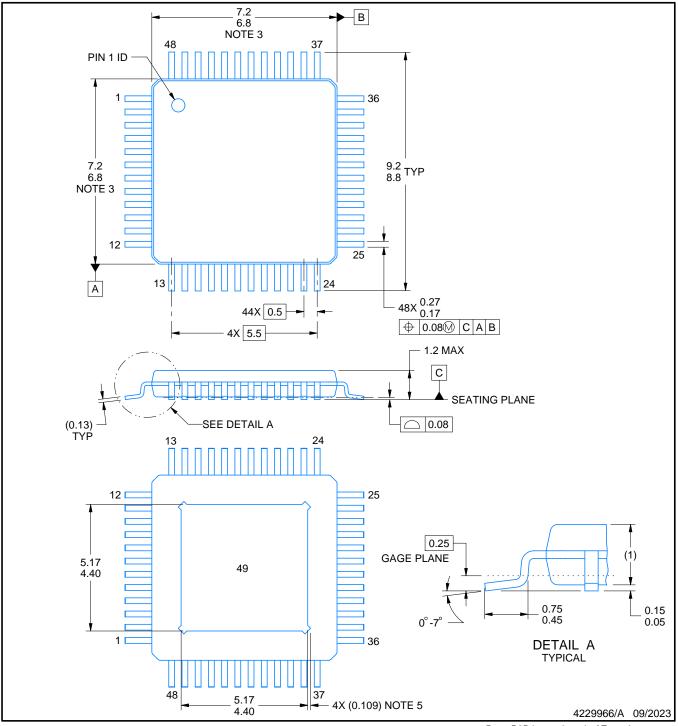

| 型番          | パッケージ       | 本体サイズ(公称)     |  |  |  |  |

|-------------|-------------|---------------|--|--|--|--|

| BQ79606A-Q1 | PQFP (48ピン) | 7.00mm×7.00mm |  |  |  |  |

(1) 利用可能なすべてのパッケージについては、このデータシートの末 尾にある注文情報を参照してください。

## Texas Instruments

www.tij.co.jp

# 目次

| 1 | 特長   |                                  | 1 |

|---|------|----------------------------------|---|

| 2 | アプ   | リケーション                           | 1 |

| 3 | 概要   | <u>.</u>                         | 1 |

| 4 | 改訂   | "履歴                              | 2 |

| 5 | 概要   | -<br>(続き)                        | 3 |

| 6 | Pin  | Configuration and Functions      | 4 |

| 7 | Spe  | cifications                      | 3 |

|   | 7.1  | Absolute Maximum Ratings         | В |

|   | 7.2  | ESD Ratings                      | В |

|   | 7.3  | Recommended Operating Conditions | З |

|   | 7.4  | Thermal Information              | 9 |

|   | 7.5  | Electrical Characteristics       | 9 |

|   | 7.6  | Timing Requirements 13           | 3 |

|   | 7.7  | Typical Characteristics 17       | 7 |

| 8 | Deta | ailed Description 18             | 3 |

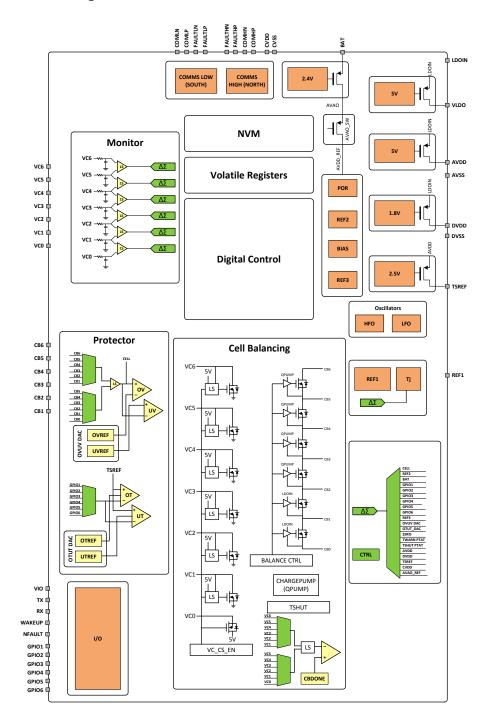

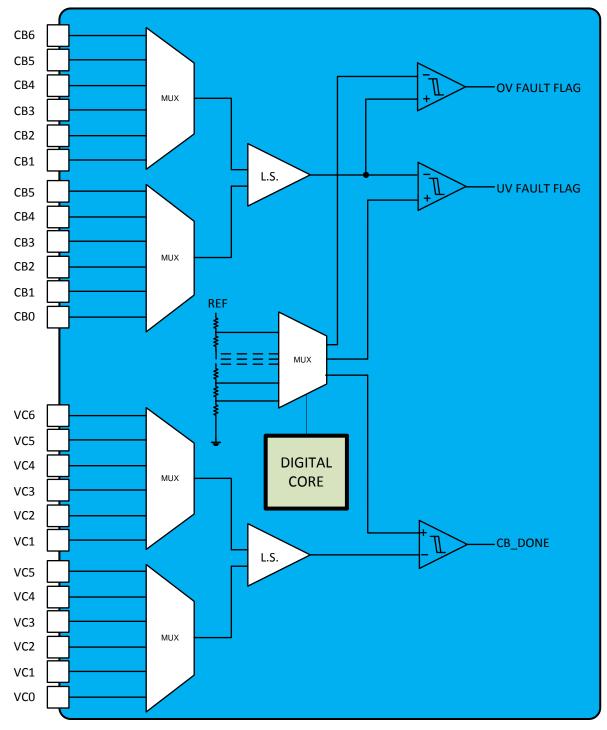

|   | 8.1  | Overview 18                      | З |

|   | 8.2  | Functional Block Diagram 19      | 9 |

|   | 8.3  | Feature Description 20           | C |

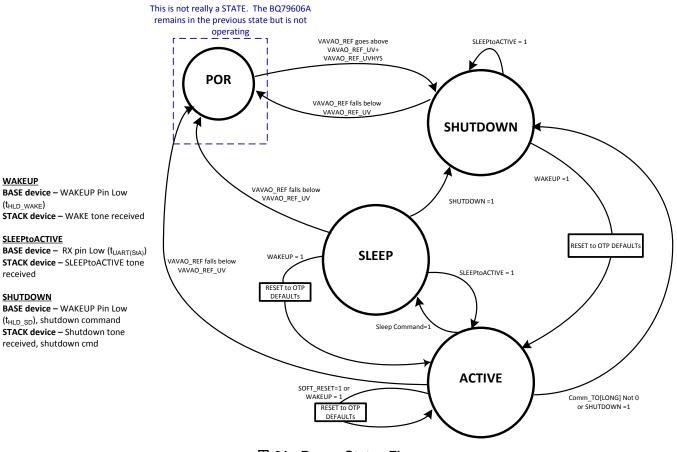

|   | 8.4  | Device Functional Modes 44       | 4 |

|   |      |                                  |   |

| 8.6 Register Maps       22         9 Application and Implementation       22         9.1 Application Information       22         9.2 Typical Applications       22         10 Power Supply Recommendations       25         10.1 Communication Bridge System       24         10.2 Integrated Base Device System       24         10.3 Multi-Drop System       24         11.1 Layout       25         11.2 Layout Example       24         11.2 Layout Example       24         11.2 Layout Example       24         12 デバイスおよびドキュメントのサポート       26         12.1 ドキュメントの更新通知を受け取る方法       26         12.3 商標       26         12.4 静電気放電に関する注意事項       26         12.5 Glossary       26         13 メカニカル、パッケージ、および注文情報       26 |    | 8.5  | Communication, Programming, GPIO, and | Safety . 48       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|---------------------------------------|-------------------|

| 9.1 Application Information       22         9.2 Typical Applications       22         10 Power Supply Recommendations       25         10.1 Communication Bridge System       24         10.2 Integrated Base Device System       24         10.3 Multi-Drop System       25         11.1 Layout       26         11.2 Layout Example       25         11.2 Layout Example       26         11.2 Layout Example       26         12.1 ドキュメントの更新通知を受け取る方法       26         12.2 コミュニティ・リソース       26         12.3 商標       26         12.4 静電気放電に関する注意事項       26         12.5 Glossary       26                                                                                                                                   |    | 8.6  | Register Maps                         | 91                |

| 9.2 Typical Applications       22         10 Power Supply Recommendations       25         10.1 Communication Bridge System       24         10.2 Integrated Base Device System       24         10.3 Multi-Drop System       25         11 Layout       26         11.1 Layout Guidelines       26         11.2 Layout Example       26         11.2 Layout Example       26         11.2 Layout Example       26         12 デバイスおよびドキュメントのサポート       26         12.1 ドキュメントの更新通知を受け取る方法       26         12.3 商標       26         12.4 静電気放電に関する注意事項       26         12.5 Glossary       26                                                                                                                                     | 9  | App  | lication and Implementation           | 228               |

| 10       Power Supply Recommendations       25         10.1       Communication Bridge System       24         10.2       Integrated Base Device System       24         10.3       Multi-Drop System       24         11       Layout       25         11.1       Layout Guidelines       24         11.2       Layout Example       25         11.2       Layout Example       26         12.1       ドキュメントの更新通知を受け取る方法       26         12.2       コミュニティ・リソース       26         12.3       商標       26         12.4       静電気放電に関する注意事項       26         12.5       Glossary       26                                                                                                                                           |    | 9.1  | Application Information               | 228               |

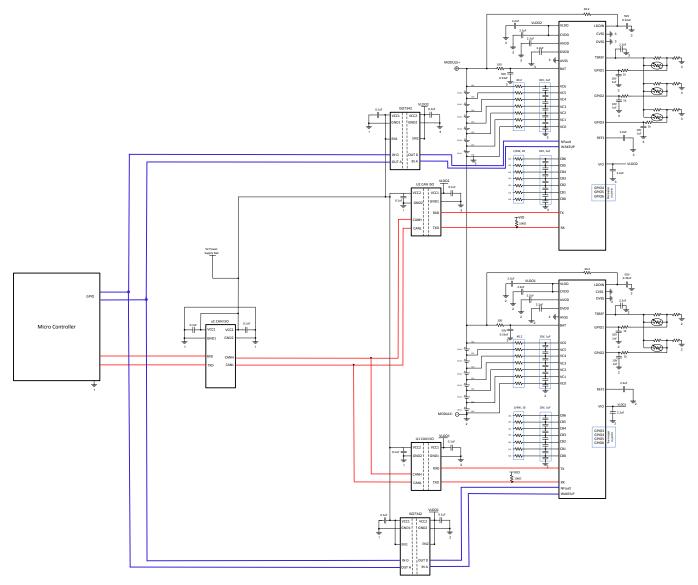

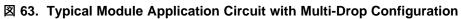

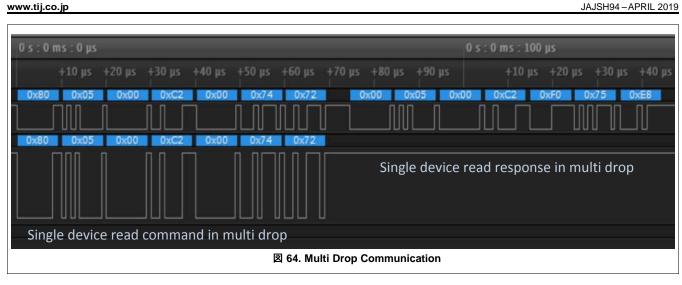

| 10.1       Communication Bridge System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 9.2  | Typical Applications                  | 229               |

| 10.2       Integrated Base Device System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 10 | Pow  | ver Supply Recommendations            | 254               |

| 10.3 Multi-Drop System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 10.1 | Communication Bridge System           | 254               |

| 11       Layout       25         11.1       Layout Guidelines       24         11.2       Layout Example       24         12       デバイスおよびドキュメントのサポート       26         12.1       ドキュメントの更新通知を受け取る方法       26         12.2       コミュニティ・リソース       26         12.3       商標       26         12.4       静電気放電に関する注意事項       26         12.5       Glossary       26                                                                                                                                                                                                                                                                                                                                                                |    | 10.2 | Integrated Base Device System         | 254               |

| 11.1       Layout Guidelines       24         11.2       Layout Example       24         12       デバイスおよびドキュメントのサポート       26         12.1       ドキュメントの更新通知を受け取る方法       26         12.2       コミュニティ・リソース       26         12.3       商標       26         12.4       静電気放電に関する注意事項       26         12.5       Glossary       26                                                                                                                                                                                                                                                                                                                                                                                                 |    | 10.3 | Multi-Drop System                     | 255               |

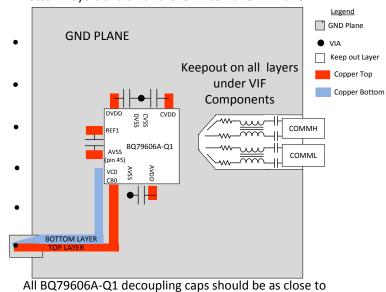

| 11.2       Layout Example       24         12       デバイスおよびドキュメントのサポート       26         12.1       ドキュメントの更新通知を受け取る方法       26         12.2       コミュニティ・リソース       26         12.3       商標       26         12.4       静電気放電に関する注意事項       26         12.5       Glossary       26                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11 | Lay  | out                                   | 257               |

| 12 デバイスおよびドキュメントのサポート       26         12.1 ドキュメントの更新通知を受け取る方法       26         12.2 コミュニティ・リソース       26         12.3 商標       26         12.4 静電気放電に関する注意事項       26         12.5 Glossary       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 11.1 | Layout Guidelines                     | 257               |

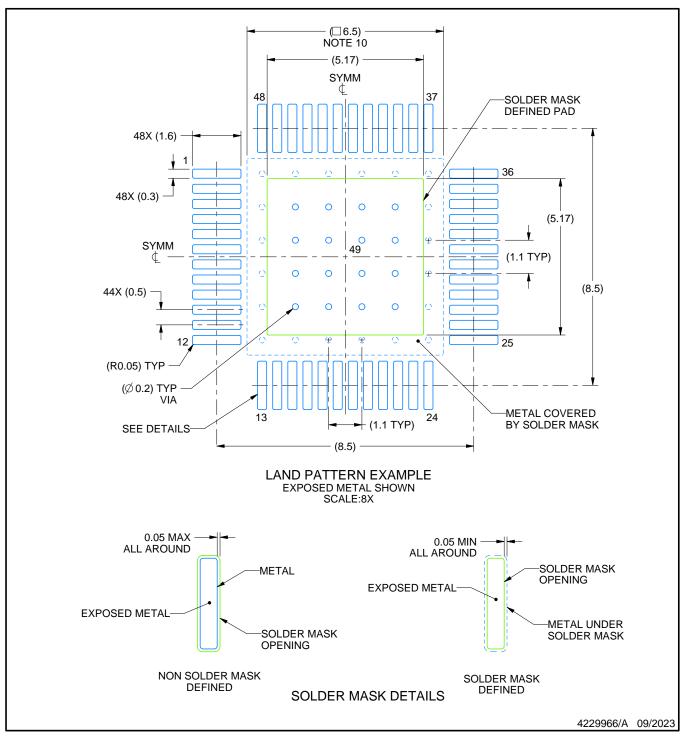

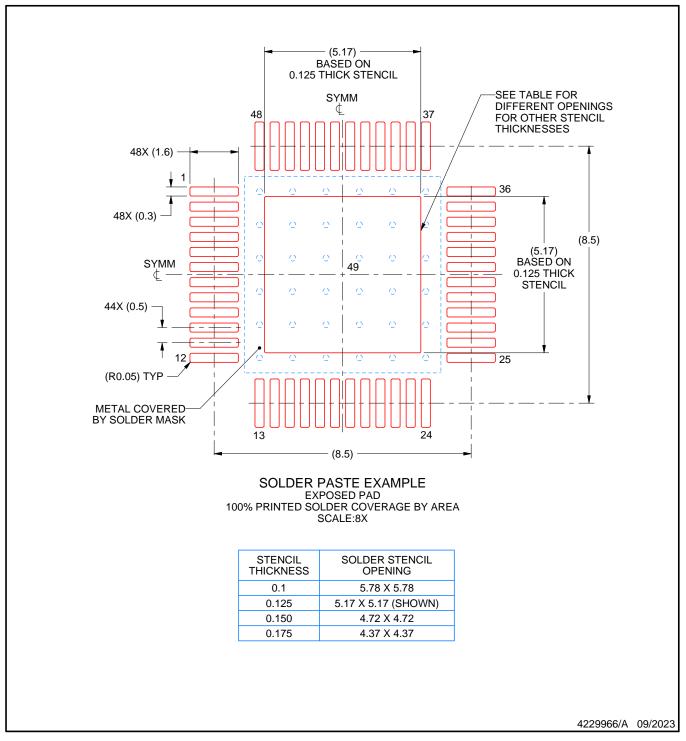

| 12.1       ドキュメントの更新通知を受け取る方法                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 11.2 | Layout Example                        | 258               |

| 12.2       コミュニティ・リソース       20         12.3       商標       20         12.4       静電気放電に関する注意事項       20         12.5       Glossary       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12 | デバ   | イスおよびドキュメントのサポート                      | <mark>26</mark> 0 |

| 12.3 商標       20         12.4 静電気放電に関する注意事項       20         12.5 Glossary       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 12.1 | ドキュメントの更新通知を受け取る方法                    | 260               |

| 12.4       静電気放電に関する注意事項       20         12.5       Glossary       20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 12.2 | コミュニティ・リソース                           | 260               |

| 12.5 Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 12.3 | 商標                                    | 260               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 12.4 | 静電気放電に関する注意事項                         | <mark>26</mark> 0 |

| 13 メカニカル、パッケージ、および注文情報                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 12.5 | Glossary                              | <mark>26</mark> 0 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13 | メカニ  | ニカル、パッケージ、および注文情報                     | 261               |

# 4 改訂履歴

| 日付         | リビジョン | 注  |

|------------|-------|----|

| 2019 年 4 月 | *     | 初版 |

# 5 概要(続き)

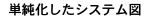

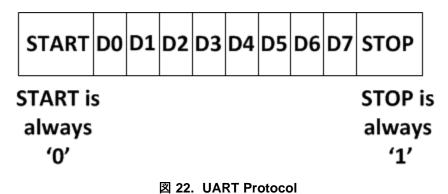

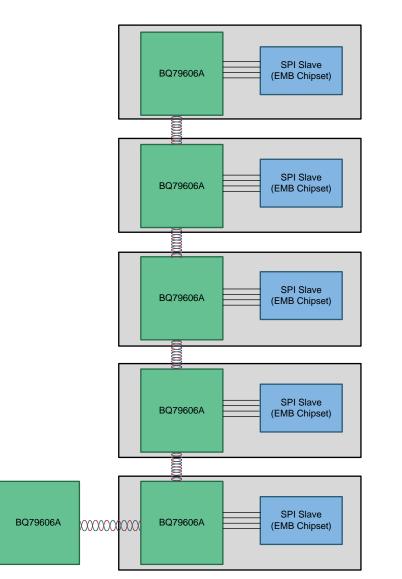

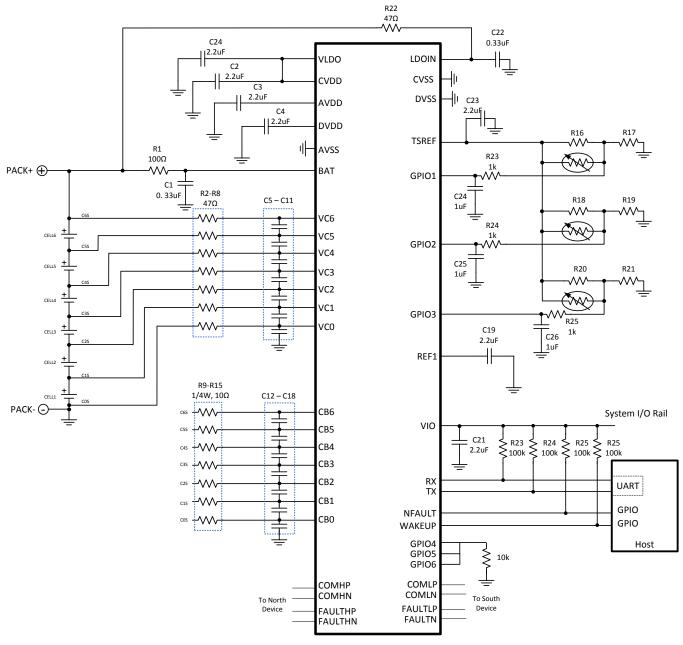

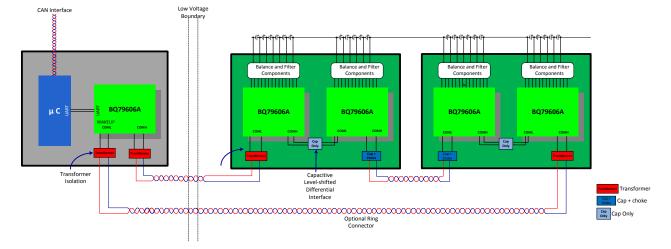

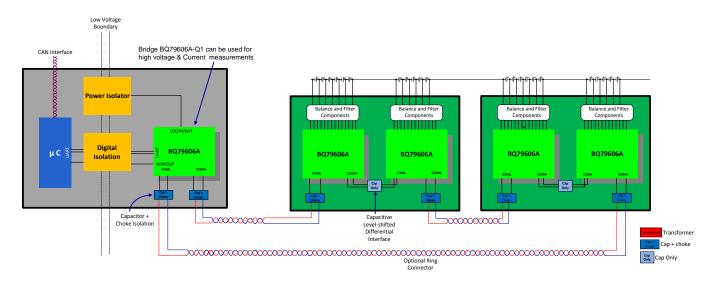

BQ79606A-Q1 デバイスへのホスト通信は、専用の UART インターフェイスで行います。さらに、コンデンサと変圧器の両 方の絶縁に対応する絶縁型差動デイジー・チェーン通信インターフェイスにより、ホストはバッテリ・スタック全体と通信でき ます。このデイジー・チェーン通信インターフェイスは、通信ラインが破損した場合にホストがスタックのどちらの端のデバイ スとでも通信できるように、オプションでリング型アーキテクチャに構成することもできます。

# 6 Pin Configuration and Functions

#### **Pin Functions**

| F    | NIN | ТҮРЕ                                                                                                                                                                                                                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | TIFE                                                                                                                                                                                                                                            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |

|      | 15  | GND                                                                                                                                                                                                                                             | Analog Ground. Pin 15 is not connected to pin 45 internally. Ground connection for internal analog circuits. Connect CVSS, DVSS, and AVSS externally. AVSS must NOT be left unconnected.                                                                                                                                                                                     |

|      |     | Analog Ground. Pin 45 is not connected to pin 15 internally. Ground connection for internal ADC circuits. Connect the decoupling capacitor of the REF1 to this pin. Connect CVSS, DVSS, and AVSS externally. AVSS must NOT be left unconnected. |                                                                                                                                                                                                                                                                                                                                                                              |

| AVDD | 44  | 0                                                                                                                                                                                                                                               | 5-V Regulator Output. AVDD supplies internal circuits. Bypass AVDD to AVSS with 2.2µF/10V ceramic capacitor. The capacitance range after derating must fall between 1uF to 2.2uF. Do not connect additional load to AVDD.                                                                                                                                                    |

| BAT  | 48  | I                                                                                                                                                                                                                                               | Battery Stack Connection. Connect BAT to the positive terminal of the highest cell in the stack through a $100\Omega$ resistor. Bypass BAT to AVSS with a $0.33\mu$ F/50V capacitor.                                                                                                                                                                                         |

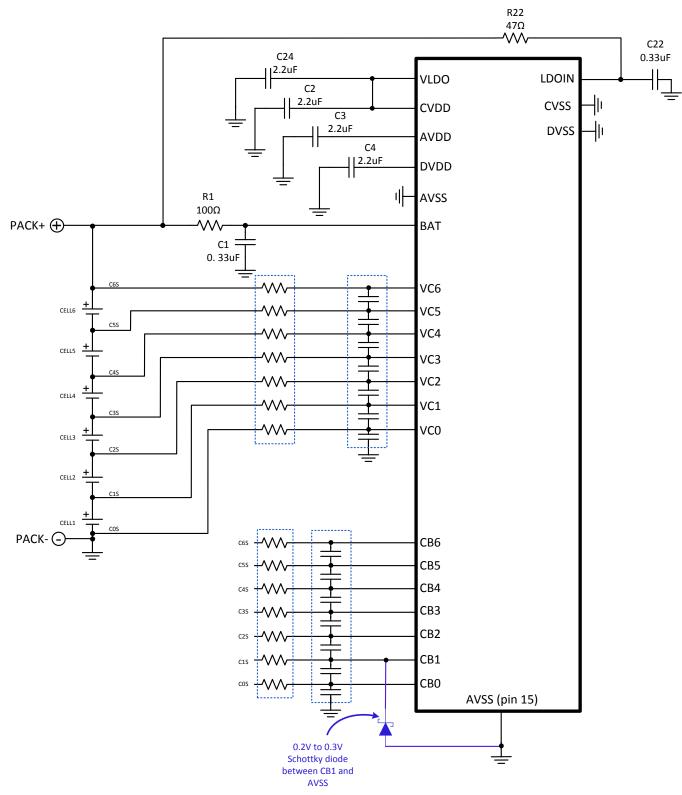

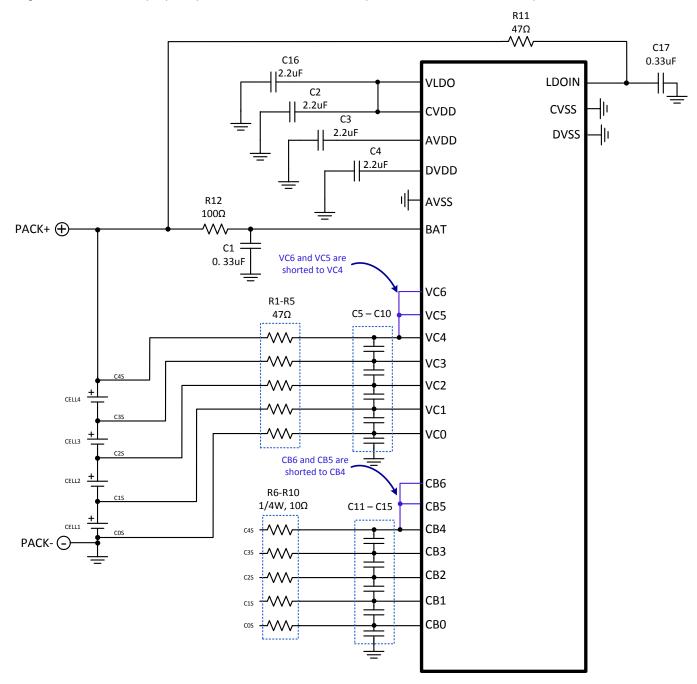

| СВО  | 13  | I/O                                                                                                                                                                                                                                             | Cell Balance Connection 0. CB0 is connected to the internal balance FET. Connect CB0 to the negative terminal of cell 1 (bottom cell) through a resistor. The resistor sets the balance current. See Selecting Cell Balance Resistors for details on calculating the resistor value. Additionally, connect a 0.47µF, 10V (or better) ceramic capacitor between CB0 and AVSS. |

# Pin Functions (continued)

| PIN     |     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|---------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

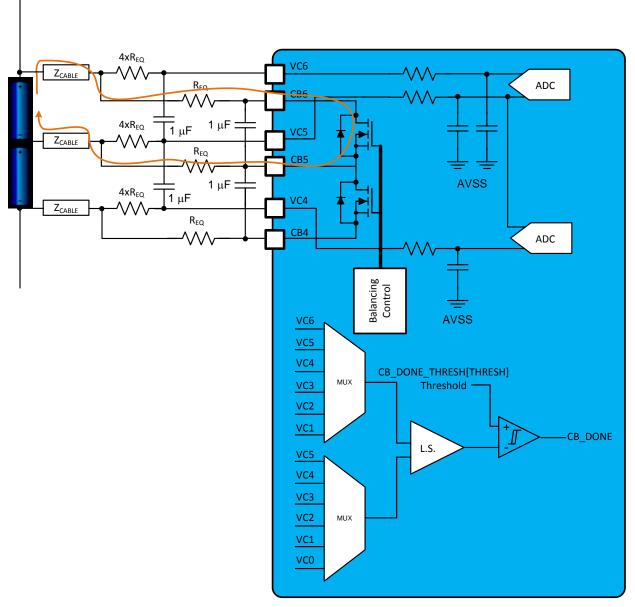

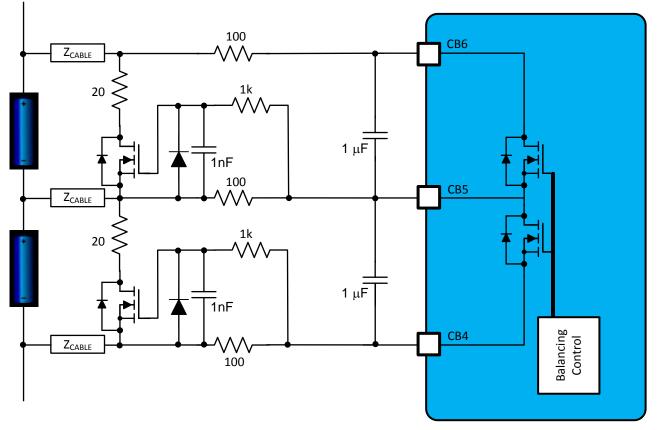

| CB1     | 11  | I/O  | Cell Balance Connection 1. CB1 is connected to the internal balance FET. Connect CB1 to the junction of the positive terminal of cell 1 (bottom cell) and the negative terminal of cell 2 through a resistor. The resistor sets the balance current. See Selecting Cell Balance Resistors for details on calculating the resistor value. Additionally, connect a $0.47\mu$ F, 10V (or better) ceramic capacitor between CB1 and CB0. Short CB1 to CB0 if cell balancing is not used. |  |  |

| CB2     | 9   | I/O  | Cell Balance Connection 2. CB2 is connected to the internal balance FET. Connect CB2 to the junction of the positive terminal of cell 2 and the negative terminal of cell 3 through a resistor. The resistor sets the balance current. See Selecting Cell Balance Resistors for details on calculating the resistor value. Additionally, connect a $0.8\mu$ F, 10V (or better) ceramic capacitor between CB2 and CB1. Short CB2 to CB1 if cell balancing is not used.                |  |  |

| СВЗ     | 7   | I/O  | Cell Balance Connection 3. CB3 is connected to the internal balance FET. Connect CB3 to the junction of the positive terminal of cell 3 and the negative terminal of cell 4 through a resistor. The resistor sets the balance current. See Selecting Cell Balance Resistors for details on calculating the resistor value. Additionally, connect a $1-\mu$ F, 10V (or better) ceramic capacitor between CB3 and CB2. Short CB3 to CB2 if cell balancing is not used.                 |  |  |

| CB4     | 5   | I/O  | Cell Balance Connection 4. CB4 is connected to the internal balance FET. Connect CB4 to the junction of the positive terminal of cell 4 and the negative terminal of cell 5 through a resistor. The resistor sets the balance current. See Selecting Cell Balance Resistors for details on calculating the resistor value. Additionally, connect a $1-\mu$ F, 10V (or better) ceramic capacitor between CB4 and CB3. Short CB4 to CB3 if cell balancing is not used.                 |  |  |

| CB5     | 3   | I/O  | Cell Balance Connection 5. CB5 is connected to the internal balance FET. Connect CB5 to the junction of the positive terminal of cell 5 and the negative terminal of cell 6 through a resistor. The resistor sets the balance current. See Selecting Cell Balance Resistors for details on calculating the resistor value. Additionally, connect a $0.8\mu$ F, 10V (or better) ceramic capacitor between CB5 and CB4. Short CB5 to CB4 if cell balancing is not used.                |  |  |

| CB6     | 1   | I/O  | Cell Balance Connection 6. CB6 is connected to the internal balance FET. Connect CB6 to the positive terminal of cell 6 through a resistor. The resistor sets the balance current. See Selecting Cell Balance Resistors for details on calculating the resistor value. Additionally, connect a $0.47\mu$ F, 10V (or better) ceramic capacitor between CB6 and CB5. Short CB6 to CB5 if cell balancing is not used.                                                                   |  |  |

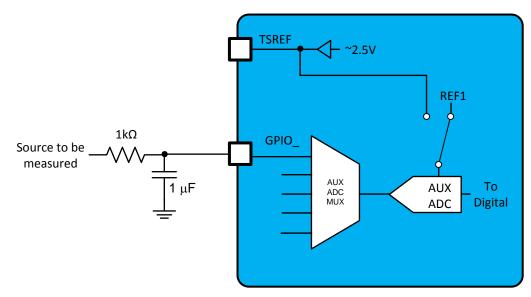

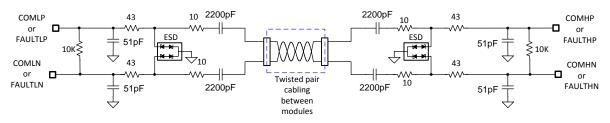

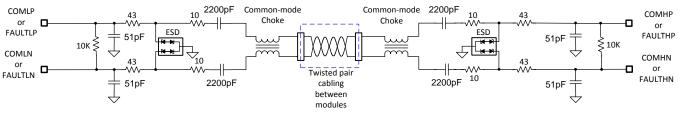

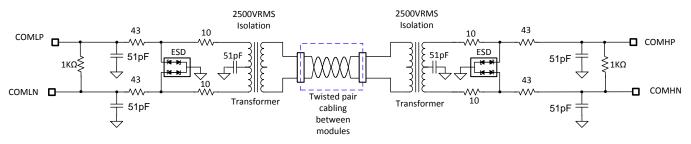

| COMHN   | 21  | I/O  | This is AC coupled I/O. Daisy Chain Communication Connections for Higher Stack Device. COMHP and                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| COMHP   | 22  | I/O  | COMHN provide differential communications for the daisy chain interface. Connect COMHP and COMHN to the COMLP and COMLN inputs on the next higher device in the stack. For devices separated by twisted pair cabling, the connections must be made through either capacitor or transformer isolation network. See Daisy-Chain Differential Bus for details. Leave COMH* unconnected if not used.                                                                                     |  |  |

| COMLN   | 20  | I/O  | This is AC coupled I/O. Daisy Chain Communication Connections for Lower Stack Device. COMLP and                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| COMLP   | 19  | I/O  | COMLN provide differential communication for the daisy chain interface. Connect COMLP and COMLN to the COMHP and COMHN inputs on the next lower device in the stack. For devices separated by twisted pair cabling, the connections must be made through either capacitor or transformer isolation network. See Daisy-Chain Differential Bus section for details. Leave COML* unconnected if not used.                                                                               |  |  |

| CVDD    | 25  | I    | Daisy Chain Communication Power. CVDD is the supply input for the stack daisy chain communication transceiver circuits. Connect CVDD to VLDO through a $0\Omega$ resistor. Bypass CVDD to CVSS with a $2.2\mu$ F/10V ceramic capacitor. The capacitance range after derating must fall between 1uF to 2.2uF (Excluding VLDO cap).                                                                                                                                                    |  |  |

| CVSS    | 26  | GND  | Daisy Chain Communication Ground. Ground connection for internal daisy chain transceivers. Connect AVSS, CVSS, and DVSS externally. CVSS must NOT be left unconnected.                                                                                                                                                                                                                                                                                                               |  |  |

| DVDD    | 36  | 0    | 1.8-V Regulator Output. DVDD supplies internal circuits. Bypass DVDD to DVSS with a ceramic capacitor ranging from 1uF to 2.2µF with 10V rating. The capacitance range after derating must fall between 1uF to 2.2uF. Connect the capacitor as close as possible to the pin with a noise free trace. Do not connect additional load to DVDD.                                                                                                                                         |  |  |

| DVSS    | 35  | GND  | Digital Ground. Ground connection for internal digital logic. Connect AVSS, CVSS, and DVSS externally.<br>DVSS must NOT be left unconnected.                                                                                                                                                                                                                                                                                                                                         |  |  |

| FAULTLP | 17  | 0    | This is AC coupled I/O. Daisy Chain Fault Connections for Lower Stack Device. FAULTLN and FAULTLP                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| FAULTLN | 18  | 0    | provide differential fault signaling for the daisy chain interface. Connect FAULTLP and FAULTLN to the FAULTHP and FAULTHN inputs on the next lower device in the stack. For devices separated by twisted pair cabling, the connections must be made through either capacitor or transformer isolation network. So Daisy-Chain Differential Bus for details. Leave FAULTL* unconnected if not used.                                                                                  |  |  |

| FAULTHP | 24  | I    | This is AC coupled I/O. Daisy Chain Fault Connections for Higher Stack Device. FAULTHN and FAULTHP                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| FAULTHN | 23  | I    | provide differential communication signaling for the daisy chain interface. Connect FAULTHP and<br>FAULTHN to the FAULTLP and FAULTLN inputs on the next higher device in the stack. For devices<br>separated by twisted pair cabling, the connections must be made through either capacitor or transformer<br>isolation network. See Daisy-Chain Differential Bus section for details. Leave FAULTH* unconnected if not<br>used.                                                    |  |  |

# Pin Functions (continued)

| P      | IN  |      |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                         |

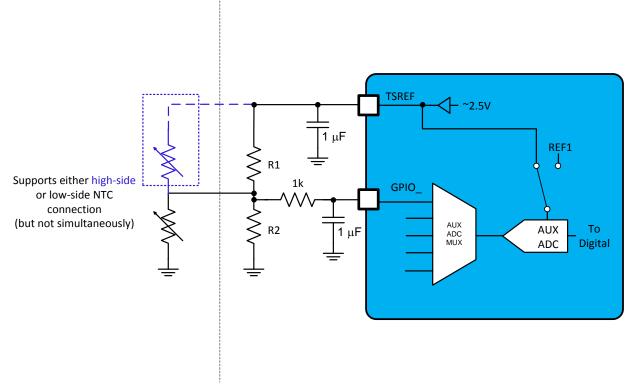

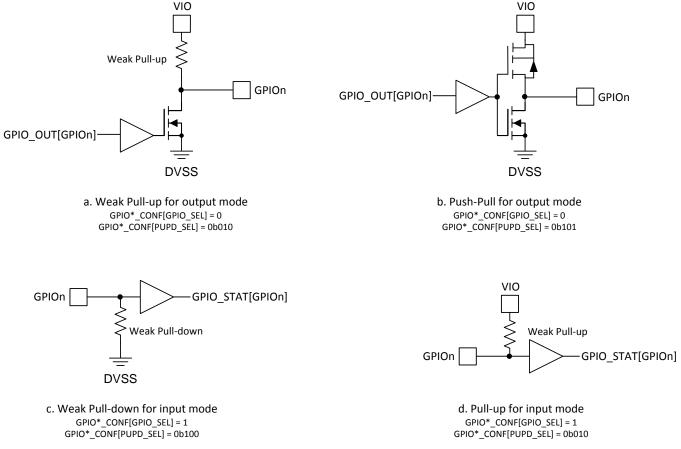

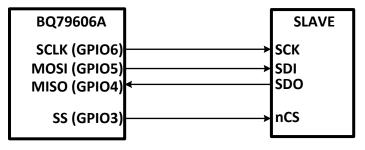

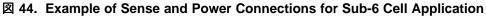

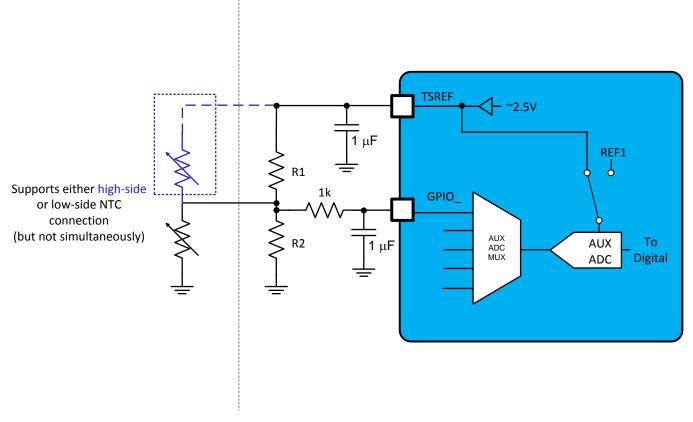

| GPIO1  | 27  | I/O  | General Purpose Input/Output. GPIO* is configurable as an input or output. GPIO* has configurable pullup                                                                                                                                                                                                                                                                                                            |

| GPIO2  | 28  | I/O  | and pulldown (weak) resistors. In input mode, GPIO* is configurable to indicate a fault on a high or low, or simply update register to indicate input level. Additionally, GPIO1-GPIO6 are configurable as an ADC                                                                                                                                                                                                   |

| GPIO3  | 29  | I/O  | input to measure an external temperature sensor (NTC) or other DC voltage. To monitor an external                                                                                                                                                                                                                                                                                                                   |

| GPIO4  | 30  | I/O  | temperature sensor, connect a resistor divider from TSREF to AVSS with GPIO* connected to the center tap. The ADC reports a ratiometric result of GPIO*/TSREF. To measure a standard DC voltage, no                                                                                                                                                                                                                 |

| GPIO5  | 31  | I/O  | resistor divider is required. When configured as an ADC input, GPIO1-GPIO6 support under temperature                                                                                                                                                                                                                                                                                                                |

| GPIO6  | 32  | I/O  | and over temperature hardware protection as well. See the GPIO* Inputs for details on calculating the component values. GPIO1-GPIO6 also are available to be used for the programming the device address. This is most commonly used in multi-drop. Connect GPIO* to AVSS through a 10-kΩ resistor if unused.                                                                                                       |

| LDOIN  | 37  | I    | LDO Supply. LDOIN supplies the internal LDO regulators. Connect LDOIN to the positive terminal of the highest cell in the stack through a $40\Omega$ to $50\Omega$ resistor. Bypass LDOIN to AVSS with a $0.33\mu$ F/50V capacitor.                                                                                                                                                                                 |

| NO     | 47  | -    | No Operate No internal connection, Leave N.O. unconnected on the based                                                                                                                                                                                                                                                                                                                                              |

| N.C.   | 38  | -    | No Connect. No internal connection. Leave N.C. unconnected on the board.                                                                                                                                                                                                                                                                                                                                            |

| NFAULT | 42  | 0    | Active-Low Fault Indication Output. NFAULT pulls low to indicate to the external host that a fault condition has occurred. NFAULT is an open-drain output. Connect a $10K\Omega$ to $100k\Omega$ resistor from NFAULT to VIO. Leave NFAULT unconnected if not used.                                                                                                                                                 |

| REF1   | 46  | 0    | High-Power Reference Bypass Connection. Bypass REF1 to AVSS (pin 45) with a $2.2\mu$ F (10V) ceramic capacitor. The capacitance range after derating must fall between 0.5uF to 2.2uF. Do not connect additional load to REF1. Put the cap as close as possible to the REF1 and AVSS pins and make sure the trace is noise free.                                                                                    |

| RX     | 41  | I    | UART Receiver Input. Connect a $10K\Omega$ to $100k\Omega$ pull up resistor from RX to VIO and connect RX to the TX output of the host micro-controller. If unused, connect RX to VIO. RX must not be left unconnected.                                                                                                                                                                                             |

| TSREF  | 43  | 0    | Bias Voltage for NTC Monitor. Bypass TSREF to AVSS with a $2.2\mu$ F (10V or better) ceramic capacitor. The capacitance range after derating must fall between 1uF to 2.2uF. Connect TSREF to the top of the resistor divider network for the GPIOs when used in NTC monitor mode. TSREF is not available to drive any load other than the resistor network. Leave TSREF unconnected if NTC monitoring is not used. |

| тх     | 40  | 0    | UART Transmitter Output. Connect TX to the RX input of the host micro-controller. For base devices, the TX must be pulled high on the host-side. Leave it floating if unused for stack configuration.                                                                                                                                                                                                               |

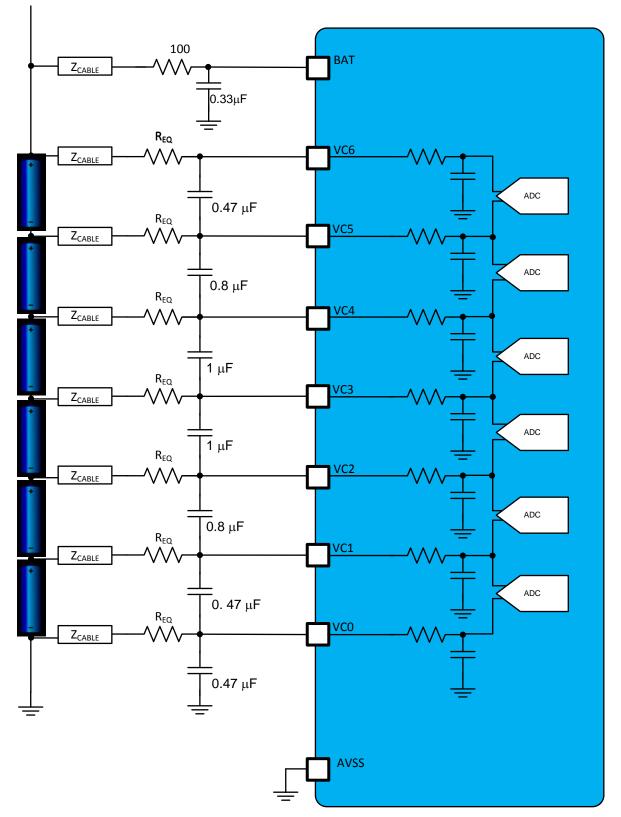

| VC0    | 14  | I    | Cell Voltage Sense Connection 0. Connect VC0 to the negative terminal of cell 1 (bottom cell) through a resistor. See the VC* Inputs section for details on selecting the resistor value. Connect a 0.47µF, 10V (or better) ceramic capacitor from VC0 to AVSS.                                                                                                                                                     |

| VC1    | 12  | I    | Cell Voltage Sense Connection 1. Connect VC1 to the junction of the positive terminal of cell 1 (bottom cell) and the negative terminal of cell 2 through a resistor. See the VC* Inputs section for details on selecting the resistor value. Connect a $0.47\mu$ F, 10V (or better) ceramic capacitor from VC1 to VC0.                                                                                             |

| VC2    | 10  | I    | Cell Voltage Sense Connection 2. Connect VC2 to the junction of the positive terminal of cell 2 and the negative terminal of cell 3 through a resistor. See the VC* Inputs section for details on selecting the resistor value. Recommend to connect a 0.8µF for better transient response, 10V (or better) ceramic capacitor from VC2 to VC1.                                                                      |

| VC3    | 8   | I    | Cell Voltage Sense Connection 3. Connect VC3 to the junction of the positive terminal of cell 3 and the negative terminal of cell 4 through a resistor. See the VC* Inputs section for details on selecting the resistor value. Recommend to connect a $1-\mu$ F for better transient response, 10V (or better) ceramic capacitor from VC3 to VC2.                                                                  |

| VC4    | 6   | I    | Cell Voltage Sense Connection 4. Connect VC4 to the junction of the positive terminal of cell 4 and the negative terminal of cell 5 through a resistor. See the VC* Inputs section for details on selecting the resistor value. Recommend to connect a $1-\mu$ F for better transient response, 10V (or better) ceramic capacitor from VC4 to VC3.                                                                  |

| VC5    | 4   | I    | Cell Voltage Sense Connection 5. Connect VC5 to the junction of the positive terminal of cell 5 and the negative terminal of cell 6 through a resistor. See the VC* Inputs section for details on selecting the resistor value. Recommend to connect a $0.8\mu$ F for better transient response, 10V (or better) ceramic capacitor from VC5 to VC4.                                                                 |

| VC6    | 2   | I    | Cell Voltage Sense Connection 6. Connect VC6 to the positive terminal of cell 6 through a resistor. See the VC* Inputs section for details on selecting the resistor value. Connect a 0.47µF, 10V (or better) ceramic capacitor from VC6 to VC5.                                                                                                                                                                    |

| VIO    | 33  | I    | I/O Supply Voltage. All of the digital pins (WAKEUP, RX, TX and GPIO's) are referenced to VIO. Connect VIO to the system rail between 1.8V and 5.25V. VIO is supplied from the external system logic supply or is connected to VLDO or CVDD for stack devices (or systems without a logic supply). Bypass VIO to AVSS with a $2.2\mu$ F/10V ceramic capacitor.                                                      |

| VLDO   | 39  | 0    | 5-V Regulator Output. VLDO supplies CVDD (can be used for VIO). Bypass VLDO to AVSS with ceramic capacitor of typical value of 2.2µF/10V. The total range of the capacitance after derating can be from 1µF to 2.2µF (Excluding the CVDD cap). The start up time will increase with higher cap value of more than 2.2µF. Do not connect additional load to VLDO.                                                    |

| VPROG  | 34  | I    | OTP Programming Voltage. Connect 7.6 V to VPROG during OTP programming with 1uF/16V capacitor to GND. If not used, connected it to GND through a $100K\Omega$ resistor.                                                                                                                                                                                                                                             |

# Pin Functions (continued)

| P        | IN | ТҮРЕ | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME NO. |    | TIPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| WAKEUP   | 16 | I    | Wake Input for Base Device. Use WAKEUP to send WAKE and SHUTDOWN commands to devices in stand alone operation, multi-drop stacks, or the base device in a daisy chain stack. See the Base Device Wakeup and Hardware Shutdown section for details on the process for sending the commands. WAKEUP must be pulled high during normal operation to configure the device as a base device. For stack devices, connect WAKEUP to AVSS. Do NOT leave WAKEUP unconnected. |  |

# 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                       |                                                   | MIN  | MAX                   | UNIT |

|---------------------------------------|---------------------------------------------------|------|-----------------------|------|

| BAT, LDOIN to AVSS <sup>(2)</sup>     |                                                   | -0.3 | 36                    | V    |

| BAT, LDOIN to AVSS                    | BAT, LDOIN to AVSS                                | -0.3 | 33                    | V    |

| VC0 to AVSS                           | VC0 to AVSS                                       | -0.3 | 5                     | V    |

| VCn to AVSS (n=1 to 2)                | VC <sub>n</sub> to AVSS (n=1 to 2)                | -0.3 | 33                    | V    |

| VCn to AVSS (n=3 to 6)                | VC <sub>n</sub> to AVSS (n=3 to 6)                | 3    | 33                    | V    |

| CBn to AVSS (n=1 to 6)                | CB <sub>n</sub> to AVSS (n=1 to 6)                | -0.3 | 33                    | V    |

| CBn to AVSS (n=0)                     |                                                   | -0.3 | 5                     | V    |

| COMHP, COMHN, COMLP, C                | COMLN, FAULTHP, FAULTHN, FAULTLP, FAULTLN to CVSS | -20  | 20                    | V    |

| COMHP to COMHN, COMLP                 | to COMLN, FAULTHP to FAULTHN, FAULTLP to FAULTLN  | -5.5 | 5.5                   | V    |

| VC(n) to $VC(n-1)$ for $n = 1$ to     | 6                                                 | -33  | 33                    | V    |

| CB(n) to $CB(n-1)$ for $n = 1$ to     | 6                                                 | -0.3 | 16                    | V    |

| GPIO*, NFAULT, RX, TX, WA             | AKEUP to AVSS                                     | -0.3 | V <sub>VIO</sub> +0.3 | V    |

| VPROG to AVSS, during OTF             | P programming                                     | -0.3 | 7.9                   | V    |

| VPROG to AVSS, OTP progr              | amming disabled                                   | -0.3 | 8                     | V    |

| AVDD, CVDD, REF1, TSREF               | F, VIO, VLDO to AVSS                              | -0.3 | 6                     | V    |

| DVDD to DVSS                          |                                                   | -0.3 | 2.3                   | V    |

| DVSS, CVSS to AVSS                    |                                                   | -0.3 | 0.3                   | V    |

| CB* current                           |                                                   |      | 175                   | mA   |

| GPIO*, RX, TX current                 |                                                   |      | 10                    | mA   |

| Ambient temperature                   |                                                   | -40  | 125                   | °C   |

| Junction temperature                  |                                                   | -40  | 150                   | °C   |

| Storage temperature, T <sub>stg</sub> |                                                   |      | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Specified for voltage spikes less than 100µs in duration for a maximum cumulative lifetime of 1000hours above 33 V.

## 7.2 ESD Ratings

|                    |                         |                                                         |                                                 | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------|-------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per AEC Q100–002 <sup>(1)</sup> |                                                 | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge |                                                         | All pins                                        | ±500  | V    |

| (ESD)              |                         | Charged-device model (CDM), per AEC Q100–011            | Corner pins (1, 12, 13, 24, 25, 36, 37, and 48) | ±750  | ·    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                        |                                                                                                                  | MIN  | MAX | UNIT |

|------------------------|------------------------------------------------------------------------------------------------------------------|------|-----|------|

| V <sub>MODULE</sub>    | Total module voltage ( $V_{BAT}$ , $V_{LDOIN}$ ), full functionality available                                   | 5.5  | 30  | V    |

| V <sub>MODULECOM</sub> | Total module voltage ( $V_{\text{BAT}}$ , $V_{\text{LDOIN}}$ ), communication bridge only                        | 4.75 | 30  | V    |

| N                      | Cell differential voltage (VC <sub>n</sub> -VC <sub>n-1</sub> , $n = 1$ to 6)                                    | -2   | 5   | V    |

| V <sub>CELL</sub>      | Cell common mode voltage (VC <sub>n</sub> -AVSS, $n = 0$ )                                                       | 0    | 3   | V    |

| V <sub>CELL</sub>      | Cell common mode voltage (VCn-AVSS, n = 1 to 2)                                                                  | 0    | 30  | V    |

| V <sub>CELL</sub>      | Cell common mode voltage (VC <sub>n</sub> -AVSS, $n = 3$ to 6)                                                   | 3    | 30  | V    |

| СВ                     | Cell Balancing pin common mode voltage (CBn-AVSS, n = 0)                                                         | 0    | 3   | V    |

| СВ                     | Condition 1:Cell Balancing deferential voltage ( $CB_n$ - $CB_{n-1}$ , n = 1 to 6) (meet condition 1 and 2)      | 0    | 14  | V    |

| СВ                     | Condition 2: Cell Balancing pin common mode voltage (CB <sub>n</sub> -AVSS, n = 1 to 6) (meet condition 1 and 2) | 0    | 30  | V    |

# **Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

|                      |                                        | MIN | MAX  | UNIT |

|----------------------|----------------------------------------|-----|------|------|

| V <sub>VIO</sub>     | VIO input voltage                      | 1.8 | 5.25 | V    |

| N                    | PROG input voltage for OTP programming | 7.4 | 7.8  | V    |

| V <sub>PROG</sub>    | PROG input voltage all other times     | 0   |      | V    |

| V <sub>CELLBAL</sub> | Cell balancing current                 | 5   | 150  | mA   |

| I <sub>IO</sub>      | GPIO*, RX, TX current                  |     | 3    | mA   |

|                      | Ambient temperature                    | -40 | 105  | °C   |

## 7.4 Thermal Information

|                       |                                              | bq79606A-Q1 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC                               | PFB (TQFP)  | UNIT |

|                       |                                              | 48 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 23.2        | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 13          | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 4.6         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.1         | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 4.7         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.4         | °C/W |

## 7.5 Electrical Characteristics

|                           | PARAMETER                                                                            | TEST CONDITIONS                                                                                                             | MIN    | TYP   | MAX    | UNIT |

|---------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|------|

| Supply Currents           |                                                                                      |                                                                                                                             |        |       |        |      |

| I <sub>SHDN</sub>         | Supply current in SHUTDOWN mode                                                      | Addition of both BAT and LDOIN supply current                                                                               | 30     | 65    | 105    | μA   |

| I <sub>SLP(IDLE)</sub>    | Supply current in SLEEP mode with no<br>functionality enabled                        | Cell balancing disabled                                                                                                     | 95     | 130   | 165    | μA   |

| I <sub>SLP(BAL)</sub>     | Supply current in SLEEP mode with only cell balancing enabled                        | One or more cell balancing FETs turned on                                                                                   | 700    | 780   | 850    | μA   |

| I <sub>ACT(IDLE)</sub>    | Supply current in ACTIVE mode with no functionality enabled                          | No communication. Cell balancing disabled.                                                                                  | 3.7    | 4.2   | 4.6    | mA   |

| I <sub>ACT(COMT)</sub>    | Additional supply current during<br>communication (Average)                          | Daisy-chain interface communicating, transformer isolation. There is a $1K\Omega$ termination. Depends on Transformer used. |        | 2     |        | mA   |

| I <sub>ACT(COMC)</sub>    | communication (Average)                                                              | Daisy-chain interface communicating, capacitor isolation. There is a $10K\Omega$ termination.                               |        | 0.5   |        |      |

| I <sub>ACT(BAL)</sub>     | Additional supply current during cell balancing                                      | No communication. Cell balancing active.                                                                                    | 125    | 145   | 170    | μA   |

| I <sub>ACT(CONVERT)</sub> | Additional supply current during ADC conversion                                      | No communication, Only Conversion<br>Conversion started, conversion period<br>active;                                       | 2.05   | 2.42  | 2.65   | mA   |

| Reference V               | oltages                                                                              |                                                                                                                             |        |       |        |      |

| V <sub>REF1</sub>         | REF1 Reference voltage                                                               | REF1 capacitor = 1 $\mu$ F, AVDD in<br>regulation,<br>T <sub>A</sub> = -40C to 105C                                         | 2.492  | 2.497 | 2.503  | V    |

| V <sub>REF1SWING</sub>    | Detectable REF1 amplitude during<br>oscillations (frequency from 0.2MHz to<br>10MHz) | Frequency between 0.2MHz to 10MHz.                                                                                          |        | 330   |        | mV   |

| V <sub>REF1OV</sub>       | Over-voltage threshold for REF1                                                      |                                                                                                                             | 2.52   | 2.59  | 2.66   | V    |

| V <sub>REF1UV</sub>       | Undervoltage threshold for REF1                                                      |                                                                                                                             | 2.37   | 2.425 | 2.47   | V    |

| V <sub>REF2</sub>         | REF2 reference voltage                                                               |                                                                                                                             | 1.0975 | 1.100 | 1.1025 | V    |

| V <sub>REF3</sub>         | Internal bandgap voltage, used by POR circuits                                       | -40C to 105C                                                                                                                | 1.2    | 1.22  | 1.26   | V    |

# **Electrical Characteristics (continued)**

|                                    | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                | MIN  | TYP             | MAX  | UNIT     |

|------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|-----------------|------|----------|

| V <sub>PTATGAIN</sub>              | PTAT voltage gain                                                                           | 25C, AVDD_REF = 2.4V                                                                                           |      | 1.17            |      | mV/C     |

| Supplies                           |                                                                                             | · · · · · ·                                                                                                    |      |                 |      |          |

| V <sub>VLDO</sub>                  | VLDO output voltage                                                                         | I <sub>OUT</sub> = 10 mA, C = 1 μF                                                                             | 4.9  | 5.0             | 5.1  | V        |

| V <sub>VLDOOV</sub>                | VLDO Over-voltage threshold                                                                 |                                                                                                                | 5.31 | 5.6             | 5.87 | V        |

| VVLDOOVHYS                         | VLDO OV hysteresis                                                                          |                                                                                                                | 50   | 60              | 150  | mV       |

|                                    | VLDO Current limit                                                                          | External allowable load on the LDO<br>including CVDD load, C=2.2uF, SLEEP<br>Mode.                             | 7.9  | 14              | 23   | mA       |

| VLDO(LIMIT)HP                      | VLDO Current limit                                                                          | External allowable load on the LDO including CVDD load, C=2.2uF, Active Mode.                                  | 21.5 | 35              | 55   | mA       |

| T <sub>SHUT(VLDO)R</sub>           | VLDO LDO thermal shutdown threshold                                                         | TJ rising                                                                                                      |      | 138             |      | °C       |

| T <sub>SHUT(VLDO)F</sub>           |                                                                                             | TJ falling                                                                                                     |      | 123             |      | °C       |

| V <sub>TSREF</sub>                 | NTC monitor reference voltage                                                               |                                                                                                                | 2.47 | 2.5             | 2.53 | V        |

| TSREF                              | TSREF current limit                                                                         |                                                                                                                | 5    |                 | 12.6 | mA       |

| VTSREFOV                           | TSREF over-voltage threshold                                                                | TSREF rising,                                                                                                  | 2.7  |                 | 2.85 | V        |

| V <sub>TSREFOV</sub>               | TSREF over-voltage threshold hysteresis                                                     | V <sub>TSREF</sub> falling                                                                                     | 2.,  | 160             | 2.00 | mV       |

| VTSREFOVHYS                        | TSREF under-voltage threshold                                                               | TSREF falling                                                                                                  | 2.16 | 2.22            | 2.27 | V        |

| V <sub>TSREFUV</sub>               | TSREF under-voltage threshold<br>hysteresis                                                 | TSREF rising                                                                                                   | 65   | 80              | 95   | mV       |

| VOSCTSREF                          | Detectable voltage oscillation above $V_{\text{TSREF}}$ at frequency from 0.2 MHz to 10 MHz |                                                                                                                |      | 300             |      | mV       |

| V <sub>AVDD</sub>                  | AVDD Output voltage                                                                         | I <sub>OUT</sub> = 8 mA, C = 2.2 μF                                                                            | 4.9  | 5.0             | 5.1  | V        |

| AVDDOV                             | AVDD over-voltage threshold                                                                 | AVDD rising                                                                                                    |      | 5.7             |      | V        |

| VAVDDOVHYS                         | AVDD OV hysteresis                                                                          | AVDD falling                                                                                                   |      | 200             |      | mV       |

| V <sub>AVDDUV_F</sub>              | Falling AVDD under-voltage threshold                                                        | AVDD Falling                                                                                                   | 4.10 |                 | 4.25 | V        |

| V <sub>AVDDUV_R</sub>              | Rising AVDD under-voltage threshold                                                         | AVDD Rising                                                                                                    | 4.4  |                 | 4.65 | V        |

| T <sub>SHUT(AVDD)R</sub>           |                                                                                             | TJ rising                                                                                                      |      | 138             |      | °C       |

| T <sub>SHUT(AVDD)</sub> F          | AVDD LDO thermal shutdown threshold                                                         | TJ falling                                                                                                     |      | 123             |      | °C       |

| V <sub>DVDD</sub>                  | DVDD Output voltage                                                                         | $I_{OUT} = 8 \text{ mA}, \text{ C} = 2.2 \mu\text{F}$                                                          | 1.65 | 1.8             | 1.95 | V        |

| V <sub>DVDD</sub>                  | DVDD over-voltage threshold                                                                 | DVDD rising, 200mV hysteresis                                                                                  | 1.00 | 2.2             | 1.00 | V        |

|                                    | Falling DVDD Digital Reset threshold                                                        | DVDD falling                                                                                                   | 1.57 | 2.2             | 1.66 | V        |

| V <sub>DRDVDD_F</sub>              | Rising DVDD Digital Reset threshold                                                         |                                                                                                                | 1.67 |                 |      | V        |

| V <sub>drdvdd_r</sub>              | Rising DVDD Digital Reset threshold                                                         | DVDD rising                                                                                                    | 1.07 | 100             | 1.77 | °C       |

| T <sub>SHUT(DVDD)R</sub>           | DVDD LDO thermal shutdown threshold                                                         | TJ rising                                                                                                      |      | 138             |      |          |

| T <sub>SHUT</sub> (DVDD)F          |                                                                                             | TJ falling                                                                                                     |      | 123             |      | <u>℃</u> |

| V <sub>AVAO_REF_1</sub>            | Internal always-on supply rail<br>(AVAO_REF)                                                | Vbat>=5.5V                                                                                                     | 2.30 | 2.40            | 2.49 | V        |

| VAVAO_REF_2                        |                                                                                             | 4.75V= <vbat<=5.5v (bridge="" devices)<="" td=""><td>2.24</td><td>2.4</td><td>2.48</td><td>V</td></vbat<=5.5v> | 2.24 | 2.4             | 2.48 | V        |

| V <sub>AVAO_REF_U</sub>            | AVAO_REF under-voltage threshold                                                            | V <sub>BAT</sub> falling, 111mV hysteresis                                                                     | 1.93 | 1.98            | 2.18 | V        |

| V <sub>AVAO_REF_O</sub>            | AVAO_REF over-voltage threshold                                                             | V <sub>BAT</sub> rising, 150mV hysteresis                                                                      | 2.75 | 2.85            | 2.95 | V        |

| V <sub>AVAO_REF_</sub> O<br>/HYS   | AVAO_REF OV hysteresis                                                                      | V <sub>BAT</sub> falling                                                                                       |      | 130             |      | mV       |

| V <sub>AVDDREF_FL</sub>            | AVDD_REF UV threshold Falling                                                               | AVDD_REF falling, 100mV hysteresis                                                                             |      | VAVAO-<br>150mV |      | mV       |

| V <sub>AVDDREF_FL</sub><br>tz_hyst | AVDD_REF UV hysteresis                                                                      | AVDD_REF rising                                                                                                |      | 50              |      | mV       |

| VVPROG                             | OTP programming voltage input range                                                         |                                                                                                                | 7.4  | 7.6             | 7.8  | V        |

| V <sub>VPROGOV</sub>               | VPROG overvoltage detection threshold                                                       | V <sub>VPROG</sub> rising,                                                                                     | 7.85 | 7.91            | 8    | V        |

| V <sub>VPROGUV</sub>               | VPROG undervoltage detection threshold                                                      | V <sub>VPROG</sub> falling, 100mV hysteresis                                                                   | 7.2  | 7.25            | 7.35 | V        |

| V <sub>vproguvhy</sub><br>s        | VPROG undervoltage detection threshold hysteresis                                           | V <sub>VPROG</sub> rising, V <sub>AVDD</sub> >4.5V,<br>SH_REFL=1.1V                                            |      | 85              |      | mV       |

# **Electrical Characteristics (continued)**

|                         | PARAMETER                                                  | TEST CONDITIONS                                                                       | MIN    | TYP   | MAX   | UNIT |

|-------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------|--------|-------|-------|------|

| V <sub>CVDD</sub>       | CVDD voltage supply input range                            |                                                                                       | 4.9    | 5     | 5.1   | V    |

| V <sub>CVDDUV</sub>     | CVDD under-voltage threshold                               | V <sub>CVDD</sub> falling, 100-mV hysteresis                                          | 4.2    | 4.41  | 4.56  | V    |

| V <sub>CVDDUVHYS</sub>  | CVDD under-voltage threshold hysteresis                    |                                                                                       |        | 70    |       | mV   |

| V <sub>VIO</sub>        | IO voltage supply input range                              |                                                                                       | 1.8    |       | 5.25  | V    |

| V <sub>VIOUV_Fall</sub> | VIO under-voltage threshold                                | VIO falling, 100-mV hysteresis                                                        | 1.3    |       | 1.75  | V    |

| V <sub>VIOUV_Hys</sub>  | VIO under-voltage hysteresis threshold                     | VIO rising                                                                            |        | 0.1   |       | V    |

| V <sub>CVSSOPEN</sub>   | CVSS open detection threshold                              |                                                                                       | 0.092  |       | 0.26  | V    |

| VDVSSOPEN               | DVSS open detection threshold                              |                                                                                       | 0.092  |       | 0.26  | V    |

|                         | leasurements (VC_ Inputs)                                  |                                                                                       | 0.001  |       | 0.20  | •    |

| V <sub>C*_N</sub>       | Cell input voltage range                                   | VCn to VCn-1, excluding VC1 to VC0,<br>Common Mode Voltage >3V for VC3 to<br>VC6.     | -2     |       | 5.0   | V    |

|                         |                                                            | VC1 to VC0                                                                            | 0      |       | 5.0   |      |

| $\Delta I_{VCn}$        | VCn to VCn–1 input current mismatch                        | (VCELLn - VCELLn-1) < 1V, $T_A = -20^{\circ}C$<br>to +65°C                            |        |       | 990   | nA   |

| $\Delta I_{VCn(FULL)}$  |                                                            | -2 V < VCELL < 5 V, $T_A = -40^{\circ}C$ to +105°C                                    |        |       | 1.5   | μΑ   |

| V <sub>ACC_1</sub>      | Total channel accuracy for voltage measurements            | VCELL = 3 V, CELL_ADC_CONF1[DR] = 0b11<br>$T_A = 25^{\circ}C$                         | -1.72  |       | 0.43  | mV   |

| V <sub>ACC_2</sub>      | Total channel accuracy for voltage measurements            | 2.0 V < VCELL < 5 V,<br>CELL_ADC_CONF1[DR] = 0b11<br>$T_A = 0^{\circ}C$ to +65°C      | -3.23  |       | 1.91  | mV   |

| V <sub>ACC_3</sub>      | Total channel accuracy for voltage measurements            | 2.0 V < VCELL < 5 V,<br>CELL_ADC_CONF1[DR] = 0b11<br>$T_A = -20^{\circ}C$ to +65°C    | -4.24  |       | 2.6   | mV   |

| V <sub>ACC_4</sub>      | Total channel accuracy for voltage measurements            | 2.0 V < VCELL < 5.0 V,<br>CELL_ADC_CONF1[DR] = 0b11<br>$T_A = -40^{\circ}C$ to +105°C | -4.46  |       | 3.77  | mV   |

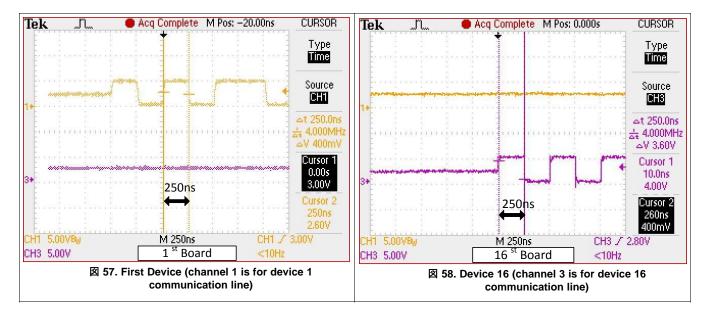

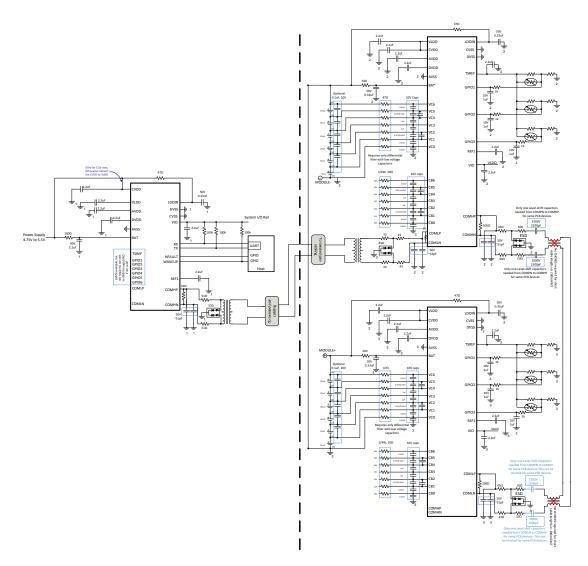

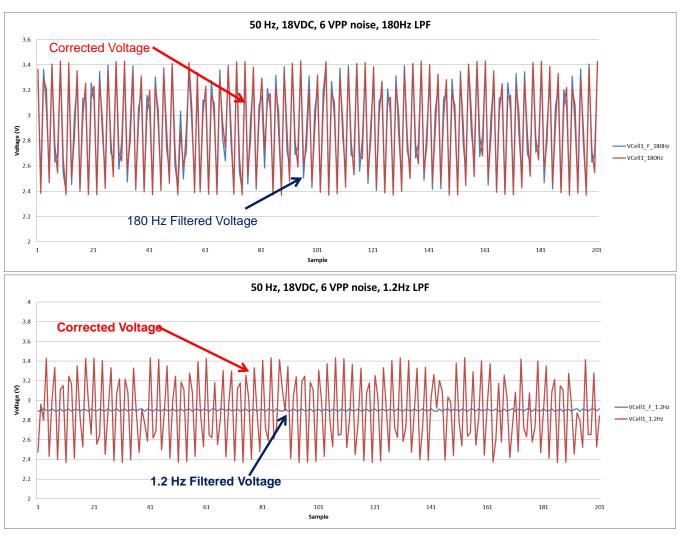

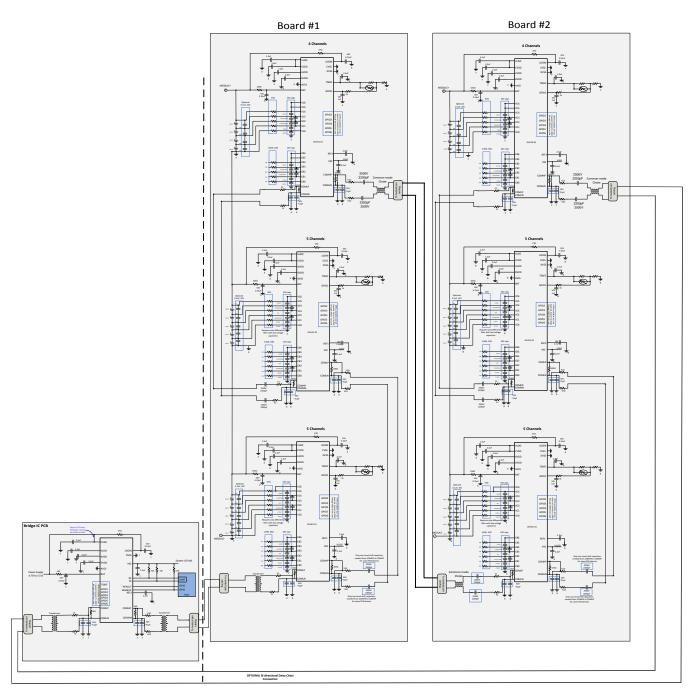

| V <sub>ACC_5</sub>      | Total channel accuracy for voltage measurements            | -2.0 V < VCELL < 2.0 V,<br>CELL_ADC_CONF1[DR] = 0b11<br>$T_A = -20^{\circ}C$ to +65°C | -14.32 |       | 14.07 | mV   |