TPS92682-Q1

JAJSHS0C - MARCH 2019 - REVISED MARCH 2021

# TPS92682-Q1 SPI インターフェイス搭載、 デュアル・チャネルの定電圧/定電流コントローラ

# 1 特長

- AEC-Q100 グレード 1 認定済み

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可

- 広い入力電圧範囲:4.5V~65V

- -40°C~150°Cの接合部温度範囲にわたって ±4% 以 内の LED 電流精度

- SPI 通信インターフェイス

- SPI のプログラム可能な機能

- スペクトラム拡散による EMI の改善

- ソフトスタートのタイミング制御

- ILED 電流と出力電圧の設定

- 電流制限、過電圧、フォルト・タイマ

- シングルおよびデュアル位相

- CV および CC モードの構成

- デュアル・チャネルのピーク電流モード (PCM) コントロ

- 低入力オフセットのレール・ツー・レール電流センス・ア ンプ

- アナログ調光

- 外部の直列 FET PWM 調光と、内蔵 P チャネル・ドラ イバ・インターフェイス

- 1000:1 を超える PWM 調光範囲

- チャネルごとのオープン・ドレインのフォルト・フラグ・イ ンジケータ

- スイッチング周波数を最高 1MHz にプログラム可能、 外部クロックとの同期も可能

- 包括的でプログラム可能なフォルト保護回路

- ウェッタブル・フランク付きの VQFN パッケージ

# 2 アプリケーション

- 車載用前方照明

- 緊急車両

- 一般的な照明

#### 3 概要

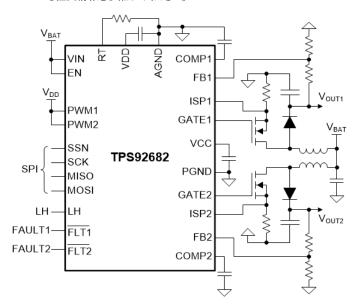

TPS92682-Q1 は、SPI 通信インターフェイスを備えたデ ュアル・チャネル・ピーク電流モード・コントローラです。本 デバイスは、定電圧 (CV) または定電流 (CC) モードで動 作するようにプログラムできます。

CV モードでは、2 つの独立した、または 2 位相の昇圧電 圧レギュレータとして動作するように、TPS92682-Q1 をプ ログラムできます。出力電圧は、外部の抵抗分圧器、およ び SPI でプログラムできる 8 ビット DAC を使用して設定 します。

CC モードでは、デュアル・チャネルの昇圧または降圧 LEDドライバ・トポロジをサポートするように設計されてい ます。LED 電流は、アナログまたは PWM 調光手法により 独立して変調できます。プログラム可能な8ビットDACを 使用して、28:1を超える範囲のアナログ的調光が可能で す。LED 電流による PWM 調光は、目的のデューティ・サ イクルで PWM 入力ピンを直接変調する方法と、SPI でプ ログラムできる 10 ビットの PWM カウンタを使用する方法 のどちらかで行います。オプションの PDRV ゲート・ドライ バ出力を使用して、外部の P チャネル直列 MOSFET を 駆動できます。

TPS92682-Q1 には、SPI でプログラムできる高度な診断 およびフォルト保護として、サイクル単位の電流制限、出 力の過電圧および低電圧保護、ILED の過電流保護、熱 警告などの機構が組み込まれています。本デバイスには、 チャネルごとにオープン・ドレインのフォルト・インジケータ 出力も内蔵されています。

TPS92682-Q1 には LH ピンが搭載されており、HIGH に 設定すると LH (Limp Home) モードが開始されます。 LH モードでは、SPI でプログラムされるレジスタの異なるセッ トを使用します。

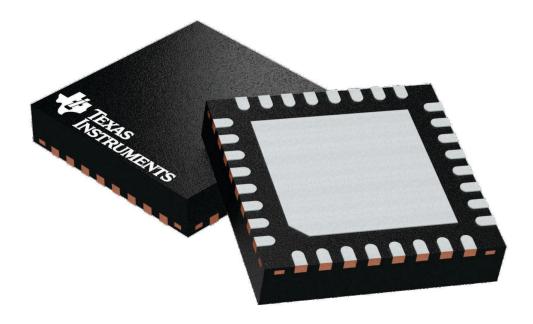

#### デバイス情報

| 部品番号        | パッケージ(1)    | 本体サイズ (公称)     |

|-------------|-------------|----------------|

| TPS92682-Q1 | VQFN (32)   | 5.0mm × 5.0mm  |

| TPS92682-Q1 | HTSSOP (32) | 11.0mm × 6.1mm |

利用可能なパッケージについては、このデータシートの末尾にあ る注文情報を参照してください。

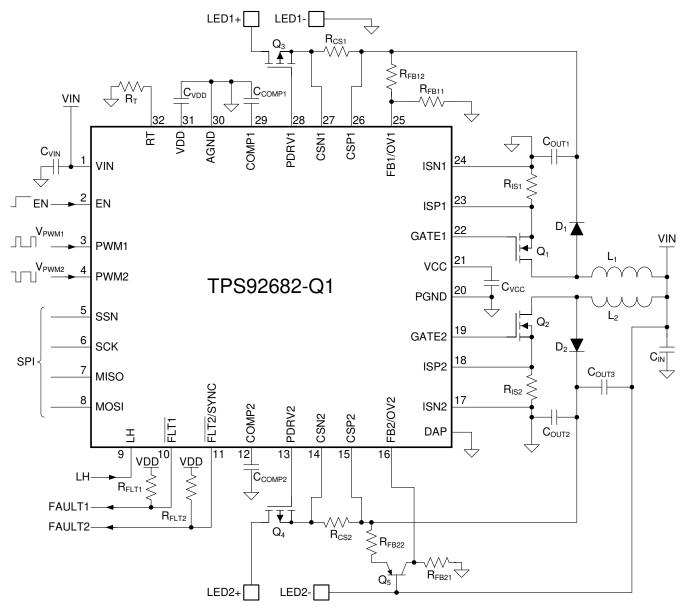

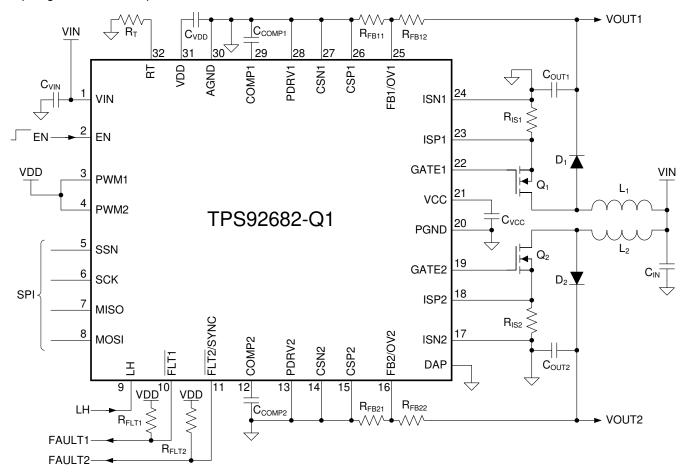

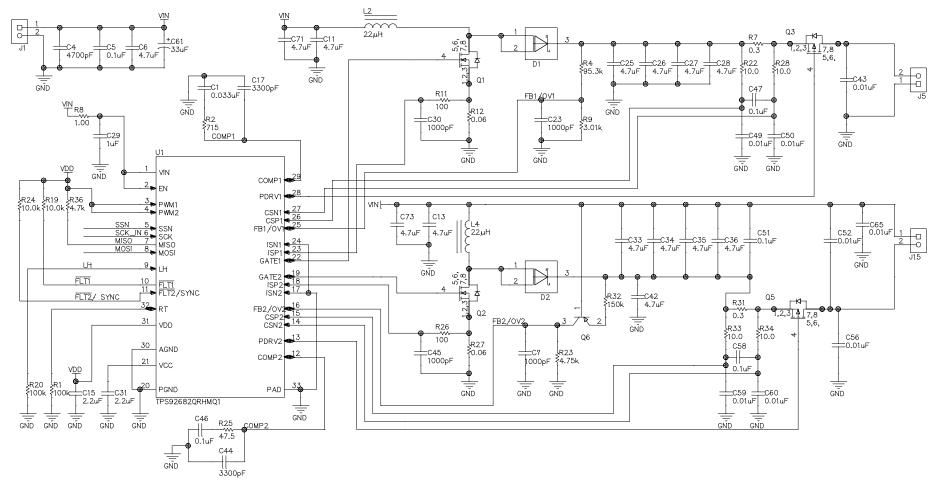

代表的なアプリケーション

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 👫 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 特長                                 | 1 | 8 Application and Implementation           | 53                                    |

|--------------------------------------|---|--------------------------------------------|---------------------------------------|

| 2 アプリケーション                           |   | 8.1 Application Information General Design |                                       |

| 3 概要                                 |   | Considerations                             | <mark>5</mark> 3                      |

| 4 Revision History                   |   | 8.2 Application Information CC Mode        | 55                                    |

| 5 Pin Configuration and Functions    |   | 8.3 Typical Application CV Mode            | 62                                    |

| 6 Specifications                     |   | 8.4 Typical Application CC Mode            |                                       |

| 6.1 Absolute Maximum Ratings         |   | 8.5 Typical Application CV Mode            | <mark>77</mark>                       |

| 6.2 ESD Ratings                      |   | 9 Power Supply Recommendations             | 83                                    |

| 6.3 Recommended Operating Conditions |   | 10 Layout                                  | 84                                    |

| 6.4 Thermal Information              |   | 10.1 Layout Guidelines                     | 84                                    |

| 6.5 Electrical Characteristics       |   | 10.2 Layout Example                        | 84                                    |

| 6.6 Typical Characteristics          |   | 11 Device and Documentation Support        | 86                                    |

| 7 Detailed Description               |   | 11.1ドキュメントの更新通知を受け取る方法                     | 86                                    |

| 7.1 Overview                         |   | 11.2 サポート・リソース                             | 86                                    |

| 7.2 Functional Block Diagram         |   | 11.3 Trademarks                            |                                       |

| 7.3 Feature Description              |   | 11.4 静電気放電に関する注意事項                         |                                       |

| 7.4 Device Functional Modes          |   | 11.5 用語集                                   |                                       |

| 7.5 Programming                      |   | 12 Mechanical, Packaging, and Orderable    |                                       |

| 7.6 TPS92682 Registers               |   | Information                                | 86                                    |

| •                                    |   |                                            |                                       |

|                                      |   |                                            | · · · · · · · · · · · · · · · · · · · |

# 4 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (July 2020) to Revision C (March 2021)   | Page |

|------------------------------------------------------------------|------|

| • RHB (VQFN) パッケージを追加                                            | 1    |

| Added RHB package thermal information                            |      |

| • Added 式 12 for the BUCK-BOOST FET RMS current                  | 53   |

| Added Programming Example for Two-Channel CC Mode section        |      |

| Added Programming Example for Two-Phase CV BOOST section         |      |

| Changes from Revision A (August 2019) to Revision B (July 2020)  | Page |

| ・「特長」に機能安全の箇条書き項目を追加                                             | 1    |

| ・ 文書全体にわたって表、図、相互参照の採番方法を更新                                      | 1    |

| Added HTSSOP package                                             | 3    |

| Added DAP package thermal information                            | 6    |

| Changes from Revision * (March 2019) to Revision A (August 2019) | Page |

| <ul><li>「事前情報」から「量産データ」に変更</li></ul>                             | 1    |

# **5 Pin Configuration and Functions**

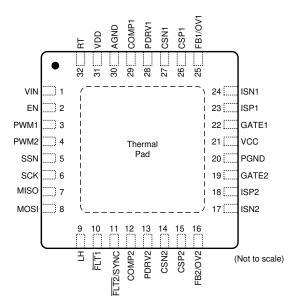

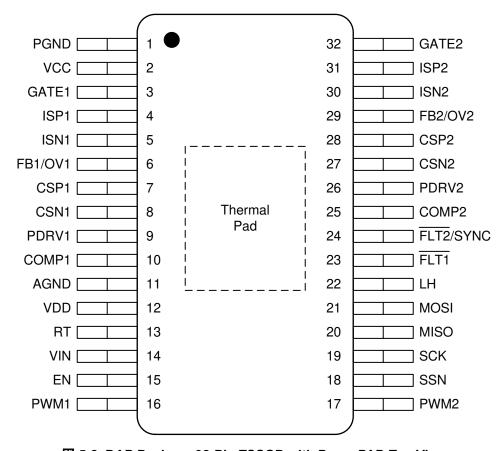

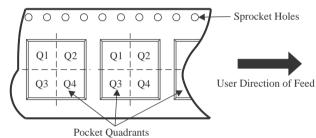

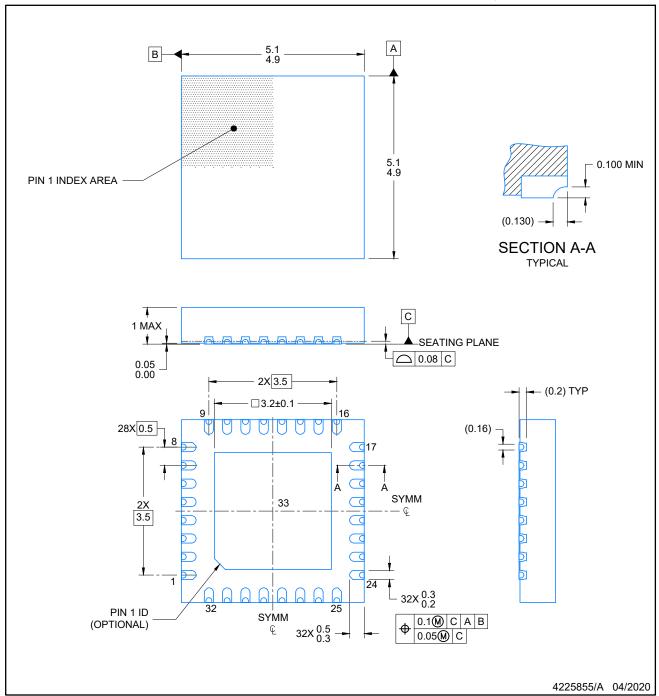

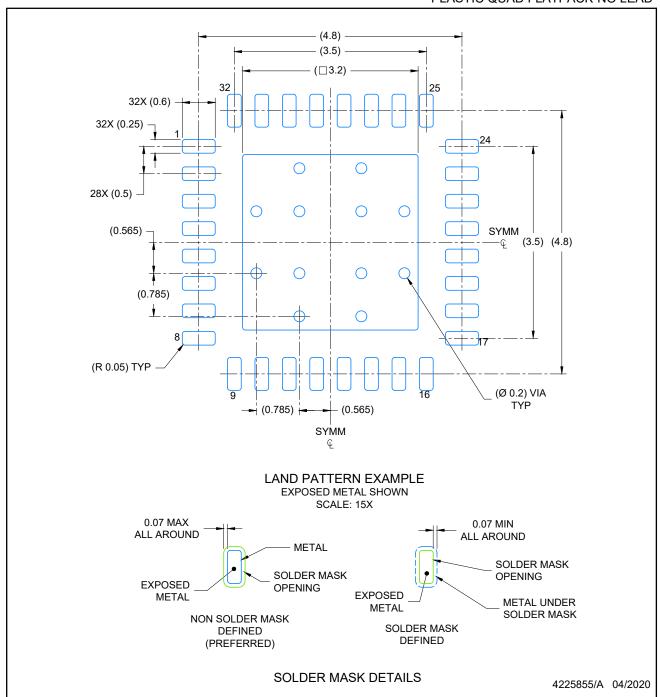

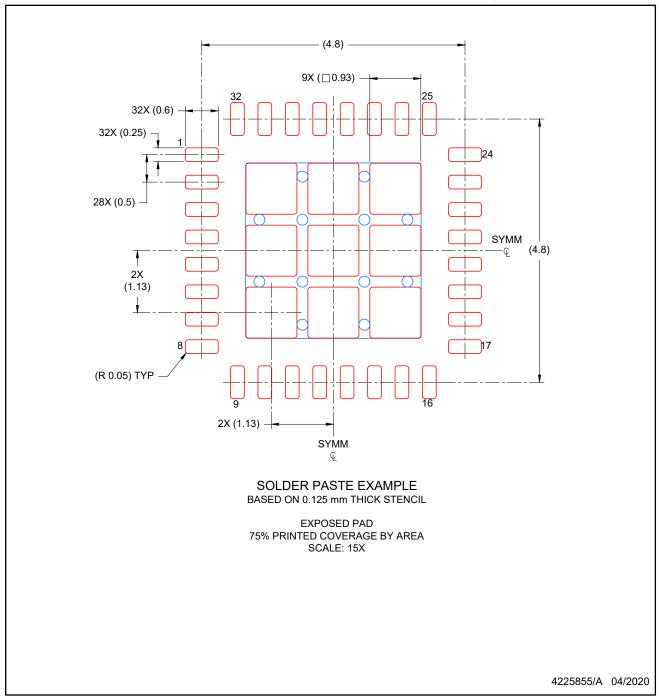

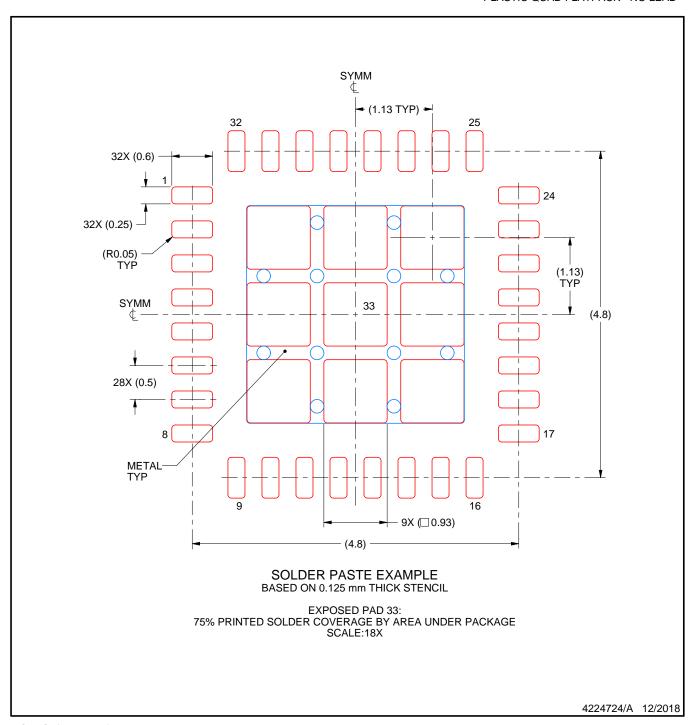

図 5-1. RHM/RHB Package 32-Pin VQFN with PowerPAD Top View

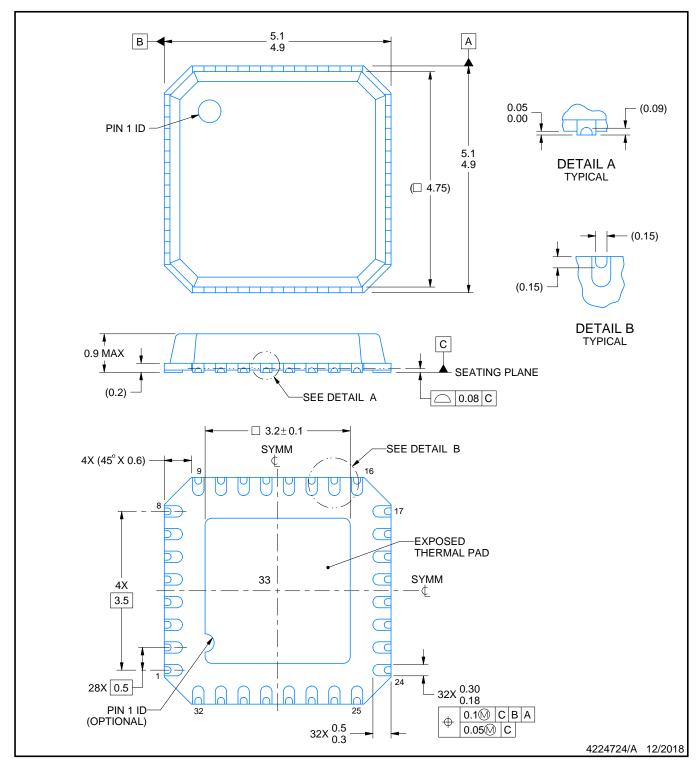

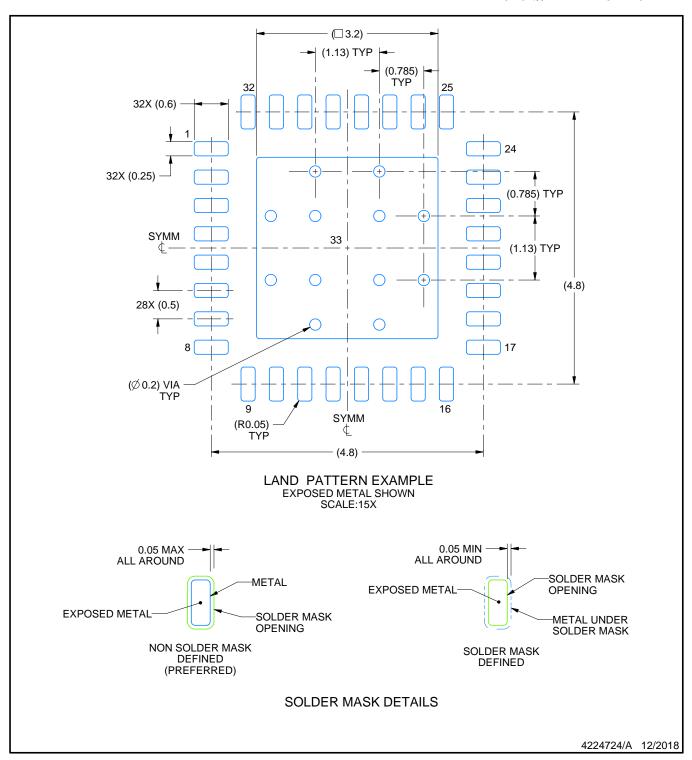

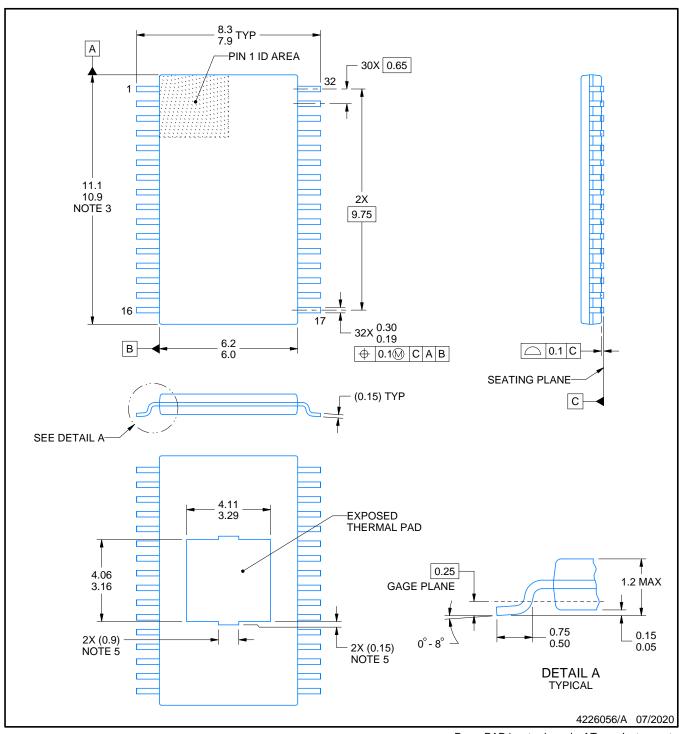

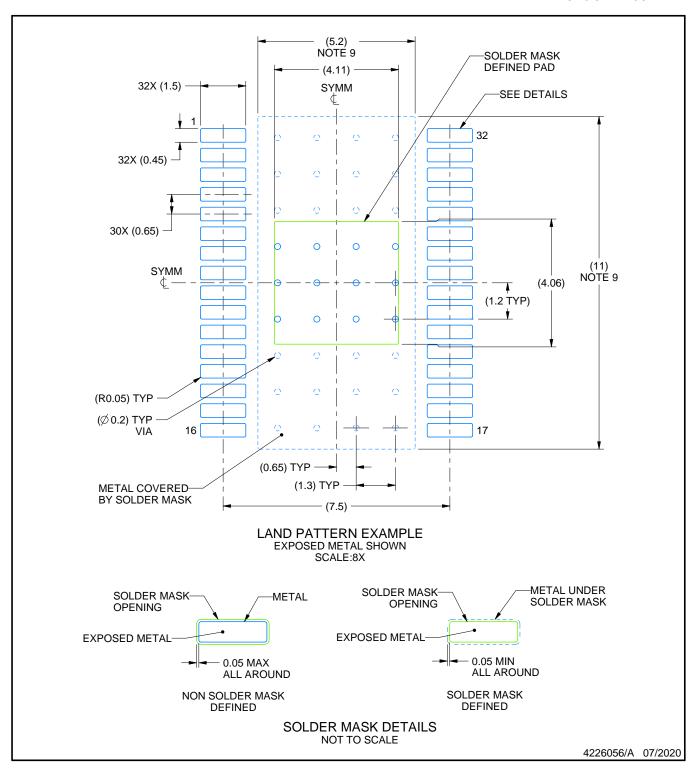

図 5-2. DAP Package 32-Pin TSSOP with PowerPAD Top View

# 表 5-1. Pin Functions

|               | PIN         |               |                    | 表 5-1. Pin Functions                                                                                                              |

|---------------|-------------|---------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| NAME          | VQFN<br>NO. | HTSSOP<br>NO. | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                       |

| AGND          | 30          | 11            | Р                  | Signal ground                                                                                                                     |

| COMP1         | 29          | 10            | I/O                | Connect to an integral or integral-proportional compensation network to ensure stability for channel-1.                           |

| COMP2         | 12          | 25            | I/O                | Connect to an integral or integral-proportional compensation network to ensure stability for channel-2.                           |

| CSN1          | 27          | 8             | I                  | High-side current sense amplifier input (–) for channel-1                                                                         |

| CSN2          | 14          | 27            | I                  | High-side current sense amplifier input (–) for channel-2                                                                         |

| CSP1          | 26          | 7             | I                  | High-side current sense amplifier input (+) for channel-1                                                                         |

| CSP2          | 15          | 28            | I                  | High-side current sense amplifier input (+) for channel-2                                                                         |

| EN            | 2           | 15            | I                  | Hardware enable. Pull this pin low to enter shutdown.                                                                             |

| FB1/OV1       | 25          | 6             | I/O                | Connect using a resistor divider to VOUT1 to set OVP threshold (and VOUT in CV mode) for channel-1.                               |

| FB2/OV2       | 16          | 29            | I/O                | Connect using a resistor divider to VOUT2 to set OVP threshold (and VOUT in CV mode) for channel-2.                               |

| FLT1          | 10          | 23            | 0                  | Open-drain fault output for channel-1 (or both channels if PIN-11 is programmed to be SYNC).                                      |

| FLT2/<br>SYNC | 11          | 24            | I/O                | Dual function pin (programmable) either open-drain fault output for channel-2 or SYNC input                                       |

| GATE1         | 22          | 3             | I/O                | Channel-1 gate driver output for external N-channel FET                                                                           |

| GATE2         | 19          | 32            | I/O                | Channel-2 gate driver output for external N-channel FET                                                                           |

| ISN1          | 24          | 5             | I                  | Switch current sense input (-) for channel-1. Connect to the GND connection of the external switch-current sense resistor.        |

| ISN2          | 17          | 30            | I                  | Switch current sense input (-) for channel-2. Connect to the GND connection of the external switch-current sense resistor.        |

| ISP1          | 23          | 4             | 1                  | Switch current sense input (+) for channel-1. Connect to external switch current sense resistor between N-channel FET and ground. |

| ISP2          | 18          | 31            | I                  | Switch current sense input (+) for channel-2. Connect to external switch current sense resistor between N-channel FET and ground. |

| LH            | 9           | 22            | I                  | Digital input, when set high, the device enters the limp home mode.                                                               |

| MISO          | 7           | 20            | 0                  | SPI slave data output                                                                                                             |

| MOSI          | 8           | 21            | I                  | SPI slave data input                                                                                                              |

| PDRV1         | 28          | 9             | I/O                | Channel-1 P-channel gate driver. Connect to gate of external series P-channel FET switch.                                         |

| PDRV2         | 13          | 26            | I/O                | Channel-2 P-channel gate driver. Connect to gate of external series P-channel FET switch.                                         |

| PWM1          | 3           | 16            | I                  | Connect to external PWM signal to enable PWM dimming for channel-1.                                                               |

| PWM2          | 4           | 17            | I                  | Connect to external PWM signal to enable PWM dimming for channel-2.                                                               |

| PGND          | 20          | 1             | Р                  | Power ground                                                                                                                      |

| RT            | 32          | 13            | I/O                | Set internal clock frequency by connecting a resistor to ground                                                                   |

| SCK           | 6           | 19            | ı                  | SPI clock input                                                                                                                   |

| SSN           | 5           | 18            | ı                  | SPI chip select input                                                                                                             |

| VCC           | 21          | 2             | Р                  | 7.5-V low-dropout regulator output                                                                                                |

| VDD           | 31          | 12            | Р                  | 5-V LDO output                                                                                                                    |

| VIN           | 1           | 14            | Р                  | High-voltage input (65 V) to internal LDO                                                                                         |

<sup>(1)</sup> I = input, O = output, P = power

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1) (2)

|                                       |                                      | MIN                   | MAX              | UNIT |

|---------------------------------------|--------------------------------------|-----------------------|------------------|------|

|                                       | VIN, EN, CSPx, CSNx                  | -0.3                  | 65               | V    |

|                                       | CSPx to CSNx (3)                     | -0.3                  | 0.3              | V    |

| In not to talk and                    | ISPx, ISNx                           | -0.3                  | 8.8              | V    |

| Input voltage                         | SSN, SCK, MOSI, LH, RT, FLTx         | -0.3                  | 5.5              | V    |

|                                       | FBx/OVx                              | -0.3                  | 5.5              | V    |

|                                       | PWMx                                 | -0.3                  | 5.5              | V    |

|                                       | VCC, GATEx                           | -0.3                  | 8.8              | V    |

|                                       | VDD                                  | -0.3                  | 5.5              | V    |

| Output voltage <sup>(4)</sup>         | PDRV                                 | V <sub>CSP</sub> -8.8 | V <sub>CSP</sub> | V    |

|                                       | MISO                                 | -0.3                  | 5.5              | V    |

|                                       | COMPx                                | -0.3                  | 4                | V    |

| Source current                        | I <sub>GATE</sub> , (pulsed < 20 ns) |                       | 500              | mA   |

| Source current                        | I <sub>PDRV</sub> , (pulsed < 10 μs) |                       | 50               | mA   |

| Sink current                          | I <sub>GATE</sub> (pulse < 20 ns)    |                       | 500              | mA   |

| Silik Culterit                        | I <sub>DDRV</sub> (pulse < 10 μs)    |                       | 50               | mA   |

| Operating junction temperate          | ure, T <sub>J</sub>                  | -40                   | 150              | °C   |

| Storage temperature, T <sub>stg</sub> |                                      |                       | 165              | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |               |                                                                   | VALUE | UNIT |

|--------------------|---------------|-------------------------------------------------------------------|-------|------|

| V                  | Electrostatic | Human-body model (HBM), per AEC Q100-002, all pins <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per AEC Q100-011                      | ±500  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                     |                                                                | MIN                  | NOM | MAX                  | UNIT |

|-------------------------------------|----------------------------------------------------------------|----------------------|-----|----------------------|------|

| VIN                                 | Supply input voltage                                           | 6.5                  | 14  | 65                   | V    |

| VIN, crank                          | Supply input, battery crank voltage                            | 4.5                  |     |                      | V    |

| V <sub>CSP</sub> , V <sub>CSN</sub> | Current sense common mode voltage (1)                          | 0                    |     | 60                   | V    |

| f <sub>SW</sub>                     | Switching frequency                                            | 100                  |     | 700                  | kHz  |

| f <sub>SYNC</sub>                   | Synchronization frequency range, vs f <sub>CLK</sub> set by RT | 0.8×f <sub>CLK</sub> |     | 1.2×f <sub>CLK</sub> | Hz   |

| F <sub>SS</sub>                     | Spread-spectrum modulation frequency                           | 0.1                  |     | 10                   | kHz  |

| T <sub>A</sub>                      | Operating ambient temperature                                  | -40                  |     | 125                  | °C   |

<sup>(1)</sup> For current sense common mode voltage below 6.5 V, PFET dimming may not be applied

<sup>(2)</sup> All voltages are with respect to GND unless otherwise noted

<sup>(3)</sup> Continuous sustaining voltage

<sup>(4)</sup> All output pins are not specified to have an external voltage applied.

# **6.4 Thermal Information**

|                       |                                              |               | TPS92682-Q1   |                 |      |

|-----------------------|----------------------------------------------|---------------|---------------|-----------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RHM<br>(VQFN) | RHB<br>(VQFN) | DAP<br>(HTSSOP) | UNIT |

|                       |                                              | 32 PINS       | 32 PINS       | 32 PINS         |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 31.2          | 31.6          | 27.3            | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 21.9          | 22.0          | 18.7            | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 12.1          | 11.7          | 9.7             | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.2           | 0.3           | 0.2             | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 12.0          | 11.7          | 9.6             | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.3           | 2.3           | 2.1             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}$ ,  $\text{V}_{\text{IN}}$ = 14V, VIADJDACx = 0xDF,  $\text{C}_{\text{VCC}}$  = 1 $\mu$ F,  $\text{C}_{\text{VDD}}$  = 1 $\mu$ F,  $\text{C}_{\text{COMP}}$  = 2.2nF,  $\text{R}_{\text{CS}}$  = 100m $\Omega$ ,  $\text{R}_{\text{T}}$  = 50k $\Omega$ ,  $\text{V}_{\text{PWM}}$  = 5V, no load on GATE and PDRV, DIV=4 (unless otherwise noted)

|                           | PARAMETER                       | TEST CONDITIONS                                                                      | MIN      | TYP   | MAX  | UNIT |

|---------------------------|---------------------------------|--------------------------------------------------------------------------------------|----------|-------|------|------|

| INPUT VOLTAC              | GE (VIN)                        |                                                                                      |          |       |      |      |

| I <sub>IN-SHDN</sub>      | Input shutdown current          | V <sub>EN</sub> = 0 V, V <sub>CSP</sub> = V <sub>CSN</sub> = V <sub>PDRV</sub> = 0 V |          | 10    |      | μА   |

|                           |                                 | V <sub>EN</sub> = 0 V, V <sub>CSP</sub> = 14 V                                       |          | 10.5  |      |      |

| I <sub>IN-STBY</sub>      | Input standby current           | Software EN1 and EN2 = 0, V <sub>PWM1</sub> = V <sub>PWM2</sub> = 0 V                |          | 2.3   |      | mA   |

| I <sub>IN-SW</sub>        | Supply switching current        | VCC=7.5V, C <sub>GATEx</sub> = 1nF, Both channels are switching                      |          | 10    |      | mA   |

| VCC BIAS SUP              | PPLY                            |                                                                                      |          |       |      |      |

|                           |                                 | VCC rising threshold,<br>V <sub>VIN</sub> = 8 V                                      |          | 4.5   | 4.9  | V    |

| VCC <sub>UVLO</sub>       | Supply under-voltage protection | VCC falling threshold,<br>V <sub>VIN</sub> = 8 V                                     | 3.7      | 4.1   |      | V    |

|                           |                                 | Hysteresis                                                                           |          | 411   |      | mV   |

| VCC <sub>(REG)</sub>      | VCC regulation voltage          | No load                                                                              | 7        | 7.5   | 8    | V    |

| I <sub>VCC(LIMIT)</sub>   | VCC current limit               | V <sub>VCC</sub> = 0 V                                                               | 40       |       |      | mA   |

| VCC <sub>DO</sub>         | VCC LDO dropout voltage         | I <sub>VCC</sub> = 30 mA, V <sub>VIN</sub> = 4.5 V                                   |          | 300   | 475  | mV   |

| VDD BIAS SUP              | PPLY                            |                                                                                      |          |       |      |      |

| VDD <sub>(REG)</sub>      | VDD regulation voltage          | No load                                                                              | 4.85     | 5     | 5.25 | V    |

| VDD <sub>(POR-RISE)</sub> | VDD rising threshold            | V <sub>VIN</sub> = 5 V                                                               |          |       | 4.1  | V    |

| VDD <sub>(POR-FALL)</sub> | VDD falling threshold           | V <sub>VIN</sub> = 5 V                                                               | 2.58     |       |      | V    |

| VDD <sub>DO</sub>         | VDD LDO dropout voltage         | I <sub>VDD</sub> = 15 mA, V <sub>VIN</sub> = 4.5 V                                   |          |       | 400  | mV   |

| I <sub>VDD(LIMIT)</sub>   | VDD current limit               | V <sub>VDD</sub> = 0 V                                                               | 30       | 39    | 50   | mA   |

| ENABLE INPU               | Т                               |                                                                                      |          |       |      |      |

| V <sub>EN</sub>           | EN voltage threshold            |                                                                                      | 1.12     | 1.21  | 1.3  | V    |

| V <sub>EN-HYS</sub>       | EN pin hysteresis               | Difference between rising and falling threshold                                      |          | 100   |      | mV   |

| I <sub>EN</sub>           | EN PIN input bias current       | V <sub>EN</sub> = 14 V                                                               |          | 5     |      | μΑ   |

| OSCILLATOR                |                                 |                                                                                      |          |       |      |      |

| •                         | 0 "1" (                         | RT = 200kΩ, DIV=4                                                                    | 85       | 100   | 115  | kHz  |

| f <sub>SW</sub>           | Switching frequency             | RT = 50kΩ, DIV=4                                                                     | 340      | 400   | 460  | kHz  |

| V <sub>RT</sub>           | RT PIN voltage                  |                                                                                      |          | 1     |      | V    |

| SPREAD SPEC               | TRUM DAC                        |                                                                                      |          |       |      |      |

| DAC <sub>DT-BITs</sub>    | Internal DAC resolution         |                                                                                      |          | 8     |      | Bits |

| DAC <sub>DT-MAX</sub>     | DAC maximum voltage             |                                                                                      |          | 1.156 |      | V    |

| DAC <sub>DT-MIN</sub>     | DAC minimum voltage             |                                                                                      |          | 855   |      | mV   |

| GATE DRIVER               |                                 |                                                                                      |          |       |      | I    |

| R <sub>GH</sub>           | Driver pull-up resistance       | I <sub>GATE</sub> = -10 mA                                                           |          | 5.1   | 11.2 | Ω    |

| R <sub>GL</sub>           | Driver pull-down resistance     | I <sub>GATE</sub> = 10 mA                                                            |          | 4.1   | 10.5 | Ω    |

|                           | RENT SENSE and ILIMIT           | 1 - 77                                                                               |          |       |      | I    |

|                           | ILIM threshold PWM = LOW        | V <sub>PWMx</sub> = 0 V, CHxILIM = XX                                                | 649      | 711   | 769  | mV   |

|                           |                                 | V <sub>PWMx</sub> = 5 V, CHxILIM = 11                                                | 228      | 253   | 277  | mV   |

| V <sub>ILIM(THR)</sub>    |                                 | $V_{PWMx}$ = 5 V, CHxILIM = 10                                                       | 132      | 151   | 171  | mV   |

| ()                        | ILIM threshold PWM = HIGH       | V <sub>PWMx</sub> = 5 V, CHxILIM = 01                                                | 82       | 100.6 | 119  | mV   |

|                           |                                 | $V_{PWMx} = 5 \text{ V, CHxILIM} = 00$                                               | 57       | 75.2  | 93   | mV   |

|                           |                                 | - FVVIVIX 0 1, 0                                                                     | <u> </u> | . 5.2 |      |      |

# **6.5 Electrical Characteristics (continued)**

$-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \text{ V}_{\text{IN}} = 14\text{V}, \text{ VIADJDACx} = 0\text{xDF}, \text{ C}_{\text{VCC}} = 1\mu\text{F}, \text{ C}_{\text{VDD}} = 1\mu\text{F}, \text{ C}_{\text{COMP}} = 2.2\text{nF}, \text{ R}_{\text{CS}} = 100\text{m}\Omega, \text{ R}_{\text{T}} = 50\text{k}\Omega, \text{ V}_{\text{PWM}} = 5\text{V}, \text{ no load on GATE and PDRV}, \text{DIV=4 (unless otherwise noted)}$

|                            | PARAMETER                                                         | TEST CONDITIONS                                                | MIN   | TYP   | MAX   | UNIT          |

|----------------------------|-------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|-------|---------------|

|                            | Loading adge blanking                                             | CHxLEB = 0                                                     |       | 75    |       | ns            |

| IS(BLANK)                  | Leading edge blanking                                             | CHxLEB = 1                                                     |       | 150   |       | ns            |

| t <sub>ILIMIT(DELAY)</sub> | ISx to GATEx delay                                                |                                                                |       | 86    |       | ns            |

| PWM COMPAR                 | RATOR                                                             |                                                                |       |       |       |               |

| D <sub>MAX</sub>           | Maximum duty cycle                                                |                                                                |       | 90    |       | %             |

| V <sub>LVx-Delta</sub>     | Difference between CH1 and CH2 PWM comparator offset              |                                                                | -17.5 |       | 17.5  | mV            |

| $I_{LVx}$                  | IS level shift bias current                                       | No slope compensation added                                    |       | 40    |       | μA            |

| T <sub>PWM-Delta</sub>     | Turn-off propagation delay from input of PWM comp. to gate output |                                                                |       | 100   |       | ns            |

| T <sub>PWMDEL-Delta</sub>  | Difference between CH1 and CH2<br>PWM comp. propagation delay     |                                                                | -30   |       | 30    | ns            |

| CURRENT SEN                | NSE AMPLIFIER (CSP, CSN)                                          |                                                                |       |       |       |               |

|                            |                                                                   | V <sub>CSP(CM)</sub> = 14 V, IADJDAC = 0×FF                    | 165.8 | 172.7 | 179.6 | mV            |

| $V_{(CSP-CSN)x}$           | Current Sense REG Voltage                                         | V <sub>CSP(CM)</sub> = 14V, IADJDAC = 0x95                     | 96.5  | 100.8 | 104.5 | mV            |

| ,                          |                                                                   | V <sub>CSP(CM)</sub> = 14V, IADJDAC = 0×0F                     |       | 10.3  |       | mV            |

| CS <sub>(BW)</sub>         | Current sense unity gain bandwidth                                |                                                                |       | 500   |       | kHz           |

| G <sub>CS</sub>            | Current Sense Gain = V <sub>IADJ</sub> /V <sub>(CSP-CSN)</sub>    | V <sub>CS</sub> = 150 mV, V <sub>CSP</sub> = 60 V              |       | 14    |       | V/V           |

| K <sub>(OCP)</sub>         | Ratio of over-current detection threshold to V <sub>IADJ</sub>    | $K_{(OCP)} = V_{(OCP-THR)}/V_{IADJ}$                           | 1.41  | 1.53  | 1.66  | V/V           |

| K <sub>(UC)</sub>          | Ratio of under-current detection threshold to V <sub>IADJ</sub>   | $K_{(UC)} = V_{(UC-THR)}/V_{IADJ}$                             |       | 0.5   |       | V/V           |

| I <sub>CSP(BIAS)</sub>     | CSP bias current                                                  | $V_{CSP} = V_{CSN} = V_{PDRV} = 14 \text{ V}$                  |       | 59    |       | μA            |

| I <sub>CSN(BIAS)</sub>     | CSN bias current                                                  | V <sub>CSP</sub> = V <sub>CSN</sub> = V <sub>PDRV</sub> = 14 V |       | 59    |       | μA            |

| SSDAC                      |                                                                   |                                                                |       |       |       |               |

| DAC <sub>SS-BITs</sub>     | Internal DAC resolution                                           |                                                                |       | 8     |       | Bits          |

| DAC <sub>SS-FS</sub>       | DAC full scale voltage                                            |                                                                |       | 2.8   |       | V             |

| CALDAC                     |                                                                   |                                                                |       |       |       |               |

| DAC <sub>CAL-BITs</sub>    | Switch current sense calibration DAC                              |                                                                |       | 3     |       | Bits          |

| DAC <sub>CAL-RES</sub>     | Offset-per-Bit applied to the switch current sense                |                                                                |       | 2.5   |       | mV            |

| FAULT FLAG (               | FLTx)                                                             |                                                                |       |       |       |               |

| R <sub>(FLT)</sub>         | Open-drain pull down resistance                                   |                                                                |       | 36    |       | Ω             |

| DAC <sub>ADJ-BITs</sub>    | Internal DAC resolution                                           |                                                                |       | 8     |       | Bits          |

| DAC <sub>ADJ-FS</sub>      | DAC full scale voltage                                            |                                                                | 2.32  | 2.4   | 2.48  | V             |

| ERROR AMPL                 |                                                                   |                                                                |       |       |       | l             |

|                            |                                                                   | HG = 0                                                         |       | 122   |       |               |

| 9м                         | Transconductance                                                  | HG = 1                                                         |       | 914   |       | μ <b>Α</b> /\ |

|                            |                                                                   | IADJx = 0×95, V <sub>(CSP-CSN)</sub> = 0 V, HG = 0             |       | 129   |       | _             |

| I <sub>COMP(SRC)</sub>     | COMP source current capacity                                      | IADJx = 0×95, V <sub>(CSP-CSN)</sub> = 0 V, HG =               |       | 777   |       | μA            |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# **6.5 Electrical Characteristics (continued)**

$-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}$ ,  $\text{V}_{\text{IN}}$ = 14V, VIADJDACx = 0xDF,  $\text{C}_{\text{VCC}}$  = 1 $\mu$ F,  $\text{C}_{\text{VDD}}$  = 1 $\mu$ F,  $\text{C}_{\text{COMP}}$  = 2.2nF,  $\text{R}_{\text{CS}}$  = 100m $\Omega$ ,  $\text{R}_{\text{T}}$  = 50k $\Omega$ ,  $\text{V}_{\text{PWM}}$  = 5V, no load on GATE and PDRV, DIV=4 (unless otherwise noted)

|                                                                 | PARAMETER                                | TEST CONDITIONS                                                                                                         | MIN  | TYP   | MAX  | UNIT     |

|-----------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------|-------|------|----------|

|                                                                 | 00110                                    | IADJx = 0×00, V <sub>(CSP-CSN)</sub> = 0.1 V, HG<br>= 0                                                                 |      | 129   |      |          |

| COMP(SINK)                                                      | COMP sink current capacity               | IADJx = 0×00, V <sub>(CSP-CSN)</sub> = 0.1 V, HG<br>= 1                                                                 |      | 783   |      | μA       |

| ΓΛ                                                              | Former and life on beauty sightle        | Gain = -3 dB, HG = 0                                                                                                    |      | 5     |      | NAL 1-   |

| EA <sub>(BW)</sub>                                              | Error amplifier bandwidth                | Gain = -3 dB, HG = 1                                                                                                    |      | 1     |      | MHz      |

| V <sub>COMP(RST)</sub>                                          | V <sub>COMP</sub> reset voltage          |                                                                                                                         |      | 100   |      | mV       |

| R <sub>COMP(DCH)</sub>                                          | COMPx discharge FET R <sub>DSON</sub>    |                                                                                                                         |      | 248   |      | Ω        |

| R <sub>COMP(DIFF)</sub>                                         | COMP1 to COMP2 short path resistance     |                                                                                                                         |      | 300   |      | Ω        |

| SLOPEDAC                                                        |                                          |                                                                                                                         |      |       |      |          |

| DAC <sub>SLP-FS</sub>                                           | DAC full scale voltage                   |                                                                                                                         |      | 0.36  |      | V        |

| VFB                                                             |                                          | -                                                                                                                       |      |       |      | •        |

| VFB <sub>ERR</sub>                                              | Regulation voltage error                 |                                                                                                                         | -4   |       | 4    | %        |

| VFB <sub>BIAS</sub>                                             | V <sub>FB</sub> pin pull up bias current |                                                                                                                         |      | 200   |      | nA       |

| OVDAC                                                           |                                          |                                                                                                                         |      |       |      | 1        |

|                                                                 | OV limit threshold, 0%                   | CHxOVDAC = 000                                                                                                          | 1.2  | 1.237 | 1.27 | V        |

|                                                                 | OV limit threshold, 2.5%                 | CHxOVDAC = 001                                                                                                          |      | 1.268 |      | V        |

|                                                                 | OV limit threshold, 5%                   | CHxOVDAC = 010                                                                                                          |      | 1.299 |      | V        |

|                                                                 | OV limit threshold, 7.5%                 | CHxOVDAC = 011                                                                                                          |      | 1.329 |      | V        |

| $V_{OV(THR)}$                                                   | OV limit threshold, 10%                  | CHxOVDAC = 100                                                                                                          |      | 1.36  |      | V        |

|                                                                 | OV limit threshold, 12.5%                | CHxOVDAC = 101                                                                                                          |      | 1.391 |      | V        |

|                                                                 | OV limit threshold, 15%                  | CHxOVDAC = 110                                                                                                          |      | 1.422 |      | V        |

|                                                                 | OV limit threshold, 20%                  | CHxOVDAC = 111                                                                                                          |      | 1.483 |      | V        |

| I <sub>OV-HYS</sub>                                             | OV hysteresis current                    |                                                                                                                         | 11.5 | 20.5  | 28.5 | μA       |

| UV (Output Un                                                   | <u> </u>                                 |                                                                                                                         |      |       |      | <u> </u> |

| V <sub>UV(THR)</sub>                                            | Under voltage protection threshold       |                                                                                                                         | 40   | 53.2  | 67   | mV       |

| t <sub>UV(BLANK)</sub>                                          | Under voltage blanking period            |                                                                                                                         |      | 5     |      | μs       |

| ,                                                               | Ts (PWMx, SYNC, LH, SSN, SCK, M          | OSI)                                                                                                                    |      |       |      | μ-0      |

| I <sub>BIAS</sub>                                               | Input bias current                       | Except PWM inputs                                                                                                       |      |       | 1    | μA       |

| VT <sub>INPUT-FALL</sub>                                        | Falling threshold                        | Z/copt. Tim inputs                                                                                                      | 0.7  |       | •    | V        |

| VT <sub>INPUT-RISE</sub>                                        | Rising threshold                         |                                                                                                                         | 0.7  |       | 1.85 | V        |

| PWM INPUT (F                                                    |                                          |                                                                                                                         |      |       | 1.00 | V        |

| R <sub>PWM(PD)</sub>                                            | PWM pull-down resistance                 |                                                                                                                         |      | 10    |      | ΜΩ       |

| t <sub>DLY(RISE)</sub>                                          | PWM rising to PDRV delay                 | C <sub>PDRV</sub> = 1 nF                                                                                                |      | 235   |      | ns       |

|                                                                 | PWM falling to PDRV delay                | C <sub>PDRV</sub> = 1 nF                                                                                                |      | 222   |      | ns       |

| t <sub>DLY(FALL)</sub><br>PFET GATE DI                          |                                          | ~FDKV                                                                                                                   |      |       |      | 110      |

| V <sub>PDRV(OFF)</sub>                                          | PDRV off-state voltage                   | V <sub>CSP</sub> = 14 V                                                                                                 |      | 14    |      | V        |

|                                                                 | PDRV on-state voltage                    | V <sub>CSP</sub> = 14 V                                                                                                 |      | 7.34  |      | V        |

| VDDDVVQVV                                                       | ום זייום אורי סוו־state voltage          | * -:                                                                                                                    |      | 29    |      | mA       |

| -                                                               | DDRV sink current                        | \\ \\ \- \\ 5 \\ nulcod < 100 uc                                                                                        |      |       |      | ı IIIA   |

| I <sub>PDRV(SINK)</sub>                                         | PDRV sink current                        | V <sub>CSP</sub> – V <sub>PDRV</sub> = 5 V, pulsed < 100 μs                                                             |      |       |      |          |

| V <sub>PDRV(ON)</sub> I <sub>PDRV(SINK)</sub> R <sub>PDRV</sub> | PDRV pull up resistance                  | V <sub>CSP</sub> - V <sub>PDRV</sub> = 5 V, pulsed < 100 μs $V_{CSP} - V_{PDRV} = 0 \text{ V, pulsed} < 100 \text{ μs}$ |      | 83.5  |      | Ω        |

| I <sub>PDRV(SINK)</sub>                                         | PDRV pull up resistance                  |                                                                                                                         |      |       |      |          |

# **6.5 Electrical Characteristics (continued)**

$-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \text{ V}_{\text{IN}} = 14\text{V}, \text{ VIADJDACx} = 0\text{xDF}, \text{ C}_{\text{VCC}} = 1\mu\text{F}, \text{ C}_{\text{VDD}} = 1\mu\text{F}, \text{ C}_{\text{COMP}} = 2.2\text{nF}, \text{ R}_{\text{CS}} = 100\text{m}\Omega, \text{ R}_{\text{T}} = 50\text{k}\Omega, \text{ V}_{\text{PWM}} = 5\text{V}, \text{ no load on GATE and PDRV, DIV=4 (unless otherwise noted)}$

|                       | PARAMETER                   | TEST CONDITIONS                                                                                                                       | MIN | TYP | MAX                 | UNIT |

|-----------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------------|------|

| C <sub>MISO</sub>     |                             |                                                                                                                                       |     | 10  |                     | pF   |

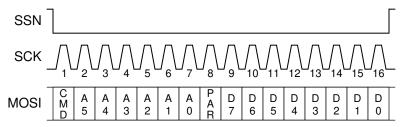

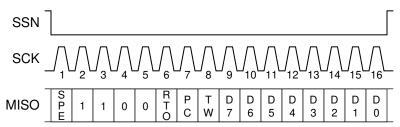

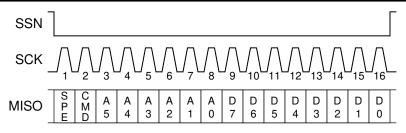

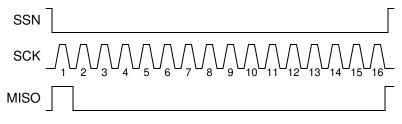

| t <sub>ss-su</sub>    | SSN setup time              | Falling edge of SSN to 1st SCK rising edge                                                                                            | 500 |     |                     | ns   |

| t <sub>ss-H</sub>     | SSN hold time               | Falling edge of 16 <sup>th</sup> SCK to SSN rising edge                                                                               | 250 |     |                     | ns   |

| t <sub>ss-HI</sub>    | SSN high time               | Time SSN must remain high between transactions                                                                                        | 1   |     |                     | μs   |

| t <sub>SCK</sub>      | SCK period                  | Clock period                                                                                                                          | 500 |     |                     | ns   |

| D <sub>SCK</sub>      | SCK duty cycle              | Clock duty cycle                                                                                                                      | 40  |     | 60                  | %    |

| t <sub>MOSI-SU</sub>  | MOSI setup time             | MOSI valid to rising edge SCK                                                                                                         | 125 |     |                     | ns   |

| t <sub>MOSI-H</sub>   | MOSI hold time              | MOSI valid after rising edge SCK                                                                                                      | 140 |     |                     | ns   |

| t <sub>MISO-HIZ</sub> | MISO tristate time          | Time to tristate MISO after SSN rising edge                                                                                           | 110 |     | 320                 | ns   |

| t <sub>MISO-HL</sub>  | MISO valid high-to-low      | Time to place valid "0" on MISO after falling SCK edge.                                                                               |     |     | 320                 | ns   |

| t <sub>MISO-LH</sub>  | MISO valid low-to-high      | Time to tri-state MISO after falling SCK edge. t <sub>RC</sub> is the time added by the application total capacitance and resistance. |     |     | 320+t <sub>RC</sub> | ns   |

| T <sub>ZO-HL</sub>    | MISO drive time high-to-low | SSN Falling Edge to MISO Falling                                                                                                      |     |     | 320                 | ns   |

Product Folder Links: TPS92682-Q1

ibmit Document Feedback

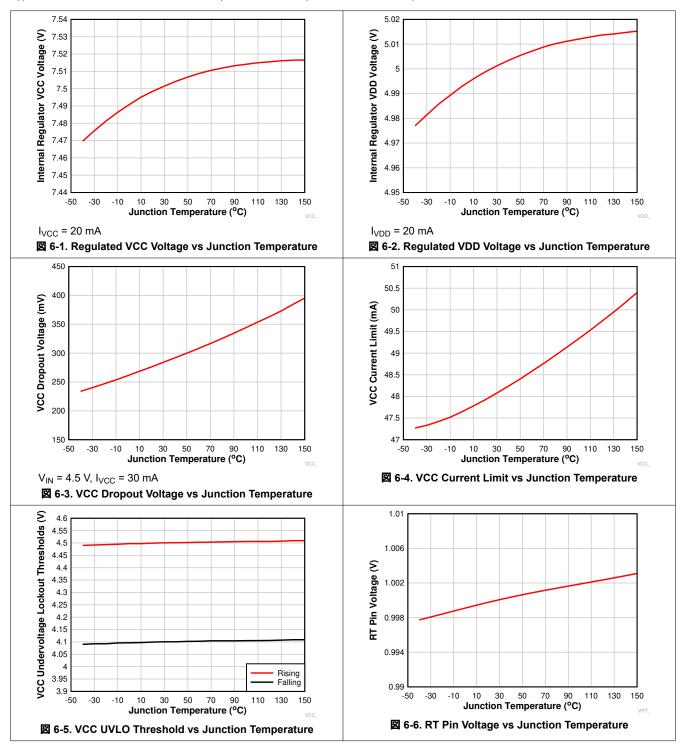

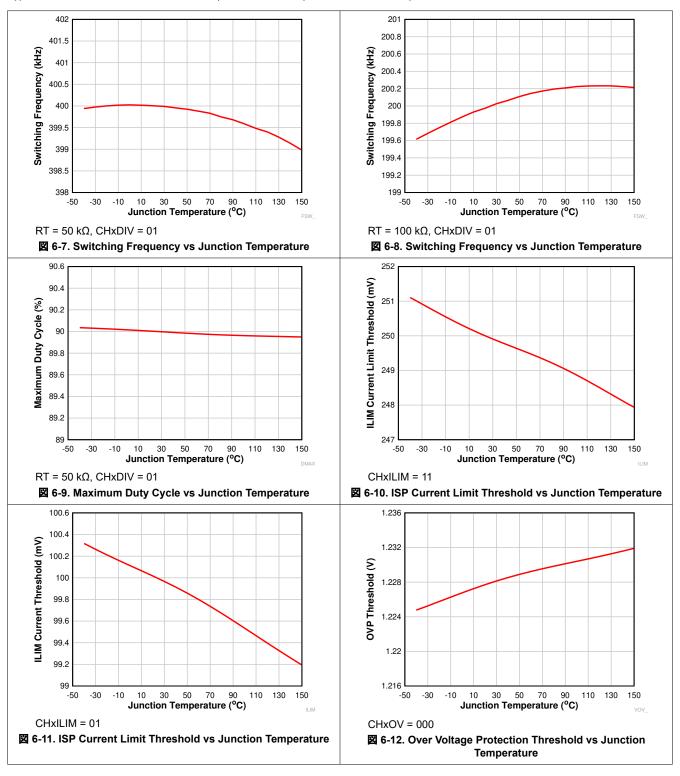

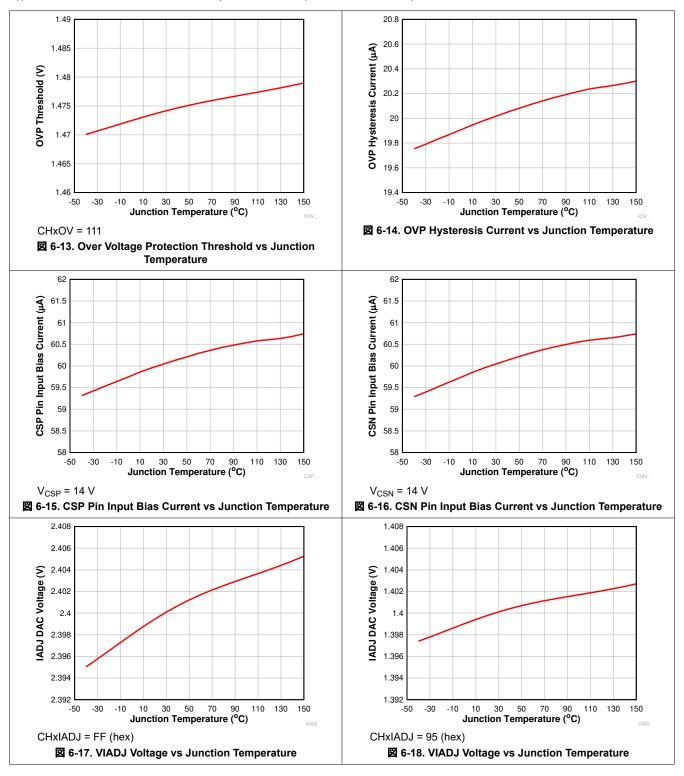

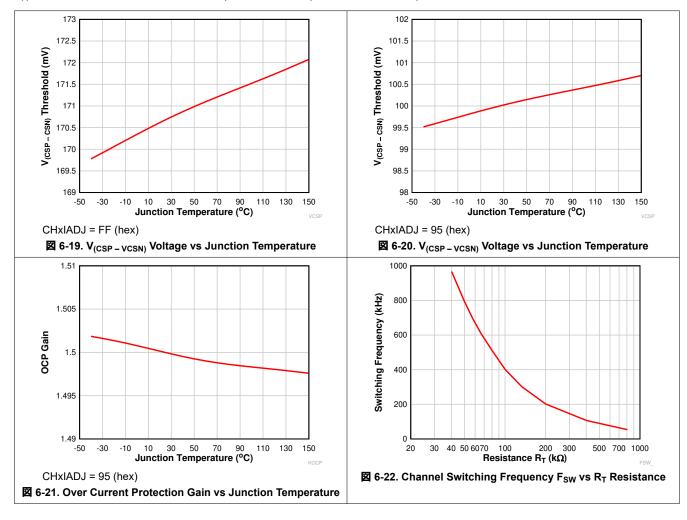

# **6.6 Typical Characteristics**

# 6.6 Typical Characteristics (continued)

# **6.6 Typical Characteristics (continued)**

# **6.6 Typical Characteristics (continued)**

# 7 Detailed Description

### 7.1 Overview

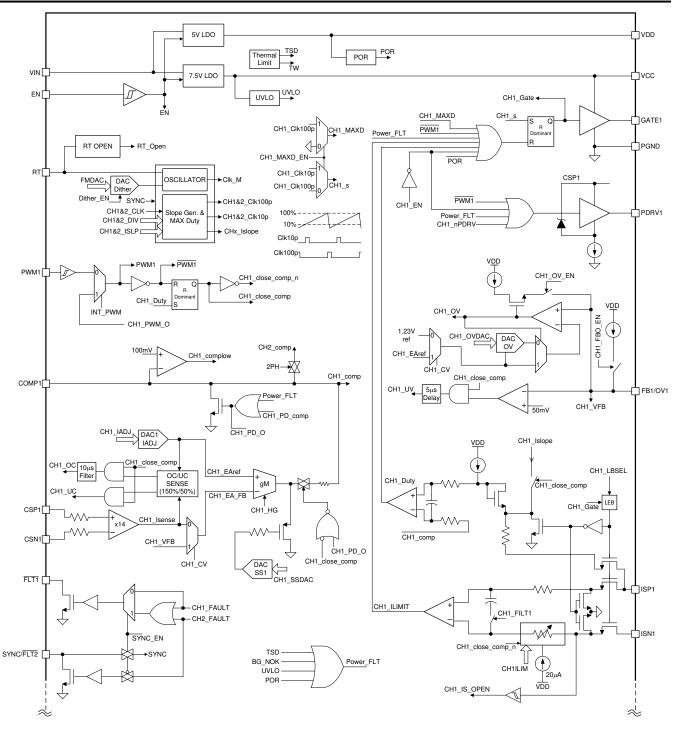

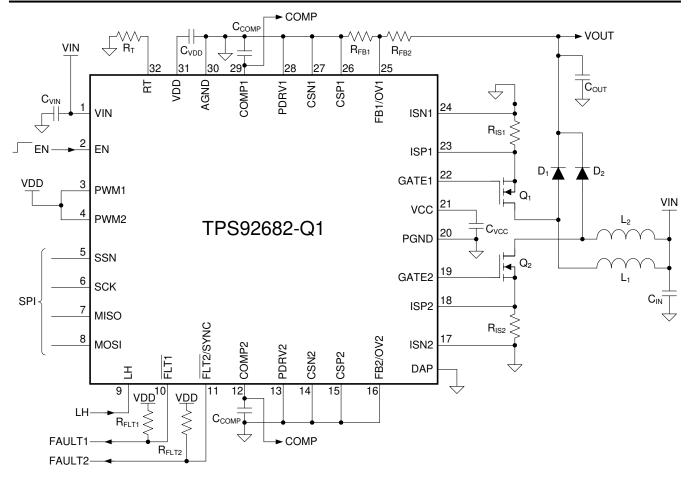

The TPS92682-Q1 device is an automotive-grade two-channel controller with Serial Peripheral Interface (SPI) interface, ideally suited for exterior lighting applications. The device is optimized to achieve high-performance solutions and features all of the functions necessary to implement LED drivers based on step-up or step-down power converter topologies with a small form-factor at a lower cost.

The two channels of the TPS92682-Q1 device can be configured independently as CC (constant current) or CV (constant voltage) mode. The device implements fixed-frequency peak current mode control to achieve regulation and fast dynamic response. Each channel can be configured as boost, boost-to-battery, SEPIC, or other converter topologies.

In CC mode, the integrated low offset and rail-to-rail current sense amplifier provide the flexibility required to power a single string consisting of 1 to 20 series connected LEDs while maintaining 4% current accuracy over the operating temperature range. The LED current regulation threshold is set by the analog adjust input CHxIADJ register over 28:1 dimming range. The TPS92682-Q1 incorporates an internal 10-bit counter for the PWM dimming function for each channel. The PWM width and frequency are programmable through the SPI registers. Alternatively, the device can also be configured to implement direct PWM dimming based on the duty cycle of the external PWM signal connected to PWM1 or PWM2 pins for channel-1 or channel-2, respectively. The internal PWM signals control the GATEx and PDRVx outputs, which control the external N-channel switching FETs and P-channel dimming FETs connected in series with LED strings.

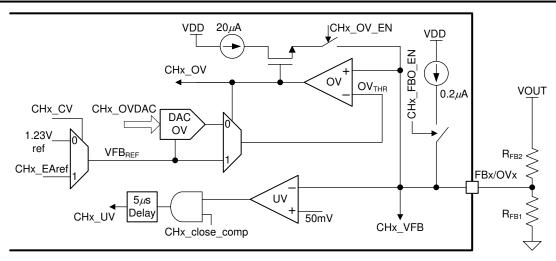

The TPS92682-Q1 can be configured in CV mode. In this mode, the device regulates the voltage connected to the FBx/OVx pins to an internal programmable reference voltage, set by the CHxIADJ register. In CV mode, the TPS92682-Q1 can be used as the first stage of a two-stage LED driver in an ECU (electronic control unit) of an exterior lighting application. The device can also be configured to operate in two-phase mode, where the switching frequencies of the two channels are phase-shifted by 180° and the channel-1 compensation loop, including COMP1 and the FB1/OV1, is shared between the two channels.

The TPS92682-Q1 incorporates an enhanced programmable fault feature. A selected number of faults, including ILIMIT (cycle-by-cycle current limit), OV (output Overvoltage), UV (output Undervoltage), and OC (LED Overcurrent), can be programmed to be latched faults, or automatically re-start the channel when the fault is cleared and after a programmed timer is expired. In addition, the TPS92682-Q1 includes open-pin faults for the FBx, ISNx, and RT pins. Other fault and diagnostic features include Thermal Shutdown (TSD), Thermal Warning (TW), LED Undercurrent (UC), and POR. Each channel includes an active-low fault pin ( $\overline{\text{FLT}}$ ) that is pulled low when a fault occurs. For each fault, there is an associated fault read-bit in the register map that can be read through SPI communication interface. For a complete list of the fault and diagnostic features, refer to the *Faults and Diagnostics* section.

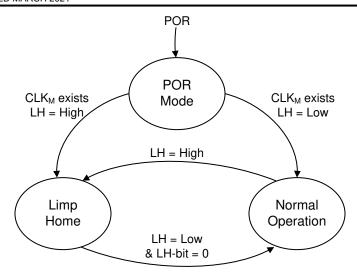

The TPS92682-Q1 includes a limp home (LH) function that is initiated when the LH pin is set high. In LH mode, the operation of the device is set by the LH registers. The LH registers are programmed upon initialization of the device. To exit the LH mode, the LH pin must be set low and the LH bit in the CFG1 register must be written to "0".

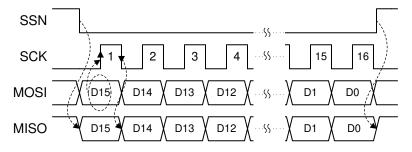

The TPS92682-Q1 device has numerous enhanced programmable features that can be accessed through the 4-wire SPI bus. The SPI bus consists of four signals: SSN, SCK, MOSI, and MISO. The SSN, SCK, and MOSI pins are TTL inputs into the device.

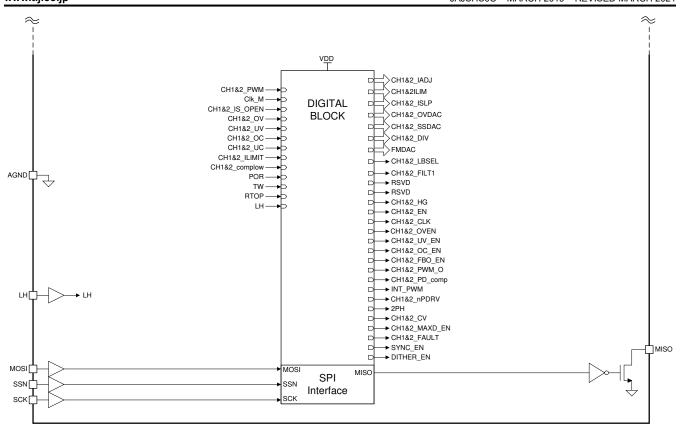

#### 7.2 Functional Block Diagram

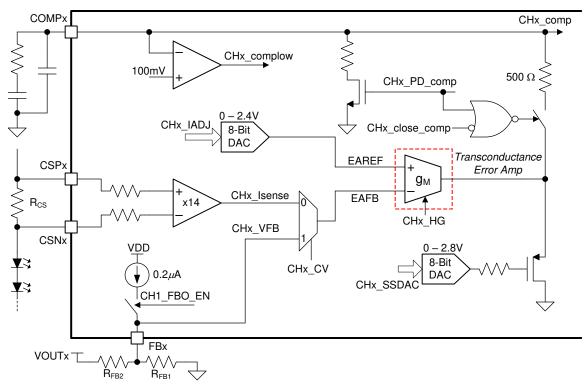

The block diagram below shows the associated blocks for channel-1. Channel-2 has a similar configuration.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

# 7.3 Feature Description

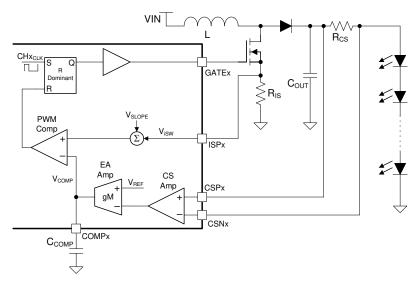

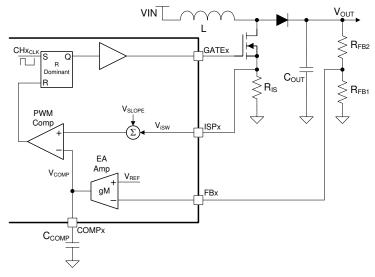

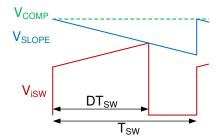

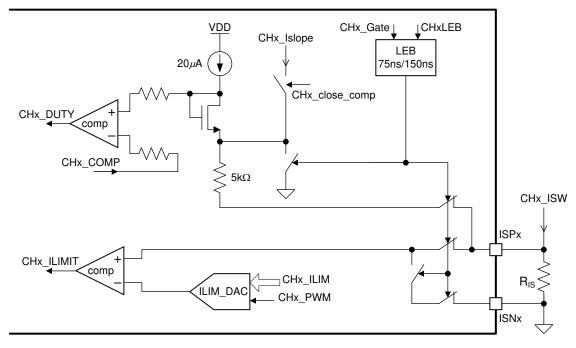

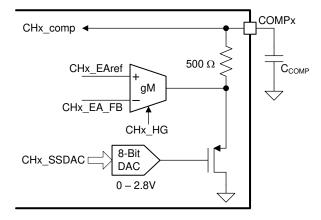

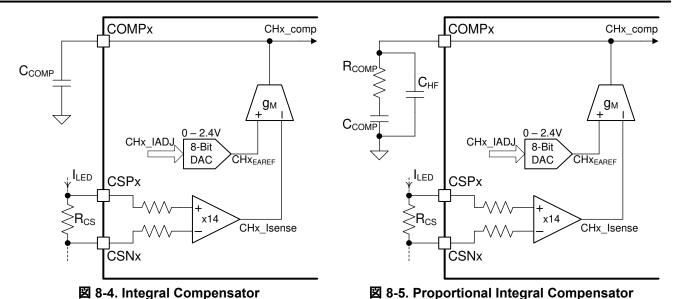

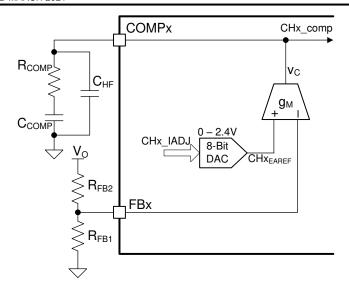

The TPS92682-Q1 device implements a fixed frequency Peak Current Mode (PCM) control. In PCM, the switching cycle starts with a rising edge of the clock. The switching cycle ends when the sensed switch current,  $V_{iSW}$  (added with  $V_{SLOPE}$ ), exceeds the compensator voltage,  $V_{COMP}$ . As shown in  $\boxtimes$  7-1 and  $\boxtimes$  7-2, a transconductance  $g_M$  error amplifier generates an error signal by comparing the feedback signal and the reference voltage,  $V_{REF}$ . The resulting error current generates the compensator voltage  $V_{COMP}$ , through a compensator impedance, connected to the COMPx pin.

For stability at high duty cycle and better noise immunity, a compensation ramp  $V_{SLOPE}$  is added to the sensed switch current  $V_{iSW}$ .

図 7-1. PCM Control in CC Mode

図 7-2. PCM Control in CV Mode

図 7-3. PCM Control and Ramp Compensation

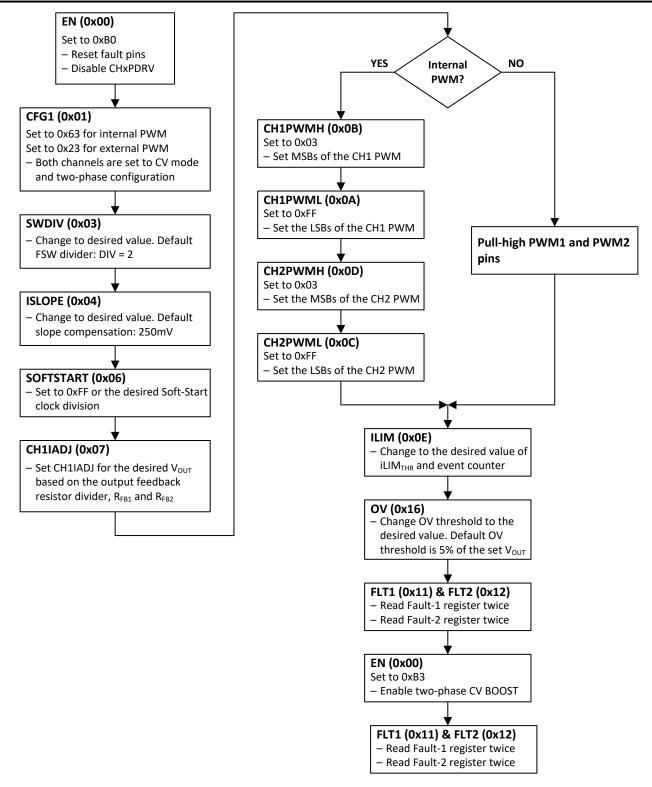

#### 7.3.1 Device Enable

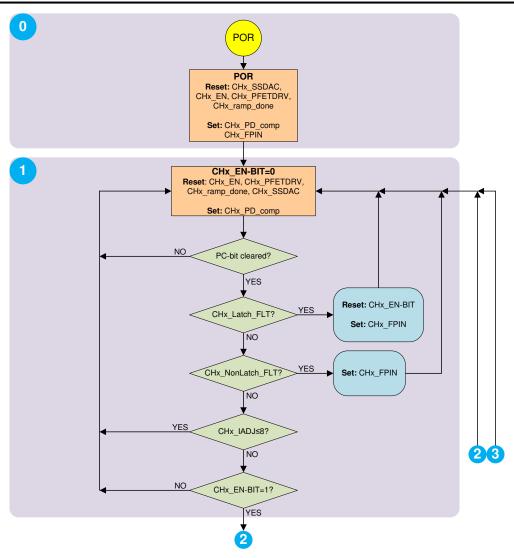

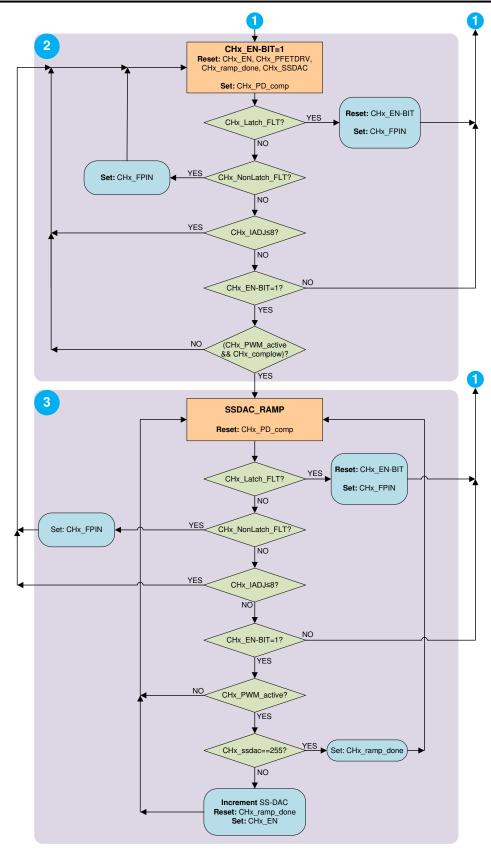

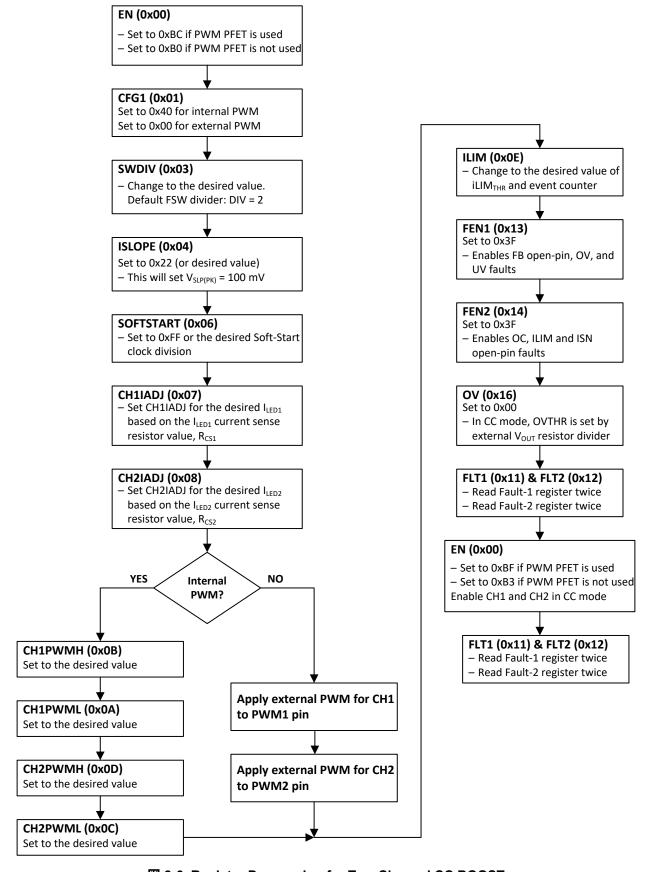

The TPS92682-Q1 can be enabled or disabled by the EN pin or the software enable bits. When EN pin is pulled low, the device enters shutdown state, where the quiescent current of the device is decreased to  $I_{\text{IN-SHDN}}$ . In shutdown state, the internal regulators are turned off and the registers are reset. When the voltage on the enable pin is increased above the voltage threshold of  $V_{\text{EN}}$ , the two channels can be enabled. In addition to the EN pin, there are two enable bits for the two channels of the TPS92682-Q1 as shown in  $\gtrsim$  7-2. In order for each channel to be turned on, the associated CHxEN bit must be set to "1" in *EN Register*.

In addition to the EN pin and the CHxEN bits, the PWMx signals (hardware or software) must be set high and the associated CHxIADJ must be set to a value greater than eight (refer to the *CH1IADJ Register*) in order for the associated channel to be turned on.

### 7.3.2 Internal Regulator and Undervoltage Lockout (UVLO)

The device incorporates 65-V input voltage rated linear regulators to generate the 7.5-V (typical) VCC bias supply, the 5-V (typical) VDD supply, and other internal reference voltages. The device monitors the VCC output to implement UVLO protection. Operation is enabled when VCC exceeds the 4.5-V (typ) threshold and is disabled when VCC drops below the 4.1-V (typical) threshold. The UVLO comparator provides a hysteresis to avoid chatter during transitions. The UVLO thresholds are internally fixed and cannot be adjusted. An internal current limit circuit is implemented to protect the device during VCC pin short-circuit conditions. The VCC supply powers the internal circuitry and the N-channel gate driver outputs, GATEx. Place a bypass capacitor in the range of  $2.2 \,\mu\text{F}$  to  $4.7 \,\mu\text{F}$  across the VCC output and GND to ensure proper operation. The regulator operates in dropout when input voltage VIN falls below 7.5 V. The VCC is a regulated output of the internal regulator and is not recommended to be driven with an external power supply.

The internal VDD regulator is used to generate supply voltage for various internal analog and digital circuits. The supply current is internally limited to protect the device from output overload and short-circuit conditions. Place a bypass capacitor in the range of  $2.2~\mu F$  to  $4.7~\mu F$  across the VDD output to GND to ensure proper operation. The POR circuit of the device is placed at the output of the VDD regulator. The POR rise and fall thresholds are provided in the *Electrical Characteristics*.

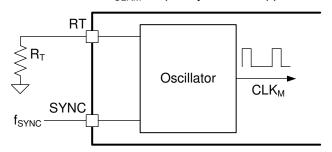

#### 7.3.3 Oscillator

The internal clock frequency of the TPS92682-Q1 device is programmable by a single external resistor, connected between the RT pin and the GND. The relationship between the resistor  $R_T$  and the internal main clock (CLK<sub>M</sub>) frequency is shown in  $\pm$  1 and  $\pm$  6-22.

$$f_{CLKM} = \frac{10^{12}}{12.5 \times R_{T}} \tag{1}$$

The relationship between the channel clock,  $CHx_{CLK}$  (or the channel switching frequency  $f_{SW}$ ), and  $f_{CLKM}$  is shown in the *SWDIV Register* section. TI recommends a switching frequency setting between 100 kHz to 700 kHz for best efficiency and for optimal performance over input and output voltage operating range. Operation at higher switching frequencies requires careful selection of N-channel MOSFET characteristics as well as detailed analysis of switching losses.

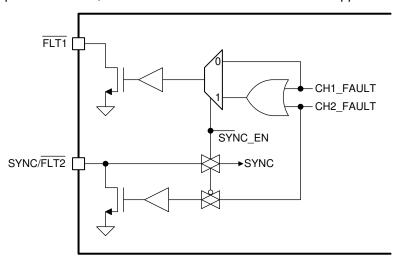

To use the synchronization functionality of the TPS92682-Q1, the SYNCEN bit shown in 表 7-3 must be set to "1", and a square wave signal with the desired  $f_{CLKM}$  frequency must be applied to the SYNC pin.

図 7-4. TPS92682 SYNC Function

# 7.3.4 Spread Spectrum Function

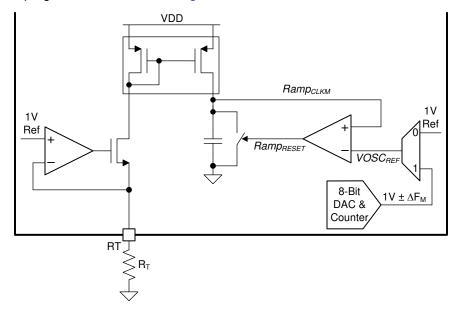

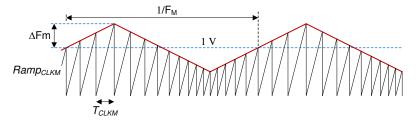

The main clock of the TPS92682-Q1,  $CLK_M$ , is generated using an internal ramp generator as shown in  $\boxtimes$  7-5. The internal ramp, RAMP<sub>CLKM</sub>, is compared with a reference voltage of VOSC<sub>REF</sub> to reset the ramp at the end of the clock period,  $T_{CLKM}$ . When the reference voltage  $VOSC_{REF}$  is constant (1 V), the main clock frequency is fixed. The frequency modulation of the main clock is achieved using an internal 8-bit digital counter DAC, and by modulating the reference voltage as shown in  $\boxtimes$  7-6. Both modulation frequency,  $F_M$ , and the modulation magnitude,  $\Delta F_M$ , are programmable in the *FM Register*.

図 7-5. Internal Ramp for CLK<sub>M</sub> Generation

図 7-6. Internal Ramp Waveform

To achieve maximum attenuation in average-EMI scan, set a modulation frequency of  $F_M$  ranging from 100 Hz to 1.2 kHz. A low modulating frequency has a small impact on the quasi-peak EMI scan. Set the modulation frequency to 10 KHz or higher to achieve attenuation for quasi-peak EMI measurements. A modulation

frequency higher than the receiver resolution bandwidth (RBW) of 9 kHz impacts only the quasi-peak EMI scan and has little impact on the average EMI measurement. The TPS92682-Q1 device simplifies EMI compliance by providing the means to tune the modulation frequency,  $F_M$ , and modulation magnitude,  $\Delta F_M$ , based on the measured EMI signature.

Equation 2 shows the relation between the channel switching frequency,  $f_{SW}$ , and the desired modulation frequency  $F_M$ .

$$F_{M} = \frac{DIV \times f_{SW}}{FM_{FREQ}} \tag{2}$$

In Equation 2, DIV is the division factor between  $CLK_M$  and the  $CHx_{CLK}$  provided in SWDIV Register, and  $FM_{FREQ}$  is the division factor given in the FM Register.

The output of the FM 8-bit digital counter always resets and starts from 1 V when a register write is performed to *FM Register*.

#### 7.3.5 Gate Driver

The TPS92682-Q1 contains an N-channel gate driver that switches the output GATEx between  $V_{CC}$  and GND. A peak source and sink current of 500 mA allows controlled slew-rate of the MOSFET gate and drain voltages, limiting the conducted and radiated EMI generated by switching.

The gate driver supply current,  $I_{CC(GATE)}$ , depends on the total gate drive charge (QG) of the MOSFET and the operating frequency of the converter,  $f_{SW}$ ,  $I_{CC(GATE)} = QG \times f_{SW}$ . Select a MOSFET with a low gate charge specification to limit the junction temperature rise and switch transition losses.

It is important to consider a MOSFET threshold voltage when operating in the dropout region (input voltage VIN is below the VCC regulation level). TI recommends a logic level device with a threshold voltage below 5 V when the device is required to operate at an input voltage less than 7 V.

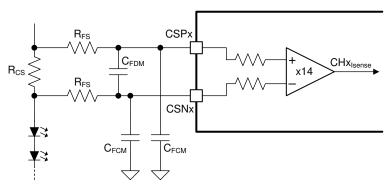

### 7.3.6 Rail-to-Rail Current Sense Amplifier

The internal rail-to-rail current sense amplifier measures the average LED current based on the differential voltage drop between the CSPx and CSNx inputs over a common mode range of 0 V to 65 V. The differential voltage, V<sub>(CSPx-CSNx)</sub>, is amplified by a voltage-gain factor of 14 and is connected to the negative input of the transconductance error amplifier. Accurate LED current feedback is achieved by limiting the cumulative input offset voltage (represented by the sum of the voltage-gain error, the intrinsic current sense offset voltage, and the transconductance error amplifier offset voltage) over the recommended common-mode voltage and temperature range.

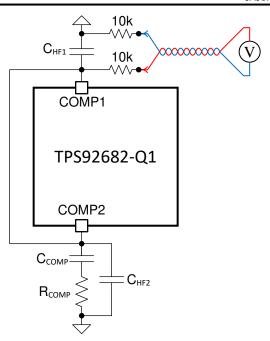

An optional common-mode ( $C_{FCM}$ ) or differential mode ( $C_{FDM}$ ) low-pass filter implementation, as shown in  $\boxtimes$  7-7, can be used to filter the effects of large output current ripple, and switching current spikes caused by diode reverse recovery. TI recommends a filter resistance in the range of 10  $\Omega$  to 100  $\Omega$  to limit the additional offset caused by amplifier bias current mismatch to achieve the best accuracy and line regulation.

図 7-7. Current Sense Amplifier

### 7.3.7 Transconductance Error Amplifier

As shown in  $\boxtimes$  7-8, the internal transconductance error amplifier generates an error signal proportional to the difference between the internal programmable 8-bit CHxIADJ-DAC (*CH1IADJ Register*) and the feedback signal. The feedback signal is the sensed current  $CHx_{Isense}$  in CC mode, or the sense output voltage,  $CHx_{VFB}$ , in CV mode. The gain  $g_M$  of the error amplifier is programmable through the  $CHx_M = 0$  or 1 are provided in the *Electrical Characteristics*. Based on the value of  $CHx_M = 0$  or 1 are provided in the *Electrical Characteristics*. Based on the value of  $CHx_M = 0$  or  $CHx_M = 0$  or

The output of the error amplifier is connected to an external compensation network to achieve closed-loop LED current (CC), or output voltage (CV) regulation. In most LED driver applications, a simple integral compensation circuit consisting of a capacitor connected from COMPx output to GND provides a stable response over a wide range of operating conditions. TI recommends a capacitor value between 10 nF and 100 nF as a good starting point. To achieve higher closed-loop bandwidth, a proportional-integral compensator, consisting of a series resistor and a capacitor network connected across the COMPx output and GND, is required. *Application and Implementation* includes a summarized detailed design procedure.

図 7-8. Feedback Connection to the Error Amplifier

### 7.3.8 Switch Current Sense

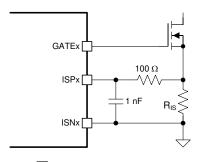

☑ 7-9 shows the simplified block diagram of the switch current sense circuitry. The ISPx input pin monitors the main MOSFET current to implement peak current mode control. The GATEx output duty cycle is derived by comparing the peak switch current, measured by the R<sub>IS</sub> resistor, to the internal CHx\_COMP voltage threshold. An internal slope signal, CHx\_ISLOPE, is added to the measured sense voltage to prevent sub-harmonic oscillations for duty cycles greater than 50%.

An internal leading-edge blanking (LEB) is applied to the switch current sense at the beginning of each switching cycle by shunting the ISPx input to the ISNx (GND connection of the R<sub>IS</sub>) for the duration of the LEB time. The LEB circuit prevents unwanted duty cycle termination due to MOSFET switching-current spike at the beginning of the new switching cycle. The LEB time can be set to 150 ns or 75 ns (typical) using the CHxLEB bit set in 表

7-5. For additional noise suppression, connect an external low-pass RC filter with resistor values ranging from 100  $\Omega$  to 500  $\Omega$  and a 1000-pF capacitor across R<sub>IS</sub>.

Cycle-by-cycle current limit is accomplished by a separate internal comparator. The current limit threshold is set based on the status of internal PWM signal and the CHxILIM setting. The current limit threshold is set to a value programmed in the CHxILIM in 表 7-17 when PWM signal is high. The current limit threshold is set to 700 mV (typical) when PWM signal is low. In CC mode, the transition between the two thresholds in conjunction with the slope compensation and the error amplifier circuit allows for higher inductor current immediately after the PWM transition, to improve LED current transient response in PWM dimming.

The device immediately terminates the GATEx and PDRVx outputs when the sensed voltage at the ISPx input exceeds the current limit threshold. For more detail on the cycle-by-cycle current limit, refer to the *Faults and Diagnostics* section.

図 7-9. Switch Current Sense and Current Limit

# 7.3.9 Slope Compensation

Switching converters with peak current mode control are subject to subharmonic oscillation for duty cycles greater than 50%. To avoid instability, the control scheme adds an artificial ramp to the sensed switch current (shown in  $\boxtimes$  7-9). The required slope of the artificial ramp depends on the input voltage,  $V_{IN}$ , output voltage,  $V_{O}$ , inductor L, and switch current sense resistor  $R_{IS}$ . The TPS92682-Q1 device provides a programmable slope compensation with seven levels of slope magnitude to simplify and enhance the performance of common switching converter topologies, such as boost, boost-to-battery, and SEPIC. The slope magnitude can be programmed through CHxISLP in the *ISLOPE Register*. The *Application and Implementation* section includes calculations for the choice of correct slope magnitude for a given application.

### 7.3.10 ILED Setting in CC Mode

In CC mode, as shown in  $\boxtimes$  7-8, the voltage across the LED current sense resistor,  $V_{(CSP-CSN)}$ , is regulated to the output of the programmable 8-bit CHxIADJ-DAC, scaled by the current sense amplifier voltage gain of 14. The LED current can be linearly adjusted by writing a different value to the CHxIADJ register. The 8-bit DAC output can be set in the range of 85 mV (CHxIADJ = 9) to 2.4 V (CHxIADJ = 255). The associated channel is turned off for CHxIADJ  $\leq$  8.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

### 7.3.11 Output Voltage Setting in CV Mode

In CV mode, as shown in  $\boxtimes$  7-8, the voltage at the FBx pin (output voltage divider) is regulated to the output of the programmable 8-bit CHxIADJ-DAC. The FBx voltage can be adjusted in the range of 85 mV (CHxIADJ = 9) to 2.4 V (CHxIADJ = 255). The associated channel is turned off for CHxIADJ  $\leq$  8.

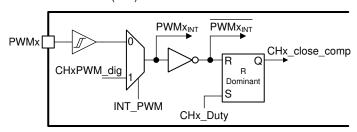

#### 7.3.12 PWM Dimming

As shown in  $\boxtimes$  7-10, the TPS92682-Q1 device incorporates both internal and external PWM dimming. To select between external or internal PWM dimming, the INTPWM bit in *CFG1 Register* must be set to "0" or "1", respectively. If internal PWM dimming operation is selected, the state of the PWMx pins do not have any effect on the operation of the device. For external PWM dimming, apply a square-wave signal to the PWMx pin with the rising and falling thresholds provided in the *Electrical Characteristics*. The LED current modulates based on the duty cycle of the external PWM signal,  $D_{PWM(EXT)}$ .

図 7-10. PWM Dimming Circuit

To use internal PWM dimming, the INTPWM bit in *CFG1 Register* must be set to "1". The TPS92682-Q1 device incorporates a 10-bit PWM counter for each channel. The duty cycle of the internal PWM can be set using a 10-bit value in the CHxPWML and CHxPWMH registers. Because CHxPWM is a 10-bit value, a PWM duty cycle update can require two SPI writes, one to the CHxPWMH and another to the CHxPWML register. To prevent transferring incoherent values, the contents of the two registers transfer to the CHxPWM counter only upon the write to the CHxPWML register. Therefore, for an update to the PWM duty cycle, it is recommended consecutively writing to CHxPWMH first and CHxPWML second. In addition, in order to avoid corrupting the progress of the current PWM duty cycle, the update from the CHxPWM registers to the CHxPWM counter occurs two PWM<sub>CLK</sub> before the end of each PWM period (at the count of 1022).

Due to synchronization of the external PWM with internal clock, when switching from external PWM to internal PWM, a glitch for the total of one PWM period can be observed in the output.

The clock to the 10-bit PWM counter is related to the main clock,  $CLK_M$ , by a division factor set by a 3-bit value in the *PWMDIV Register*. The relation between the  $PWM_{CLK}$  and PWM frequency with  $CLK_M$  frequency are shown in Equation 3 and Equation 4.

$$PWM_{CLK} = \frac{f_{CLKM}}{PWM_{DIV}}$$

(3)

$$PWM_{FREQ} = \frac{PWM_{CLK}}{1024} \tag{4}$$

For example, if the  $CLK_M$  frequency is set to  $f_{CLKM}$  = 800 kHz and  $PWM_{DIV}$  = 001 (division value of 2), the  $PWM_{FREQ} \approx 390$  Hz.

The phase between the internal PWM dimming for the two channels can be set to 180° if the PWMPH bit in *CFG1 Register* is set to 0. For PWMPH = 1, there is zero phase shift between the internal 10-bit PWM counters of the two channels.

The PWM signal controls the GATEx and PDRVx outputs. If  $PWM_{xINT}$  is set low, the associated channel is turned off, the COMPx pin is disconnected from the error amplifier, and the PDRVx output is set to  $V_{CSP}$  to maintain the charge on the compensation network and output capacitors. On the rising edge of the  $PWM_{xINT}$ , the

GATEx and PDRVx outputs are enabled to ramp the inductor current to the previous steady-state value. The COMPx pin connects to the error amplifier only when the switch current sense voltage  $V_{\rm ISPx}$  exceeds the COMPx voltage, CHx\_comp. This connection immediately forces the converter into steady-state operation with minimum LED current overshoot. When dimming is not required, connect the PWMx pins to the VDD pin. An internal pull-down resistor sets the PWM inputs to logic-low and disables the device when the pins are disconnected or left floating, and the INTPWM bit in *CFG1 Register* is set to the default value of "0".

#### 7.3.13 P-Channel FET Gate Driver Output

The PDRVx output is a function of the internal PWM signal and is capable of sinking and sourcing up to 50 mA of peak current to control a high-side series connected P-channel dimming FET. The PDRV switches between VCSP and (VCSP − 7 V) is based on the status of the PWM signal to completely turn off and turn on the external P-channel dimming FET. In CC mode, a series dimming FET is required to achieve high contrast ratio since it ensures fast rise and fall times of the LED current in response to the PWM input. Without any dimming FET, the rise and fall times are limited by the inductor slew rate and the closed-loop bandwidth of the system. In CC mode, leave the PDRVx pin unconnected if not used. In CV mode, the PDRVx together with CSPx and CSNx pins can be connected to GND to limit the shutdown current. The PDRVx can also be disabled by setting the CHxPDRVEN bit in ₹ 7-3 to zero.

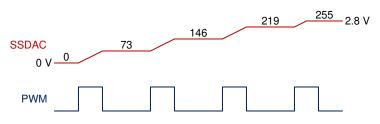

#### 7.3.14 Soft Start

The soft start feature helps the regulator gradually reach the steady-state operating point, thus reducing start-up stresses and current surges. The device clamps the COMPx pin to the output of the SSDAC plus the threshold voltage of a P-FET, until the LED current or the output voltage approaches the regulation threshold. The soft start is controlled with an 8-bit DAC which ramps from 0 V to 2.8 V during start-up of an associated channel. The rate of the soft-start ramp (or the ramp time) can be controlled by programming the clock of the internal digital ramp counter. The clock of the digital ramp counter is related to the associated channel clock (switching frequency  $f_{SW}$ ) by:

$$SS_{CLK} = \frac{CHx_{CLK}}{SSx_{DIV}}$$

(5)

The SSx<sub>DIV</sub> is a division factor provided in the *SOFTSTART Register*. For example, if the channel switching frequency is set to 400 kHz, the soft-start ramp time can be programmed between 1.3 ms and 64 ms. It is important to note that the ramp time is the time for the SSDAC output to ramp from 0 V to 2.8 V (digital ramp counter to count from 0 to 255), but the controller can reach the regulation point before the ramp is completed.

図 7-11. Soft-Start Circuit

When programming the soft-start ramp, It is essential to ensure that the soft-start ramp time is longer than the time required to charge the output capacitor.

Copyright © 2023 Texas Instruments Incorporated

Submit Document Feedback

To initiate the soft-start ramp, the PWM signal (internal or external) must be set high. If PWM dimming occurs during the soft-start period, the digital ramp counter holds the ramp value when PWM = LOW, and re-starts the ramp from the last ramp value when PWM = HIGH.  $\boxtimes$  7-12 shows an example of this feature.

図 7-12. Soft-start Period During PWM Dimming

# 7.3.15 Two-Phase Operation

The TPS92682-Q1 device can be programmed in two-phase mode by setting the 2PH bit to "1" in *CFG1 Register*. In two-phase mode, the CH1\_comp is internally connected to the CH2\_comp with 500  $\Omega$  (max) of resistance. In this case, the error amplifier of channel-2 is disabled and only the error amplifier of channel-1 connects to both COMP1 and COMP2 pins. TI recommends that external compensators be connected to both COMP1 and COMP2 pins, and that these two pins be shorted together externally.

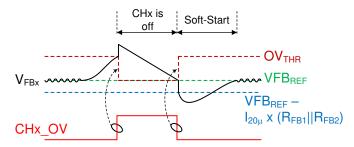

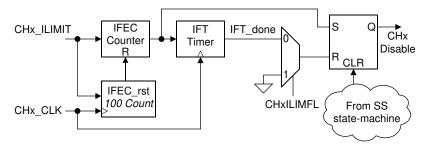

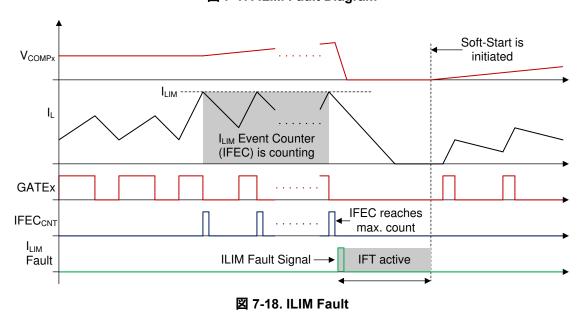

Two-phase mode uses only the channel-1 soft-start DAC and controls both phases. To generate the channel clocks, only the division factor for the channel-1, programmed in SWDIV Register, is used. The two channel clocks (switching frequency  $f_{SW}$ ) are the same and are 180° out-of-phase.