# 高性能RF設計に高速オペアンプを使用する(Part 1)

By Bruce Carter

Advanced Linear Products, OpAmp Applications

### 目次

| 高速オペアンプのメリット          | 2 |  |

|-----------------------|---|--|

| 高速オペアンプのデメリット         | 2 |  |

| 電圧帰還か、電流帰還か           | 2 |  |

| 従来型RFアンプを見直してみると      | 3 |  |

| 再びアンプのゲインについて         | 4 |  |

| 散乱パラメータ               | 4 |  |

| 入力VSWR S11と出力VSWR S22 | 4 |  |

| リターン・ロス               | 5 |  |

| 順方向伝達 S <sub>21</sub> | 5 |  |

| 逆方向伝達 S <sub>12</sub> | 5 |  |

| 位相リニアリティ              | 5 |  |

| 関連サイト                 |   |  |

|                       |   |  |

| 図1. 従来のRF段            | 3 |  |

|                       |   |  |

|                       |   |  |

| 図4. 出力ピーキング・キャパシタ     | 5 |  |

|                       |   |  |

|                       |   |  |

|                       |   |  |

| 表                     |   |  |

|                       |   |  |

| 表1. 散乱パラメータ           | 4 |  |

この資料は日本テキサス・インスツルメンツ(日本TI)が、お客様がTIおよび日本TI製品を理解するための一助としてお役に立てるよう、作成しております。製品に関する情報は随時更新されますので最新版の情報を取得するようお勧めします。

TIおよび日本TIは、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。また、TI及び日本TIは本ドキュメントに記載された情報により発生した問題や障害等につきましては如何なる責任も負いません。

RF設計にオペアンプを使う理由とは?ディスクリート・トランジスタを使う従来からの技術が何十年もの間、RF設計では問題なく実践されてきたというのに。「今までどおり」のもので満足しているRF設計者だったら、オペアンプを用いた新しい設計技術を導入するのにためらうでしょう。特に、高速オペアンプにかかるコストには驚くに違いありません。数セントで済むトランジスタの代わりに、数ドルもかかるような部品を使う理由とは何でしょうか?

これは非常に多くの商品について当てはまる疑問です。そしてほとんどどの商品の場合でも、答えは「やはり従来からの技術をそのまま使い続けることにする」というものになります。ただし、高性能RF機器で高速オペアンプを使うことにはいくつかの明確なメリットがあります。オペアンプの優れた性能を利用するために、すでにオペアンプに移行したアプリケーションも数多く存在します。RFのような高速アプリケーションも同様に移行していくと考えるのは妥当なことでしょう。

本論は二部構成になっています。Part 1ではオペアンプと散乱パラメータで形成されるRF段の実際のトポロジーに重点をおき、Part2ではRF設計の優れた点いくつかと、RF独自の仕様についてさらに詳しく述べることに重点をおきます。

## 高速オペアンプのメリット

高速オペアンプを使用することの主なメリットは、ディスクリート・トランジスタの実装よりも高度な柔軟性があることです。ディスクリート・トランジスタを使用した場合、トランジスタのバイアス点と動作点がその段のゲインおよびチューニングと影響を与え合ってしまいます。これに対して、オペアンプを使用した場合は、オペアンプの電源ピンに適切な電源を印加するだけで段のバイアスを達成できます。段のゲインはバイアスからは完全に独立しています。ゲインが段のチューニングに影響を与えることはなく、チューニングは受動部品によって達成されます。

オペアンプはまた、システムの動作温度範囲に対するトランジスタのパラメータのドリフトも減らします。

## 高速オペアンプのデメリット

オペアンプはRF設計にとって魅力的なものではありますが、その使用の妨げとなる障壁もいくつかあります。最初の障壁は、もちろんコストです。

RFの設計者はオペアンプの動作点を設定する方法を学ぶ必要がありますが、そのプロセスはトランジスタの段にバイアスをかけるよりもかなり容易です。

RFの設計者はRFの性能を何らかの方法で記述するのに慣れていますが、オペアンプのac性能はac性能の観点からのみ記述されます。RF設計者は、オペアンプのacパフォーマンスのパラメータをRFに合わせて解釈する方法を学ぶ必要があります。それが、本論の主目的のひとつです。

## 電圧帰還か、電流帰還か

オペアンプについて考慮するRF設計者は、次のようなジレンマにさらされます。「設計上、電圧帰還アンプを使った方がいいだろうか、それとも電流帰還アンプの方がいいか?」オペアンプのデータ・シートに記載されている帯域幅の仕様では、内部補償および/または寄生成分によりデバイスのユニティ・ゲイン帯域幅が3dB分減っているポイントについてしか言及していません – これでは、デバイスの実際の動作周波数範囲を決める役にはあまり立ちません。

内部補償を受けるために、電圧帰還アンプの帯域幅の大半は内部「主要極」補償キャパシタに占められており、その結果ゲイン/帯域幅に常に制約がある状態になっています。これに対して電流帰還アンプには主要極キャパシタがなく、したがってより高いゲインで、アンプの最大周波数により近いところまで動作可能です。言い換えれば、ゲイン/帯域幅の依存関係から脱却できるのです。

電圧帰還オペアンプと電流帰還オペアンプを比較すると、次のようになります。

• THS4001: 電圧帰還アンプ。

開ループ帯域幅270MHz (-3dB)。 ゲイン100 (20dB)で、約10MHzまでのみ使用 可能。

• THS3001: 電流帰還アンプ。

開ループ帯域幅420MHz (-3dB)。

ゲイン100 (20dB)で、約150MHzまで使用可能。

それでも、どちらを選択するかは設計者次第です。ユニティ・ゲインおよび低ゲインでは電流帰還アンプを使うメリットもあまりないかもしれませんが、高ゲインの場合は明らかに電流帰還アンプを選んだ方が得です。もしもトランジスタを使ってひとつの段でゲイン10(20dB)を得られたら、多くのRF設計者は大喜びするでしょう – 実際には難しいことですが。ところがオペアンプを使えば、ほとんど何の造作もなく可能になります。

RF設計者は、次のような電流帰還アンプの問題点についても知っておく必要があります。

- 電流帰還アンプでも、回路トポロジーは従来と変わらない。

- 電流帰還アンプのデータシートには帰還抵抗RFの推奨値が記載されている。これらの推奨値は真剣に考慮する必要がある。RGによってゲイン調整を行う必要がある。

- キャパシタを帰還ループから離しておくこと。

上記の制約を守った上で、レイアウトに通常と同じ注意を払い、高速RF回路のバイパス要件に合わせさえすれば、電流帰還アンプについて気を遣うべきことは他にありません。電圧帰還アンプでも電流帰還アンプでも、反転オペアンプ入力上のキャパシタンスには制限を課す必要があります。これは不安定性の主な原因になるからです。粗雑なPCBレイアウトの上にストレー・キャパシタンスを蓄積するのは非常に簡単なことです。このストレー・キャパシタンスを減らすために、Texas Instrumentsでは、多層基板上のオペアンプの反転入力の下にあるグラウンド・プレーンとパワー・プレーンに各々1つずつ穴を開けておくことを推奨します。

### 従来型 RF アンプを見直してみると

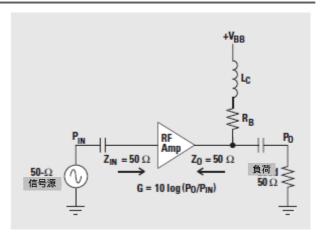

従来型RFアンプ(図1)では、ゲイン要素としてトランジスタ (もっと昔なら真空管)が使用されます。dcバイアス( $+V_{BB}$ ) は バイアス抵抗 $R_{B}$ を通って、負荷でゲイン要素に注入されます。RFはインダクタ $L_{C}$ にブロックされて電源にショートされず、dcはカプリング・キャパシタによって負荷からブロックされます。

入力インピーダンスと負荷は両方とも $50\,\Omega$  で、これによって段間マッチングが確実に行えます。

トランジスタに替わる回路の能動要素としてオペアンプを採用する際には、オペアンプを適応させるためにいくつかの点が変更されます。

オペアンプ自体は差動入力かつ開ループのデバイスであり、(レシーバのAGCループとは別の)閉ループ動作用に意図されたものです。各オペアンプの帰還ループは、個々のRF段内でローカルに閉じている必要があります。

これを達成する方法は2つあります - 「反転」と「非反転」です。この2つの言葉は、オペアンプ回路の出力が入力から反転されているかいないかを表します。RF設計の観点からは、こ

図1. 従来のRF段

れにはほとんど何の心配もありません。どのような実用目的であれ、どちらの構成でもうまくいき、結果も同じになります。使いやすさではおそらく非反転構成の方が上でしょう。

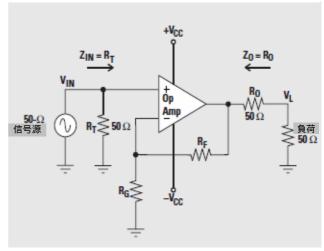

図2. 非反転RFオペアンプのゲイン段

図2は非反転RFアンプです。非反転入力の入力インピーダンスは高いため、入力は抵抗 $50\Omega$ で終端処理されます。ゲインはRFとRGの比率によって設定されます。ログ・ゲインについては次のようになります。

$$G = 20 \log \frac{1}{2} \left( 1 + \frac{R_F}{R_G} \right) dB$$

所要のゲインについては次のようになります。

$$1 + \frac{R_F}{R_G} = 2 \left( 10^{G/20} \right)$$

抵抗 $50\Omega$ を出力と直列に置くことによって、段の出力は $50\Omega$ に変換されます。これを負荷50Ωと結合すると、ゲインを分 圧器によって2(-6dB)で割ることになるため、ユニティ・ゲイン (0dB)のゲイン段はゲイン0.5つまり-6dBになるはずです。

RF設計者からすると、負電源を追加したために電源要件が 複雑になったとも言えます。その場合は、段を単電源動作用 に変更することも容易にできます。

## 再びアンプのゲインについて

オペアンプ設計者がオペアンプ段のゲインについて考える時 は、電圧ゲインの観点から考えます。しかしRF設計者の場 合は、次のように電力の観点からRF段のゲインを考えるこ とに慣れています。

絶対電力

$$(W) = \frac{V_{rms}^2}{50\Omega}$$

$$P_o(dBm) = 10 log \left( \frac{絶対電力}{0.001W} \right)$$

|                 | 散乱パラメータ | RFアンプの仕様    |

|-----------------|---------|-------------|

| S <sub>11</sub> | 入力反射    | 入力VSWR      |

| S <sub>22</sub> | 出力反射    | 出力VSWR      |

| S <sub>21</sub> | 順方向伝達   | アンプのゲインと帯域幅 |

| S <sub>12</sub> | 逆方向伝達   | 逆方向絶縁       |

表1. 散乱パラメータ

dB<sub>m</sub> = dBV +13 (50Ωシステムの場合)

# 散乱パラメータ

RF段の性能はしばしば、4つの「散乱」パラメータ(Sパラ メータ)によって特徴付けられます。散乱パラメータの定義 は表1にあります。(VSWR[電圧定在波比]というのは、入力 または出力の反射に関する用語です)

「散乱」という言葉には「損失」という意味がある程度含ま れていますが、これは4つのうち3つのパラメータに特に当て はまります。VSWRの散乱パラメータS11とS22には反射があ りますが、これは有用な信号を無効にする可能性がありま す。逆方向伝達S<sub>12</sub>は、負荷から出力を盗み取ります。散乱 パラメータの中では、順方向伝達S21のみが望ましいもので す。RF段の設計では、S21を最大限にして、S11、S22、S12を 最小限にすることが必要です。

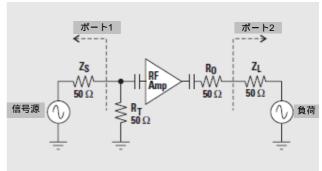

図3. 散乱パラメータのテスト回路

RFアンプ用に指定される小信号acパラメータは、Sパラメー タから派生します。これらの指定は周波数依存であり、ネッ トワーク・アナライザとSパラメータのテスト・セットで測定 されます。テスト回路を図3に示します。

## 入力 VSWR S<sub>11</sub> と出力 VSWR S<sub>22</sub>

VSWRとは、入力インピーダンスと出力インピーダンスが、 信号源インピーダンスと負荷インピーダンスにどの程度整合 しているかを知る基準となるものです。反射を回避するため には、それらのインピーダンスができるだけ整合している必 要があります。

VSWRは次のように定義されます。

VSWR =

$$\frac{Z_{110}}{Z_s}$$

と  $\frac{Z_s}{Z_{110}}$  のうち、>1である方

ここでZioは、アンプの入力インピーダンスまたは出力イン ピーダンスであり、Zsはテスト・システムの信号源インピー ダンスです。理想的なVSWRは1:1に相当しますが、動作周 波数範囲に対するRFアンプのVSWRは、たいていの場合 1.5:1より良くなることはありません。

入力VSWRを測定することは、図3のポート1 (S11)上の反射 電力と放射電力の比率を測定することです。完全に整合する 場合には、電力反射は起きません。

出力VSWRも、ポート2(S22)で同様に測定されます。 オペアンプの入力インピーダンスと出力インピーダンスは、 設計者の選択した外部部品によって決まります。このため、 オペアンプのデータ・シート上でVSWRの仕様を定めること はできません。

### リターン・ロス

リターン・ロスとVSWRの関係は次のようになります。

リターン・ロス =

$$20 \log \left( \frac{\text{VSWR} + 1}{\text{VSWR} - 1} \right) = 10 \log(S_{11})^2$$

または=10 log(S<sub>22</sub>)<sup>2</sup> 出力

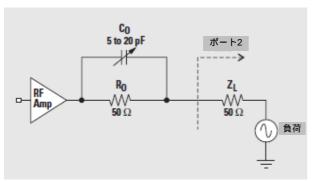

Roは、高い周波数ではZLと完全にはマッチしません。アンプの出力インピーダンスは、ループ・ゲインが低下するに従って増加します。これにより、出力VSWRが変化します。Roに並行して追加されたピーキング・キャパシタCOで、この影響を補償することができます(図4)。オペアンプの出力インピーダンスは明確に定義されているため、たいていは実験で正確な値が決まった後で固定値に置き換えることができます。

アンプの入力インピーダンスを減らすと高周波寄生成分の影響が無効になるため、使用可能な周波数の上限が拡張されます。

図4. 出力ピーキング・キャパシタ

#### 順方向伝達 S21

順方向伝達 $S_{21}$ は、関心の対象となる動作周波数範囲に対して指定されます。 $S_{21}$ はゲインの関数であり、ゲインは入力抵抗RFと帰還抵抗 $R_G$ によって決まるため、 $S_{21}$ の仕様がオペアンプのデータ・シートで指定されることはありません。非反転オペアンプ段の順方向伝達は次のようになります。

$$S_{21} = A_L = \frac{V_L}{V_{IN}} = \frac{1}{2} \left( 1 + \frac{R_F}{R_G} \right)$$

反転オペアンプ段の順方向伝達は次のようになります。

$$S_{21} = A_L = -\frac{V_L}{V_{IN}} = -\frac{1}{2} \left( \frac{R_F}{R_G} \right)$$

オペアンプのデータ・シートには開ループのゲインと位相が記載されていますが、閉ループのゲインと位相については設計者が自分で調べる必要があります。幸い、これは難しいことではありません。データ・シートには開ループ帯域幅の優れたグラフが記載されていることが多く、時には位相まで記載されていることもあります。ループを閉じると、所要のゲインでグラフに交わる直線が現れ、極限に向かって曲線化していきます。開ループ帯域幅のプロットは絶対最大値として使う必要があります。設計者が極限に近づこうとするほど、広範囲の補償と複雑なPCBレイアウト技法が必要になります。

## 逆方向伝達 S<sub>12</sub>

オペアンプのトポロジー、特に電流帰還アンプでは、入力が両方とも低いインピーダンスに接続されていることが前提となっています。オペアンプのRF回路の逆方向絶縁が優れているのはこのためです。

逆方向絶縁は、非反転電流帰還アンプの構成での方が多少良くなっています。出力信号が信号源に到達するためには、非 反転入力と反転入力を接続する回路も通らなければならないからです。

## 位相リニアリティ

設計者はしばしば、RF回路の位相レスポンスに関心を持ちます。映像設計の場合はそれ自体が特殊なRF設計であるため、特にそうなります。電圧帰還アンプよりも、電流帰還アンプの方が良い位相リニアリティを持つ傾向にあります。

電圧帰還 THS4001: 微分位相= 0.15°

電流帰還 THS3001: 微分位相= 0.02°

本論のPart2と、今後Applications Journal上で発表される 結論にご期待ください。

#### 関連サイト

www.ti.com/sc/device/THS3001

www.ti.com/sc/device/THS4001

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、 条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

Copyright © 2007, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点 を遵守して下さい。

#### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装) 又は製品単品で取り扱いを行う場合は、接地された導 電性のテーブル上で(導電性マットにアースをとったも の等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる 全ての装置類は、静電気の帯電を防止する措置を施す こと。

- 前記のリストストラップ・導電性手袋・テーブル表面 及び実装装置類の接地等の静電気帯電防止措置は、常 に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に 従い基板実装すること。

#### 4. 機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、 衝撃を与えないこと。

#### 5. 熱衝撃

● はんだ付け時は、最低限260°C以上の高温状態に、10 秒以上さらさないこと。(個別推奨条件がある時はそれ に従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。 (不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます) 及びTexas Instruments Incorporated(TIJの親会社、以下TIJおよびTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIの標準契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、且つその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

Copyright © 2007, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

## 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点 を遵守して下さい。

#### 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装) 又は製品単品で取り扱いを行う場合は、接地された導 電性のテーブル上で(導電性マットにアースをとったも の等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すった。

- 前記のリストストラップ・導電性手袋・テーブル表面 及び実装装置類の接地等の静電気帯電防止措置は、常 に管理されその機能が確認されていること。

#### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送 及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に 従い基板実装すること。

#### 4. 機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、 衝撃を与えないこと。

#### 5. 熱衝撃

● はんだ付け時は、最低限260°C以上の高温状態に、10 秒以上さらさないこと。(個別推奨条件がある時はそれ に従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。 (不純物含有率が一定以下に保証された無洗浄タイプの フラックスは除く。)

以上