# 2 段目のフィルタを使用して電圧リップルを低減

#### Rich Nowakowski

**Product Marketing Engineer**

#### Sarmad Abedin

Power Design Services Engineer

#### 概要

ポイント・ツー・ポイントのシリアル通信またはアナログ・フロン ト・エンド (AFE) を内蔵した高度なプロセッサやシステム・オ ン・チップ (SoC) では、シグナル・インテグリティを維持し、性 能を向上させるために、出力電圧リップルが低い電源が必要 です。プロセッサのポイント・オブ・ロード (POL) 電源の出力電 圧リップル要件は 2mV 未満になる可能性があります。これ は、標準的な設計のリップルの約 1/10 であり、同期整流降 圧コンバータの設計に大きな制約が課されます。プロセッサ の出力電流要件はリニア・ポスト・レギュレータの能力を上回 るため、2段目のフィルタを採用し、高いスイッチング周波数 と追加の出力容量により POL のリップルが大幅に低減され ます。同期整流降圧コンバータは、複数の異なる制御アーキ テクチャで利用可能であり、それぞれが低リップル電圧向け に設計する際の安定性を確保するための独自の方法を持っ ています。この記事では、外部補償電圧モード、コンスタント・ オン・タイム (COT: 一定のオン時間)、選択可能な補償電流モ ードという3種類の制御アーキテクチャを比較します。また、 同じ電気的仕様を使用して 1mV の出力電圧リップルを実現 し、テスト・データを掲載しているほか、出力電圧リップル、ソリ ューション・サイズ、負荷過渡、効率を比較しています。

# アプリケーションの選択と境界設定

同様の動作条件下で各制御モードの性能を実証するために、3 つの異なる電源を設計および構築しました。各設計の入力電圧は 12V、出力電圧は 1V、各デバイスの出力電流は15Aです。これらの要件は、低出力電圧リップルを必要とする、高感度なアナログ回路を内蔵した高性能 SoC に電力を供給する場合に一般的です。

フィルタの設計と性能の期待値を制限するため、許容されるリップル電圧は出力電圧の ±0.15%、つまり ±1.5mV (3mVpp)です。この比較では、15A D-CAP3™ 降圧コンバータ (TPS548A28)、20A 内部補償型の高度電流モード (ACM) 降圧コンバータ (TPS543B22)、15A 電圧モード降圧コンバータ (TPS56121) という3つのテキサス・インスツルメンツの DC/DC コンバータを取り上げています。出力電圧、出力電流、動作周波数は、コンバータの能力の範囲内で互いに可能な限り近い値を選択し、同様の2段目のフィルタ部品をサポートするようにしています。

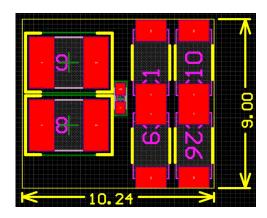

## 2段目のフィルタの設計

等価直列抵抗 (ESR) の小さいセラミック出力コンデンサを使用したとしても、降圧コンバータのインダクタとコンデンサ (LC) による出力フィルタを使用して出力電圧リップルを低くすることは、現実的ではありません。設計者は、出力リップルを 5mV 未満にするには、2 段目の LC フィルタを使用する必要があると思われます。2 段目のフィルタの設計やリップル測定手法の詳細については、「リソース」セクションを参照してください。2 段目のフィルタのインダクタ値は、式1を使用して L2を解くことで計算できます。インダクタ L2 は 2 段目のインダクタ、C1 は降圧コンバータの 1 段目の出力コンデンサ、C2 は 2 段目のコンデンサ・ネットワークです。3 つの設計すべてで、同じ 2 段目のフィルタが使用され (表1を参照)、92mm²の基板面積を占有しています (図1を参照)。

Switching Frequency =  $1/(2\pi^*\sqrt{L2^*Cs})$ , where Cs = 1/(1)  $\left(\frac{1}{C1} + \frac{1}{C2}\right)$

| 部品番号      | 制御アーキテ<br>クチャ | スイッチング<br>周波数 | 2 段目のイン<br>ダクタンス | 2 段目の容量             |

|-----------|---------------|---------------|------------------|---------------------|

| TPS548A28 | D-CAP3        | 800kHz        | 2 x 0.68µH       | 4x 100μF +<br>0.1μF |

| TPS543B22 | ACM           | 1000kHz       | 2 x 0.68µH       | 4x 100μF +<br>0.1μF |

| TPS56121  | 電圧モード         | 500kHz        | 2 x 0.68µH       | 4x 100μF +<br>0.1μF |

表1.コンバータ制御アーキテクチャと2段目のフィルタ。

図1.92mm<sup>2</sup>の2段目フィルタの基板面積。

2 段目のインダクタ値 (L2) を選択し、部品を組み立てたら、次のステップは、安定性を確保するために 2 段目のインダクタンスと容量を追加して DC/DC コンバータの制御ループを再補償することです。各制御アーキテクチャには、必要に応じて2 段目のフィルタを追加した後に制御ループを再補償する独自の手法があることに言及することが重要です。各制御アーキテクチャの出力電圧リップル、効率ペナルティ、安定性を評価し、結果をまとめました。

#### 電圧モード制御アーキテクチャ

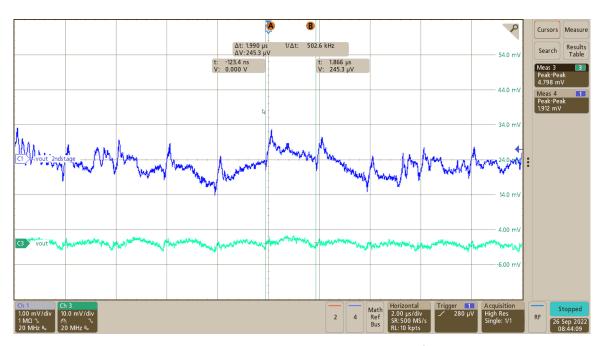

電圧モード制御アーキテクチャによるパルス幅変調 (PWM) は、出力電圧と基準電圧からの電圧誤差信号を、一定ののこぎり (ランプ) 波形と比較することで実現されます。ランプは、発振器からのクロック信号によって開始されます。TPS56121 は、2 極電力段を対象とする外部補償型のタイプ 3 補償を採用しており、2 段目のフィルタを追加した後にコンバータを再補償できます。2 段目のフィルタを追加した後に外部抵抗とコンデンサの値を調整することで、安定性が確保されます。フィルタを追加しない場合の出力電圧のピーク・ツー・ピーク・リップルは 4.8mV です。追加のフィルタを適用すると、出力電圧リップルは 1.9mV になります (図 2 を参照)。この場合、TPS56121 の設計では、安定性を確保するためのループ補償の調整は必要ありません。図 3 は、10A の負荷ステップで

の負荷過渡波形を示しており、2段目のフィルタを実装した後

の出力電圧波形には不安定性の兆候はありません。

図2. 追加の2段目のフィルタを使用した場合と使用しない場合のTPS56121の出力電圧リップル。

図3. 電圧モード制御を使用した TPS56121 の過渡応答。

#### D-CAP3 制御アーキテクチャ

D-CAP3 はワンショット・タイマを使用して、入力電圧と出力電圧に比例するオン時間パルスを生成します。立ち下がりフィードバック電圧が基準電圧と等しくなると、新しい PWM オンパルスが生成されます。ランプは出力インダクタによってエミュレートされます。内部リップル注入回路からの信号は、オフセ

ット電圧が除去された状態でコンパレータに直接供給されるため、コンデンサの ESR からの出力電圧リップルが低減されます。D-CAP3 や他のコンスタント・オンタイム・コンバータの利点の 1 つは、ループ補償回路を追加する必要がないことです。ただし、デバイスがこの機能をサポートしている場合、制御ループは、可変ランプによって調整される可能性があり、出力電圧帰還抵抗分割回路ネットワークにフィードフォワード容

量を追加する可能性があります。フィルタを追加しない場合の **TPS548A28** の出力電圧のピーク・ツー・ピーク・リップルは 7.6mV です。追加のフィルタを適用した場合、出力電圧リップルは 2.3mV になります (**図 4** を参照)。この場合、

TPS548A28 の設計では、安定性を確保するために調整する

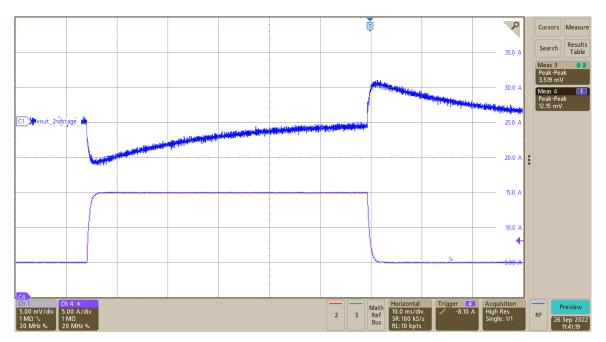

必要はありません。図 5 に、従来のコンバータと同じ 10A 負荷ステップでの負荷過渡波形を示します。2 段目のフィルタを実装した後の出力電圧波形には、不安定性の兆候はありません。

図4. 追加の2段目のフィルタを使用した場合と使用しない場合の TPS548A28 の出力電圧リップル。

図5. D-CAP3 制御を使用した TPS548A28 の過渡応答。

## 高度な電流モード (ACM) 制御アーキテクチャ

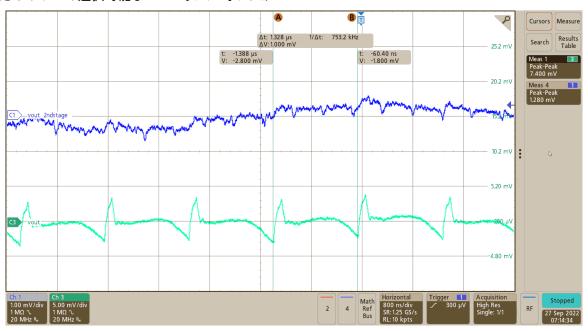

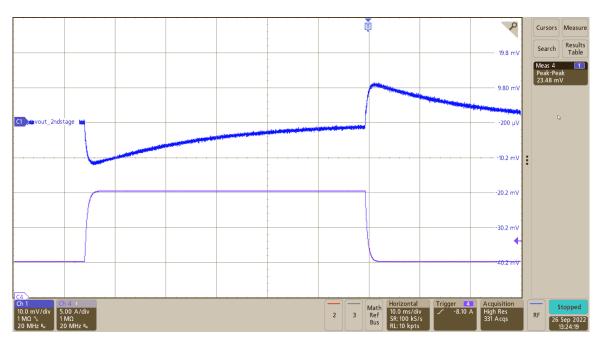

内部補償型 ACM は、リップル・ベースのピーク電流モード制御方式で、内部で生成されたランプを使用してインダクタ電流を表します。この制御モードでは、D-CAP3 などの非線形制御モードの高速過渡応答と、電圧モード制御のような他の外部補償型固定周波数制御アーキテクチャの幅広いコンデンサ安定性との間のバランスを提供します。ACM は、抵抗とコンデンサのネットワークではなく、単一の抵抗でループを補償できる新しい制御アーキテクチャです。TPS543B22 には、2段目のフィルタが実装されているときに制御ループの性能を最適化するための3つの選択可能な PWM ランプ・オプショ

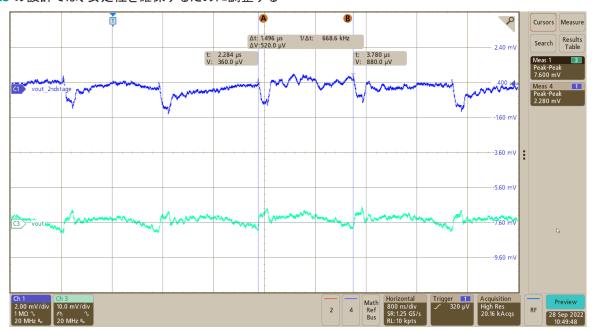

ンがあります。興味深いのは、この評価基板には、回路基板上にコンデンサとインダクタのハンダ・パッドがあり、2 段目のフィルタ部品を搭載するのに便利であることです。フィルタを追加しない場合の TPS543B22 の出力電圧のピーク・ツー・ピーク・リップルは 7.4mV です。追加のフィルタを適用した場合、出力電圧リップルは 1.3mV になります (図 6 を参照)。 TPS543B22 の設計では、安定性を確保するためにランプを調整する必要はありません。図 7 に、従来のコンバータと同じ 10A 負荷ステップでの負荷過渡波形を示します。2 段目のフィルタを実装した後の出力電圧波形には、不安定性の兆候はありません。

図6. 追加の2段目のフィルタを使用した場合と使用しない場合のTPS543B22の出力電圧リップル。

図7. ACM 制御を使用した TPS543B22 の過渡応答。

### 効率の低下

各 DC/DC コンバータの全負荷効率を、追加の 2 段目のフィルタを使用する場合と使用しない場合で測定し、電力損失を比較しました。表 2 に、結果を示します。2 段目のフィルタによる電力損失と効率の低下は無視できます。各 DC/DC コンバータには独自のパワー MOSFET があり、効率の結論が不正確になるため、不足と電力損失の差を測定しました。効率の低下と 92mm² の追加で必要となる基板面積が、出力電圧リップルの改善に見合うかどうかは、設計者が判断します。

従来、設計者は追加の低ドロップアウト (LDO) レギュレータを使用して、DC/DC コンバータの出力電圧をポストレギュレーションし、低出力電圧リップルを実現してきました。設計者が、2 段目のフィルタの代わりに LDO を使用したい場合、4A のTPS7A54 を並列接続することで最大 8A を供給できます。たとえば、LDO の電圧降下が 175mV の場合、2 つの LDO は8A で 1.4W を消費しますが、2 段目のフィルタでは 0.02Wです。LDO の出力電圧リップル・ノイズは 4µV と低くなりますが、

2 段目のフィルタが SoC と AFE に許容可能な低出力電圧リップルを提供する場合、設計の小型化、電力損失の低減、部品コストの削減という利点があります。

| P/N       | lout (A) | フィルタ  | 効率     | 電力損失 (W) |

|-----------|----------|-------|--------|----------|

| TPS543B22 | 15       | 1 次   | 86.43% | 2.358    |

|           |          | 1次+2次 | 86.33% | 2.378    |

|           |          | 相違点   | -0.1%  | -0.02    |

| TPS548A28 | 15       | 1 次   | 83.98% | 2.829    |

|           |          | 1次+2次 | 83.87% | 2.850    |

|           |          | 相違点   | -0.11% | -0.021   |

| TPS56121  | 15       | 1 次   | 89.19% | 1.834    |

|           |          | 1次+2次 | 89.34% | 1.806    |

|           |          | 相違点   | -0.15% | -0.028   |

表 2. 効率と電力損失の比較。

#### まとめ

2 段目のフィルタは、簡単で小型、効率的で低コストのソリューションであり、大電流負荷に対して低出力電圧リップルになるように設計され、それを実現します。あらゆる設計状況に対応できる完璧な制御モードは存在しませんが、多くの降圧コンバータ制御アーキテクチャでは 2 段目のフィルタを実装できます。ネットワーク・インターフェイス・カードの SoC またはAFE を使用するリモート無線ユニットで設計する場合、2 段目のフィルタは標準的な降圧コンバータよりもはるかに低いリップルを実現します。表 3 に、各デバイスに関連するリップル、効率、サイズのトレードオフをまとめたものを示します。

| デバイス          | 電流容量<br>(A) | 制御アー<br>キテクチャ | リップル電<br>圧 (mV) | フィルタ・サ<br>イズ      | 電力損失<br>ペナルティ<br>(W) |

|---------------|-------------|---------------|-----------------|-------------------|----------------------|

| TPS543B2<br>2 | 20          | ACM           | 1.3             | 92mm <sup>2</sup> | 0.020                |

| TPS548A2<br>8 | 15          | D-CAP3        | 2.3             | 92mm <sup>2</sup> | 0.021                |

| TPS56121      | 15          | 電圧モード         | 1.9             | 92mm <sup>2</sup> | 0.028                |

表3. リップル、サイズ、効率のトレードオフ。

#### 関連資料

- テキサス・インスツルメンツ: Power Tips: 2 段 LC フィルタの設計

- 2. テキサス・インスツルメンツ: スイッチング・レギュレータの 出力ノイズの低減

- 3. テキサス・インスツルメンツ: 制御モード・クイック・リファレンス・ガイド 降圧、非絶縁型 DC/DC

#### 関連 Web サイト

- TPS548A28 リモート・センス機能と 3V LDO 搭載、2.7V ~16V、15A 同期整流降圧コンバータ

- TPS543B22 4V~18V 入力、高度な電流モード、20A 同期整流 SWIFT™ 降圧コンバータ

- TPS56121 4.5V~14V、15A 同期整流 SWIFT™ 降圧 コンバータ

- TPS7A54 4A、低い VIN (1.1V)、低ノイズ、高精度、超低 ドロップアウト電圧レギュレータ

重要なお知らせ:ここに記載されているテキサス・インスツルメンツ社および子会社の製品およびサービスの購入には、TI の販売に関する標準の使用許諾契約への同意が必要です。お客様には、ご注文の前に、TI 製品とサービスに関する完全な最新情報のご入手をお勧め致します。TI は、アプリケーションに対する援助、お客様のアプリケーションまたは製品の設計、ソフトウェアのパフォーマンス、または特許の侵害に対して一切責任を負いません。ここに記載されている他の会社の製品またはサービスに関する情報は、TI による同意、保証、または承認を意図するものではありません。

#### 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated