## TMS320x28xx, 28xxx DSP シリアル通信インターフェイス(SCI)

# リファレンス・ガイド

2008 DSP Products

# 目次

| 1 | 概要.   |                                        | 1-1  |

|---|-------|----------------------------------------|------|

|   | シリフ   | アル通信インターフェイス(SCI)について                  |      |

|   | 1.1   | エンハンスド SCI モジュールの概要                    | 1-2  |

|   | 1.2   | アーキテクチャ                                | 1-7  |

|   |       | 1.2.1 SCI モジュール信号一覧                    | 1-7  |

|   |       | 1.2.2 マルチプロセッサおよび非同期通信モード              | 1-8  |

|   |       | 1.2.3 SCI プログラマブル・データ・フォーマット           | 1-8  |

|   |       | 1.2.4 SCI マルチプロセッサ通信                   | 1-9  |

|   |       | 1.2.5 アイドル・ライン・マルチプロセッサ・モード            | 1-11 |

|   |       | 1.2.6 アドレス・ビット・マルチプロセッサ・モード            | 1-13 |

|   |       | 1.2.7 SCI 通信フォーマット                     | 1-15 |

|   |       | 1.2.8 SCI ポート割り込み                      | 1-18 |

|   |       | 1.2.9 SCI ボー・レート計算                     | 1-19 |

|   |       | 1.2.10 SCI 拡張機能                        | 1-19 |

| 2 | SCI [ | レジスタ                                   | 2-1  |

|   | シリフ   | アル通信インターフェイス(SCI)について                  |      |

|   | 2.1   | SCI モジュールのレジスター覧                       | 2-2  |

|   | 2.2   | SCI 通信コントロール・レジスタ(SCICCR)              | 2-3  |

|   | 2.3   | SCI コントロール・レジスタ 1(SCICTL1)             | 2-5  |

|   | 2.4   | SCI ボー・セレクト・レジスタ(SCIHBAUD、SCILBAUD)    | 2-7  |

|   | 2.5   | SCI コントロール・レジスタ 2(SCICTL2)             | 2-8  |

|   | 2.6   | SCI レシーバ・ステータス・レジスタ(SCIRXST)           | 2-9  |

|   | 2.7   | レシーバ・データ・バッファ・レジスタ(SCIRXEMU、SCIRXBUF)  | 2-11 |

|   |       | 2.7.1 エミュレーション・データ・バッファ (SCIRXEMU)     | 2-11 |

|   |       | 2.7.2 レシーバ・データ・バッファ (SCIRXBUF)         | 2-12 |

|   | 2.8   | SCI 送信データ・バッファ・レジスタ(SCITXBUF)          | 2-13 |

|   | 2.9   | SCI FIFO レジスタ(SCIFFTX、SCIFFRX、SCIFFCT) |      |

|   | 2.10  | 優先順位コントロール・レジスタ(SCIPRI)                | 2-17 |

|   |       |                                        |      |

## 図目次

| 4 d    |                                               | 4.0  |

|--------|-----------------------------------------------|------|

| 図 1-1  | SCI CPU インターフェイス                              |      |

| 図 1-2  | シリアル通信インターフェイス(SCI)モジュールのブロック図ク図              | 1-4  |

| 図 1-3  | 一般的な SCI データ・フレーム・フォーマット                      | 1-8  |

| 図 1-4  | アイドル・ライン・マルチプロセッサ通信フォーマット                     | 1-11 |

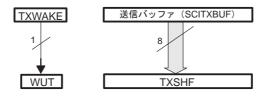

| 図 1-5  | ダブル・バッファリングされた WUT と TXSHF                    |      |

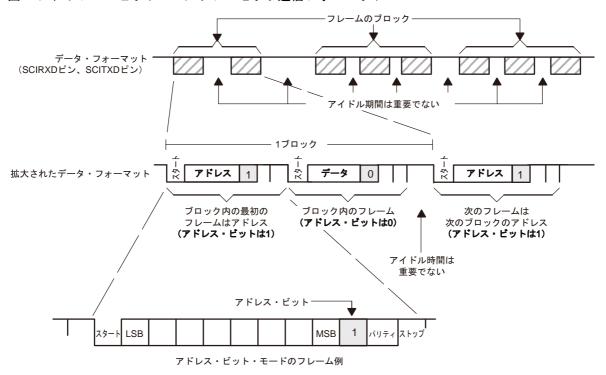

| 図 1-6  | アドレス・ビット・マルチプロセッサ通信フォーマット                     |      |

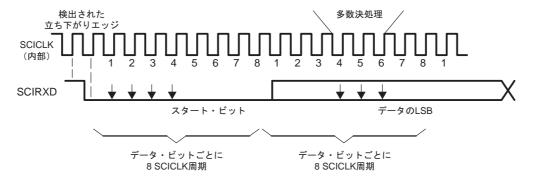

| 図 1-7  | SCI 非同期通信フォーマット                               | 1-15 |

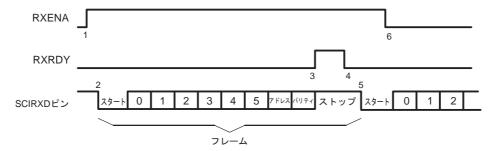

| 図 1-8  | 通信モードにおける SCI RX 信号                           | 1-16 |

| 図 1-9  | 通信モードにおける SCI TX 信号                           |      |

| 図 1-10 | SCI FIFO 割り込みフラグとイネーブル・ロジック                   | 1-21 |

| 図 2-1  | SCI 通信コントロール・レジスタ(SCICCR) – アドレス 7050h        | 2-3  |

| 図 2-2  | SCI コントロール・レジスタ 1(SCICTL1) – アドレス 7051h       | 2-5  |

| 図 2-3  | ボー・セレクト MSbyte レジスタ(SCIHBAUD) – アドレス 7052h    | 2-7  |

| 図 2-4  | ボー・セレクト LSbyte レジスタ(SCILBAUD) – アドレス 7053h    | 2-7  |

| 図 2-5  | SCI コントロール・レジスタ 2(SCICTL2) – アドレス 7054h       | 2-8  |

| 図 2-6  | SCI コントロール・レジスタ 2(SCICTL2) – アドレス 7054h       | 2-9  |

| 図 2-7  | SCIRXST レジスタのビットの関係 – アドレス 7055h              | 2-10 |

| 図 2-8  | エミュレーション・データ・バッファ・レジスタ(SCIRXEMU) – アドレス 7056h | 2-11 |

| 図 2-9  | SCI 受信データ・バッファ・レジスタ(SCIRXBUF) – アドレス 7057h    | 2-12 |

| 図 2-10 | 送信データ・バッファ・レジスタ(SCITXBUF) – アドレス 7059h        | 2-13 |

| 図 2-11 | SCI FIFO 送信(SCIFFTX)レジスタ – アドレス 705Ah         | 2-13 |

| 図 2-12 | SCI FIFO 受信(SCIFFRX)レジスタ – アドレス 705Bh         | 2-15 |

| 図 2-13 | SCI FIFO コントロール(SCIFFCT)レジスタ – アドレス 705Ch     | 2-16 |

| 図 2-14 | SCI 優先順位コントロール・レジスタ(SCIPRI) – アドレス 705Fh      | 2-17 |

|        |                                               |      |

## 表目次

| 表 1-1  | SCI-A レジスタ                           | 1-5  |

|--------|--------------------------------------|------|

| 表 1-2  | SCI-B レジスタ                           | 1-6  |

| 表 1-3  | SCICCR を使用したデータ・フォーマットのプログラミング       | 1-9  |

| 表 1-4  | 一般的な SCI ビット・レートの非同期ボー・レジスタ値         |      |

| 表 1-5  | SCI 割り込みフラグ                          |      |

| 表 2-1  | SCIA レジスタ                            | 2-2  |

| 表 2-2  | SCIB レジスタ                            | 2-2  |

| 表 2-3  | SCI 通信コントロール・レジスタ(SCICCR)のビットの説明     | 2-3  |

| 表 2-4  | SCI コントロール・レジスタ 1(SCICTL1)のビットの説明    |      |

| 表 2-5  | ボー・セレクト・レジスタのビットの説明                  |      |

| 表 2-6  | SCI コントロール・レジスタ 2(SCICTL2)のビットの説明    | 2-8  |

| 表 2-7  | SCI レシーバ・ステータス・レジスタ(SCIRXST)のビットの説明  | 2-9  |

| 表 2-8  | SCI 受信データ・バッファ・レジスタ(SCIRXBUF)のビットの説明 | 2-12 |

| 表 2-9  | SCI FIFO 送信(SCIFFTX)レジスタのビットの説明      | 2-14 |

| 表 2-10 | SCI FIFO 受信(SCIFFRX)レジスタのビットの説明      | 2-15 |

| 表 2-11 | SCI FIFO コントロール(SCIFFCT)レジスタのビットの説明  |      |

| 表 2-12 | SCI 優先順位コントロール・レジスタ(SCIPRI)のビットの説明   |      |

#### 第1章

### 概要

シリアル通信インターフェイス(SCI)は、UART として一般的に知られる 2 線式非同期シリアル・ポートです。SCI モジュールは、標準 NRZ(non-return-to-zero)フォーマットを使用する CPU と他の非同期ペリフェラルの間のデジタル通信をサポートします。SCI レシーバおよびトランスミッタは、処理オーバーヘッドを削減するための 16 段 FIFO を備えており、それぞれ独自のイネーブル・ビットと割り込みビットがあります。どちらも、半二重通信用に独立して動作するか、または全二重通信用に同時に動作できます。

データ整合性を保証するために、SCI はブレーク検出、パリティ、オーバーラン、およびフレーミング・エラーについて受信データをチェックします。ビット・レートは、16 ビットのボー・セレクト・レジスタによって、さまざまな速度にプログラムできます。

このリファレンス・ガイドは、TMS320x280x および TMS320x281x ファミリのプロセッサに搭載されている SCI に適用できます。これには、上記ファミリ内のフラッシュベース、ROM ベース、および RAM ベースのデバイスがすべて含まれます。

項目 ページ

| 1.1 | エンハンスド SCI モジュールの概要 | 1-2 |

|-----|---------------------|-----|

| 1.2 | アーキテクチャ             | 1-7 |

#### 注:28x 拡張機能

240xA SCI に比べて、28xSCI はいくつかの機能拡張を特徴としています。 これらの機能については、セクション 1.2.10 を参照してください。

240x、28x は、テキサス・インスツルメンツの商標です。

#### 1.1 エンハンスド SCI モジュールの概要

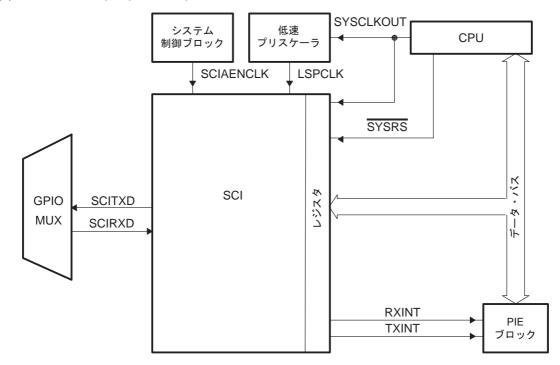

SCI インターフェイスを図 1-1 に示します。

図1-1 SCI CPU インターフェイス

SCIモジュールの機能を以下に示します。

- □ 2つの外部ピン:

- SCITXD: SCI 送信出カピン

- SCIRXD: SCI 受信入力ピン

SCI に使用しない場合は、どちらのピンも GPIO として使用できます。

- □ 64K の異なるレートにプログラムできるボー・レート

- □ データ・ワード・フォーマット

- 1つのスタート・ビット

- 1~8ビットにプログラムできるデータ・ワード長

- オプションの偶数パリティ・ビット / 奇数パリティ・ビット / パリティ・ビット トなし

- 1つまたは2つのストップ・ビット

- □ 4つのエラー検出フラグ:パリティ、オーバーラン、フレーミング、およびブレー ク検出

- □ 2つのウェイクアップ・マルチプロセッサ・モード: アイドル・ラインとアドレス・ビット

- □ 半二重または全二重動作

- □ ダブル・バッファリングされた受信および送信機能

1-2 *概要* JAJU092

- □ トランスミッタおよびレシーバ動作は、ステータス・フラグを使用した割り込み 駆動またはポーリング・アルゴリズムによって実現可能

- □ トランスミッタおよびレシーバ割り込み用の別々のイネーブル・ビット(BRKDT を除く)

- NRZ (non-return-to-zero) フォーマット

- □ アドレス 7050h から始まるコントロール・レジスタ・フレームに配置された 13 の SCI モジュールコントロール・レジスタ

このモジュール内のレジスタは、すべてペリフェラル・フレーム 2 に接続されている 8 ビット・レジスタです。レジスタにアクセスする場合、レジスタ・データは下位バイト (7-0) にあり、上位バイト (15-8) はゼロとしてリードされます。上位バイトにライトしても影響はありません。

#### 拡張機能:

- □ 自動ボー検出ハードウェア・ロジック

- □ 16 段の送信 / 受信 FIFO

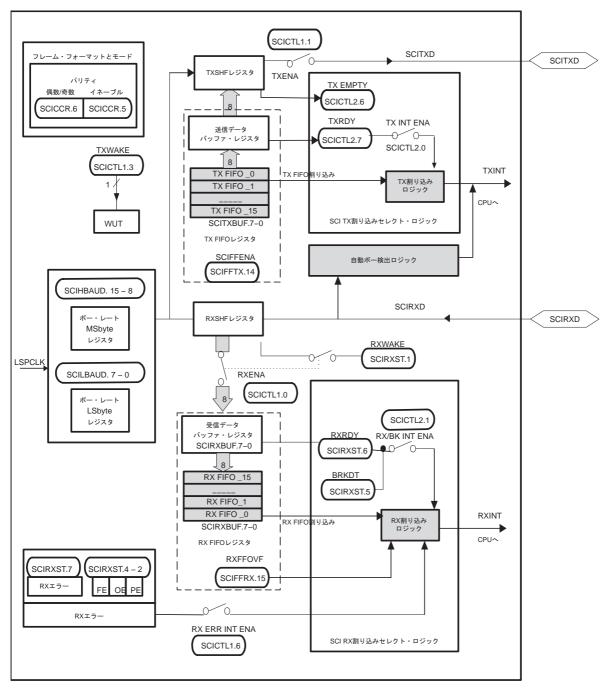

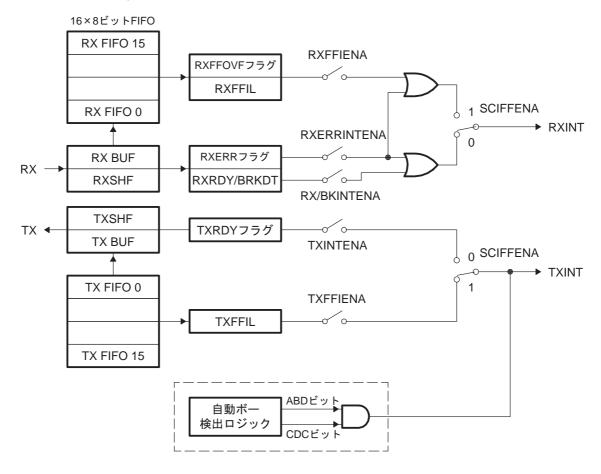

図 1-2 に SCI モジュールのブロック図を示します。

SCI ポート動作は、表 1-1 と表 1-2 に示したレジスタによって設定および制御されます。

*JAJU092* 概要 1-3

#### 図 1-2 シリアル通信インターフェイス (SCI) モジュールのブロック図

1-4 *概要* JAJU092

表 1-1 SCI-A レジスタ

| 名前       | アドレス範囲      | サイズ(x16) | 説明                             |

|----------|-------------|----------|--------------------------------|

| SCICCR   | 0x0000-7050 | 1        | SCI-A 通信コントロール・レジスタ            |

| SCICTL1  | 0x0000-7051 | 1        | SCI-A コントロール・レジスタ 1            |

| SCIHBAUD | 0x0000-7052 | 1        | SCI-A ボー・レジスタ、上位ビット            |

| SCILBAUD | 0x0000-7053 | 1        | SCI-A ボー・レジスタ、下位ビット            |

| SCICTL2  | 0x0000-7054 | 1        | SCI-A コントロール・レジスタ 2            |

| SCIRXST  | 0x0000-7055 | 1        | SCI-A 受信ステータス・レジスタ             |

| SCIRXEMU | 0x0000-7056 | 1        | SCI-A 受信エミュレーション・データ・バッファ・レジスタ |

| SCIRXBUF | 0x0000-7057 | 1        | SCI-A 受信データ・バッファ・レジスタ          |

| SCITXBUF | 0x0000-7059 | 1        | SCI-A 送信データ・バッファ・レジスタ          |

| SCIFFTX  | 0x0000-705A | 1        | SCI-A FIFO 送信レジスタ              |

| SCIFFRX  | 0x0000-705B | 1        | SCI-A FIFO 受信レジスタ              |

| SCIFFCT  | 0x0000-705C | 1        | SCI-A FIFO コントロール・レジスタ         |

| SCIPRI   | 0x0000-705F | 1        | SCI-A 優先順位コントロール・レジスタ          |

JAJU092 概要 1-5

表 1-2 SCI-B レジスタ

| 名前       | アドレス範囲      | サイズ(x16) |                                |

|----------|-------------|----------|--------------------------------|

| SCICCR   | 0x0000-7750 | 1        | SCI-B 通信コントロール・レジスタ            |

| SCICTL1  | 0x0000-7751 | 1        | SCI-B コントロール・レジスタ 1            |

| SCIHBAUD | 0x0000-7752 | 1        | SCI-B ボー・レジスタ、上位ビット            |

| SCILBAUD | 0x0000-7753 | 1        | SCI-B ボー・レジスタ、下位ビット            |

| SCICTL2  | 0x0000-7754 | 1        | SCI-B コントロール・レジスタ 2            |

| SCIRXST  | 0x0000-7755 | 1        | SCI-B 受信ステータス・レジスタ             |

| SCIRXEMU | 0x0000-7756 | 1        | SCI-B 受信エミュレーション・データ・バッファ・レジスタ |

| SCIRXBUF | 0x0000-7757 | 1        | SCI-B 受信データ・バッファ・レジスタ          |

| SCITXBUF | 0x0000-7759 | 1        | SCI-B 送信データ・バッファ・レジスタ          |

| SCIFFTX  | 0x0000-775A | 1        | SCI-B FIFO 送信レジスタ              |

| SCIFFRX  | 0x0000-775B | 1        | SCI-B FIFO 受信レジスタ              |

| SCIFFCT  | 0x0000-775C | 1        | SCI-B FIFO コントロール・レジスタ         |

| SCIPRI   | 0x0000-775F | 1        | SCI-B 優先順位コントロール・レジスタ          |

注: 1) レジスタは、ペリフェラル・フレーム 2 にマップされます。このフレームでは、16 ビット・アクセスだけが許可されます。32 ビッ

1-6 概要 JAJU092

ト・アクセスを使用すると、結果は不定になります。 2) SCIB はオプションのペリフェラルです。一部のデバイスでは、このオプションがない場合があります。ペリフェラルの可用性につ いては、デバイス別のデータ・シートを参照してください。

#### 1.2 アーキテクチャ

図1-2に示す全二重動作で使用される主なエレメントには、以下のものが含まれます。

- □ トランスミッタ (TX) とその主要レジスタ (図 1-2 の上半分)

- SCITXBUF トランスミッタ・データ・バッファ・レジスタ。送信される データ(CPU によってロードされる)が入っている

- TXSHF レジスタ トランスミッタ・シフト・レジスタ。SCITXBUF レジス タからデータを受け入れ、データを 1 ビットずつ SCITXD ピンにシフトする

- □ レシーバ(RX) とその主要レジスタ(図 1-2 の下半分)

- RXSHF レジスタ レシーバ・シフト・レジスタ。SCIRXD ピンからデータ を 1 ビットずつシフトインする

- SCIRXBUF レシーバ・データ・バッファ・レジスタ。CPU によってリードされるデータが入っている。リモート・プロセッサからのデータは、RXSHF レジスタにロードされてから、SCIRXBUF および SCIRXEMU レジスタにロードされる

- □ プログラマブル・ボー・ジェネレータ

- □ データ・メモリ・マップドコントロールおよびステータス・レジスタ

SCIレシーバおよびトランスミッタは独立し、同時に動作できます。

#### 1.2.1 SCI モジュール信号一覧

| 信号名     | 説明                   |

|---------|----------------------|

| 外部信号    |                      |

| SCIRXD  | SCI 非同期シリアル・ポート受信データ |

| SCITXD  | SCI 非同期シリアル・ポート送信データ |

| コントロール  |                      |

| ボー・クロック | LSPCLK プリスケール・クロック   |

| 割り込み信号  |                      |

| TXINT   | 送信割り込み               |

| RXINT   | 受信割り込み               |

JAJU092 概要 1-7

#### 1.2.2 マルチプロセッサおよび非同期通信モード

SCIには、2 つのマルチプロセッサ・プロトコルがあります。1 つはアイドル・ライン・マルチプロセッサ・モード (1-11 ページのセクション 1.2.5 を参照)、もう 1 つはアドレス・ビット・マルチプロセッサ・モード (1-13 ページのセクション 1.2.6 を参照)です。これらのプロトコルにより、複数のプロセッサ間の効率的なデータ転送が可能になります。

SCI は、多くの一般的なペリフェラルとインターフェイスを行うためのユニバーサル 非同期レシーバ / トランスミッタ (UART) 通信モードを提供します。非同期モード (1-15 ページのセクション 1.2.7) では、RS-232-C フォーマットを使用する端末やプリンタなどの多数の標準デバイスとインターフェイスを行うために 2 つのラインが必要になります。データ送信の特性を以下に示します。

- □ 1つのスタート・ビット

- □ 1~8つのデータ・ビット

- □ 偶数 / 奇数パリティ・ビット、またはパリティ・ビットなし

- □ 1つまたは2つのストップ・ビット

#### 1.2.3 SCI プログラマブル・データ・フォーマット

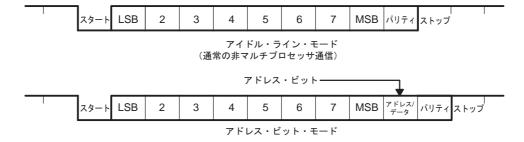

SCI データ(受信と送信の両方)は、NRZ(non-return-to-zero)フォーマットです。 NRZ データ・フォーマット(図 1-3 を参照)は、以下で構成されます。

- □ 1つのスタート・ビット

- □ 1~8つのデータ・ビット

- □ 偶数 / 奇数パリティ・ビット (オプション)

- □ 1つまたは2つのストップ・ビット

- □ アドレスとデータを区別するためのエクストラ・ビット (アドレス・ビット・モードのみ)

データの基本単位はキャラクタと呼ばれ、1~8 ビットの長さです。データの各キャラクタは、1つのスタート・ビット、1つまたは2つのストップ・ビット、オプションのパリティおよびアドレス・ビットでフォーマットされます。フォーマット情報を持ったデータのキャラクタはフレームと呼ばれます(図 1-3 を参照)。

#### 図 1-3 一般的な SCI データ・フレーム・フォーマット

1-8 *概要* JAJU092

データ・フォーマットをプログラムするには、SCICCR レジスタを使用します。データ・フォーマットのプログラミングに使用するビットを表 1-3 に示します。

表 1-3 SCICCR を使用したデータ・フォーマットのプログラミング

| ビット | ビット名            | 指定         | 機能                                                                      |

|-----|-----------------|------------|-------------------------------------------------------------------------|

| 2-0 | SCI CHAR2-0     | SCICCR.2:0 | キャラクタ(データ)長(0~8ビット)を選択します。                                              |

| 5   | PARITY ENABLE   | SCICCR.5   | 1 にセットされた場合はパリティ機能をイネーブルにし、0 にクリ<br>アされた場合はパリティ機能をディスエーブルにします。          |

| 6   | EVEN/ODD PARITY | SCICCR.6   | パリティがイネーブルの場合、0 にクリアされると奇数パリティを<br>選択し、1 にセットされると偶数パリティを選択します。          |

| 7   | STOP BITS       | SCICCR.7   | 送信されるストップ・ビットの数を決定します(0 にクリアされた場合は1つのストップ・ビット、1 にセットされた場合は2つのストップ・ビット)。 |

#### 1.2.4 SCI マルチプロセッサ通信

マルチプロセッサ通信フォーマットを使用すると、プロセッサは同じシリアル・リンク上の他のプロセッサにデータのブロックを効率的に送信できます。1つのシリアル・ライン上に存在する転送は、一度に1つだけでなければなりません。つまり、シリアル・ライン上に一度に存在できるのは1つのトーカだけです。

#### アドレス・バイト

トーカが送信する情報ブロックの*最初のバイト*には、すべてのリスナによってリードされるアドレス・バイトが含まれています。アドレス・バイトに続くデータ・バイトによって割り込みできるのは、正しいアドレスを持ったリスナだけです。アドレスが正しくないリスナは、次のアドレス・バイトまで割り込みなしのままになります。

#### スリープ・ビット

シリアル・リンク上の各プロセッサは、アドレス・バイトが検出された場合にのみ割り込みされるように SCI SLEEP ビット (SCICTL1 のビット 2) を 1 にセットします。アプリケーション・ソフトウェアによって設定された CPU デバイス・アドレスに対応するブロック・アドレスをプロセッサがリードする場合、プログラムではSLEEP ビットをクリアして、SCI が各データ・バイトの受信時に割り込みを生成できるようにする必要があります。

レシーバは SLEEP ビットが 1 でも引き続き動作しますが、アドレス・バイトが検出され、受信したフレームのアドレス・ビットが 1 でない限り、RXRDY、RXINT、または任意のレシーバ・エラー・ステータス・ビットを 1 にセットしません(アドレス・ビット・モードに適用可能)。SCI は SLEEP ビットを変更しません。SLEEP ビットの変更は、ソフトウェアで行う必要があります。

JAJU092 概要 1-9

#### 1.2.4.1 アドレス・バイトの認識

プロセッサは、使用しているマルチプロセッサ・モードに応じてアドレス・バイトをさまざまに認識します。その例を以下に示します。

- □ アイドル・ライン・モード(1-11ページのセクション1.2.5)では、アドレス・バイトの前にクワイエット・スペースが残されます。このモードは、エクストラ・アドレス/データ・ビットがなく、10バイトを超えるデータが含まれているブロックの処理ではアドレス・ビット・モードよりも効率的です。アイドル・ライン・モードは、一般的な非マルチプロセッサ SCI 通信の場合に使用する必要があります。

- □ アドレス・ビット・モード (1-13 ページのセクション 1.2.6) では、アドレスと データを区別するためにエクストラ・ビット (つまり、アドレス・ビット) が各 バイトに追加されます。アイドル・モードとは違って、データのブロック間で待 機する必要がないため、多数の小さなデータ・ブロックの処理では、このモード がより効率的です。ただし、高い送信速度では、プログラムは送信ストリームで 10 ビットのアイドルを回避するほど十分に速くありません。

#### 1.2.4.2 SCI TX および RX 機能の制御

マルチプロセッサ・モードは、ADDR/IDLE MODE ビット(SCICCR、ビット 3)に よってソフトウェアで設定できます。どちらのモードも、TXWAKE フラグ・ビット(SCICTL1、ビット 3)、RXWAKE フラグ・ビット(SCIRXST、ビット 1)、SLEEP フラグ・ビット(SCICTL1、ビット 2)を使用して、これらのモードの SCI トランスミッタおよびレシーバ機能を制御します。

#### 1.2.4.3 受信シーケンス

どちらのマルチプロセッサ・モードでも、受信シーケンスは以下のようになります。

- 1) アドレス・ブロックの受信では、SCIポートがウェイクアップして割り込みを要求します(割り込みを要求するには、SCICTL2 のビット番号 1 の RX/BK INT ENA をイネーブルにする必要がある)。SCIポートは、ブロックの最初のフレームをリードします。このフレームには、デスティネーション・アドレスが含まれています。

- 2) 割り込みを通じてソフトウェア・ルーチンに入り、そのルーチンによって受信アドレスがチェックされます。このアドレス・バイトは、メモリに格納されているデバイス・アドレス・バイトと照合されます。

- 3) チェックによって受信した宛先が CPU と同じであることが分かった場合、CPU は SLEEP ビットをクリアし、ブロックの残り部分をリードします。それ以外の場合は、ソフトウェア・ルーチンは SLEEP ビットがセットされたまま終了し、次のブロックが始まるまで割り込みを受信しません。

1-10 *概要* JAJU092

#### 1.2.5 アイドル・ライン・マルチプロセッサ・モード

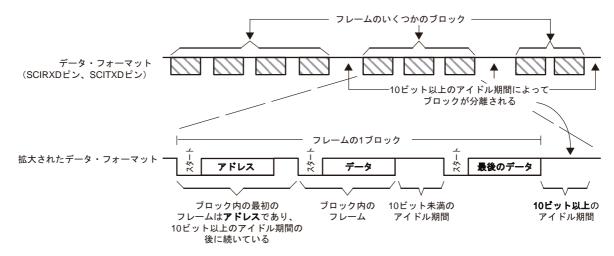

アイドル・ライン・マルチプロセッサ・プロトコル(ADDR/IDLE MODE ビット = 0)では、ブロック内のフレーム間よりもブロック間のアイドル時間を長くすることによってブロックが分離されます。フレーム後の 10 以上のハイレベル・ビットのアイドル時間は、新しいブロックの開始を示します。単一ビットの時間は、ボー値(1 秒当たりのビット数)から直接計算されます。アイドル・ライン・マルチプロセッサ通信フォーマットを図 1-4 に示します (ADDR/IDLE MODE ビットは SCICCR のビット3)。

#### 図 1-4 アイドル・ライン・マルチプロセッサ通信フォーマット

#### 1.2.5.1 アイドル・ライン・モードのステップ

アイドル・ライン・モードでのステップを以下に示します。

- 1) ブロック開始信号を受信すると、SCI がウェイクアップします。

- 2) プロセッサは、次の SCI 割り込みを認識します。

- 3) 割り込みサービス・ルーチンは、受信したアドレス(リモート・トランスミッタ から送られたアドレス)を自身のアドレスと比較します。

- 4) CPU の*宛先と一致した*場合、サービス・ルーチンは SLEEP ビットをクリアし、 残りのデータ・ブロックを受信します。

- 5) CPUの宛先と一致しない場合は、SLEEPビットはセットされたままになります。これにより、次のブロック開始を検出するまで、CPUはSCIポートによって割り込みされることなくメイン・プログラムを引き続き実行できます。

*JAJU092* 概要 1-11

#### 1.2.5.2 ブロック開始信号

ブロック開始信号を送る方法は2つあります。

- □ 方法 1: 前のブロックに含まれるデータの最終フレームの送信から新しいブロックのアドレス・フレームの送信までの時間を遅らせることによって、10 ビット以上のアイドル時間を意図的に残します。

- □ 方法 2: SCI ポートは、SCITXBUF レジスタにライトする前に TXWAKE ビット (SCICTL1、ビット 3) を 1 にセットします。これにより、ちょうど 11 ビットの アイドル時間が送信されます。この方法では、シリアル通信ラインが必要以上に 長くアイドル状態になることはありません。(アイドル時間を送信するために、 TXWAKE の設定後、およびアドレスの送信前に、内容は重要でない don't care バイトを SCITXBUF にライトする必要があります。)

#### 1.2.5.3 ウェイクアップ・テンポラリ (WUT) フラグ

TXWAKE ビットには、ウェイクアップ・テンポラリ(WUT)フラグが関連付けられています。WUT は内部フラグであり、TXWAKE でダブル・バッファリングされます。TXSHF が SCITXBUF からロードされると、WUT が TXWAKE からロードされ、TXWAKE ビットは 0 にクリアされます。この仕組みを図 1-5 に示します。

#### 図 1-5 ダブル・バッファリングされた WUT と TXSHF

**注**:WUT = ウェイクアップ・テンポラリ

#### ブロック開始信号の送信

ブロック送信のシーケンス中に、ちょうど1フレーム時間のブロック開始信号を送信するには、以下の操作を行います。

- 1) TXWAKE ビットに 1 をライトします。

- 2) データ・ワード (内容は重要でない: don't care) を SCITXBUF レジスタ (送信 データ・バッファ) にライトして、ブロック開始信号を送信します (ライトされ た最初のデータ・ワードは、ブロック開始信号の送信中は抑止され、その後は無 視されます)。 TXSHF (送信シフト・レジスタ) が再び解放されると、SCITXBUF の内容が TXSHF にシフトされ、TXWAKE 値が WUT にシフトされて、その後に TXWAKE がクリアされます。

TXWAKE は 1 にセットされたため、スタート・ビット、データ・ビット、およびパリティ・ビットは、前フレームの最後のストップ・ビットに続いて送信された 11 ビットのアイドル期間に置き換えられます。

3) 新しいアドレス値を SCITXBUF にライトします。

TXWAKE ビット値を WUT にシフトできるように、don't care データ・ワードを最初に SCITXBUF レジスタにライトする必要があります。don't care データ・ワードが TXSHF レジスタにシフトされた後は、TXSHF と WUT がどちらもダブル・バッファリングされるため、SCITXBUF(および、必要に応じて TXWAKE)に再びライトすることができます。

1-12 *概要* JAJU092

#### 1.2.5.4 レシーバの動作

レシーバは、SLEEP ビットに関係なく動作します。ただし、レシーバは RXRDY もエラー・ステータス・ビットもセットせず、アドレス・フレームが検出されるまで は受信割り込みも要求しません。

#### 1.2.6 アドレス・ビット・マルチプロセッサ・モード

アドレス・ビット・プロトコル (ADDR/IDLE MODE ビット = 1) では、フレームには、最後のデータ・ビットの直後に続くアドレス・ビットというエクストラ・ビットがあります。アドレス・ビットは、ブロックの最初のフレームでは 1 にセットされ、その他のフレームでは 0 にセットされます。アイドル期間のタイミングは関係ありません(図 1-6 を参照。SCICCR のビット 3 にある ADDR/IDLE MODE ビット)。

#### 1.2.6.1 アドレスの送信

TXWAKE ビット値は、アドレス・ビットに格納されます。送信中は、SCITXBUF レジスタと TXWAKE がそれぞれ TXSHF レジスタと WUT にロードされると、TXWAKE は 0 にリセットされ、WUT は現在のフレームのアドレス・ビット値になります。したがって、アドレスを送信するには、以下の操作を行います。

1) TXWAKE ビットを 1 にセットし、適切なアドレス値を SCITXBUF レジスタにライトします。

このアドレス値が TXSHF レジスタに転送されてシフトアウトされると、アドレス・ビットは 1 として送信されます。これにより、シリアル・リンク上の他のプロセッサは、そのアドレスをリードするよう合図されます。

- 2) TXSHF と WUT がロードされた後に、SCITXBUF と TXWAKE にライトします (TXSHF と WUT はどちらもダブル・バッファリングされるため、すぐにライトできます)。

- 3) TXWAKE ビットを 0 にセットしたままにして、ブロック内の非アドレス・フレームを送信します。

#### 注:アドレス・ビット・フォーマットは、11 パイト以下の転送用です。

一般に、アドレス・ビット・フォーマットは 11 バイト以下のデータ・フレームに 使用されます。このフォーマットでは、送信されるすべてのデータ・バイトに 1 つのビット値(アドレス・フレームの場合は 1、データ・フレームの場合は 0)が追 加されます。アイドル・ライン・フォーマットは、通常は 12 バイト以上のデータ・フレームに使用されます。

JAJU092 概要 1-13

#### 図 1-6 アドレス・ビット・マルチプロセッサ通信フォーマット

1-14 *概要* JAJU092

#### 1.2.7 SCI 通信フォーマット

SCI 非同期通信フォーマットでは、単一ライン(一方向)または 2 ライン(双方向)のいずれかの通信を使用します。このモードでは、フレームは 1 つのスタート・ビット、 $1 \sim 8$  つのデータ・ビット、オプションの偶数 / 奇数パリティ・ビット、および 1 つまたは 2 つのストップ・ビットで構成されます(図 1-7 を参照)。データ・ビットごとに 8 SCICLK 周期があります。

レシーバは、有効なスタート・ビットを受信すると動作を開始します。有効なスタート・ビットは、ゼロ・ビットの4連続の内部SCICLK周期によって識別されます(図 1-7 を参照)。いずれかのビットがゼロでない場合、プロセッサは最初からやり直して、別のスタート・ビットを探します。

スタート・ビットに続くビットでは、プロセッサはそれらのビットの中間で 3 つのサンプルを作成してビット値を判断します。これらのサンプルは4番目、5番目、および6番目の SCICLK 周期で発生し、ビット値は過半数(3 つのうちの2つ)に基づいて判断されます。これについて、スタート・ビットと共に非同期通信フォーマットを図1-7に示します。この図は、どのようにエッジが検出され、どこで多数決処理が行われるのかを表しています。

レシーバはフレームに対して自身を同期させるため、外部の送信および受信デバイスは同期したシリアル・クロックを使用する必要はありません。クロックはローカルで生成できます。

#### 図1-7 SCI 非同期通信フォーマット

JAJU092 概要 1-15

#### 1.2.7.1 通信モードにおけるレシーバ信号

図 1-8 は、以下の条件を前提としたレシーバ信号タイミングの例を示しています。

- □ アドレス・ビット・ウェイクアップ・モード (アイドル・ライン・モードではアドレス・ビットは現れない)

- □ キャラクタごとに6ビット

#### 図 1-8 通信モードにおける SCI RX 信号

- 注: 1) レシーバをイネーブルにするためにフラグ・ビット RXENA (SCICTL1、ビット 0) が High になります。

- 2) データが SCIRXD ピンに到着し、スタート・ビットが検出されます。

- 3) RXSHFからレシーバ・バッファ・レジスタ (SCIRXBUF) にデータがシフトされ、割り込みが要求されます。新しいキャラクタが 受信されたことを知らせるためにフラグ・ビット RXRDY (SCIRXST、ビット 6) が High になります。

- 4) プログラムは SCIRXBUF をリードし、RXRDY フラグは自動的にクリアされます。

- $\vec{r}$  5) データの次のバイトが SCIRXD ピンに到着します。スタート・ビットが検出され、その後にクリアされます。

- 6) レシーバをディスエーブルにするために RXENA ビットが Low になります。データは引き続き RXSHF でアセンブルされますが、 レシーバ・バッファ・レジスタには転送されません。

1-16 *概要* JAJU092

#### 1.2.7.2 通信モードにおけるトランスミッタ信号

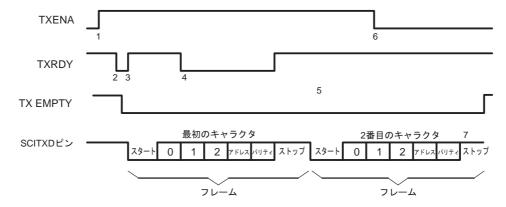

図 1-9 は、以下の条件を前提としたトランスミッタ信号タイミングの例を示しています。

- □ アドレス・ビット・ウェイクアップ・モード (アイドル・ライン・モードではアドレス・ビットは現れない)

- □ キャラクタごとに3ビット

#### 図 1-9 通信モードにおける SCI TX 信号

- 注: 1) TXENA ビット (SCICTL1、ビット 1) が High になり、トランスミッタでデータを送信できるようになります。

- 2) SCITXBUF にライトされます。したがって、(1) トランスミッタは空でなくなり、(2) TXRDY は Low になります。

- 3) SCI はデータをシフト・レジスタ(TXSHF)に転送します。トランスミッタは2番目のキャラクタの準備ができており(TXRDY が High になる)、割り込みを要求します(割り込みをイネーブルにするには、TX INT ENA ビット(SCICTL2、ビット 0)をセットする必要がある)。

- 4) TXRDY が High になると(項目 3)、プログラムは 2 番目のキャラクタを SCITXBUF にライトします。2 番目のキャラクタが SCITXBUF にライトされると、TXRDY がまた Low になります。

- 5) 最初のキャラクタの送信が完了します。シフト・レジスタ TXSHF への 2 番目のキャラクタの転送が始まります。

- 6) トランスミッタをディスエーブルにするために TXENA ビットが Low になります。SCI は現在のキャラクタの送信を終了します。

- 7) 2番目のキャラクタの送信が完了します。トランスミッタは空であり、新しいキャラクタの準備ができています。

*JAJU092* 概要 1-17

#### 1.2.8 SCI ポート割り込み

SCI レシーバおよびトランスミッタは、割り込み制御することができます。SCICTL2 レジスタにはアクティブな割り込み状態を示す 1 つのフラグ・ビット(TXRDY)があり、SCIRXST レジスタには 2 つの割り込みフラグ・ビット(RXRDY と BRKDT)に加えて、FE、OE、および PE 状態の論理 OR である RX ERROR 割り込みフラグがあります。トランスミッタとレシーバは、別々の割り込みイネーブル・ビットを備えています。イネーブルにしなかった場合は、割り込みはアサートされませんが、状態フラグはアクティブなままであり、送信および受信ステータスを反映します。

SCIには、レシーバとトランスミッタに対する独立したペリフェラル割り込みベクトルがあります。ペリフェラル割り込みリクエストは、高い優先順位または低い優先順位にすることができます。これは、ペリフェラルから PIE コントローラに出力される優先順位ビットによって指定されます。RX 割り込みリクエストと TX 割り込みリクエストの両方が同じ優先順位レベルで行われた場合は、レシーバが常にトランスミッタよりも高い優先順位になるため、レシーバのオーバーランが発生する可能性は減少します。

ペリフェラル割り込みの動作については、『TMS320x281x, 280x System Control and Interrupts Peripheral Reference Guide』(文書番号: SPRU078) のペリフェラル割り込み拡張(PIE) の章に記載されています。

- □ RX/BK INT ENA ビット (SCICTL2、ビット 1) がセットされた場合は、以下のいずれかのイベントが発生すると、レシーバ・ペリフェラル割り込みリクエストがアサートされます。

- SCIが完全なフレームを受信し、RXSHFレジスタのデータをSCIRXBUFレジスタに転送する。このアクションにより、RXRDYフラグ(SCIRXST、ビット6)がセットされ、割り込みが開始される。

- ブレーク検出状態が発生する(欠けているストップ・ビットに続いて 10 ビットの期間にわたり SCIRXD が Low になる)。このアクションにより、BRKDTフラグ・ビット(SCIRXST、ビット5)がセットされ、割り込みが開始される。

- □ TX INT ENA ビット (SCICTL2.0) がセットされた場合は、SCITXBUF レジスタのデータが TXSHF レジスタに転送されるたびにトランスミッタ・ペリフェラル割り込みリクエストがアサートされ、CPU が SCITXBUF にライトできることが示されます。このアクションにより、TXRDY フラグ・ビット (SCICTL2、ビット7) がセットされ、割り込みが開始されます。

#### 注:

RXRDY および BRKDT ビットによる割り込み生成は、RX/BK INT ENA ビット (SCICTL2、ビット 1) によって制御されます。RX ERROR ビットによる割り込み 生成は、RX ERR INT ENA ビット (SCICTL1、ビット 6) によって制御されます。

1-18 *概要* JAJU092

#### 1.2.9 SCI ボー・レート計算

内部的に生成されるシリアル・クロックは、低速ペリフェラル・クロック (LSPCLK) とボー・セレクト・レジスタによって決定されます。SCI は、ボー・セレクト・レジスタの 16 ビット値を使用して、特定の LSPCLK に対して実現できる 64K の異なるシリアル・クロック・レートのいずれかを選択します。

SCI 非同期ボーの計算時に使用する式については、セクション 2.4「SCI ボー・セレクト・レジスタ(SCIHBAUD、SCILBAUD)」(2-7 ページ)のビット説明を参照してください。表 1-4 は、一般的な SCI ビット・レートのボー・セレクト値を示しています。

表 1-4 一般的な SCI ビット・レートの非同期ボー・レジスタ値

|        | LSPCLK クロック周波数、37.5MHz |       |       |  |

|--------|------------------------|-------|-------|--|

| 理想的なポー | BRR                    | 実際のボー | エラー%  |  |

| 2400   | 1852 (7A0h)            | 2400  | 0     |  |

| 4800   | 976 (3D0h)             | 4798  | -0.04 |  |

| 9600   | 487 (1E7h)             | 9606  | 0.06  |  |

| 19200  | 243 (F3h)              | 19211 | 0.06  |  |

| 38400  | 121 (79h)              | 38422 | 0.06  |  |

#### 1.2.10 SCI 拡張機能

28x SCI は、自動ボー検出と送信 / 受信 FIFO を特徴としています。以下のセクションでは、FIFO 動作について説明します。

#### 1.2.10.1 SCI FIFO の説明

以下のステップでは、FIFO 機能について説明します。これは、FIFO を使用した SCI のプログラミングで役立ちます。

- 1) <u>リセット</u>。リセット時には、SCI は標準 SCI モードで起動し、FIFO 機能はディスエーブルになります。FIFO レジスタの SCIFFTX、SCIFFRX、および SCIFFCT はインアクティブのままです。

- 2) <u>標準 SCI</u>。標準の 240x SCI モードは、モジュールの割り込みソースとして TXINT/ RXINT 割り込みで通常どおり機能します。

- 3) <u>FIFO イネーブル</u>。SCIFFTX レジスタの SCIFFEN ビットをセットすると、FIFO モードがイネーブルになります。SCIRST は、任意の動作段階で FIFO モードをリセットすることができます。

- 4) <u>アクティブなレジスタ</u>。SCI レジスタとSCI FIFO レジスタ (SCIFFTX、SCIFFRX、 および SCIFFCT) はすべてアクティブです。

- 5) <u>割り込み</u>。FIFO モードには 2 つの割り込みがあります。1 つは送信 FIFO 用の TXINT、もう 1 つは受信 FIFO 用の RXINT です。RXINT は、SCI FIFO 受信、受信エラー、および受信 FIFO オーバーフロー状態の一般的な割り込みです。標準 SCI の TXINT はディスエーブルになり、この割り込みは SCI 送信 FIFO 割り込みとして機能します。

*JAJU092* 概要 1-19

- 6) <u>バッファ</u>。送信および受信バッファは、2 つの 16 レベル FIFO で補われます。送信 FIFO レジスタは 8 ビット幅、受信 FIFO レジスタは 10 ビット幅です。標準 SCI の 1 ワード送信バッファは、送信 FIFO とシフト・レジスタの間のトランジション・バッファとして機能します。1 ワード送信バッファは、シフト・レジスタの最終ビットがシフトアウトされた後にのみ送信 FIFO からロードされます。FIFO をイネーブルにすると、TXSHF はオプションの遅延値(SCIFFCT)の後に直接ロードされます。TXBUF は使用されません。

- 7) 遅延転送。FIFO 内のワードが送信シフト・レジスタに転送されるときのレートはプログラム可能です。SCIFFCT レジスタ・ビット(7-0)の FFTXDLY7 ~ FFTXDLY0 では、ワード転送間の遅延が定義されます。遅延は、SCI ボー・クロック・サイクル数で定義されます。8 ビット・レジスタでは、0 ボー・クロック・サイクルの最小遅延と 256 ボー・クロック・サイクルの最大遅延を定義できます。遅延がゼロの場合、SCI モジュールは連続モードでデータを送信し、FIFO ワードを続けてシフトアウトすることができます。遅延が 256 クロックの場合、SCI モジュールは最大遅延モードでデータを送信し、各ワード間で 256 ボー・クロックの遅延を使用して FIFO ワードをシフトアウトすることができます。プログラマブル遅延は、CPU がほとんど介在しない低速 SCI/UART との通信を容易にします。

- 8) FIFO ステータス・ビット。送信 FIFO と受信 FIFO には、FIFO で常に使用できるワード数を定義する TXFFST または RXFFST ステータス・ビット (ビット 12-0) があります。送信 FIFO リセット・ビット TXFIFO と受信リセット・ビット RXFIFO を 0 にクリアすると、FIFO ポインタがゼロにリセットされます。これらのビットを 1 にセットすると、FIFO は動作をはじめから再開します。

- 9) プログラマブル割り込みレベル。送信 FIFO と受信 FIFO は、どちらも CPU 割り込みを生成できます。割り込みトリガは、送信 FIFO ステータス・ビットの TXFFST (ビット 12-8) が割り込みトリガ・レベル・ビットの TXFFIL (ビット 4-0) と一致する (TXFFIL 以下になる) たびに生成されます。これにより、SCI の送信および受信セクションに対するプログラマブル割り込みトリガが提供されます。これらのトリガ・レベル・ビットのデフォルト値は、受信 FIFO では 0x11111、送信 FIFO では 0x000000 となります。

図 1-10 と表 1-5 では、非 FIFO/FFO モードにおける SCI 割り込みの動作 / 設定について説明します。

1-20 *概要* JAJU092

#### 図 1-10 SCI FIFO 割り込みフラグとイネーブル・ロジック

表 1-5 SCI 割り込みフラグ

| FIFO<br>オプション      | SCI 割り込み<br>ソース    | 割り込み<br>フラグ | 割り込み<br>イネーブル           | FIFO<br>イネーブル<br>SCIFFENA | 割り込みライン |

|--------------------|--------------------|-------------|-------------------------|---------------------------|---------|

| FIFO を使用しない<br>SCI | 受信エラー              | RXERR       | RXERRINTENA             | 0                         | RXINT   |

|                    | 受信ブレーク             | BRKDT       | RX/BKINTENA             | 0                         | RXINT   |

|                    | データ受信              | RXRDY       | RX/BKINTENA             | 0                         | RXINT   |

|                    | 送信エンプティ            | TXRDY       | TXINTENA                | 0                         | TXINT   |

| FIFO を使用した<br>SCI  | 受信エラーおよび<br>受信ブレーク | RXERR       | RXERRINTENA             | 1                         | RXINT   |

|                    | FIFO 受信            | RXFFIL      | RXFFIENA                | 1                         | RXINT   |

|                    | 送信エンプティ            | TXFFIL      | TXFFIENA                | 1                         | TXINT   |

| 自動ボー               | 自動ボー検出             | ABD         | Don't care<br>(どちらでもよい) | x                         | TXINT   |

注: 1) RXERR は、BRKDT、FE、OE、PE フラグで設定できます。FIFO モードでは、BRKDT 割り込みは RXERR フラグだけを介します。

*JAJU092* 概要 1-21

<sup>2)</sup> FIFO モード TXSHF は遅延値の後に直接ロードされ、TXBUF は使用されません。

#### 1.2.10.2 SCI 自動ボー

ほとんどの SCI モジュールには、自動ボー検出ロジック内蔵ハードウェアがありません。これらの SCI モジュールは、クロック・レートが PLL リセット値に依存する組み込みコントローラと統合されます。多くの場合、組み込みコントローラのクロックは最終設計後に変更されます。拡張機能セットでは、このモジュールはハードウェアにおける自動ボー検出ロジックをサポートします。以下のセクションでは、自動検出機能のイネーブル・シーケンスについて説明します。

#### 1.2.10.3 自動ボー検出シーケンス

SCIFFCT の ABD および CDC ビットは、自動ボー・ロジックを制御します。自動ボー・ロジックを機能させるには、SCIRST ビットをイネーブルにする必要があります。

CDC が 1 (自動ボー・アラインメントを示す) のときに ABD をセットすると、SCI 送信 FIFO 割り込みが発生します (TXINT)。割り込みサービス後は、ソフトウェアで CDC ビットをクリアする必要があります。割り込みサービス後も CDC がセットされたままになっていると、繰り返しの割り込みはなくなります。

ステップ1: SCIFFCT の CDC ビット (ビット 13) をセットし、ABDCLR ビット (ビット 14) に 1 をライトして ABD ビット (ビット 15) をクリアすることにより、SCI の自動ボー検出モードをイネーブルにします。

ステップ2: 1 またはボー・レート限度の 500Kbps 未満になるようにボー・レジス タを初期化します。

ステップ3: 必要なボー・レートでホストからキャラクタ「A」または「a」を受信することを SCI に許可します。最初のキャラクタが「A」または「a」の場合、自動ボー検出ハードウェアは受信ボー・レートを検出して ABD ビットをセットします。

ステップ4: 自動検出ハードウェアは、等価の 16 進ボー値でボー・レート・レジス タを更新します。このロジックは、CPU への割り込みも生成します。

ステップ 5: 割り込みに応答し、SCIFFCT レジスタの ABD CLR (ビット 14) に 1 をライトすることで ABD ビットをクリアします。また、0 をライトして CDC ビットをクリアすることにより、さらなる自動ボー・ロックをディスエーブルにします。

**ステップ6**: キャラクタ「A」または「a」の受信バッファをリードして、バッファ およびバッファ・ステータスを空にします。

1-22 *概要* JAJU092

ステップ7: CDC が 1 (自動ボー・アラインメントを示す) のときに ABD をセットすると、SCI 送信 FIFO 割り込みが発生します (TXINT)。割り込みサービス後は、ソフトウェアで CDC ビットをクリアする必要があります。

#### 注:

より高いボー・レートでは、受信データ・ビットのスルー・レートがトランシーバおよびコネクタの性能に左右されることがあります。通常のシリアル通信が正常に機能していても、より高いボー・レート(一般に、100k ボー以上)では、このスルー・レートによって確実な自動ボー検出が制限され、自動ボー・ロック機能が正常に作動しない可能性があります。

これを回避するには、以下のことをお奨めします。

- □ より低いボー・レートを使用して、ホストと 28x SCI ブート・ローダの間でボー・ロックを実現します。

- □ その後、ホストはロードされた 28x アプリケーションとハンドシェークして、 SCI ボー・レート・レジスタを必要な高いボー・レートに設定できます。

JAJU092 概要 1-23

以下余白

1-24 *概要* JAJU092

### 第2章

### SCI レジスタ

SCIの機能は、ソフトウェアで設定できます。コントロール・ビットのセット(専用のバイトに構成されている)は、必要な SCI 通信フォーマットを初期化するためにプログラムされます。これには、動作モードとプロトコル、ボー値、キャラクタ長、偶数/奇数パリティまたはパリティなし、ストップ・ビットの数、割り込みの優先順位とイネーブルが含まれます。

| 1 | 項目   | ページ                                        |

|---|------|--------------------------------------------|

|   | 2.1  | SCI モジュールのレジスター覧2-2                        |

|   | 2.2  | SCI 通信コントロール・レジスタ(SCICCR)                  |

|   | 2.3  | SCI コントロール・レジスタ 1 (SCICTL1)2-5             |

|   | 2.4  | SCI ボー・セレクト・レジスタ(SCIHBAUD、SCILBAUD)2-7     |

|   | 2.5  | SCI コントロール・レジスタ 2 (SCICTL2)2-8             |

|   | 2.6  | SCI レシーバ・ステータス・レジスタ(SCIRXST)2-9            |

|   | 2.7  | レシーバ・データ・バッファ・レジスタ(SCIRXEMU、SCIRXBUF) 2-11 |

|   | 2.8  | SCI 送信データ・バッファ・レジスタ(SCITXBUF)2-13          |

|   | 2.9  | SCI FIFO レジスタ(SCIFFTX、SCIFFRX、SCIFFCT)2-13 |

|   | 2.10 | 優先順位コントロール・レジスタ(SCIPRI)2-17                |

| ı |      |                                            |

#### 2.1 SCI モジュールのレジスター覧

SCI は、表 2-1 と表 2-2 に示したレジスタを通じて制御およびアクセスされます。これらのレジスタについては、後続のセクションで説明します。

表 2-1 SCIA レジスタ

| レジスタ・ニーモニック | アドレス        | ビット数 | 説明                             |

|-------------|-------------|------|--------------------------------|

| SCICCR      | 0x0000-7050 | 1    | SCI-A 通信コントロール・レジスタ            |

| SCICTL1     | 0x0000-7051 | 1    | SCI-A コントロール・レジスタ 1            |

| SCIHBAUD    | 0x0000-7052 | 1    | SCI-A ボー・レジスタ、上位ビット            |

| SCILBAUD    | 0x0000-7053 | 1    | SCI-A ボー・レジスタ、下位ビット            |

| SCICTL2     | 0x0000-7054 | 1    | SCI-A コントロール・レジスタ 2            |

| SCIRXST     | 0x0000-7055 | 1    | SCI-A 受信ステータス・レジスタ             |

| SCIRXEMU    | 0x0000-7056 | 1    | SCI-A 受信エミュレーション・データ・バッファ・レジスタ |

| SCIRXBUF    | 0x0000-7057 | 1    | SCI-A 受信データ・バッファ・レジスタ          |

| SCITXBUF    | 0x0000-7059 | 1    | SCI-A 送信データ・バッファ・レジスタ          |

| SCIFFTX     | 0x0000-705A | 1    | SCI-A FIFO 送信レジスタ              |

| SCIFFRX     | 0x0000-705B | 1    | SCI-A FIFO 受信レジスタ              |

| SCIFFCT     | 0x0000-705C | 1    | SCI-A FIFO コントロール・レジスタ         |

| SCIPRI      | 0x0000-705F | 1    | SCI-A 優先順位コントロール・レジスタ          |

注:濃く塗られた領域のレジスタは、拡張モードで動作します。

表 2-2 SCIB レジスタ

| 名前       | アドレス範囲      | ビット数 | 説明                             |

|----------|-------------|------|--------------------------------|

| SCICCR   | 0x0000-7750 | 1    | SCI-B 通信コントロール・レジスタ            |

| SCICTL1  | 0x0000-7751 | 1    | SCI-B コントロール・レジスタ 1            |

| SCIHBAUD | 0x0000-7752 | 1    | SCI-B ボー・レジスタ、上位ビット            |

| SCILBAUD | 0x0000-7753 | 1    | SCI-B ボー・レジスタ、下位ビット            |

| SCICTL2  | 0x0000-7754 | 1    | SCI-B コントロール・レジスタ 2            |

| SCIRXST  | 0x0000-7755 | 1    | SCI-B 受信ステータス・レジスタ             |

| SCIRXEMU | 0x0000-7756 | 1    | SCI-B 受信エミュレーション・データ・バッファ・レジスタ |

| SCIRXBUF | 0x0000-7757 | 1    | SCI-B 受信データ・バッファ・レジスタ          |

| SCITXBUF | 0x0000-7759 | 1    | SCI-B 送信データ・バッファ・レジスタ          |

| SCIFFTX  | 0x0000-775A | 1    | SCI-B FIFO 送信レジスタ              |

| SCIFFRX  | 0x0000-775B | 1    | SCI-B FIFO 受信レジスタ              |

| SCIFFCT  | 0x0000-775C | 1    | SCI-B FIFO コントロール・レジスタ         |

| SCIPRI   | 0x0000-775F | 1    | SCI-B 優先順位コントロール・レジスタ          |

2-2 SCI レジスタ JAJU092

#### 2.2 SCI 通信コントロール・レジスタ(SCICCR)

SCICCRでは、SCIによって使用されるキャラクタ・フォーマット、プロトコル、および通信モードが定義されます。

図 2-1 SCI 通信コントロール・レジスタ (SCICCR) - アドレス 7050h

| 7         | 6                  | 5                | 4               | 3                 | 2        | 1        | 0        |

|-----------|--------------------|------------------|-----------------|-------------------|----------|----------|----------|

| STOP BITS | EVEN/ODD<br>PARITY | PARITY<br>ENABLE | LOOPBACK<br>ENA | ADDR/IDLE<br>MODE | SCICHAR2 | SCICHAR1 | SCICHAR0 |

| R/W-0     | R/W-0              | R/W-0            | R/W-0           | R/W-0             | R/W-0    | R/W-0    | R/W-0    |

凡例: R = リード・アクセス、W = ライト・アクセス、-0 = リセット後の値

表 2-3 SCI 通信コントロール・レジスタ (SCICCR) のビットの説明

| ピット | 名前            | 説明                                                                                                                                                                                         |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOP BITS     | SCIストップ・ビット数。このビットでは、送信されるストップ・ビットの数が指定されます。レシーバは、1つのストップ・ビットだけをチェックします。                                                                                                                   |

|     |               | 1 2つのストップ・ビット                                                                                                                                                                              |

|     |               | 0 1つのストップ・ビット                                                                                                                                                                              |

| 6   | PARITY        | SCI パリティの奇数 / 偶数選択。PARITY ENABLE ビット(SCICCR、ビット 5)をセットした場合は、PARITY(ビット 6)によって奇数または偶数パリティが指定されます(送信キャラクタと受信キャラクタの両方における、値が 1 の奇数または偶数のビット)。                                                 |

|     |               | 1 偶数パリティ                                                                                                                                                                                   |

|     |               | 0 奇数パリティ                                                                                                                                                                                   |

| 5   | PARITY ENABLE | SCIパリティ・イネーブル。このビットは、パリティ機能をイネーブルまたはディスエーブルにします。SCIがアドレス・ビット・マルチプロセッサ・モードの場合(このレジスタのビット3を使用して設定)、アドレス・ビットはパリティ計算に含まれます(パリティがイネーブルになっている場合)。8ビット未満のキャラクタの場合は、残りの未使用ビットをパリティ計算から除外する必要があります。 |

|     |               | 1 パリティがイネーブルになる                                                                                                                                                                            |

|     |               | 0 パリティがディスエーブルになる。パリティ・ビットは送信時に生成されない、<br>または受信時に予期されない                                                                                                                                    |

| 4   | LOOP BACK ENA | ループバック・テスト・モード・イネーブル。このビットは、ループバック・テスト・モードをイネーブルにします。このモードでは、Tx ピンが内部的に Rx ピンに接続されます。                                                                                                      |

|     |               | 1 ループバック・テスト・モードがイネーブルになる                                                                                                                                                                  |

|     |               | 0 ループバック・テスト・モードがディスエーブルになる                                                                                                                                                                |

JAJU092 SCI レジスタ 2-3

表 2-3 SCI 通信コントロール・レジスタ (SCICCR) のビットの説明 (続き)

| ビット | 名前             | 説明                   |                                 |                     |                                                                                                            |

|-----|----------------|----------------------|---------------------------------|---------------------|------------------------------------------------------------------------------------------------------------|

| 3   | ADDR/IDLE MODE |                      | コセッサ・モー<br>・プロトコルがi             |                     | ・ビット。このビットでは、いずれかのマル                                                                                       |

|     |                | ビット3)を使<br>モードは、エ    | 使用するため、他<br>クストラ・ビッ<br>イン・モードは、 | !の通信モードと<br>トをフレームに | TL1、ビット 2)と TXWAKE 機能 (SCICTL1、<br>は異なります。一般に、アイドル・ライン・<br>追加するため、通常の通信に使用されます。<br>ラ・ビットを追加せず、RS-232 タイプの通 |

|     |                | 1 アドレ                | ノス・ビット・モ                        | ード・プロトコ             | ルが選択される                                                                                                    |

|     |                | 0 アイド                | ・ル・ライン・モ                        | ード・プロトコ             | ルが選択される                                                                                                    |

| 2-0 | SCI CHAR2-0    | 8 ビット) が選<br>で右詰めされ、 | 選択されます。8<br>、SCIRXBUF で         | ビット未満のキ<br>は先行ゼロで埋  | nらのビットでは、SCI キャラクタ長(1 ~ャラクタは、SCIRXBUF および SCIRXEMU<br>といったでは、SCITXBUF は、先行ゼロで埋っのビット値とキャラクタ長は、以下のとお         |

|     |                | SCI CHAR2-0          | ビット値(バイ                         | ナリ)                 |                                                                                                            |

|     |                | SCI CHAR2            | SCI CHAR1                       | SCI CHAR0           | キャラクタ長(ビット)                                                                                                |

|     |                | 0                    | 0                               | 0                   | 1                                                                                                          |

|     |                | 0                    | 0                               | 1                   | 2                                                                                                          |

|     |                | 0                    | 1                               | 0                   | 3                                                                                                          |

|     |                | 0                    | 1                               | 1                   | 4                                                                                                          |

|     |                | 1                    | 0                               | 0                   | 5                                                                                                          |

|     |                | 1                    | 0                               | 1                   | 6                                                                                                          |

|     |                | 1                    | 1                               | 0                   | 7                                                                                                          |

|     |                | 1                    | 1                               | 1                   | 8                                                                                                          |

2-4 SCI レジスタ JAJU092

#### 2.3 SCI コントロール・レジスタ 1 (SCICTL1)

SCICTL1 は、レシーバ / トランスミッタ・イネーブル、TXWAKE および SLEEP 機能、SCI ソフトウェア・リセットを制御します。

図 2-2 SCI コントロール・レジスタ1 (SCICTL1) – アドレス 7051h

| 7   | 6                 | 5           | 4   | 3      | 2     | 1     | 0     |

|-----|-------------------|-------------|-----|--------|-------|-------|-------|

| 予約  | RX ERR<br>INT ENA | SW<br>RESET | 予約  | TXWAKE | SLEEP | TXENA | RXENA |

| R-0 | R/W-0             | R/W-0       | R-0 | R/S-0  | R/W-0 | R/W-0 | R/W-0 |

**凡例**: R = リード・アクセス、W = ライト・アクセス、-0 = リセット後の値

表 2-4 SCI コントロール・レジスタ 1 (SCICTL1) のビットの説明

| ビット | 名前             | 説明                   |                                      |                                                               |

|-----|----------------|----------------------|--------------------------------------|---------------------------------------------------------------|

| 7   | 予約             | リードはゼロを返             | こします。ライトは何の影響も及ぼし                    | ません。                                                          |

| 6   | RX ERR INT ENA |                      |                                      | ノ、RX ERROR ビット(SCIRXST、<br>トすると割り込みがイネーブルにな                   |

|     |                | 1 受信エラ               | 一割り込みがイネーブルになる                       |                                                               |

|     |                | 0 受信エラ               | 一割り込みがディスエーブルになる                     |                                                               |

| 5   | SW RESET       | ステート・マシン<br>に初期化されます | および動作フラグのレジスタ(SCIO。                  | このビットに 0 をライトすると、SCI<br>CTL2 と SCIRXST)がリセット状態                |

|     |                | SW RESET ビッ          | トは、どの設定ビットにも影響しまっ                    | せん。                                                           |

|     |                | 持されます(リセ             | ット後のビット値は、このセクショ<br>、システム・リセット後は、このビ | されるまで特定のリセット状態に保<br>ンの各レジスタ図の下に示されてい<br>ットに 1 をライトして SCI を再度イ |

|     |                | レシーバ・ブレー<br>ビットをクリアし |                                      | ・ビット、ビット 5) の後には、この                                           |

|     |                | セット値をリスト             |                                      | 定ビットに影響することはなく、リ<br>, SW RESET がアサートされると、<br>されます。            |

|     |                | 影響を受けるフラ             | がは以下のとおりです。                          |                                                               |

|     |                | SCI フラグ              | レジスタ・ビット                             | SW RESET 後の値                                                  |

|     |                | TXRDY                | SCICTL2、ビット7                         | 1                                                             |

|     |                | TX EMPTY             | SCICTL2、ビット6                         | 0                                                             |

|     |                | RXWAKE               | SCIRXST、ビット1                         | 0                                                             |

|     |                | PE                   | SCIRXST、ビット2                         | 0                                                             |

|     |                | OE                   | SCIRXST、ビット3                         | 0                                                             |

|     |                | FE                   | SCIRXST、ビット4                         | 0                                                             |

|     |                | BRKDT                | SCIRXST、ビット5                         | 0                                                             |

|     |                | RXRDY                | SCIRXST、ビット6                         | 0                                                             |

|     |                | RX ERROR             | SCIRXST、ビット7                         |                                                               |

JAJU092 SCI レジスタ 2-5

表 2-4 SCI コントロール・レジスタ 1 (SCICTL1) のビットの説明(続き)

| ビット | 名前     | 説明                                                                                                                                                                                             |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | 予約     | リードはゼロを返します。ライトは何の影響も及ぼしません。                                                                                                                                                                   |

| 3   | TXWAKE | SCI トランスミッタ・ウェイクアップ方式セレクト。TXWAKE ビットは、ADDR/IDLE MODE ビット(SCICCR、ビット 3)で指定された送信モード(アイドル・ラインまたはアドレス・ビット)に応じてデータ送信機能の選択を制御します。                                                                    |

|     |        | 1 選択される送信機能は、モード(アイドル・ラインまたはアドレス・ビット)に<br>依存する                                                                                                                                                 |

|     |        | び信機能は選択されない<br>アイドル・ライン・モードの場合: TXWAKE に 1 をライトしてから、データを<br>SCITXBUF レジスタにライトして、11 データ・ビットのアイドル期間を生成する<br>アドレス・ビット・モードの場合: TXWAKE に 1 をライトしてから、データを<br>SCITXBUF にライトして、そのフレームのアドレス・ビットを1にセットする |

|     |        | TXWAKE は、SW RESET ビット(SCICTL1、ビット 5)ではクリアされません。システム・リセット、または WUT フラグへの TXWAKE の転送によってクリアされます。                                                                                                  |

| 2   | SLEEP  | SCI スリープ。TXWAKE ビットは、ADDR/IDLE MODE ビット(SCICCR、ビット 3)で指定された送信モード(アイドル・ラインまたはアドレス・ビット)に応じてデータ送信機能の選択を制御します。マルチプロセッサ・コンフィギュレーションでは、このビットはレシーバ・スリープ機能を制御します。このビットをクリアすると、SCI はスリープ・モードから復帰します。    |

|     |        | SLEEP ビットがセットされても、レシーバは引き続き動作します。ただし、アドレス・バイトが検出されない限り、レシーバ・バッファ・レディ・ビット(SCIRXST、ビット 6、RXRDY)やエラー・ステータス・ビット(SCIRXST、ビット 5-2: BRKDT、FE、OE、および PE)は更新されません。SLEEP は、アドレス・バイトの検出時には $クリア$ されません。   |

|     |        | 1 スリープ・モードがイネーブルになる                                                                                                                                                                            |

|     |        | 0 スリープ・モードがディスエーブルになる                                                                                                                                                                          |

| 1   | TXENA  | SCI トランスミッタ・イネーブル。データは、TXENA がセットされている場合にのみ<br>SCITXD ピンを通じて送信されます。リセットした場合、送信は停止されますが、以前に<br>SCITXBUF にライトしたデータがすべて送信された後にのみ停止されます。                                                           |

|     |        | 1 トランスミッタがイネーブルになる                                                                                                                                                                             |

|     |        | 0 トランスミッタがディスエーブルになる                                                                                                                                                                           |

| 0   | RXENA  | SCI レシーバ・イネーブル。データは SCIRXD ピンで受信され、レシーバ・シフト・レジスタに送信されてからレシーバ・バッファに送信されます。このビットは、レシーバ(バッファへの転送)をイネーブルまたはディスエーブルにします。                                                                            |

|     |        | RXENA をクリアすると、2 つのレシーバ・バッファへの受信キャラクタの転送は停止され、レシーバ割り込みの生成も停止されます。ただし、レシーバ・シフト・レジスタは引き続きキャラクタをアセンブルできます。したがって、キャラクタの受信中に RXENA がセットされた場合は、完全なキャラクタがレシーバ・バッファ・レジスタ(SCIRXEMUと SCIRXBUF)に転送されます。    |

|     |        | 1 受信したキャラクタを SCIRXEMU および SCIRXBUF に送信する                                                                                                                                                       |

|     |        | 0 受信したキャラクタを SCIRXEMU および SCIRXBUF レシーバ・バッファに転送<br>することを防止する                                                                                                                                   |

2-6 SCI レジスタ JAJU092

#### 2.4 SCI ボー・セレクト・レジスタ(SCIHBAUD、SCILBAUD)

SCIHBAUD および SCILBAUD の値では、SCI のボー・レートが指定されます。

図 2-3 ボー・セレクト MSbyte レジスタ (SCIHBAUD) – アドレス 7052h

| 15           | 14     | 13     | 12     | 11     | 10     | 9     | 8     |

|--------------|--------|--------|--------|--------|--------|-------|-------|

| BAUD15 (MSB) | BAUD14 | BAUD13 | BAUD12 | BAUD11 | BAUD10 | BAUD9 | BAUD8 |

| R/W-0        | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

図 2-4 ボー・セレクト LSbyte レジスタ (SCILBAUD) – アドレス 7053h

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0           |

|-------|-------|-------|-------|-------|-------|-------|-------------|

| BAUD7 | BAUD6 | BAUD5 | BAUD4 | BAUD3 | BAUD2 | BAUD1 | BAUD0 (LSB) |

| R/W-0       |

凡例:R=リード・アクセス、W=ライト・アクセス、-n=リセット後の値

表 2-5 ボー・セレクト・レジスタのビットの説明

| ビット  | 名前               | リセット | 説明                                                                                                                                              |

|------|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-0 | BAUD15-<br>BAUD0 | 0    | SCI 16 ビット・ボー選択レジスタの SCIHBAUD(MSbyte)と SCILBAUD<br>(LSbyte)は、16 ビット・ボー値の BRR を形成するために連結されます。                                                    |

|      |                  |      | 内部的に生成されるシリアル・クロックは、低速ペリフェラル・クロック (LSPCLK) 信号と 2 つのボー・セレクト・レジスタによって決定されます。 SCI は、これらのレジスタの 16 ビット値を使用して、通信モードに対する 64K シリアル・クロック・レートのいずれかを選択します。 |

|      |                  |      | SCI ボー・レートは、以下の式で計算されます。                                                                                                                        |

|      |                  |      | SCI 非同期ボー =                                                                                                                                     |

|      |                  |      | あるいは、                                                                                                                                           |

|      |                  |      | BRR = $\frac{\text{LSPCLK}}{\text{SCI 非同期ボー \times 8}} - 1$                                                                                     |

|      |                  |      | 上記の式は、1 $\leq$ BRR1 $\leq$ 65535 の場合にのみ適用されることに注意してください。BRR = 0 の場合は、以下のようになります。                                                                |

|      |                  |      | $SCI$ 非同期ボー = $\frac{LSPCLK}{16}$                                                                                                               |

|      |                  |      | ここで、BRR はボー・セレクト・レジスタの 16 ビット値(10 進数)です。                                                                                                        |

JAJU092 SCI レジスタ 2-7

#### 2.5 SCI コントロール・レジスタ 2 (SCICTL2)

SCICTL2 は、受信レディ、ブレーク検出、および送信レディ割り込みと、トランスミッタ・レディおよびトランスミッタ・エンプティ・フラグをイネーブルにします。

図 2-5 SCI コントロール・レジスタ 2 (SCICTL2) – アドレス 7054h

| 7     | 6        | 5 |     | 2 | 1             | 0          |   |

|-------|----------|---|-----|---|---------------|------------|---|

| TXRDY | TX EMPTY |   | 予約  |   | RX/BK INT ENA | TX INT ENA | ı |

| R-1   | R-1      |   | R-0 |   | R/W-0         | R/W-0      |   |

凡例:R=リード・アクセス、W=ライト・アクセス、-n=リセット後の値

表 2-6 SCI コントロール・レジスタ 2 (SCICTL2) のビットの説明

| ビット | 名前            | 説明                                                                                                                                                                                                                                                                                               |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TXRDY         | トランスミッタ・バッファ・レジスタ・レディ・フラグ。セットした場合、このビットは、送信データ・バッファ・レジスタの SCITXBUF が別のキャラクタを受信できる状態であることを示します。データを SCITXBUF にライトすると、このビットは自動的にクリアされます。このフラグをセットすると、割り込みイネーブル・ビット TX INT ENA (SCICTL2.0) もセットされている場合はトランスミッタ割り込みリクエストがアサートされます。TXRDY は、SW RESET ビット (SCICTL.2) のイネーブルまたはシステム・リセットによって 1 にセットされます。 |

|     |               | 1 SCITXBUF は次のキャラクタを受信する準備ができている                                                                                                                                                                                                                                                                 |

|     |               | 0 SCITXBUF はフルである                                                                                                                                                                                                                                                                                |

| 6   | TX EMPTY      | トランスミッタ・エンプティ・フラグ。このフラグの値は、トランスミッタのバッファ・レジスタ(SCITXBUF)とシフト・レジスタ(TXSHF)の内容を示します。アクティブなSW RESET(SCICTL1.2)、またはシステム・リセットによって、このビットがセットされます。このビットは、割り込みリクエストを <i>引き起こしません</i> 。                                                                                                                      |

|     |               | 1 トランスミッタ・バッファとシフト・レジスタは、どちらも空である                                                                                                                                                                                                                                                                |

|     |               | <ul><li>トランスミッタ・バッファまたはシフト・レジスタ(あるいは、その両方)にデータがロードされる</li></ul>                                                                                                                                                                                                                                  |

| 5-2 | 予約            |                                                                                                                                                                                                                                                                                                  |

| 1   | RX/BK INT ENA | レシーバ・バッファ / ブレーク割り込みイネーブル。このビットは、セットされている RXRDY フラグまたは BRKDT フラグ (SCIRXST.6 および.5) のいずれかによって引き起こされた割り込みリクエストを制御します。<br>ただし、RX/BK INT ENA はこれらのフラグの設定を防止しません。                                                                                                                                     |

|     |               | 1 RXRDY/BRKDT 割り込みをイネーブルにする                                                                                                                                                                                                                                                                      |

|     |               | 0 RXRDY/BRKDT 割り込みをディスエーブルにする                                                                                                                                                                                                                                                                    |

| 0   | TX INT ENA    | SCITXBUF レジスタ割り込みイネーブル。このビットは、TXRDY フラグ・ビット (SCICTL2.7) のセットによって引き起こされた割り込みリクエストを制御します。ただし、TXRDY フラグがセットされることは防止しません (セットされている状態は、レジスタが別のキャラクタを受信する準備ができていることを示す)。                                                                                                                               |

|     |               | 1 TXRDY割り込みをイネーブルにする                                                                                                                                                                                                                                                                             |

|     |               | 0 TXRDY 割り込みをディスエーブルにする                                                                                                                                                                                                                                                                          |

2-8 SCI レジスタ JAJU092

#### 2.6 SCI レシーバ・ステータス・レジスタ (SCIRXST)

SCIRXST には、レシーバ・ステータス・フラグである 7 つのビットがあります(そのうちの 2 つは、割り込みリクエストを生成できる)。完全なキャラクタがレシーバ・バッファ(SCIRXEMU と SCIRXBUF)に転送されるたびに、ステータス・フラグが更新されます。 2-10 ページの図 2-7 は、このレジスタのいくつかのビット間の関係を示しています。

図 2-6 SCI コントロール・レジスタ 2 (SCICTL2) – アドレス 7054h

| 7        | 6     | 5     | 4   | 3   | 2   | 1      | 0   |

|----------|-------|-------|-----|-----|-----|--------|-----|

| RX ERROR | RXRDY | BRKDT | FE  | OE  | PE  | RXWAKE | 予約  |

| R-0      | R-0   | R-0   | R-0 | R-0 | R-0 | R-0    | R-0 |

凡例:R=リード・アクセス、W=ライト・アクセス、-n=リセット後の値

表 2-7 SCI レシーバ・ステータス・レジスタ (SCIRXST) のビットの説明

| ビット | 名前       | 説明                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RX ERROR | SCI レシーバ・エラー・フラグ。RX ERROR フラグは、レシーバ・ステータス・レジス<br>タのいずれかのエラー・フラグがセットされていることを示します。RX ERROR は、ブ<br>レーク検出、フレーミング・エラー、オーバーラン、およびパリティ・エラー・イネーブ<br>ル・フラグ(ビット 5-2:BRKDT、FE、OE、PE)の論理 OR です。                                                                                                                                                                                                                                  |

|     |          | RX ERR INT ENA ビット (SCICTL1.6) がセットされている場合は、このビットが 1 になると割り込みが発生します。このビットは、割り込みサービス・ルーチン中の迅速なエラー状態チェックに使用できます。このエラー・フラグは、直接クリアできません。アクティブな SW RESET またはシステム・リセットによってクリアされます。                                                                                                                                                                                                                                         |

|     |          | 1 エラー・フラグがセットされている                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |          | 0 エラー・フラグはセットされていない                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6   | RXRDY    | SCI レシーバ・レディ・フラグ。新しいキャラクタを SCIRXBUF レジスタからリードする<br>準備ができると、レシーバはこのビットをセットし、RX/BK INT ENA ビット(SCICTL2.1)<br>が 1 の場合はレシーバ割り込みが生成されます。RXRDY は、SCIRXBUF レジスタのリー<br>ド、アクティブな SW RESET、またはシステム・リセットによってクリアされます。                                                                                                                                                                                                            |

|     |          | 1 キャラクタを SCIRXBUF からリードする準備ができている                                                                                                                                                                                                                                                                                                                                                                                    |

|     |          | 0 SCIRXBUF には新しいキャラクタがない                                                                                                                                                                                                                                                                                                                                                                                             |

| 5   | BRKDT    | SCI ブレーク検出フラグ。ブレーク状態が発生すると、SCI はこのビットをセットします。 SCI レシーバ・データ・ライン(SCIRXD)が、欠けている最初のストップ・ビット後から 10 ビット以上連続して Low のままになると、ブレーク状態が発生します。ブレークが発生すると、RX/BK INT ENA ビットが 1 の場合はレシーバ割り込みが生成されますが、レシーバ・バッファはロードされません。レシーバの SLEEP ビットが 1 に設定されている場合でも、BRKDT 割り込みが発生する可能性があります。BRKDT は、アクティブな SW RESET またはシステム・リセットによってクリアされます。ブレークが検出された後のキャラクタの受信ではクリアされません。さらにキャラクタを受信するためには、SW RESET のトグルまたはシステム・リセットによって SCI をリセットする必要があります。 |

|     |          | 1 ブレーク状態が発生している                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |          | 0 ブレーク状態なし                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | FE       | SCI フレーミング・エラー・フラグ。予期されたストップ・ビットが見つからないと、SCI はこのビットをセットします。最初のストップ・ビットだけがチェックされます。欠けているストップ・ビットは、スタート・ビットとの同期が失われていること、およびキャラクタが正しくフレーミングされていないことを意味します。FE ビットは、SW RESET ビットのクリア、またはシステム・リセットによってリセットされます。                                                                                                                                                                                                           |

|     |          | 1 フレーミング・エラーが検出されている                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          | 0 フレーミング・エラーは検出されていない                                                                                                                                                                                                                                                                                                                                                                                                |

JAJU092 SCI レジスタ 2-9

表 2-7 SCI レシーバ・ステータス・レジスタ(SCIRXST)のビットの説明(続き)

| ビット | 名前     | 説明                                                                                                                                                                                                                                           |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | OE     | SCI オーバーラン・エラー・フラグ。前のキャラクタが CPU または DMAC によって完全<br>にリードされる前にキャラクタが SCIRXEMU および SCIRXBUF レジスタに転送される<br>と、SCI はこのビットをセットします。前のキャラクタは上書きされて失われます。OE<br>フラグ・ビットは、アクティブな SW RESET またはシステム・リセットによってリセットされます。                                      |

|     |        | 1 オーバーラン・エラーが検出されている                                                                                                                                                                                                                         |

|     |        | 0 オーバーラン・エラーは検出されていない                                                                                                                                                                                                                        |

| 2   | PE     | SCIパリティ・エラー・フラグ。1の数とパリティ・ビットの間の不整合がある状態でキャラクタが受信されると、このフラグ・ビットがセットされます。アドレス・ビットは、この計算に含まれます。パリティの生成と検出がイネーブルになっていない場合は、PE フラグはディスエーブルになり、0としてリードされます。PE ビットは、アクティブな SW RESET またはシステム・リセットによってリセットされます。                                       |

|     |        | 1 パリティ・エラーが検出されている                                                                                                                                                                                                                           |

|     |        | 0 パリティ・エラーなし、 <b>または</b> パリティがディスエーブルになっている                                                                                                                                                                                                  |

| 1   | RXWAKE | レシーバ・ウェイクアップ検出フラグ。                                                                                                                                                                                                                           |

|     |        | このビットの値が1の場合は、レシーバ・ウェイクアップ状態の検出を意味します。アドレス・ビット・マルチプロセッサ・モード (SCICCR.3 = 1) では、RXWAKE は SCIRXBUF に含まれているキャラクタのアドレス・ビットの値を反映します。アイドル・ライン・マルチプロセッサ・モードでは、SCIRXD データ・ラインがアイドルとして検出された場合に RXWAKE がセットされます。RXWAKE はリード専用フラグであり、以下のいずれかによってクリアされます。 |

|     |        | □ SCIRXBUF に対するアドレス・バイト後の最初のバイトの転送                                                                                                                                                                                                           |

|     |        | □ SCIRXBUF Øリード                                                                                                                                                                                                                              |

|     |        | □ アクティブな SW RESET                                                                                                                                                                                                                            |

|     |        | ロ システム・リセット                                                                                                                                                                                                                                  |

| 0   | 予約     | リードはゼロを返します。ライトは何の影響も及ぼしません。                                                                                                                                                                                                                 |

#### 図 2-7 SCIRXST レジスタのビットの関係 – アドレス 7055h

| 7        | 6     | 5     | 4  | 3  | 2  | 1      | 0  |

|----------|-------|-------|----|----|----|--------|----|

| RX ERROR | RXRDY | BRKDT | FE | OE | PE | RXWAKE | 予約 |

RX/BK INT ENA(SCICTL2.1)= 1の場合は、 RXRDYまたはBRKDTによって割り込みが発生する

─ Rビット5~2のいずれかの値が1の場合は、RX ERROR = 1

2-10 SCI レジスタ JAJU092

#### 2.7 レシーバ・データ・バッファ・レジスタ(SCIRXEMU、SCIRXBUF)

受信したデータは、RXSHFから SCIRXEMU および SCIRXBUF に転送されます。 転送が完了すると、RXRDY フラグ(ビット SCIRXST.6)がセットされ、受信デー タをリードする準備ができたことが示されます。どちらのレジスタにも同じデータ が含まれます。これらのレジスタは別々のアドレスを持ちますが、物理的に分かれ たバッファではありません。

唯一の違いは、SCIRXEMU をリードしても RXRDY フラグはクリアされず、 SCIRXBUF をリードすると RXRDY フラグがクリアされるという点です。

#### 2.7.1 エミュレーション・データ・バッファ (SCIRXEMU)

通常の SCI データ受信動作では、SCIRXBUF レジスタから受信したデータがリードされます。SCIRXEMU レジスタは、RXRDY フラグをクリアすることなく画面更新のために受信データを継続的にリードできるため、主にエミュレータ (EMU) によって使用されます。SCIRXEMU は、システム・リセットによってクリアされます。

これは、SCIRXBUF レジスタの内容を表示するために CCS のウォッチ・ウィンドウで使用する必要があるレジスタです。

SCIRXEMU は物理的に実装されません。これは、RXRDY フラグをクリアすることなく SCIRXBUF レジスタにアクセスするための別のアドレス・ロケーションにすぎません。

図2-8 エミュレーション・データ・バッファ・レジスタ (SCIRXEMU) – アドレス 7056h

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ERXDT7 | ERXDT6 | ERXDT5 | ERXDT4 | ERXDT3 | ERXDT2 | ERXDT1 | ERXDT0 |

| R-0    |

**凡例**: R = リード・アクセス、-0 = リセット後の値

JAJU092 SCI レジスタ 2-11

#### 2.7.2 レシーバ・データ・バッファ (SCIRXBUF)

受信した現在のデータが RXSHF からレシーバ・バッファにシフトされると、RXRDY フラグ・ビットがセットされ、データをリードできる状態になります。 RX/BK INT ENA ビット(SCICTL2.1)がセットされている場合は、このシフトによって割り込みも発生します。 SCIRXBUF がリードされると、 RXRDY フラグがリセットされます。 SCIRXBUF は、システム・リセットによってクリアされます。

図 2-9 SCI 受信データ・バッファ・レジスタ (SCIRXBUF) – アドレス 7057h

| 15      | 14      | 13    |       |       |       |       | 8     |

|---------|---------|-------|-------|-------|-------|-------|-------|

| SCIFFFE | SCIFFPE |       |       | 予約    |       |       |       |

| R-0     | R-0     |       |       | R-    | -0    |       |       |

| 7       | 6       | 5     | 4     | 3     | 2     | 1     | 0     |

| RXDT7   | RXDT6   | RXDT5 | RXDT4 | RXDT3 | RXDT2 | RXDT1 | RXDT0 |

| R-0     | R-0     | R-0   | R-0   | R-0   | R-0   | R-0   | R-0   |

凡例:R=リード・アクセス、W=ライト・アクセス、-n=リセット後の値

注:濃く塗られた領域は、FIFOがイネーブルになっている場合にのみ適用できます。

表 2-8 SCI 受信データ・バッファ・レジスタ (SCIRXBUF) のビットの説明

| ビット  | 名前      | 説明                                                                                             |

|------|---------|------------------------------------------------------------------------------------------------|

| 15   | SCIFFFE | SCIFFFE。SCI FIFO フレーミング・エラー・フラグ・ビット                                                            |

|      |         | 1 ビット 7-0 でキャラクタを受信中にフレーム・エラーが発生しました。このビットは、FIFOの一番上にあるキャラクタに関連付けられています。                       |

|      |         | <ul><li>びット 7-0 でキャラクタを受信中にフレーム・エラーは発生しませんでした。このビットは、FIFO の一番上にあるキャラクタに関連付けられています。</li></ul>   |

| 14   | SCIFFPE | SCIFFPE。SCI FIFO パリティ・エラー・フラグ・ビット                                                              |

|      |         | 1 ビット 7-0 でキャラクタを受信中にパリティ・エラーが発生しました。このビットは、FIFOの一番上にあるキャラクタに関連付けられています。                       |

|      |         | <ul><li>0 ビット 7-0 でキャラクタを受信中にパリティ・エラーは発生しませんでした。このビットは、FIFO の一番上にあるキャラクタに関連付けられています。</li></ul> |

| 13-8 | 予約      |                                                                                                |

| 7-0  | RXDT7-0 | 受信キャラクタ・ビット                                                                                    |

2-12 SCI レジスタ JAJU092

#### 2.8 SCI 送信データ・バッファ・レジスタ (SCITXBUF)

送信されるデータ・ビットは、SCITXBUF にライトされます。長さが 8 ビット未満のキャラクタでは最も左側のビットが無視されるため、これらのビットは右詰にする必要があります。このレジスタから TXSHF トランスミッタ・シフト・レジスタにデータを転送すると、TXRDY フラグ(SCICTL2.7)がセットされ、SCITXBUF で別のデータ・セットを受信する準備ができたことが示されます。TX INT ENA ビット(SCICTL2.0)がセットされている場合は、このデータ転送によって割り込みも発生します。

図 2-10 送信データ・バッファ・レジスタ (SCITXBUF) – アドレス 7059h

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TXDT7 | TXDT6 | TXDT5 | TXDT4 | TXDT3 | TXDT2 | TXDT1 | TXDT0 |

| R/W-0 |

**凡例:**R=リード・アクセス、W=ライト・アクセス、-0=リセット後の値

#### 2.9 SCI FIFO レジスタ (SCIFFTX、SCIFFRX、SCIFFCT)

図 2-11 SCI FIFO 送信(SCIFFTX)レジスタ – アドレス 705Ah

| 15              | 14             | 13              | 12      | 11      | 10      | 9       | 8       |

|-----------------|----------------|-----------------|---------|---------|---------|---------|---------|

| SCIRST          | SCIFFENA       | TXFIFO<br>Reset | TXFFST4 | TXFFST3 | TXFFST2 | TXFFST1 | TXFFST0 |

| R/W-1           | R/W-0          | R/W-1           | R-0     | R-0     | R-0     | R-0     | R-0     |

| 7               | 6              | 5               | 4       | 3       | 2       | 1       | 0       |

| TXFFINT<br>Flag | TXFFINT<br>CLR | TXFFIENA        | TXFFIL4 | TXFFIL3 | TXFFIL2 | TXFFIL1 | TXFFIL0 |

| R-0             | W-0            | R/W-0           | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

**凡例:**R=リード・アクセス、W=ライト・アクセス、-0=リセット後の値

JAJU092 SCI レジスタ 2-13

表 2-9 SCI FIFO 送信(SCIFFTX)レジスタのビットの説明

| ビット  | 名前           | 説明                                                 |                                                                                                                                   |

|------|--------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 15   | SCIRST       | 0                                                  | 0 をライトすると、SCI 送信および受信チャネルがリセットされます。SCI FIFO レジスタ設定ビットは、そのまま残されます。                                                                 |

|      |              | 1                                                  | SCI FIFO は送信または受信を再開できます。SCIRST は、自動ボー・ロジックを機能させる場合でも1にする必要があります。                                                                 |

| 14   | SCIFFENA     | 0                                                  | SCI 拡張 FIFO はディスエーブルになる                                                                                                           |

|      |              | 1                                                  | SCI 拡張 FIFO はイネーブルになる                                                                                                             |

| 13   | TXFIFO Reset | 送信 F                                               | FO リセット                                                                                                                           |

|      |              | 0                                                  | FIFO ポインタをゼロにリセットし、リセットの状態を保持する                                                                                                   |

|      |              | 1                                                  | 送信 FIFO の動作を再度イネーブルにする                                                                                                            |

| 12-8 | TXFFST4-0    | 00000<br>00001<br>00010<br>00011<br>0xxxx<br>10000 | 送信 FIFO は空である<br>送信 FIFO には 1 ワードがある<br>送信 FIFO には 2 ワードがある<br>送信 FIFO には 3 ワードがある<br>送信 FIFO には x ワードがある<br>送信 FIFO には 16 ワードがある |

| 7    | TXFFINT      | 送信F                                                | FO 割り込み                                                                                                                           |

|      |              | 0                                                  | TXFIFO 割り込みは発生していない(リード専用ビット)                                                                                                     |

|      |              | 1                                                  | TXFIFO 割り込みが発生している(リード専用ビット)                                                                                                      |

| 6    | TXFFINT CLR  | 0                                                  | 0 をライトしても TXFIFINT フラグ・ビットには影響しない。 ビットはゼロをリード・バックする                                                                               |

|      |              | 1                                                  | 1 をライトすると、ビット 7 の TXFFINT フラグがクリアされる                                                                                              |

| 5    | TXFFIENA     | 0                                                  | TXFFIVL マッチ (より小さいまたは等しい) に基づいた TX FIFO 割り込みがディスエーブルになる                                                                           |

|      |              | 1                                                  | TXFFIVL マッチ (より小さいまたは等しい) に基づいた TX FIFO 割り込みがディスエーブルになる                                                                           |

| 4-0  | TXFFIL4-0    | が FIF                                              | _4-0 送信 FIFO 割り込みレベル・ビット。FIFO ステータス・ビット(TXFFST4-0)<br>O レベル・ビット(TXFFIL4-0)とマッチする(より小さいまたは等しい)場合、送<br>O は割り込みを生成します。               |

|      |              | デフォ                                                | ルト値は、0x00000 でなければなりません。                                                                                                          |

2-14 SCI レジスタ JAJU092

図 2-12 SCI FIFO 受信(SCIFFRX)レジスタ – アドレス 705Bh

| 15              | 14             | 13              | 12       | 11      | 10      | 9       | 8       |

|-----------------|----------------|-----------------|----------|---------|---------|---------|---------|

| RXFFOVF         | RXFFOVR<br>CLR | RXFIFO<br>Reset | RXFIFST4 | RXFFST3 | RXFFST2 | RXFFST1 | RXFFST0 |

| R-0             | W-0            | R/W-1           | R-0      | R-0     | R-0     | R-0     | R-0     |

|                 |                |                 |          |         |         |         |         |

| 7               | 6              | 5               | 4        | 3       | 2       | 1       | 0       |

| RXFFINT<br>Flag | RXFFINT<br>CLR | RXFFIENA        | RXFFIL4  | RXFFIL3 | RXFFIL2 | RXFFIL1 | RXFFIL0 |

| R-0             | W-0            | R/W-0           | R/W-1    | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

注:R=リード・アクセス、W=ライト・アクセス、-0=リセット後の値

表 2-10 SCI FIFO 受信 (SCIFFRX) レジスタのビットの説明

| ビット  | 名前          | 説明                                                                                                                                                               |

|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | RXFFOVF     | 受信 FIFO オーバーフロー。これはフラグとして機能しますが、単独で割り込みを生成することはできません。この状態は、受信割り込みがアクティブのときに発生します。受信割り込みは、このフラグ状態を処理する必要があります。                                                    |

|      |             | 0 受信 FIFO はオーバーフローしていない(リード専用ビット)                                                                                                                                |

|      |             | 1 受信 FIFO がオーバーフローしている(リード専用ビット)。17 ワード以上が FIFO で受信されており、最初に受信したワードが失われている                                                                                       |

| 14   | RXFFOVF CLR | 0 0をライトしても RXFFOVF フラグ・ビットには影響しない。ビットはゼロをリード・バックする                                                                                                               |

|      |             | 1 1 をライトすると、ビット 15 の RXFFOVF フラグがクリアされる                                                                                                                          |

| 13   | RXFFOVF     | 受信 FIFO リセット                                                                                                                                                     |

|      | Reset       | 0 FIFO ポインタをゼロにリセットして、リセットの状態にするには、0 をライトする                                                                                                                      |

|      |             | 1 受信 FIFO の動作を再度イネーブルにする                                                                                                                                         |

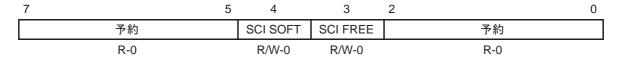

| 8-12 | RXFFST4-0   | 00000 受信 FIFO は空である   00001 受信 FIFO には 1 ワードがある   00010 受信 FIFO には 2 ワードがある   00011 受信 FIFO には 3 ワードがある   0xxxx 受信 FIFO には x ワードがある   10000 受信 FIFO には 16 ワードがある |