# TI Designs: TIDA-01410

# 複数PLLシンセサイザの位相同期のリファレンス・デザイン

# TEXAS INSTRUMENTS

#### 概要

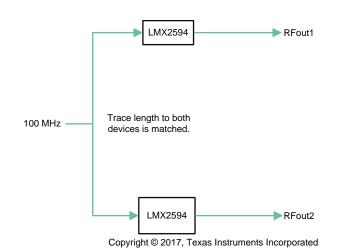

多くのアプリケーションでは、同じ周波数の2つ以上の出力が必要で、位相関係を調整できる必要があります。例として、複数のデータ・コンバータへのクロック供給、ビームの方向調整、スマート・アンテナなどが挙げられます。TIDA-01410デザインでは、2つのLMX2594シンセサイザを使用し、非常に細かい位相調整能力がある、位相の揃った2つの出力を生成します。LMX2594は、10MHz~15GHzの非常に広い範囲で周波数を設定できます。出力信号がプリント基板(PCB)上で遠く離れる可能性がある場合や、PCB上の長い距離にわたって高周波の信号を配線するのを回避したい場合、複数のデバイスを使用するのが適切な方法です。

#### リソース

TIDA-01410

デザイン・フォルダ

LMX2594

プロダクト・フォルダ

PLLATINUMSIM-SW PLLatinum Simulationソフトウェア

TICSPRO-SW TICSProソフトウェア

#### 特長

- 10MHz~15GHzの出力周波数範囲

- 5MHz~1400MHzの入力クロック周波数

- 出力位相が一貫し、調整可能

#### アプリケーション

- ワイヤレス通信テスター

- 半導体テスター

- 信号生成器

- 関数/任意波形

- オシロスコープ

- スペクトラム・アナライザ

- ベクタ信号解析器

- ネットワーク・アナライザ

- ・レーダー

- 軍需/ターゲット認識

使用許可、知的財産、その他免責事項は、最終ページにあるIMPORTANT NOTICE(重要な注意事項)をご参照くださいますようお願いいたします。 英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。 該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。 TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

System Description www.tij.co.jp

#### 1 System Description

The TIDA-01410 design uses two LMX2594 synthesizers to generate two phase coherent outputs locked to the same input reference. Both phase-locked loops (PLLs) have identical routing so that the phase can be controlled. The devices can be synchronized thorough software or pin. The synthesizers can be programmed independently or together by using the programming switches on the board.

Phase synchronization between two PLL synthesizers is very useful for many applications. One such application is test equipment that uses multiple data converters for higher performance. Having clocks with that are high frequency with coherent and adjustable phase are required to clock these converters and allows them to be interleaved for higher performance. This technique is relevant for wireless communication testers, semiconductor testers, functional and arbitrary waveform generators, oscilloscopes, spectrum analyzers, signal analyzers, and network analyzers. Other applications may use two or more elements with adjustable phases for beam steering, smart antennas, and RADAR.

# 1.1 Key System Specifications

表 1. Key System Specifications

| PARAMETER              | SPECIFICATIONS                  |

|------------------------|---------------------------------|

| Output frequency range | 10 MHz to 15 GHz                |

| Input frequency range  | 5 MHz to 1400 MHz               |

| Input voltage range    | 3.15 V to 3.45 V; 3.3-V nominal |

表 2. Loop Filter

| PARAMETER                | VALUE             |

|--------------------------|-------------------|

| VCO frequency            | 7.5 MHz to 15 MHz |

| Phase detector frequency | 200 MHz           |

| Charge pump gain         | 15 mA             |

| Loop bandwidth           | 250 kHz           |

| C1_LF                    | 0.39 nF           |

| C2_LF                    | 68 nF             |

| C3_LF                    | 1.8 nF            |

| R2_LF                    | 68 Ω              |

| R3_LF                    | 18 Ω              |

The loop filter is designed for a 200-kHz phase detector frequency for optimal jitter. If the phase detector frequency requires a significant change, such as in a case when the channel divider is used (due to the extra division in the input path), then the loop filter remains stable and demonstrates the phase relationship. However, the loop filter should be redesigned if the designer wishes to optimize jitter.

www.tij.co.jp System Overview

# 2 System Overview

#### 2.1 Block Diagram

図 1. TIDA-01410 Block Diagram

# 2.2 System Design Theory

The TIDA-01410 reference design features two LMX2594 devices that are capable of demonstrating the use of two synthesizers to generate two outputs that are coherent but adjustable in phase. This design theory has two components: synchronization and phase adjustment. Synchronization involves setting up the devices to maintain the same phase relationship every time they are programmed or the power is cycled. Phase adjustment is the ability to adjust the phase, which is simply referred to as phase adjust.

One important consideration for synchronizing the LMX2594 device in phase is the treatment of the channel divider after the VCO. The approach of the LMX2594 is to include part of this divide inside the feedback loop (known as the IncludedChannelDivide) and then put the rest of the divide outside the loop. This included divide has implications to phase synchronization and phase shifting (see 表 3).

表 3. IncludedChannelDivide

| CHANNEL DIVIDER VALUE       | IncludedChannelDivide |

|-----------------------------|-----------------------|

| Bypass                      | 1                     |

| 6, 12, 48, 72, 96, 384, 768 | 6                     |

| All other values            | 4                     |

System Overview www.tij.co.jp

#### 2.2.1 Theory of Phase Synchronization

The first step in establishing two outputs to be phase coherent is to ensure that the phase relationship can be made to be the same every time. One thing that can cause the phase relationships to be different is if there are divides involved. For instance, whenever a signal is divide-by-two there are two possible output phases, which requires the designer to take action. If this divider is inside the PLL feedback loop (PLL\_N), then the correct phase is always found by the PLL loop itself and no synchronization is required. However, if this divider is outside the loop, such as in the case of using the input divider (PLL\_R), then the designer must provide a synchronization signal. This scenario also applies to the divider after the VCO (CHDIV). Synchronization may also be required when fractional circuitry is involved.

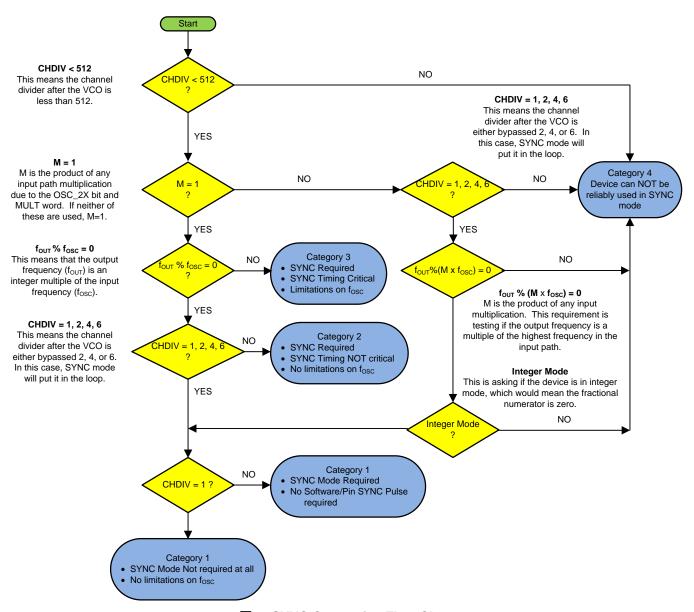

The key to synchronization is to provide a SYNC signal. This signal marks the specific edge of the input signal (OSCin) that is to be used. In some situations the timing of this signal is not critical, but it is still necessary to put the device in SYNC mode and send a pulse. This scenario is referred to as category 2. In other situations, the timing of this SYNC signal is critical. This scenario is referred to as category 3. Refer to the *LMX2594 High Performance*, *Wideband PLLatinum™ RF Synthesizer with Integrated VCO* datasheet[1] and the following  $\boxtimes$  2 for more details on the synchronization process.

www.tij.co.jp System Overview

図 2. SYNC Categories Flow Chart

In the case that the output frequency is a multiple of the input frequency, the timing of this synchronization pulse is not critical, with the exception of where the fractional mode is used with MASH\_SEED > 0. In the case of non-critical timing, sometimes no synchronization pulse is required and other times it is and can be done by toggling the VCO\_PHASE\_SYNC bit ("software sync"). In other cases of non-critical timing, the choice of which input clock rising edge is selected is important and this is referred to as a timing critical sync. The onboard SYNC SMA input can be used for a timing critical sync. This input can be driven with another device such as an LMK04828 or LMX2594 evaluation board to produce a SYNC signal that is far from the rising edge of the input reference clock. The board also allows connection of this SYNC input to the programmable header through resistor R26, which is good for debugging purposes. The SYNC pulse sent by the TICS Pro software is *not* synchronous to OSCin, but the setup is easy to proceed with as long as user is aware that TICS Pro may send the SYNC signal right on the rising edge of OSCin on rare occasions.

System Overview www.tij.co.jp

注: If using the SYNC pin, be sure that the SYNC\_IGNORE bit is disabled. If the SYNC\_IGNORE bit is disabled, ensure that the SYNC input is not floating.

#### 2.2.2 Theory of Phase Shift

After establishing the deterministic phase of the devices, the next task is enable phase shifting. The input and output traces are matched to reduce skew resulting from the board; however, there may still be some phase error introduced by differences in the delays through the components on these traces. The MASH\_SEED word can be used to make fine adjustments for this phase error and remain the same for every power cycle. The phase adjustment due to this MASH\_SEED is calculated using  $\stackrel{\rightarrow}{\Rightarrow}$  1:

Delay (in degrees) = MASH\_SEED

$$\times \frac{\text{(IncludedChannelDivide)}}{\text{(PLL_DEN} \times \text{CHDIV)}}$$

(1)

where,

- MASH\_SEED is the programmed value for MASH\_SEED

- IncludedChannelDivide is the portion of the channel divide that SYNC mode includes in the feedback loop (discussed further in the datasheet)

- · PLL\_DEN is the fractional denominator

- CHDIV is the channel divide value.

- 注: If the SYNC pin or MASH\_RST\_N bit is toggled, the seed value in the accumulator is MASH\_SEED. However, if the MASH\_SEED value is programmed, this value is added to the value in the accumulator. For instance, if the user presses the ENTER key with the cursor in the MASH\_SEED box in TICS Pro, the phase increments each time.

When the device is in SYNC mode (VCO\_PHASE\_SYNC = 1), part of the channel divider may be put in the feedback loop. The part of the divider that is included is the IncludedChannelDivide.

注: The fractional denominator, PLL\_DEN, must be a factor of the IncludedChannelDivide if MASH\_SEED > 0.

Phase shifting *is* possible for integer values of N. In this case, the device is still in fractional mode, but the numerator is zero. Some freedom of choice exists for choosing the denominator, but there is a strategy. Programming non-zero seed values can actually produce fractional spurs with a numerator of zero. Therefore, optimal spurs are obtained when MASH\_SEED is a multiple of IncludedChannelDivide and the fractional denominator is set to k × IncludedChannelDivide, where k is a positive integer that has no factors of 2 or 3. Sub-fractional spurs can be avoided using this strategy. For example, if the channel divide is 4 then IncludedChannelDivide would be 4. Good choices for the fractional denominator would be 4, 20, 28, 44, 52, 68, and so forth. If MASH\_SEED is incremented in steps of IncludedChannelDivide, then there are no resulting sub-fractional spurs. MASH\_SEED can still be incremented in smaller increments; however, the sub-fractional spurs are still present despite being minimal.

www.tij.co.jp System Overview

# 2.3 Highlighted Products

#### 2.3.1 LMX2594

The LMX2594 is a high-performance, wideband PLL with integrated VCOs that can generate any frequency from 10 MHz to 15 GHz without using an internal doubler, which eliminates the requirement for sub-harmonic filters. The high performance PLL with a –236-dBc/Hz figure of merit and high phase detector frequency can attain very low in-band noise and integrated jitter. The high speed N-divider has no pre-divider, thus significantly reducing the amplitude and number of spurs. The device also has a programmable input multiplier to mitigate integer boundary spurs. The LMX2594 allows users to synchronize the output of multiple devices and also enables applications that require deterministic delay between input and output. A frequency ramp generator can synthesize up to two segments of ramp in an automatic ramp generation option or a manual option for maximum flexibility. The fast calibration algorithm allows changing frequencies faster than 20 μs. The LMX2594 adds support for generating or repeating SYSREF (compliant to JESD204B standard), which makes it an ideal low-noise clock source for high-speed data converters. Fine delay adjustment (9-ps resolution) is provided in this configuration to account for delay differences of board traces. The output drivers within LMX2594 deliver output power as high as 7 dBm at a 15-GHz carrier frequency. The device runs from a single 3.3-V supply and has integrated low-dropout (LDOs) regulators that eliminate the requirement for onboard LDOs.

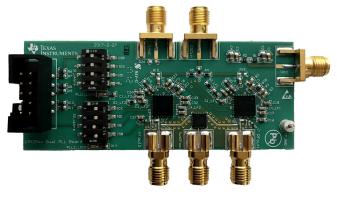

# 3 Getting Started Hardware and Software

# 3.1 Hardware Setup

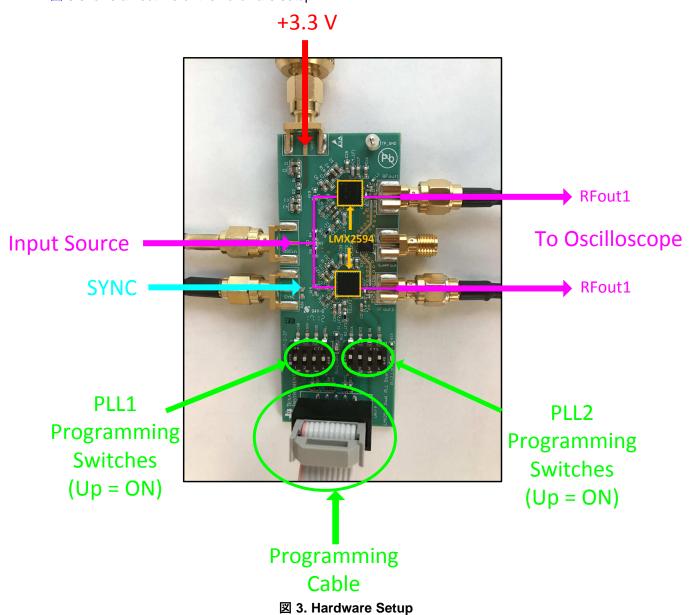

3 shows an outline of the hardware setup.

# 3.1.1 **Power**

Set the power supply to 3.3 V and connect this to the Vcc input SMA. Set the current limit to 1 A.

#### 3.1.2 Input Signal

Connect the input signal to the OSCin SMA. A 100-MHz input signal has been used to obtain the test results in this reference design. Simply use a signal source if a timing critical SYNC is not required; however, if a timing SYNC is required, then consider using something that can produce a SYNC pulse that occurs on the rising edge of the input clock, such as the LMX2594 board (using RFoutB as SYSREF) or the LMK04828 EVM.

If using a noisy signal source, such as a signal generator, be aware that this can dominate close-in phase noise.

#### 3.1.3 Output Signal

Connect the RFout1 and RFout2 outputs to an oscilloscope. Ensure that C13 and C30 are in place and that C13p and C30p are open.

#### 3.1.4 Programming Interface

Connect the laptop to the board using the USB2ANY or ReferencePro interface. For more details, refer to the *LMX2594 EVM Instructions – 15-GHz Wideband Low Noise PLL With Integrated VCO* user's guide[2] to use the TICS Pro graphical user interface (GUI) for programming.

#### 3.2 Programming Switches

This reference design has two banks of switches, one for each LMX2594 synthesizer. Each set of switches has four switches for CSB, SCK, SDA, and MUXout and all four switches in the set should be either ON or OFF altogether. If both sets of switches are ON, then both devices are programmed to the same setting. However, if the designer wants to program the synthesizers to different settings, as would be the case when using MASH\_SEED, then the switches on one of the devices can be turned OFF so that the other device is not programmed. With this set of instructions using switches, a single programming interface can be used to program both devices.

#### 3.3 Software

#### 3.3.1 Download Texas Instruments Clock and Synthesizers (TICS) Pro Software

- 1. Download the TICS Pro Software from Tl.com: http://www.ti.com/tool/TICSPRO-SW.

- 2. To start the software, open the TICS PRO.exe from the installed directory.

Testing and Results www.tij.co.jp

# 4 Testing and Results

# 4.1 Test Setup

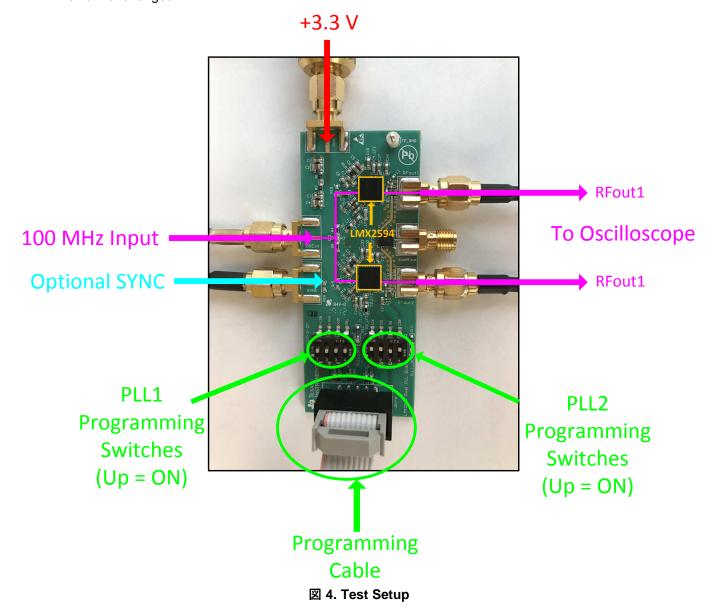

The following test results were obtained using an 8-GHz oscilloscope and the test setup in ☒ 4. The skew between channel 1 and channel 2 has been adjusted to de-skew the signals for the initial setup, but remain unchanged.

www.tij.co.jp Testing and Results

#### 4.2 Test Data

# 4.2.1 Non-Critical TimingSYNC Example

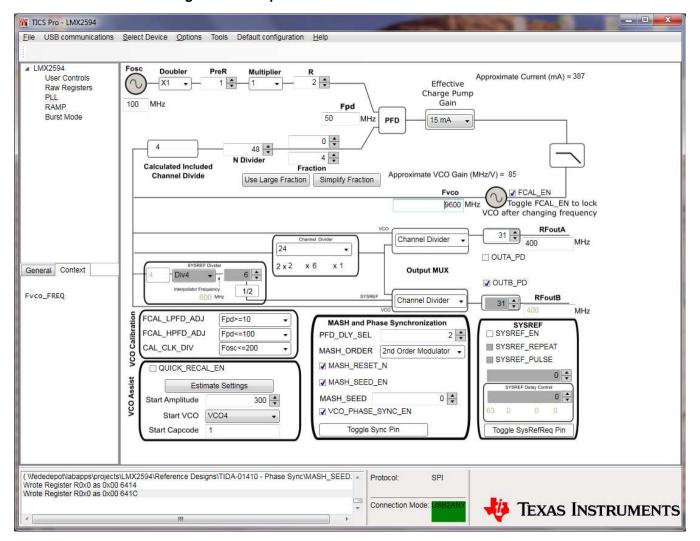

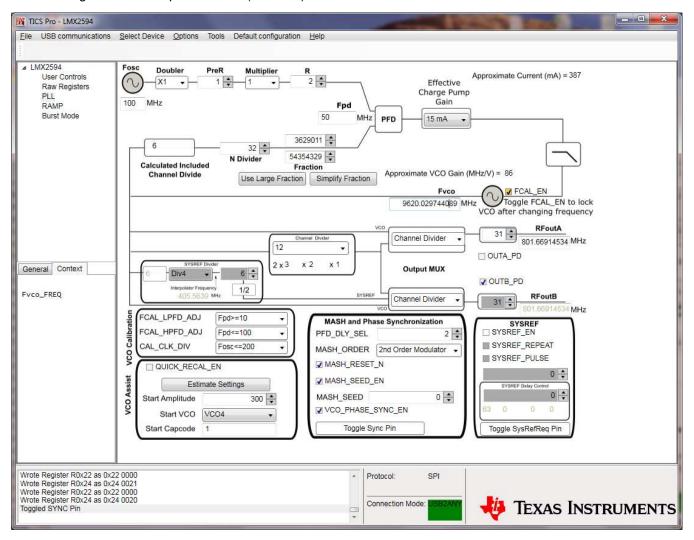

図 5. TICSPro Software Setup for Non-Critical Timing Case

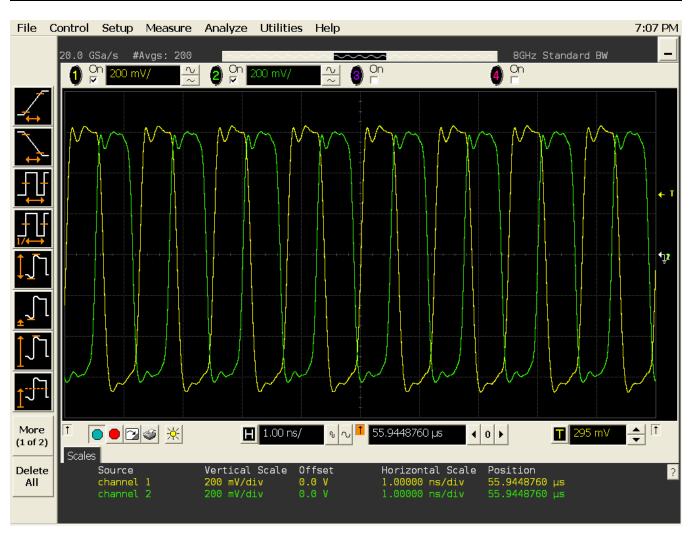

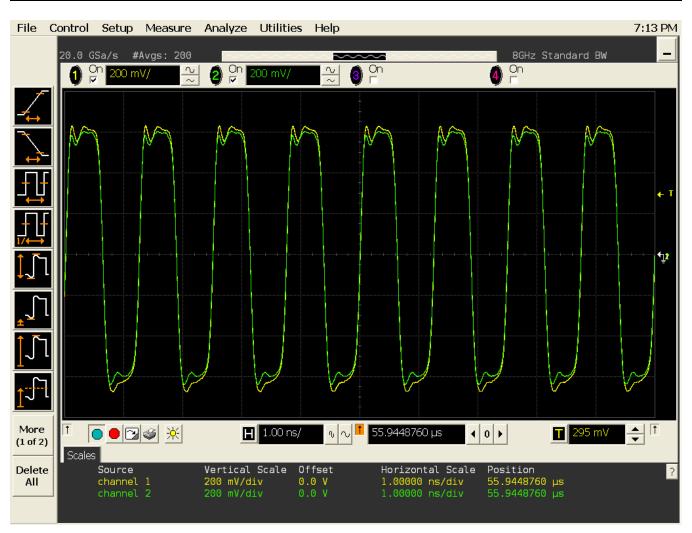

The following figures show the results before ( and after ( 7) VCO PHASE SYNC EN is toggled.

Testing and Results www.tij.co.jp

図 6. Non-Timing Critical Example Before SYNC Pulse

www.tij.co.jp Testing and Results

図 7. Non-Critical SYNC Example After SYNC Pulse

Testing and Results www.tij.co.jp

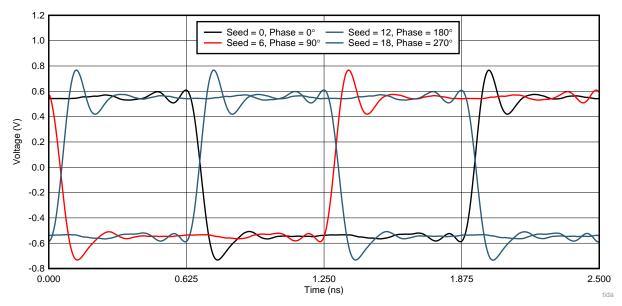

# 4.2.2 Phase Shift Using MASH\_SEED

Using the setup in  $\boxtimes$  5 a starting point, the MASH\_SEED word can be used to shift the phase. In this case, the SYNC is not timing critical because the output frequency is a multiple of the input frequency. The fractional denominator is 4, the included channel divide is 4, and the channel divide is 24; therefore, the designer can determine that each increment in the MASH\_SEED represents a phase shift of:  $360 \times 4 / (4 \times 24) = 15^{\circ}$ . So incrementing the MASH\_SEED by 6 represents a 90° phase shift, which was the measured result. The oscilloscope was triggered on the PLL that was not shifted and the increment in the MASH\_SEED caused a delay, which effectively causes a phase shift to the left. The MASH\_RST\_N bit was toggled each time the seed was changed, which can also be achieved with the SYNC pin. Note that when MASH\_SEED = 6 or 18, there are sub-fractional spurs, but they are very low and far from the carrier (see  $\boxtimes$  8).

図 8. Phase Shift Using MASH SEED

www.tij.co.jp Testing and Results

# 4.3 Timing Critical SYNC Example

In this example, the output frequency is clearly not a multiple of the input frequency, which means the timing of the SYNC pin is critical (see  $\boxtimes$  9).

図 9. Timing Critical Setup Example

Testing and Results www.tij.co.jp

図 10. Timing Critical Example before SYNC

www.tij.co.jp Testing and Results

図 11. Timing Critical Example After SYNC

Design Files www.tij.co.jp

# 5 Design Files

#### 5.1 Schematics

To download the schematics, see the design files at TIDA-01410.

#### 5.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01410.

# 5.3 PCB Layout Recommendations

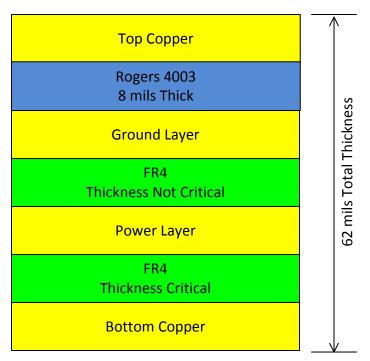

図 12. TIDA-01410 Layer Stack Up Information

Rogers 4003 was chosen for high-frequency performance.

#### 5.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01410.

www.tij.co.jp Design Files

# 5.3.2 Layout Guidelines

Overall, the layout guidelines are similar to most other PLL devices. The following guidelines list the ideal layout:

- Place output pull-up components close to the pin.

- Ensure that the input signal trace is well-matched.

- For the routing of the outputs, single-ended is chosen so that trace lengths can be kept short and

equal length. Pullup components should be as close to the pin as possible. The unused side was sent

to the back side of the board through a via with the loading symmetrical to the used side.

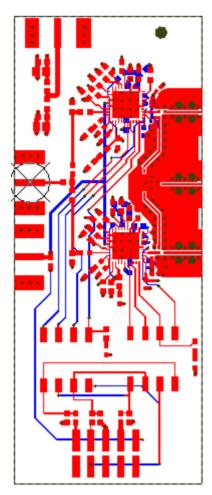

- 13 shows an example layout of the LMX2594 board.

図 13. LMX2594 Layout Example

For more information, see the LMX2594 Datasheet[1] and the LMX2594EVM User's Guide[3].

# 5.4 Altium Project

To download the Altium project files, see the design files at TIDA-01410.

#### 5.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01410.

Design Files www.tij.co.jp

#### 5.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01410.

#### 6 Software Files

To download the software files, see the design files at TIDA-01410.

#### 7 Related Documentation

- 1. Texas Instruments, *LMX2594 High Performance, Wideband PLLatinum™ RF Synthesizer with Integrated VCO*, LMX2594 Datasheet (SNAS646)

- 2. Texas Instruments, *LMX2594 EVM Instructions 15-GHz Wideband Low Noise PLL With Integrated VCO*, LMX5294EVM User's Guide (SNAU210)

- 3. Texas Instruments, *LMX2594EVM High Performance, Wideband PLLatinum™ RF Synthesizer Evaluation Board Operating Instructions*, LMX2594EVM User's Guide (SNAU195)

- 4. Texas Instruments, WEBENCH® Design Center, (http://www.ti.com/webench)

# 7.1 商標

WEBENCH is a registered trademark of Texas Instruments. すべての商標および登録商標はそれぞれの所有者に帰属します。

#### 8 About the Author

**DEAN BANERJEE** is an applications engineer with Texas Instruments working with PLL synthesizers and is the author of *PLL Performance, Simulation, and Design*.

#### TIの設計情報およびリソースに関する重要な注意事項

Texas Instruments Incorporated ("TI")の技術、アプリケーションその他設計に関する助言、サービスまたは情報は、TI製品を組み込んだアプリケーションを開発する設計者に役立つことを目的として提供するものです。これにはリファレンス設計や、評価モジュールに関係する資料が含まれますが、これらに限られません。以下、これらを総称して「TIリソース」と呼びます。いかなる方法であっても、TIリソースのいずれかをダウンロード、アクセス、または使用した場合、お客様(個人、または会社を代表している場合にはお客様の会社)は、これらのリソースをここに記載された目的にのみ使用し、この注意事項の条項に従うことに合意したものとします。

TIによるTIリソースの提供は、TI製品に対する該当の発行済み保証事項または免責事項を拡張またはいかなる形でも変更するものではなく、これらのTIリソースを提供することによって、TIにはいかなる追加義務も責任も発生しないものとします。TIは、自社のTIリソースに訂正、拡張、改良、およびその他の変更を加える権利を留保します。

お客様は、自らのアプリケーションの設計において、ご自身が独自に分析、評価、判断を行う責任がお客様にあり、お客様のアプリケーション(および、お客様のアプリケーションに使用されるすべてのTI製品)の安全性、および該当するすべての規制、法、その他適用される要件への遵守を保証するすべての責任をお客様のみが負うことを理解し、合意するものとします。お客様は、自身のアプリケーションに関して、(1) 故障による危険な結果を予測し、(2) 障害とその結果を監視し、および、(3) 損害を引き起こす障害の可能性を減らし、適切な対策を行う目的での、安全策を開発し実装するために必要な、すべての技術を保持していることを表明するものとします。お客様は、TI製品を含むアプリケーションを使用または配布する前に、それらのアプリケーション、およびアプリケーションに使用されているTI製品の機能性を完全にテストすることに合意するものとします。TIは、特定のTIリソース用に発行されたドキュメントで明示的に記載されているもの以外のテストを実行していません。

お客様は、個別のTIリソースにつき、当該TIリソースに記載されているTI製品を含むアプリケーションの開発に関連する目的でのみ、使用、コピー、変更することが許可されています。明示的または黙示的を問わず、禁反言の法理その他どのような理由でも、他のTIの知的所有権に対するその他のライセンスは付与されません。また、TIまたは他のいかなる第三者のテクノロジまたは知的所有権についても、いかなるライセンスも付与されるものではありません。付与されないものには、TI製品またはサービスが使用される組み合わせ、機械、プロセスに関連する特許権、著作権、回路配置利用権、その他の知的所有権が含まれますが、これらに限られません。第三者の製品やサービスに関する、またはそれらを参照する情報は、そのような製品またはサービスを利用するライセンスを構成するものではなく、それらに対する保証または推奨を意味するものでもありません。TIリソースを使用するため、第三者の特許または他の知的所有権に基づく第三者からのライセンス、あるいはTIの特許または他の知的所有権に基づくTIからのライセンス、あるいはTIの特許または他の知的所有権に基づくTIからのライセンスが必要な場合があります。

TIのリソースは、それに含まれるあらゆる欠陥も含めて、「現状のまま」提供されます。TIは、TIリソースまたはその仕様に関して、明示 的か暗黙的かにかかわらず、他のいかなる保証または表明も行いません。これには、正確性または完全性、権原、続発性の障害に関する保 証、および商品性、特定目的への適合性、第三者の知的所有権の非侵害に対する黙示の保証が含まれますが、これらに限られません。

TIは、いかなる苦情に対しても、お客様への弁護または補償を行う義務はなく、行わないものとします。これには、任意の製品の組み合わせに関連する、またはそれらに基づく侵害の請求も含まれますが、これらに限られず、またその事実についてTIリソースまたは他の場所に記載されているか否かを問わないものとします。いかなる場合も、TIリソースまたはその使用に関連して、またはそれらにより発生した、実際的、直接的、特別、付随的、間接的、懲罰的、偶発的、または、結果的な損害について、そのような損害の可能性についてTIが知らされていたかどうかにかかわらず、TIは責任を負わないものとします。

お客様は、この注意事項の条件および条項に従わなかったために発生した、いかなる損害、コスト、損失、責任からも、TIおよびその代表 者を完全に免責するものとします。

この注意事項はTIリソースに適用されます。特定の種類の資料、TI製品、およびサービスの使用および購入については、追加条項が適用されます。これには、半導体製品(http://www.ti.com/sc/docs/stdterms.htm)、評価モジュール、およびサンプル(http://www.ti.com/sc/docs/sampterms.htm)についてのTIの標準条項が含まれますが、これらに限られません。

Copyright © 2017, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社