TI Designs: TIDA-01411

# Type-2 PoE PSE、6kVの雷サージのリファレンス・デザイン

# TEXAS INSTRUMENTS

## 概要

このリファレンス・デザインは、TIのPSEコントローラ TPS23861を基礎とするPoE (Power over Ethernet) PSE (Power-Sourcing Equipment)システム用の雷サージ保護のソリューションです。このような保護を実装するユースケースは一般に、PSEが動作する予定の環境と、PSEの本質的な絶縁特性に依存します。雷サージ保護はシステム設計の重要な考慮事項であり、ネットワーク・ビデオ・レコーダ (NVR)やデジタル・ビデオ・レコーダ (DVR)などの産業用アプリケーション、およびイーサネット・スイッチ、ゲートウェイなどのテレコム・アプリケーションに有用です。

#### リソース

| TIDA-01411 | デザイン・フォルダ  |

|------------|------------|

| TPS23861   | プロダクト・フォルダ |

| LM5019     | プロダクト・フォルダ |

| ISO7221    | プロダクト・フォルダ |

| ISO1541    | プロダクト・フォルダ |

E2Eエキスパートに質問

## 特長

- UNH-IOL PoE準拠/相互運用性テストと、SIFO Type-1/Type-2のテスト・スイートに合格済み

- 完全自律モードにより、デジタル・インターフェイスの要件を撤廃

- 自動検出および分類、PDの自動電源オンと切断

- 6kV同相および4kV差動モードの雷サージ・テストに合格済み

- 4レベルの雷サージ・レベルの設計

## アプリケーション

- 監視用NVRおよびDVR

- 小型の家庭用およびオフィス用ルータ

- イーサネット・スイッチ

- PoEパススルー・システム

- レジデンシャル・ゲートウェイ

- スモールセル(ピコ、マイクロ、フェムト基地局)

System Description www.tij.co.jp

使用許可、知的財産、その他免責事項は、最終ページにあるIMPORTANT NOTICE(重要な注意事項)をご参照くださいますようお願いいたします。 英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。 該当する正式な英語版の最新情報は、www.ti.comで閲覧でき、その内容が常に優先されます。 TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず最新版の英語版をご参照くださいますようお願いいたします。

## 1 System Description

As integrated circuits (ICs) continue to scale, they become more susceptible to damage from voltage transients. One of the most dangerous types of voltage transients is lightning surge, which can cause arcing or component degradation and lead to device failure. Designing effective protection circuitry is difficult due to the variability of both the magnitude and path of the surges. This reference design shows practical methods for designing protection circuitry for various lightning surge situations.

This reference design showcases robust lightning surge protection for POE PSE systems based on the TI TPS23861 PSE controller. This protection is realized through a variety of methods including: transient voltage suppressors (TVS), Bob Smith terminations, varistors, and grounding. Proper selection and implementation of these components aids in both the suppression and diversion of lightning surges to prevent component failure. A series of surge tests were performed to measure the success of the design. The stated goal during testing was to retain proper device functionality after applying up to 6 kV of common and differential voltage surges to the device.

## 1.1 Key System Specifications

表 1. Key System Specifications

| PARAMETER                            | SPECIFICATIONS                                       |

|--------------------------------------|------------------------------------------------------|

| DC power supply                      | 54 V                                                 |

| PD classification                    | Class 4                                              |

| Surge waveform for common mode       | ±1 kV, 2 kV, 4 kV, and 6 kV;<br>1.2/50 μs, 10/700 μs |

| Surge waveform for differential mode | ±1 kV, 2 kV, 4 kV; 1.2/50 μs                         |

#### **System Overview** 2

#### 2.1 **Block Diagram**

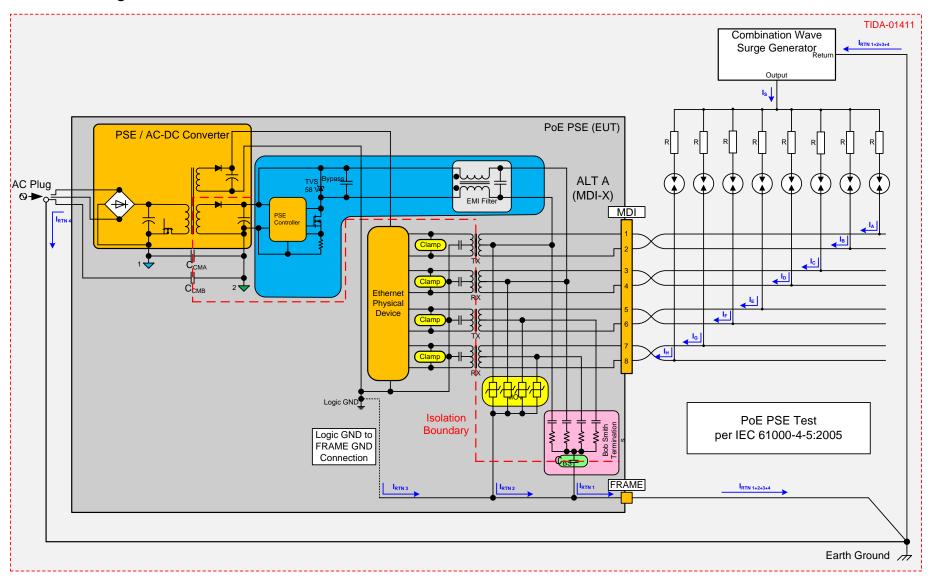

図 1. Examples of Surge Current Paths Through Earthed PSE Application

Most (if not all) PSE applications include a dedicated connection to earth ground, as the previous 🗵 1 shows. Along with acting as a safety ground, this earth-ground connection can serve as a reference ground for internal PSE circuitry, such as Bob Smith cable terminations and the primary-side of an isolated AC/DC converter. These internal earth-ground connections can create paths for common-mode surge currents to flow from the generator, through the PSE, and back to the return of the generator (see 🗵 1).

Referring to  $\boxtimes$  1, the surge current from the generator,  $I_S$ , divides into the eight-wire input of the PSE, as current paths  $I_A$  through  $I_H$  indicate. After entering the PSE, the surge current seeks any paths to earth ground to return to the generator. Two possible return paths are  $I_{RTN}$ , through the Bob Smith termination circuit block,  $I_{RTN}$ , and through the isolated AC/DC converter circuit block. The main conduits for these return paths are the highlighted  $C_{BS}$  capacitor in the Bob Smith termination block and the typically-used  $C_{CMB}$  common-mode noise capacitor in the AC/DC converter block, each of which crosses the isolation boundary. These two return paths plus  $I_{RTN}$  and  $I_{RTN}$  3 combine as  $I_{RTN}$  1+2+3+4, which then returns back to the generator.

The currents indicate a positive surge from the surge generator, despite the fact that the PSE will be subjected to five positive and five negative surges, according to the IEC 61000-4-5 test procedure. Note that the surge current paths within each circuit block can vary depending on the surge polarity. For example, during a positive surge, some surge current flows through the port TVS to the positive rail of the 48-V power supply; conversely, during a negative surge, some surge current flows through the body diode of the port MOSFET.

The PSE controller block includes an electromagnetic interference (EMI) filter, which is normally required to meet conducted emissions requirements. This filter typically employs ferrite beads or a common-mode choke, which can help to reduce the amount of surge current that flows back to the converter. The shown PSE controller block also includes a 58-V TVS, which is typically placed across the port to protect against hot-plug transients and electrostatic discharge (ESD) events. This TVS device also contributes to the protection of the PSE controller during a lightning surge.

Although this reference design primarily focuses on lightning surge protection for the front end and power sections of the PSE, note that surge protection devices (SPD) may be required on the secondary-side data lines, as shown by the clamp blocks highlighted in  $\mathbb Z$  1. Several manufacturers, such as Bourns® and Littelfuse®, offer devices to protect the data lines. To maintain signal integrity, the type of device selected normally depends on the capacitance associated with the device and the data rate of the PoE system. Consult the data sheet of the manufacturer for proper selection of these devices.

The requirements for SPDs in a PSE application normally depends on the required surge test level and the inherent isolation properties of the PSE. The IEEE 802.3 standard specifies that the PSE must provide electrical isolation that withstands an electrical strength test of 1500  $V_{RMS}$ , 2250-V DC, or the 1500  $V_{PK}$  10/700- $\mu$ s impulse test defined in the IEC 60950-1 standard. If the surge test level is below the inherent withstand strength of the PSE, then additional SPDs may not be required. Alternatively, if the PSE is to encounter surge test levels that exceed the withstand strength of the PSE, then the design will most likely require additional SPDs at the front end of the PSE to either clamp the surge voltage below the withstand rating of the PSE or crowbar the surge to earth ground.

## 2.2 Highlighted Products

### 2.2.1 TPS23861

The TPS23861 is an easy-to-use, flexible, IEEE802.3at PSE solution. As shipped, the device automatically manages four 802.3at ports without the requirement of any external control.

The TPS23861 automatically detects powered devices (PDs) that have a valid signature, determines power requirements according to classification, and applies power. Two-event classification is supported for type-2 PDs. The TPS23861 supports DC disconnection and the external field-effect-transistor (FET) architecture allows designers to balance size, efficiency, and solution cost requirements.

The unique pin-out enables two-layer printed-circuit board (PCB) designs through logical grouping and clear upper- and lower-differentiation of I<sup>2</sup>C and power pins. This configuration delivers best-in-class thermal performance, Kelvin accuracy, and low-build cost.

In addition to automatic operation, the TPS23861 supports semi-auto mode through I<sup>2</sup>C control for precision monitoring and intelligent power management.

Compliance with the 400-ms TPON specification is ensured whether in semi-automatic or automatic mode.

The key features are as follows:

- IEEE 802.3at quad-port PSE controller

- Auto detect, classification

- Automatic mode available as shipped

- Optional I<sup>2</sup>C control and monitoring

- TSSOP 28 package 9.8 mm x 6.6 mm

#### 2.2.2 ISO7221BD

The ISO7221B is a dual-channel digital isolator. This device has a logic input and output buffer separated by Tl's silicon-dioxide ( $SiO_2$ ) isolation barrier, providing galvanic isolation of up to 4000  $V_{PK}$  per  $V_{DE}$ . When used with isolated power supplies, this device blocks high voltage, isolates grounds, and prevents noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry.

#### 2.2.3 ISO1541D

The ISO1541 device is a low-power, bidirectional isolator which is compatible with I<sup>2</sup>C interfaces. This device has logic input and output buffers which are separated by Texas Instrument's Capacitive Isolation technology using an SiO2 barrier. When used with isolated power supplies, this device blocks high voltages, isolates grounds, and prevent noise currents from entering the local ground and interfering with or damaging sensitive circuitry.

This isolation technology offers function, performance, size, and power consumption advantages when compared to optocouplers. The ISO1541 device enables the designer to implement a complete, isolated I<sup>2</sup>C interface within a small form factor.

## 2.2.4 LM5019

The LM5019 is a 100-V, 100-mA synchronous step-down regulator with integrated high-side and low-side MOSFETs. The constant-on-time (COT) control scheme employed in the LM5019 requires no loop compensation, provides excellent transient response, and enables very-low step-down ratios. A high-voltage start-up regulator provides bias power for internal operation of the IC and for integrated gate drivers.

A peak current limit protects against overload conditions. The undervoltage lockout (UVLO) circuit allows users to independently program the input undervoltage threshold and hysteresis. Other protection features include thermal shutdown and bias supply undervoltage lockout.

## 2.3 Design Considerations

#### 2.3.1 Overall Guidelines

Many guidelines apply to voltage transient protection for electronic systems. The following is a list of some practical rules along with circuits design strategies:

- The source of transient voltage can be differential-, common-mode type, or both.

- The main categories of protection techniques against transient voltages are shielding and grounding, filtering, isolation, and nonlinear devices.

- A well-designed circuit protection interface is usually the result of a good combination of blocking and diverting techniques.

- The selected voltage suppressor must have the speed and robustness (short-circuit current and waveform) required for the application. Shunt (line-to-earth GND) capacitors that may take direct transient hits must be rated for high voltage (≥ 2 kV). These capacitors must also have the following characteristics: low equivalent series resistance (ESR) at high frequency and low parasitic inductance.

- The protection circuit must not interfere with the normal behavior of the circuitry under protection.

- The protection circuit must be able to prevent any voltage transient from causing erratic behavior (repetitive or not) throughout the complete system—electrical fast transient (EFT) is one example. Use common-mode chokes when necessary.

#### 2.3.2 Basic Circuit Layout Rules

The basic rules of the circuit layout design are:

- Define a low-impedance path that diverts any transient current or voltage away from sensitive components. Do not allow ESD to find a way to earth GND by itself.

- Have a good, solid, and low-impedance earth ground connection onboard.

- Keep the transient current density and the current path impedances as low as possible by using

multipoint grounds where the current is designed to flow, and single-point grounds where it is not.

- The loop within which the fast-rising currents must circulate should be a small area. For fast transients, use local ceramic capacitors whenever necessary, particularly when using clamping diodes on a power-supply rail.

- Create physical separation between high-voltage/current transients area, in close proximity to I/O connectors, and the sensitive circuitry. The high-current suppressors must be located in that I/O area, as well as the switches, LEDs, and displays

- Put all the connectors on one edge of the circuit, if possible. Place sensitive circuitry at the center of the PCB, if possible.

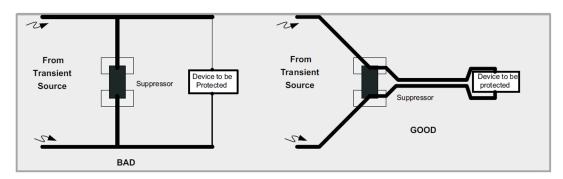

- Route each protected signal from the suppressor to the sensitive circuitry in parallel with its individual return signal to prevent any inadvertent transformer effect.

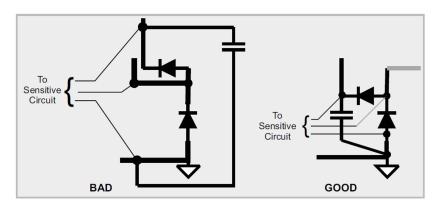

- Use a surface-mount package for suppressors. Use a four-terminal connection type to mitigate the parasitic inductance effect (see ⋈ 2 and ⋈ 3).

- Mitigate parasitic capacitances that are bypassing blocking series elements. However, having parasitic

inductance in series with blocking elements is not a problem.

図 2. Interconnection to Clamping Devices

図 3. Interconnection of Transient Voltage Suppressor on PCB Diagram

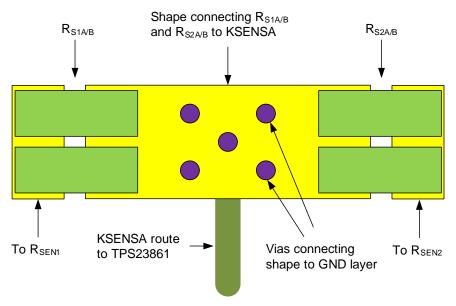

## 2.3.2.1 PCB Layout Considerations for TPS23861

• KSENSA is shared between SEN1 and SEN2, while KSENSB is shared between SEN3 and SEN4. To optimize the accuracy of the measurement, the designer must carefully perform the PCB layout to minimize impact of PCB trace resistance. Refer to

4 as an example.

図 4. Kelvin Sense Layout Example

- Power pin bypass capacitors

- C<sub>VPWR</sub>: Place close to pin 28 (VPWR) and connect with low inductance traces and vias according to 図 5.

- C<sub>VDD</sub>: Place close to pin 1 (VDD) and connect with low inductance traces and vias according to

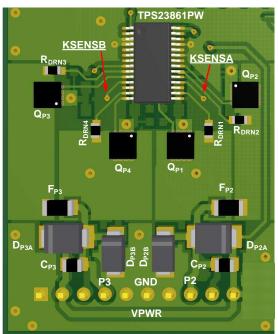

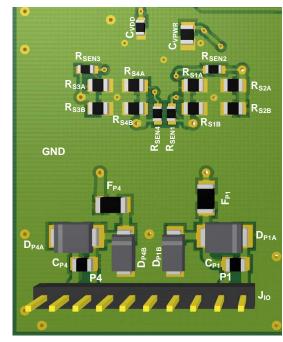

# **BOTTOM SIDE (not mirrored)**

図 5. Four-Port Layout Example

- Per-port components

- R<sub>SnA</sub> / R<sub>SnB</sub>: Place according to 🗵 4 in a manner that facilitates a clean Kelvin connection with

## KSENSEA/B.

- $R_{DRNn}$ : Place  $R_{DRNn}$  near to  $Q_{Pn-D}$ . Connect to DRAINn pins as shown in  $\boxtimes$  5.

- R<sub>SENn</sub>: Place R<sub>SENn</sub> near to Q<sub>Pn-S</sub>. Connect to S<sub>ENn</sub> pins as shown in 図 5.

- F<sub>Pn</sub>, C<sub>Pn</sub>, D<sub>PnA</sub>, D<sub>PnB</sub>: Place this circuit group near the RJ45 port connector (or port power interface if using a daughterboard type of interface as shown in ⋈ 5). Connect this circuit group to Q<sub>Pn-D</sub> / GND (TPS23861-AGND) using low inductance traces.

# 2.4 Choosing SPDs for High-Voltage Surge PSE Applications

This section expands on the PSE example introduced in 2.1 by relating the actual requirement and selection of SPDs to the various test levels associated with the IEC 61000-4-5:2005 symmetrical lines test.

The SPD block is shown to be metal oxide varistors (MOVs) that are used to clamp the surge voltage to earth ground, which creates an added current path, I<sub>RTN 2</sub>, to return the surge current back to the generator when the MOVs are activated. Each MOV would have to be capable of handling the combined currents of two lines. The actual necessity for the MOVs depends on the test-level requirement and the withstand strength of the PSE.

This section also discusses a four-port PSE application with each port defined to meet a different surge level. 表 2 shows the high-level requirement summary.

|      |                  | TEST LEVELS                                 |                        |                                       |                        |             |             |

|------|------------------|---------------------------------------------|------------------------|---------------------------------------|------------------------|-------------|-------------|

| PORT |                  | UNSYMMETRICALLY-<br>OPERATED CIRCUITS/LINES |                        | SYMMETRICALLY-OPERATED CIRCUITS/LINES |                        | WAVEFORM    |             |

| PORT | CLASS            | COUPLING MODE                               |                        | COUPLING MODE COUPLING MODE           |                        | (OCV        | -SCC)       |

|      |                  | LINE-TO-LINE                                | ALL LINES<br>TO GROUND | LINE-TO-LINE                          | ALL LINES<br>TO GROUND |             |             |

| 4    | 2                | _                                           | 1000                   | _                                     | 1000                   |             |             |

| 3    | 3                | _                                           | 2000                   | _                                     | 2000                   | 10/700 µs - | 1.2/50 µs - |

| 2    | 4 <sup>(1)</sup> | 2000                                        | 4000                   | _                                     | 4000                   | 5/320 µs    | 8/20 μs     |

| 1    | 5++              | _                                           | 6000                   | _                                     | 6000                   |             |             |

表 2. Requirements for Four Port Design

The MOVs may not be required for test levels up to 1000 V because the IEEE 802.3 standard specifies that the PSE must have a withstand strength of at least 1500  $V_{PK}$  for the 10/700- $\mu$ s impulse test. This is the case for port 4 ( $\gtrsim$  2) . Use the guidance provided in *Electrical Transient Immunity for Power-Over-Ethernet* for this case. If the PSE port has been designed with a withstand rating per the 1500- $V_{RMS}$  or 2250-V DC rating specified in the IEEE 802.3 standard then the MOVs may not be required for the 2000-V test level. This design example uses MOVs for port 3. The MOVs are a definite requirement to meet test levels that exceed the withstand strength of the PSE, which includes the 4000-V test level in most cases and the 6000-V level always. MOVs are also used for port 1 and port 2 to show the design and selection procedure.

Although the MOVs may not be required to meet some of the lower test levels, implementing them for all conditions can reduce the stress on sensitive components within the AC/DC converter and add to the overall robustness of the PSE. Consider the intended operating environment of the PSE should to assess the potential risk of damage and downtime of the PSE equipment against the added cost of the protection.

<sup>&</sup>lt;sup>(1)</sup> The line-line can be implemented as a line-GND test for an unbalanced circuit or line.

When selecting the proper MOV, be sure to consider the allowable operating voltage, maximum clamping voltage, and surge current ratings. The repetitive surge capability (lifetime rating) of the MOV is equally important because it must survive ten repetitions (five positive and five negative) during the test. In general, the package size of the MOV is directly proportional to its energy handling and surge capability. While MOVs are available in a variety of package styles, this reference design focuses on the use of radial-leaded disc-type devices, which are available in various diameters ranging from 5 mm to 20 mm.

As the test results later verify, the chosen MOVs provide a significantly-higher lifetime rating than ten pulses, which is proven by performing surge testing well beyond the normal product surge lifetime.

The general safety section of the IEEE 802.3 standard specifies that the PoE equipment must conform to the safety requirements of the IEC 60950-1 standard. Section 6.1.2 of this IEC standard states the following regarding SPDs that are connected from telecommunications networks to earth:

6.1.2 Separation of the telecommunication network to earth

## 6.1.2.1 Requirements

Except as specified in 6.1.2.2, there shall be insulation between circuitry intended to be connected to a telecommunications network and any parts or circuitry that will be earthed in some applications, either within the EUT or via other equipment.

Surge suppressors that bridge the insulation must have a minimum rated operating voltage Uop (for example, the sparkover voltage of a gas discharge tube) of Uop = Upeak +  $\Delta$ Usp +  $\Delta$ Usa where Upeak is one of the following values: for equipment intended to be installed in an area where the nominal voltage of the AC mains exceeds 130 V: 360 V for all other equipment: 180 V  $\Delta$ Usp ... shall be taken as 10% of the rated operating voltage of the component.

△Usa ... shall be taken as 10% of the rated operating voltage of the component.

Therefore, based on standard principle, the MOV used for the earthed PSE must have an allowable operating voltage of at least 216  $V_{RMS}$  when installed in an area where the nominal AC mains is less than 130 V and at least 432  $V_{RMS}$  when installed in an area where the nominal AC mains is greater than 130 V. This reference design assumes that the PSE is installed in an area where the nominal AC mains are less than 130 V, which requires an MOV with an allowable operating voltage of at least 230  $V_{RMS}$  (standard value).

Note that the IEC 60950-1 standard allows the removal of insulation-bridging surge suppressors during the steady-state electrical strength test of an SELV circuit. Additionally, the IEEE 802.3 standard specifies that the PSE of the PoE system must not introduce non-SELV power into the PoE wiring plant, which implies that the PSE is considered to be an SELV circuit.

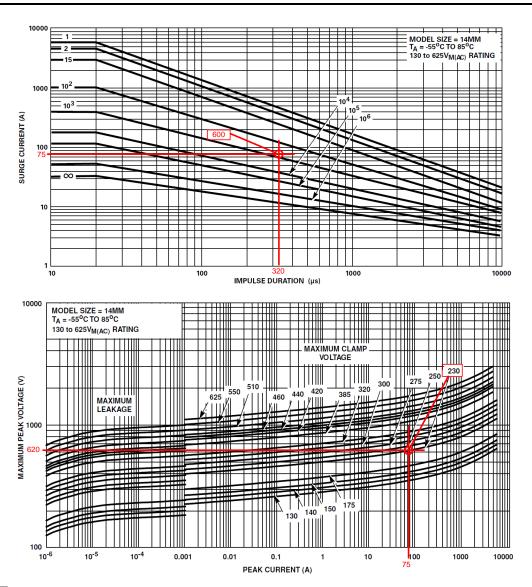

For this example, use the current levels for the two-line differential mode (DM), four-wire CDN shown in  $\gtrsim$  3. The Littelfuse UltraMOV® Varistor Series was chosen based on availability and because of the detailed repetitive surge capability curves within the device data sheet. The standard value for the 230-V<sub>RMS</sub> rating was chosen (VxxE230P, where xx = disc diameter). The selection process continues by using the repetitive surge curves provided for each MOV size. The repetitive surge curves indicate the maximum current versus the pulse-width rating of the MOV based on the number of expected surge pulses.

表 3. Maximum Configuration—Two Center-Tap Currents: 10/700 and 1.2/50 Waveforms

| VPOC (V) | 4-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) | 8-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) |

|----------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| 500      | 6.25                     | 3.13                     | 6.25                     | 3.76                     | 1.88                     | 3.76                     |

## 表 3. Maximum Configuration—Two Center-Tap Currents: 10/700 and 1.2/50 Waveforms (continued)

| VPOC (V) | 4-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) | 8-LINE<br>CMIPCT-PSC (A) | 1-LINE<br>DMIPCT-PSC (A) | 2-LINE<br>DMIPCT-PSC (A) |

|----------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|

| 1000     | 12.50                    | 6.25                     | 12.50                    | 7.52                     | 3.76                     | 7.52                     |

| 1500     | 18.75                    | 9.38                     | 18.75                    | 11.28                    | 5.64                     | 11.28                    |

| 2000     | 25.00                    | 12.50                    | 25.00                    | 15.04                    | 7.52                     | 15.04                    |

| 4000     | 50.00                    | 25.00                    | 50.00                    | 30.08                    | 15.04                    | 30.08                    |

| 6000     | 75.00                    | 37.50                    | 75.00                    | 37.50                    | 18.75                    | 37.50                    |

For the IEC 61000-4-5:2005 test, the MOV must be able to survive ten surge pulses with each current surge having an equivalent rectangular pulse width of 320  $\mu$ s, which is based on the 320- $\mu$ s time to half value associated with the 10/700- $\mu$ s to 5/320- $\mu$ s combination wave.

The Littlefuse V14E230P, V10E230P, and V07E230P were selected for port 1 (75 A), port 2 (50 A), and port 3 (25 A), respectively. For port 1, use a 320- $\mu$ s impulse duration and 75-A surge current (see  $\boxtimes$  6) to obtain approximately 600 repetitions. This configuration provides additional lifetime margin for extended testing and higher current levels such as the values in  $\equiv$  3. If the V10E230P MOV is used at a 320- $\mu$ s impulse duration and 75-A surge current, the number of repetitions drops to approximately 30.

図 6. Using MOV Repetitive Surge Capability and Maximum Clamping Voltage Curves

To finish the design for port 2 and port 3, see the Littelfuse data sheet for V10E230P and V07E230P. For port 2, at a 320- $\mu$ s impulse duration and 50-A surge current, there are approximately 100 repetitions. For port 3 (25 A), there are 300 repetitions. The surge voltage at port 2 (50 A) and port 3 (25 A) is 640 V and 630 V, respectively.

If the current waveform of the 1.2/50- $\mu$ s to 8/20- $\mu$ s combination wave generator sets the PSE surge requirement, the MOV surge current requirement is reduced by approximately ten times. This requirement can reduce the amount of PCB area and the cost associated with the larger MOVs.

## 3 Hardware, Software, Testing Requirements, and Test Results

## 3.1 Required Hardware and Software

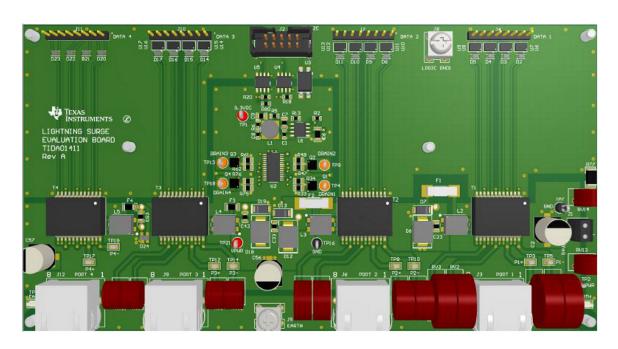

This section covers an overview of the TIDA-01411 design board and all the test connections required to evaluate the reference board.

#### 3.1.1 Hardware

To evaluate the lighting surge for PSE devices, the designer must first set up the complete system solution.

| ITEM                            | COMMENTS                                         | PART NUMBER    |

|---------------------------------|--------------------------------------------------|----------------|

| Lighting surge evaluation board | Four-port IEEE 802.3at compliant PSE TPS23861    | PR2189E1       |

| PD controller                   | Must be IEEE 802.3at compliant                   | TPS2378EVM-105 |

| USB TO GPIO                     | Connect USB port of PC to JTAG port of PSE board | _              |

| Two CAT5 Ethernet cables        | Both < 100 m in length                           | _              |

| Power supply                    | Supply 54 V to PSE                               | _              |

| CDN-UTP                         | Coupling and decoupling network for test         | EMC PARTNER    |

| Transient 2000                  | SURGE generator                                  | EMC PARTNER    |

| PC with USB port                | Control PSE through GUI                          | _              |

#### 3.1.2 Software

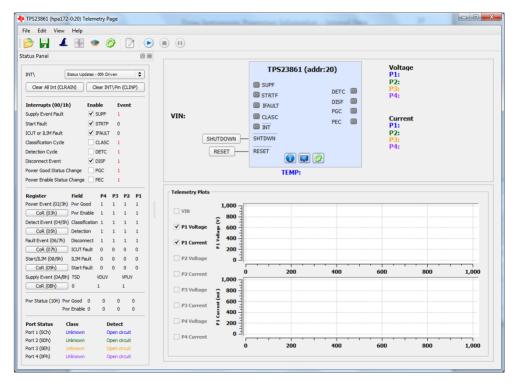

The Texas Instruments PI Commander graphical user interface (GUI) can be used with this reference design to provide real-time feedback on port telemetry and also control advanced PSE settings. Download PI Commander (PI Commander - TPS23861- setup.exe) from the TPS23861 product page: Software Section. For more information on how to connect and communicate with the TIDA-01411 design, see the section regarding TPS23891EVM-612 PI Commander GUI Setup in TPS23861EVM-612 Auto-Mode Evaluation Module for TPS23861.

図 7. TPS23861EVM GUI

# 3.2 Testing and Results

#### 3.2.1 Test Setup

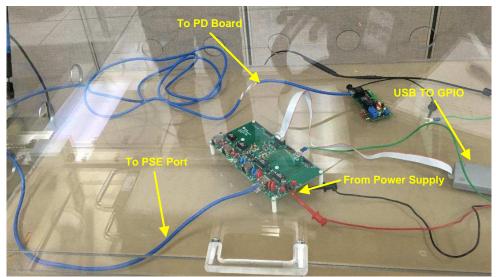

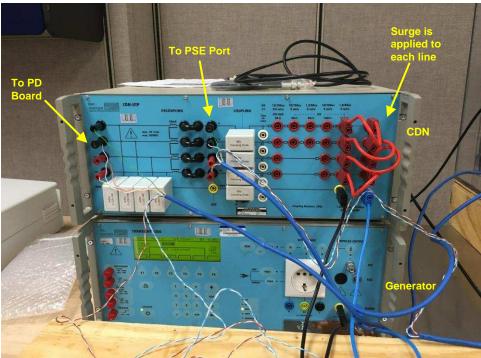

☑ 8 shows a photo of the entire test system. The first step is to connect the USB-to-GPIO from the JTAG port of the PSE evaluation board to the USB port of the computer. Then connect the 54-V power supply and make sure that it is OFF before testing. Next, use a CAT5 Ethernet wire to connect from the PSE port to the coupling side of CDN-UTP and connect the PD to the decoupling side of CDN-UTP. The following step is to connect the surge generator output of the Transient 2000 to the CDN and apply surge to each line. After these steps, the user can begin lighting surge testing with a power on and configuration of the PSE.

図 8. PSE Surge Test Setup

#### 3.2.2 **Test Results**

#### 3.2.2.1 Common Mode

表 4. Common Mode: 1.2/50-µs Waveform Test Results

| PORT  | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|-------|------------------|--------------|-----------------|---------|

| 1 (1) | Open circuit     | Unknown      | ±6 kV 1.2/50 μs | Pass    |

| 2     | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

Surges applied to pair 1 and 2 followed by pair 3 and 6 using the surge generator in series with a  $42-\Omega$  resistor. Port tested is in forced ON state with DC disconnect disabled.

## 表 4. Common Mode: 1.2/50-µs Waveform Test Results (continued)

| PORT | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------|------------------|--------------|-----------------|---------|

| 3    | Resistance valid | Class 4      | ±2 kV 1.2/50 μs | Pass    |

| 4    | Resistance valid | Class 4      | ±1 kV 1.2/50 μs | Pass    |

## 表 5. Common Mode: 10/700-µs Waveform Test Results

| PORT             | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------------------|------------------|--------------|-----------------|---------|

| 1 (1)            | Open circuit     | unknown      | ±6 kV 10/700 μs | Pass    |

| 2 <sup>(1)</sup> | Open circuit     | unknown      | ±4 kV 10/700 μs | Pass    |

| 3 <sup>(1)</sup> | Open circuit     | unknown      | ±2 kV 10/700 μs | Pass    |

| 4 <sup>(1)</sup> | Open circuit     | unknown      | ±1 kV 10/700 μs | Pass    |

Surges applied to pair 1 and 2 followed by pair 3 and 6 using the surge generator in series with a 40-Ω resistor. Port tested is in forced ON state with DC disconnect disabled.

## 3.2.2.2 Differential Mode (Single-Wire Differential)

## 表 6. Single-Wire Differential Mode: 1.2/50-µs Waveform Test Results

| PORT             | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------------------|------------------|--------------|-----------------|---------|

| 1 <sup>(1)</sup> | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

| 2                | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

| 3                | Resistance valid | Class 4      | ±2 kV 1.2/50 μs | Pass    |

| 4                | Resistance valid | Class 4      | ±1 kV 1.2/50 μs | Pass    |

<sup>(1)</sup> The surge generator used during testing had a ±4-kV maximum capability.

## 3.2.2.3 Differential Mode (Single-Pair Differential)

## 表 7. Single-Pair Differential Mode: 1.2/50-µs Waveform Test Results

| PORT             | DETECTION STATUS | CLASS STATUS | SURGE WAVEFORM  | PORT ON |

|------------------|------------------|--------------|-----------------|---------|

| 1 <sup>(1)</sup> | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

| 2                | Resistance valid | Class 4      | ±4 kV 1.2/50 μs | Pass    |

| 3                | Resistance valid | Class 4      | ±2 kV 1.2/50 μs | Pass    |

| 4                | Resistance valid | Class 4      | ±1 kV 1.2/50 μs | Pass    |

<sup>&</sup>lt;sup>(1)</sup> The surge generator used during testing had a ±4-kV maximum capability.

www.tij.co.jp Design Files

## 4 Design Files

#### 4.1 Schematics

To download the schematics, see the design files at TIDA-01411.

#### 4.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-01411.

## 4.3 PCB Layout Recommendations

- PCB spacings

- More than 80 mils from earth (and logic) ground ( > 4 kV based on 20 V/mil)

- More than 30 mils from Ethernet cable side nets (> 600 V)

- More than 20 mils from 54-V DC (VPWR) and port DRAINx nets

- Grounding

- System frame or earth ground-current shunting path for RJ45 housings

- PoE or 54-V DC power ground from DC power supply

- Logic or digital ground may be connected to earth ground through resistors

## 4.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-01411.

## 4.4 Altium Project

To download the Altium project files, see the design files at TIDA-01411.

### 4.5 Gerber Files

To download the Gerber files, see the design files at TIDA-01411.

#### 4.6 Assembly Drawings

To download the assembly drawings, see the design files at TIDA-01411.

#### 5 Software Files

To download the software files, see the design files at TIDA-01411.

#### 6 Related Documentation

- 1. Texas Instruments, Lightning Surge Considerations for PoE Power Sourcing Equipment Devices

- 2. Texas Instruments, Electrical Transient Immunity for Power-Over-Ethernet

- 3. Texas Instruments, TPS23861EVM-612: Auto-Mode Evaluation Module for TPS23861

- 4. Texas Instruments, TPS2378 EVM User's Guide

## 6.1 商標

Bourns is a registered trademark of Bourns, Inc.. Littelfuse, UltraMOV are registered trademarks of Littelfuse, Inc.. すべての商標および登録商標はそれぞれの所有者に帰属します。

改訂履歷 www.tij.co.jp

## 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### TIの設計情報およびリソースに関する重要な注意事項

Texas Instruments Incorporated ("TI")の技術、アプリケーションその他設計に関する助言、サービスまたは情報は、TI製品を組み込んだアプリケーションを開発する設計者に役立つことを目的として提供するものです。これにはリファレンス設計や、評価モジュールに関係する資料が含まれますが、これらに限られません。以下、これらを総称して「TIリソース」と呼びます。いかなる方法であっても、TIリソースのいずれかをダウンロード、アクセス、または使用した場合、お客様(個人、または会社を代表している場合にはお客様の会社)は、これらのリソースをここに記載された目的にのみ使用し、この注意事項の条項に従うことに合意したものとします。

TIによるTIリソースの提供は、TI製品に対する該当の発行済み保証事項または免責事項を拡張またはいかなる形でも変更するものではなく、これらのTIリソースを提供することによって、TIにはいかなる追加義務も責任も発生しないものとします。TIは、自社のTIリソースに訂正、拡張、改良、およびその他の変更を加える権利を留保します。

お客様は、自らのアプリケーションの設計において、ご自身が独自に分析、評価、判断を行う責任がお客様にあり、お客様のアプリケーション(および、お客様のアプリケーションに使用されるすべてのTI製品)の安全性、および該当するすべての規制、法、その他適用される要件への遵守を保証するすべての責任をお客様のみが負うことを理解し、合意するものとします。お客様は、自身のアプリケーションに関して、(1) 故障による危険な結果を予測し、(2) 障害とその結果を監視し、および、(3) 損害を引き起こす障害の可能性を減らし、適切な対策を行う目的での、安全策を開発し実装するために必要な、すべての技術を保持していることを表明するものとします。お客様は、TI製品を含むアプリケーションを使用または配布する前に、それらのアプリケーション、およびアプリケーションに使用されているTI製品の機能性を完全にテストすることに合意するものとします。TIは、特定のTIリソース用に発行されたドキュメントで明示的に記載されているもの以外のテストを実行していません。

お客様は、個別のTIリソースにつき、当該TIリソースに記載されているTI製品を含むアプリケーションの開発に関連する目的でのみ、使用、コピー、変更することが許可されています。明示的または黙示的を問わず、禁反言の法理その他どのような理由でも、他のTIの知的所有権に対するその他のライセンスは付与されません。また、TIまたは他のいかなる第三者のテクノロジまたは知的所有権についても、いかなるライセンスも付与されるものではありません。付与されないものには、TI製品またはサービスが使用される組み合わせ、機械、プロセスに関連する特許権、著作権、回路配置利用権、その他の知的所有権が含まれますが、これらに限られません。第三者の製品やサービスに関する、またはそれらを参照する情報は、そのような製品またはサービスを利用するライセンスを構成するものではなく、それらに対する関係証または推奨を意味するものでもありません。TIリソースを使用するため、第三者の特許または他の知的所有権に基づく第三者からのライセンス、もしくは、TIの特許または他の知的所有権に基づくTIからのライセンスが必要な場合があります。

TIのリソースは、それに含まれるあらゆる欠陥も含めて、「現状のまま」提供されます。TIは、TIリソースまたはその仕様に関して、明示 的か暗黙的かにかかわらず、他のいかなる保証または表明も行いません。これには、正確性または完全性、権原、続発性の障害に関する保 証、および商品性、特定目的への適合性、第三者の知的所有権の非侵害に対する黙示の保証が含まれますが、これらに限られません。

TIは、いかなる苦情に対しても、お客様への弁護または補償を行う義務はなく、行わないものとします。これには、任意の製品の組み合わせに関連する、またはそれらに基づく侵害の請求も含まれますが、これらに限られず、またその事実についてTIリソースまたは他の場所に記載されているか否かを問わないものとします。いかなる場合も、TIリソースまたはその使用に関連して、またはそれらにより発生した、実際的、直接的、特別、付随的、間接的、懲罰的、偶発的、または、結果的な損害について、そのような損害の可能性についてTIが知らされていたかどうかにかかわらず、TIは責任を負わないものとします。

お客様は、この注意事項の条件および条項に従わなかったために発生した、いかなる損害、コスト、損失、責任からも、TIおよびその代表者を完全に免責するものとします。

この注意事項はTIリソースに適用されます。特定の種類の資料、TI製品、およびサービスの使用および購入については、追加条項が適用されます。これには、半導体製品(http://www.ti.com/sc/docs/stdterms.htm)、評価モジュール、およびサンプル(http://www.ti.com/sc/docs/sampterms.htm)についてのTIの標準条項が含まれますが、これらに限られません。

Copyright © 2018, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社