Design Guide: TIDA-050050

# YUV422、PMIC、FPD-Link III、POC を搭載した、車載用 1.3MP 低コスト・カメラ・モジュールのリファレンス・デザイン

# TEXAS INSTRUMENTS

# 概要

このカメラ・モジュール・リファレンス・デザインは、イメージ信号プロセッサ (ISP) を内蔵した 1.3 メガピクセル・イメージャと、12 ビット、100MHz の TI FPD-Link III シリアライザと組み合わせることで、車載運転支援システム (ADAS)での小型低コストのカメラのニーズに対応します。また、電源管理集積回路 (PMIC) により、超小型のフォームファクタで 2 つのデバイスに電力を供給できます。このデザインには、リモート車載用カメラ・モジュールをディスプレイやマシン・ビジョン処理システムに同軸ケーブルで接続し、データと電力の両方を伝送する、高速シリアル・インターフェイスが含まれています。このリファレンス・デザインが使用している FPD-Link III SerDes テクノロジーにより、1 本の同軸ケーブルを使用して、生または処理済みの 2MP ビデオ・データ、双方向の制御信号、同軸ケーブルを使用したPower Over Coax (POC)の伝送を実現できます。

### Resources

TIDA-050050 Design Folder

TPS650330-Q1 Product Folder

DS90UB933-Q1 Product Folder

Ask our TI E2E™ support experts

# 特長

- 1 枚の 18mm × 18mm PCB に統合型電源を搭載した省スペース設計

- 統合型 TPS650320-Q1 電源に 3 つの降圧コンバー タと LDO を内蔵し、高効率と低ノイズの電源生成を実 現

- P2P 互換電源により機能安全アプリケーションを実現

- DS90UB933-Q1 を使用して最大 1MP/60fps のカメ ラ・アプリケーションを実現

- Omnivision 製 1.3MP OX01F10 イメージ・センサにより、HDR YUV422、RGB888、RAW に対応

- デジタル・ビデオ、電力供給、制御、診断用に Rosenberger 製 FAKRA 同軸コネクタを 1 個実装

# アプリケーション

- 処理機能なしのカメラ・モジュール

- リア・カメラ

- サラウンド・ビュー・システムの ECU

System Description www.tij.co.jp

# 1 System Description

Many automotive applications require small form factors with reduced circuit area that enable compact and modular systems. As a result, most cameras along with electronic components must meet this minimal area constraint when designing ADAS camera applications. This reference design addresses these needs by including a 1-megapixel imager, 1.9 Gbps serializer, and a single Power Management IC, and all components contained within an area of an 18-mm × 18-mm circuit board. The only connection required by the system is a single  $50-\Omega$  coaxial cable.

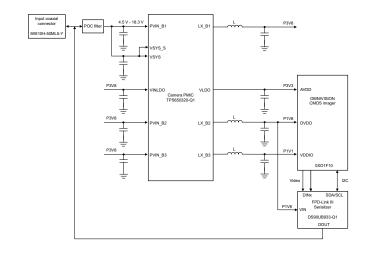

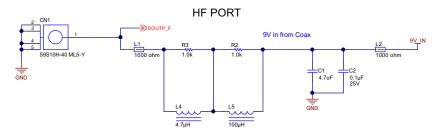

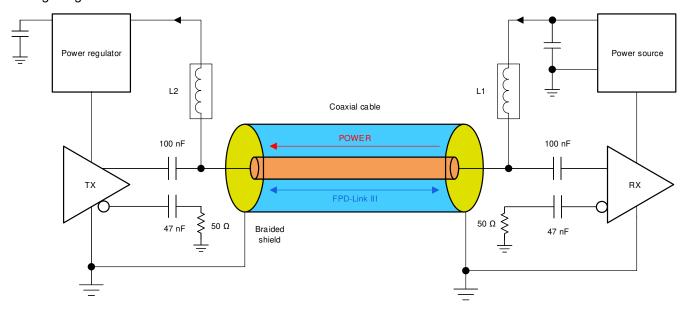

A combined signal containing the DC power, the FPD-Link front and back channels enter the board through the FAKRA coax connector. The filter in 🗵 1-1 blocks all of the high-speed content of the signal (without significant attenuation) while allowing the DC (power) portion of the signal to pass through inductor L5.

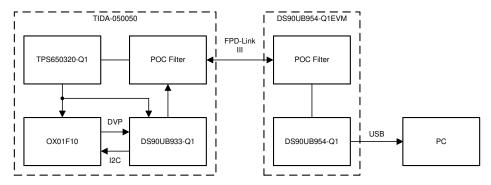

図 1-1. FPD-Link III Signal Path

The DC portion is connected to the buck 1 input of the TPS650320-Q1 Power Management IC. This voltage powers buck 2 and buck 3 of the device, which are responsible for creating the supply rails to the imager and serializer. The LDO input pin is supplied 3.8 V, which is responsible for providing a low-noise, 3.3-V analog supply to the imager. Buck 3 outputs the imager-dedicated 1.1-V and buck 2 generates a universal 1.8-V digital supply that is shared by both the imager and serializer. The high-frequency portion of the signal is connected directly to the serializer. This is the path that the video data and the control back channel takes between the serializer and deserializer.

The output of the imager is connected through a parallel digital video port (DVP) interface to the serializer. The serializer transmits this video data over a single LVDS pair to the deserializer located on the other end of the coax cable.

Additionally, on the same coax cable, there is a separate low-latency, bidirectional control channel that provides the additional function of transmitting control information from an I<sup>2</sup>C port. This control channel is independent of the video blanking period. It is used by the system microprocessor to configure and control the imager.

# 1.1 Key System Specifications

表 1-1. Key System Specifications

| 2 · · · · · · · · · · · · · · · · · · · |                         |                         |     |     |         |                 |

|-----------------------------------------|-------------------------|-------------------------|-----|-----|---------|-----------------|

|                                         | PARAMETER               | COMMENTS                | MIN | TYP | MAX     | UNIT            |

| V <sub>IN</sub>                         | Supply voltage          | Power over coax (POC)   | 4.5 | 9   | 18.3    | V               |

| P <sub>TOTAL</sub>                      | Total power consumption | V <sub>POC</sub> = 12 V | _   | 0.6 | 1       | W               |

| A <sub>PCB</sub>                        | PCB Area                |                         | _   | _   | 18 x 18 | mm <sup>2</sup> |

# 2 System Overview

# 2.1 Block Diagram

図 2-1. Camera Block Diagram

# 2.2 Design Considerations

The following subsections discuss the considerations behind the design of each subsection of the system.

## 2.2.1 PCB and Form Factor

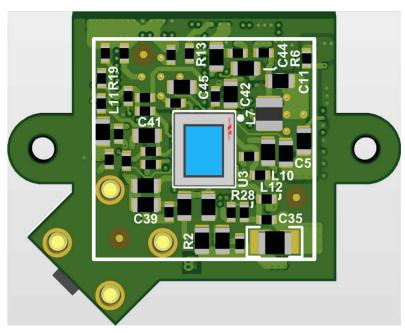

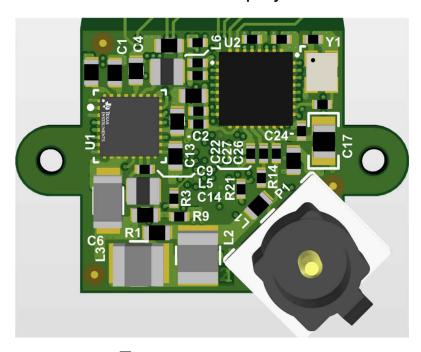

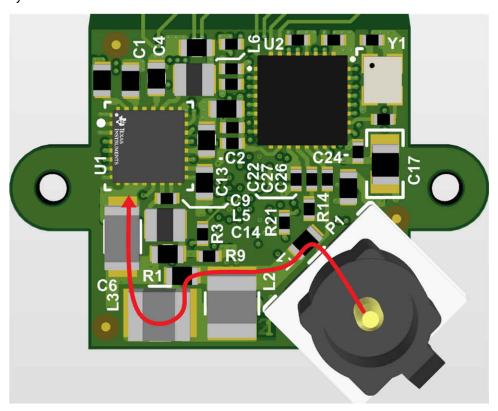

This reference design is not intended to fit any particular form factor; however, the goal of the design is to showcase a solution with minimal PCB area and compact design. The area of the board roughly equates to a dimension of 18 mm × 18 mm. The area near the board edge in ot in 2-2 is reserved for attaching the optics housing that holds the lens.

図 2-2. 3-D PCB Top Layer

図 2-3. 3-D PCB Bottom Layer

## 2.2.2 Power Supply Design

## 2.2.2.1 POC Filter

One of the most critical portions of a design that uses POC is the filter circuitry. The goal is twofold:

- 1. Deliver a clean DC supply to the input of the switching regulators.

- 2. Protect the FPD-Link communication channels from noise-coupled backwards from the rest of the system.

The DS90UB933-Q1 and DS90UB954-Q1 SerDes devices used in this system communicate over two carrier frequencies, 1 GHz at full speed ("forward channel") and a lower frequency of 2.5 MHz ("back channel") determined by the deserializer device. The filter must attenuate this rather large band spanning both carriers, hoping to pass only DC.

For the POC design, to enable the forward channel and back channel to pass uninterrupted over the coax, an impedance of 1 k $\Omega$  across the 1-MHz to 1-GHz bandwidth is required. Use two inductors: a 4.7- $\mu$ H inductor for high-frequency forward channel filtering, and a 100- $\mu$ H inductor for low-frequency back-channel filtering. For more details, see the *Sending Power Over Coax in DS90UB913A Designs* application report. In addition, a 1-k $\Omega$  resistor is placed in parallel with both of these inductors. A 1-k $\Omega$  ferrite bead is also placed in series for extra filtering at the forward channel data rate.

Lastly, in regards to filtering, ensuring that the FPD-Link signal is uninterrupted is just as important as providing a clean, noise-free DC supply to the system. To achieve this, AC coupling capacitors shown by the 0.1  $\mu$ F and 0.047  $\mu$ F are chosen to ensure the high-speed AC data signals are passed through but that the DC is blocked from getting on the data lines.

図 2-4. Power Over Coax

## 2.2.2.2 Power Supply Considerations

Because this reference design is targeted at automotive applications, there are several considerations that limit design choices. Additionally, the following list of system-level specifications helped shape the final overall design:

- The total solution size must be minimized to meet the size requirement of this design, which is equivalent to 18 mm × 18 mm. This means choosing parts that integrate FETs, diodes, compensation networks, and feedback resistor dividers to eliminate the need for external circuitry.

- To avoid interference with the AM radio band, all switching frequencies must be greater than 1700 kHz or lower than 540 kHz. Lower switching frequencies are less desirable in this case because they require large inductors and can still produce harmonics in the AM band. For this reason, this reference design looks at higher frequency switchers.

- All devices must be AEC Q100 (-Q1) rated.

System Overview www.tij.co.jp

Before parts are chosen, the input voltage range, required voltage rails, and required current per rail must be known. In this case, the input voltage is a pre-regulated 9-V supply coming in over the coaxial cable. This system has only two main devices, the imager and serializer, which are responsible for power consumption during operation. 表 2-1 shows the requirements of the supplies:

| 表 2-1. | System | Power | <b>Budget</b> |

|--------|--------|-------|---------------|

|--------|--------|-------|---------------|

| PARAMETER  | VOLTAGE (V) | CURRENT (mA) | POWER (mW) |  |

|------------|-------------|--------------|------------|--|

| DS90UB933  |             |              |            |  |

| VDD        | 1.8         | 98           | 176        |  |

| OX01F10    |             |              |            |  |

| VDD-D      | 1.1         | 170          | 187        |  |

| VDD-IO     | 1.8         | 21           | 38         |  |

| VDD-A      | 3.3         | 33           | 109        |  |

| Oscillator |             |              |            |  |

| VDD        | 1.8         | 3            | 5          |  |

| Total      |             |              |            |  |

| VDD-D      | 1.1         | 170          | 187        |  |

| VDD-IO     | 1.8         | 122          | 220        |  |

| VDD-A      | 3.3         | 33           | 109        |  |

The9-V supply over the coaxial cable is first stepped down to 3.8 V, which then supplies the rest of the system on the camera module. In this design, the 1.8-V rail supplies both the DS90UB933 supply, and the interface supply of the OX01F10 imager. The OX01F10 3.3-V analog rail requires 33 mA, the DS90UB933 serializer 1.8-V rail requires 98 mA, and the OX01F10 digital 1.1-V rail requires 170 mA.

Assuming 85% efficiency to simplify calculations with the previous values, it is calculated that the 3.8-V supply will require 160 mA to successfully power the 1.1-V, 1.8-V, and 3.3-V rails. Because the input and output voltages, output current requirements, and total wattage consumption are known, calculate the input current using  $\pm$  1:

$$\begin{split} P_{IN} &= V_{IN} \times I_{IN} = \frac{P_{OUT}}{\eta_{SYSTEM}} = \frac{\frac{P_{OUT2}}{\eta_2} + \frac{P_{OUT3}}{\eta_3} + \frac{P_{LDO}}{\eta_{LDO}}}{\eta_1} \\ &\therefore I_{IN} &= \frac{\frac{187 \text{ mW}}{85 \%} + \frac{220 \text{ mW}}{85 \%} + \frac{109 \text{ mW}}{87 \%}}{9 \text{ V} \times 85 \%} = 79.0 \text{ mA} \end{split}$$

This information provides a strong foundation in the selection of power topologies and inductive passives that are explained in later sections.

Due to the requirement of Q100, it is mandatory that the switching frequency is rated outside of the AM band and must satisfy the voltage and current requirements derived previously. As the input voltage is a regulated voltage that will always be greater than any of the power rails produced, the power topologies selected should either be step-down converters (bucks) or LDOs. Bucks are generally included in supplies where switching noise is not a significant concern, and power savings is the largest care about. Conversely, LDOs can be incorporated in establishing low-noise analog supplies that reduce inherent noise and are more robust against EMI interactions; however, this is at the expense of larger current consumption.

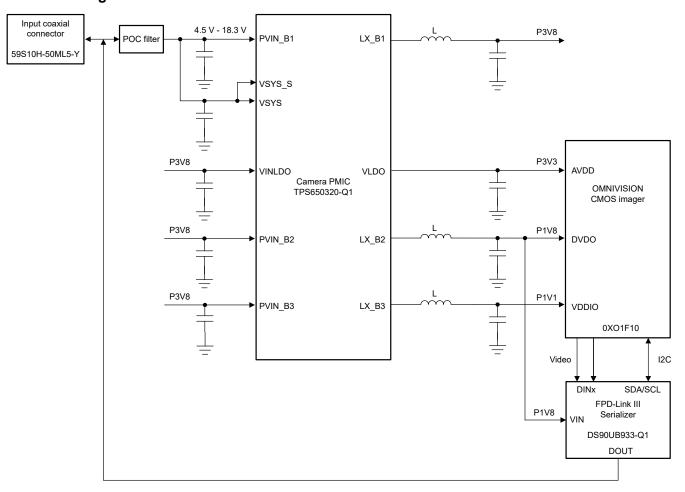

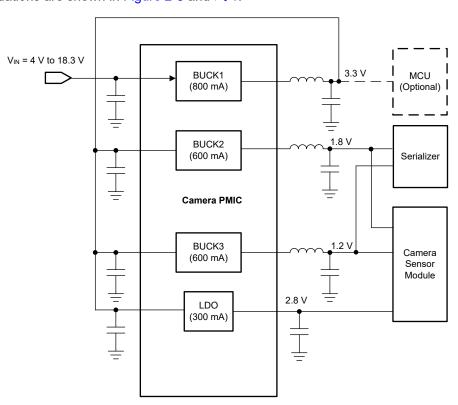

In this design, a single Power Management IC is responsible for powering the supply rails. This device, the TPS650320-Q1, was chosen as it incorporates three step-down converters (BUCKS) and an LDO in a single 4.0-mm x 4.0-mm VQFN package. The current requirements of the design also played an important role in the selection of the device, as the secondary BUCKS are capable of providing 600 mA, while the LDO is capable of supplying a maximum current output of 300 mA. BUCK1 steps down the 9-V POC input to 3.8 V. The 3.8-V rail then supplies power to BUCK2, BUCK3, and the LDO input. BUCK 2 provides the interface and digital supply for both the OX01F10 imager and DS90UB933 serializer, while the LDO output creates a clean, low-noise supply for the 3.3-V analog supply for the OX01F10.

## 2.2.2.1 Choosing External Components

For simplicity, the efficiency of the buck regulators is assumed to be 85% for these operating conditions, and the efficiency of the LDO is given by  $\pm 2$ .

$$\eta_{\rm LDO} = \frac{V_{\rm OUT}}{V_{\rm IN}} \tag{2}$$

System and Buck 1 currents calculated assuming 85% switching regulator efficiency are given in 式 1.

表 2-2 shows the load capability of each regulator compared to the requirements of the camera module. The TPS650320-Q1 device is capable of supplying the system power with plenty of margin to account for variations between typical and maximum current variation.

| 表 2-2. Regulator Load Capability | 表 2-2. Regulato | or Load C | apability |

|----------------------------------|-----------------|-----------|-----------|

|----------------------------------|-----------------|-----------|-----------|

| REGULATOR | OUTPUT VOLTAGE (V) | MAX CURRENT (mA) | REQUIRED CURRENT (mA) |

|-----------|--------------------|------------------|-----------------------|

| Buck 1    | 3.8                | 800              | 160                   |

| Buck 2    | 1.8                | 600              | 122                   |

| Buck 3    | 1.1                | 600              | 170                   |

| LDO       | 3.3                | 300              | 33                    |

After determining that the TPS650320-Q1 device is suitable based on the power requirements, the external components can be chosen quickly based on the data sheet recommendations, simplifying the design process. These recommendations are shown in Figure 2-5 and 式 1.

図 2-5. TPS650320-Q1 Typical Application Circuit

| 表 2-3. TPS650330-Q1 Recommended Components | 表 2-3. | TPS650330-Q1 | Recommended | Components |

|--------------------------------------------|--------|--------------|-------------|------------|

|--------------------------------------------|--------|--------------|-------------|------------|

| COMPONENT                | DESCRIPTION                | VALUE | UNIT |

|--------------------------|----------------------------|-------|------|

| C <sub>VSYS,VSYS_S</sub> | VSYS and VSYS_S decoupling | 10    | μF   |

| C <sub>PVIN_B1</sub>     | Buck 1 input capacitor     | 10    | μF   |

| L <sub>SW_B1</sub>       | Buck 1 inductor            | 2.2   | μH   |

| C <sub>OUT_B1</sub>      | Buck 1 output capacitor    | 10    | μF   |

| C <sub>PVIN_B2</sub>     | Buck 2 input capacitor     | 10    | μF   |

| L <sub>SW_B2</sub>       | Buck 2 inductor            | 1.0   | μH   |

| C <sub>OUT_B2</sub>      | Buck 2 output capacitor    | 10    | μF   |

| C <sub>PVIN_B3</sub>     | Buck 3 input capacitor     | 10    | μF   |

| L <sub>SW_B3</sub>       | Buck 3 inductor            | 1.0   | μH   |

| C <sub>OUT_B3</sub>      | Buck 3 output capacitor    | 10    | μF   |

| C <sub>PVIN_LDO</sub>    | LDO input capacitor        | 1.0   | μF   |

| C <sub>OUT_LDO</sub>     | LDO output capacitor       | 2.2   | μF   |

The high, fixed PWM 2.3-MHz switching frequency enables the use of small inductors with a fast transient response. A value of 2.2 µH is typically recommended for the BUCK1 channel output. This value helps to minimize the inductor ripple current.

With the inductance value chosen, the design now needs an inductor with a proper saturation current. This is the combination of the steady-state supply current as well as the inductor ripple current. The current rating needs to be sufficiently high but minimized as much as possible to reduce the physical size of the inductor. Calculate inductor ripple with 式 3:

$$\Delta I_{L(max)} = V_{OUT} \times \left( \frac{1 - \frac{V_{OUT}}{V_{IN(max)}}}{L(min) \times f_{SW}} \right)$$

(3)

#### where:

- I<sub>L</sub>(max) is the maximum inductor current

- Δl<sub>L</sub> is the peak-to-peak inductor ripple current

- L<sub>(min)</sub> is the minimum effective inductor value

- f<sub>SW</sub> is the actual PWM switching frequency

The parameters for this reference design using the TPS650330-Q1 are:

- $V_{OUT} = 3.3 V$

- $V_{IN(max)} = 18.3 V$

- L<sub>(min)</sub> = 2.2 μH

f<sub>SW</sub> = 2.3 MHz

These parameters yield an inductor current of  $\Delta I_L$  = 535 mA. The maximum current draw of the system through this regulator is 327 mA. The minimum saturation current is calculated as:

$$L_{SAT} \ge I_{OUT(MAX)} + \frac{\Delta I_{L(MAX)}}{2} = 327 \text{ mA} + \frac{535 \text{ mA}}{2} = 594 \text{ mA}$$

(4)

The TPS650330-Q1 device on this design uses a Murata® LQM2MPN2R2NG0, which has a rated current of 1.2 A and a DC resistance maximum of 138 mΩ. Additionally, this device has an operating temperature from -55°C to 125°C and comes in a very small 2-mm × 1.6-mm package.

#### 2.2.2.2 Choosing the Buck 1 Inductor

With an inductance value of 2.2  $\mu$ H selected, the minimum inductor saturation current must be derived to choose an appropriate inductor for the design. This is the combination of the steady-state supply current as well as the inductor ripple current. To ensure flexibility of the power and serializer base board to higher power image sensors, the inductor is chosen based on each maximum rated output current of the regulator.  $\sharp$  5 calculates inductor ripple current:

$$\Delta I_{L(max)} = V_{OUT} \times \left( \frac{1 - \frac{V_{OUT}}{V_{IN(max)}}}{L_{(min)} \times f_{sw}} \right)$$

(5)

where

- ΔI<sub>L(max)</sub> is the maximum peak-to-peak inductor ripple current

- L<sub>(min)</sub> is the minimum effective inductor value

- f<sub>sw</sub> is the actual PWM switching frequency

The parameters for Buck 1 of this reference design are:

- V<sub>OUT</sub> = 3.8 V

- $V_{IN(max)} = 18.3 V$

- $L_{(min)} = 2.2 \mu H$

- $f_{sw} = 2.3 \text{ MHz}$

These parameters yield an inductor ripple current of  $\Delta I_L$  = 595 mA. Assuming a maximum load current of 800 mA, use  $\pm$  6 to calculate a minimum saturation current of 1100 mA.

$$L_{SAT} \ge I_{OUT, (MAX)} + \frac{\Delta I_{L(MAX)}}{2} \tag{6}$$

The TPS650330-Q1 device on this design uses a TDK® TFM201610ALMA2R2MTAA, which has a rated current of 2 A and a DC resistance maximum of 152 m $\Omega$ . Additionally, this inductor has an operating temperature from – 55°C to 150°C in a very small 2.0-mm × 1.6-mm package.

#### 2.2.2.3 Choosing the Buck 2 and Buck 3 Inductors

Buck 2 and Buck 3 have a recommended inductor value of 1.0  $\mu$ H. When selecting a component, it is important to verify the DC resistance and saturation current. The DC resistance of the inductance influences the efficiency of the converter directly – lower DC resistance is directly proportional to efficiency. The saturation requirement of the inductor is determined by combining the steady-state supply current and the inductor ripple current. The current rating needs to be sufficiently high but minimized as much as possible to reduce the physical size of the inductor. Calculate the inductor ripple current using  $\pm$  5.

The parameters for the Buck 2 1.8-V rail include:

- V<sub>OUT</sub> = 1.8 V

- V<sub>IN(max)</sub> = 3.8 V

- $L_{(min)} = 1.0 \mu H$

- $f_{sw} = 2.3 \text{ MHz}$

These parameters yield an inductor ripple current of  $\Delta I_L$  = 412 mA. Assuming a maximum load current of 600 mA,  $\gtrsim$  6 can be used to calculate a minimum saturation current of 810 mA.

The parameters for the Buck 3 1.2-V rail include:

- V<sub>OUT</sub> = 1.2 V

- V<sub>IN(max)</sub> = 3.8 V

- $L_{(min)} = 1.0 \mu H$

- $f_{sw} = 2.3 \text{ MHz}$

These parameters yield an inductor ripple current of  $\Delta I_L$  = 357 mA. Assuming a maximum load current of 600 mA,  $\gtrsim$  6 can be used to calculate a minimum saturation current of 780 mA.

System Overview

Buck 2 and Buck 3 of this design use the TDK® TFM201610ALMA1R0MTAA, which has a current rating of 3.1 A and a DC resistance of 60 m $\Omega$ . Additionally, this inductor has an operating temperature of –55°C to 150°C in a very small 2.0-mm × 1.6-mm package.

## 2.2.2.3 Functional Safety

The TPS650320-Q1 device has integrated supervisors in addition to temperature and current monitoring. The device is also pin-compatible with the TPS650331-Q1, TPS650332-Q1, and TPS650333-Q1, with only a single component change of the Buck 1 inductor to 1.5  $\mu$ H. Each of the TPS650331-Q1, TPS650332-Q1, and TPS650333-Q1 devices provides additional safety features as an ASIL-B safety elements out of context (SEooC), allowing the scalability of this design to camera applications with more stringent safety requirements.

# 2.3 Highlighted Products

This reference design uses the following TI products:

- DS90UB933-Q1: is the serializer portion of a chipset that offers an FPD-Link III interface with a high-speed

forward channel and a bidirectional control channel for data transmission over a single coaxial cable or

differential pair. This chipset incorporates differential signaling on both the high-speed forward channel and

bidirectional control channel data paths. The serializer-deserializer pair is targeted for connections between

imagers and video processors in an electronic control unit (ECU).

- TPS650320-Q1: an automotive qualified, four-channel PMIC optimized for camera applications. The device

integrates three buck converters and one LDO, along with overvoltage protection and undervoltage

supervisors on each voltage rail. A high, fixed PWM 2.3-MHz switching frequency enables the use of small

inductors with a fast transient response. The low-noise, high-PSRR LDO provides an output voltage option

for sensitive analog circuits. A wide range of output voltage and sequencing settings, along with other

operational settings, are programmable for compatibility with a variety of imagers without the need for any

additional components.

# 2.3.1 OX01F10 Imager

The OmniVision® OX01F10 is a diagonal 6.67-mm, 1/3.55" color CMOS image sensor with 1.36 effective megapixels. The sensor supports AD 10-bit, MIPI 2-lane, DVP, YUV422, RGB888, BT656, and RAW10 up to RAW24 HDR output. Other included features follow:

- Supports 1340 × 1020 resolution (1.3-MP) and any cropped size image sizes

- Integrated ISP with AEC, AGC, AWB, lens correction, defective pixel correction, HDR combination, tone mapping, and black level correction

- 50- and 60-Hz flicker cancellation

- Requires three voltage rails (3.3 V, 1.8 V, and 1.1 V)

- Can be configured using an I<sup>2</sup>C-compatible two-wire serial interface

## 2.3.2 DS90UB933-Q1

Using a serializer to combine 10-bit video with a bidirectional control signal onto one coax or twisted pair greatly simplifies system complexity, cost, and cabling requirements. The parallel video input of the DS90UB933-Q1 mates well with the 10-bit parallel video output of the OV10640 imager. Once combined with the filters for the POC, video, I2C, diagnostics, and power can all be transmitted up to 15 m on a single, inexpensive coax cable. For more information on the cable itself, see the *Cable Requirements for the DS90UB913A and DS90UB914A* application report.

#### 2.3.3 TPS650320-Q1

The TPS650320-Q1 device is a highly-integrated power management IC for automotive camera modules. This device combines three step down converters and one low-dropout (LDO) regulator. The BUCK1 step-down converter has an input voltage range up to 18.3 V for connections to Power over Coax (POC). All converters operate in a forced fixed-frequency PWM mode. The LDO can supply 300 mA and operate with an input voltage range from 3.0 V to 5.5 V. The step-down converters and the LDO have separate voltage inputs that enable maximum design and sequencing flexibility. Additionally, an integrated advanced Spread-Spectrum Clock (SSC) enables robust EMI performance. A small form-factor, added rail supervision features, and programmability make this device a very attractive candidate for designs that need to be expedited or scaled for future applications.

# 2.4 System Design Theory

The main design challenges to consider for automotive cameras are size, ease of use, and thermal efficiency. Automotive cameras are often placed in remote regions of the vehicle where area is limited, requiring an overall compact solution. Because of this, the system is designed around having the lowest number of components with a fully-integrated PMIC power solution. The ease of use and design flexibility offered by a PMIC solution is also critical to enable a single platform design and reduce development time as ADAS applications continue to grow. The DS90UB933-Q1 and TPS650320-Q1 additionally both provide compatibility with a wide range of imagers. The choice of a two-board solution highlights this capability, as the power and serializer base board can be reused with different imager boards depending on the camera application. Lastly, the small size and remote placement of these cameras increases their susceptibility to heat. A power-efficient system is crucial to preserve the image quality in these conditions. The TPS650320-Q1 device is optimized for efficiency with a three-buck and one-LDO regulator topology, enabling the support of medium- and high-quality imagers without sacrificing thermal performance. Due to the impact of thermals on the system performance, it is important to calculate total system efficiency as part of the design process. From the Buck 1 output power in 表 2-2, the TPS650320-Q1 efficiency is about 80%. Using this value, 式 3 calculates a system input power of about 760 mW. 式 7 can then be used with the output power of Buck 2, Buck 3, and the LDO to calculate the overall system efficiency.

$$\eta_{SYSTEM} = {}^{P}OUT/P_{IN} = ({}^{P}OUT, 2 + {}^{P}OUT, 1 + {}^{P}OUT, LDO)/P_{IN, 1} = 68\%$$

(7)

# 3 Hardware, Testing Requirements, and Test Results

# 3.1 Hardware Requirements

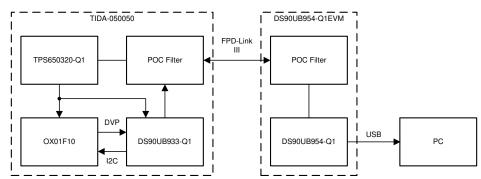

This reference design needs only one connection to a system with a compatible deserializer over the FAKRA connector as shown in  $\boxtimes$  3-1.

図 3-1. Getting Started With the Board

# 3.1.1 Hardware Setup

☑ 3-2 shows the setup to test the camera module reference design. This design includes an OX01F10 image sensor, which connects to the DS90UB933-Q1 serializer over CSI-2 and I<sup>2</sup>C interfaces. The DS90UB933-Q1 serializer then connects through POC to a DS90UB954-Q1 deserializer. Note that for test setup, only one channel is used from the DS90UB954-Q1 device. The Analog LaunchPad<sup>™</sup> GUI writes all the back channel I<sup>2</sup>C setting configurations for the IMX390, DS90UB933-Q1, and DS90UB954-Q1 devices.

図 3-2. Block Diagram of Test Setup

## 3.1.2 FPD-Link III I<sup>2</sup>C Initialization

With the setup in 🗵 3-2 connected, the DS90UB954-Q1 EVM is supplied 12-V input power, which is regulated to 9-V with an onboard LDO and delivered through POC to power the TIDA-050050 camera module. Once all rails are established, all devices (OX01F10, DS90UB933-Q1, and DS90UB954-Q1) receive power. Then, the I<sup>2</sup>C writes for initialization can begin. Note that the following writes are only showing one channel camera and may not be the mode wanted for specific multi-camera mode. The Analog LaunchPad compatible Python® script to initialize the DS90UB954-Q1 deserializer and DS90UB933-Q1 serializer are as follows:

```

# Set up Port1

board.WriteI2C(UB954, 0x4C, 0x12)

# Set up Back Channel Config (0x58)

board.WriteI2C(UB954,0x58,0x58)

# Set up SER Alias ID

board.WriteI2C(UB954,0x5C,UB933)

# Set up Slave/Camera ID

board.WriteI2C(UB954,0x5D,SensorID)

# Set up Slave/Camera Alias ID

board.WriteI2C(UB954,0x65,Sensor)

# Set GPIO2 output high, where GPIO2 = XSHUTDOWN

board.WriteI2C(UB933,0x0D,0x95)

```

#### 3.1.3 OX01F10 Initialization

Once the FPD-Link III setup is done for the DS90UB933-Q1 and DS90UB954-Q1 devices, the I<sup>2</sup>C initialization can now be done on the OX01F10. For these writes, see the OX01F10 data sheet for register settings. There are many register settings listed to configure both the imager and ISP, but as long as the DS90UB933-Q1 and DS90UB954-Q1 FPD-Link III parts are configured, the I<sup>2</sup>C back channel allows for the OX01F10 to be accessed at address 0x6C. For this testing, the OX01F10 is configured for YUV422 DVP output at 1340 × 1020 resolution.

# 3.2 Test Setup

For the following tests to verify power supply and I<sup>2</sup>C communication, the camera is connected to the DS90UB954-Q1 EVM.

図 3-3. Block Diagram of Characterization Test Setup

## 3.2.1 Power Supplies Start Up

To verify the power supply sequencing and start-up behavior, each voltage rail output from the TPS650320-Q1 device is measured after applying power over coax to the system.

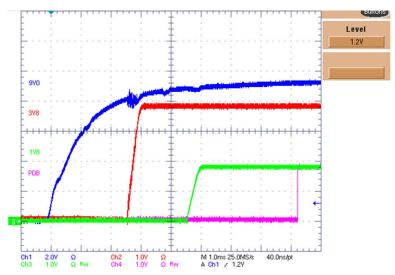

In this design, the PDB reset signal of the DS90UB933-Q1 device is connected directly to the nRSTOUT pin of the TPS650320-Q1 device. With the integrated sequencing capabilities of the PMIC, this ensures that the PDB reset line goes high after the 1.8-V supply is stable, eliminating the need for an external RC network.

## 3.2.2 Setup for Verifying I<sup>2</sup>C Communications

Back-channel I2C communications are verified with the DS90UB954-Q1 compatible GUI, Analog LaunchPad. The GUI is available for download here.

## 3.3 Test Results

The following sections show the test data from verifying the functionality of the camera design.

## 3.3.1 Power Supplies Start-Up

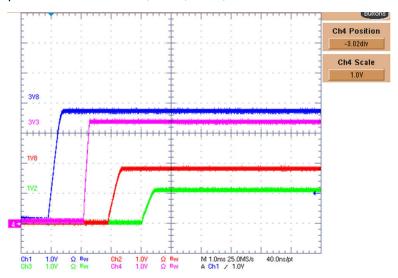

☑ 3-4 shows the start-up behavior for the 3.8-V, 1.8-V, 1.1-V, and 3.3-V rails.

(Channel 1): 3.3-V supply; (Channel 2): 2.9-V supply; (Channel 3): 1.2-V supply; (Channel 4): 1.8-V supply

図 3-4. Point-of-Load Power Supply Start-Up

# 3.3.2 Power Supply Start-Up—1.8-V Rail and PDB

To properly initialize, the PDB pin of the serializer remains low until all power supplies stabilize to their final voltages. 🗵 3-5 shows the power supply start up. Note that the PDB pin is directly connected to RSTOUT the of TPS650320-Q1 device and allows proper PDB synchronization after all rails are established.

(Channel 1): PDB; (Channel 2): 2.9-V supply; (Channel 3): 1.2-V supply; (Channel 4): 1.8-V supply

図 3-5. Serializer Power-Up Sequence

## 3.3.3 Power Supply Voltage Ripple

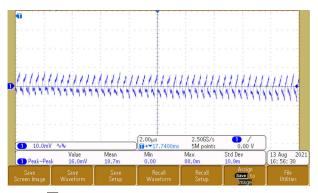

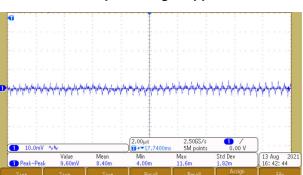

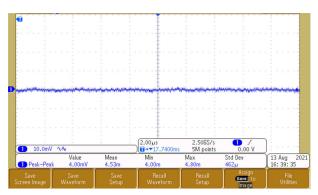

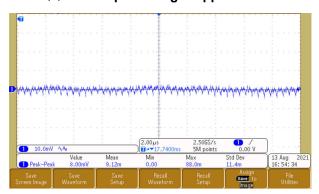

To achieve a quality output video stream, the output voltage ripple on the OX01F10 and DS90UB933-Q1 supplies must be low so that it does not affect the integrity of the high-speed data and internal PLL clocks. Measurements for 3.8-V, 3.3-V, 1.8-V, and 1.1-V rails are shown in ☑ 3-6, ☑ 3-7, and ☑ 3-8, respectively. The rails that impact imager performance are the 3.3-V and 1.1-V rails as they are responsible for providing a clean analog rail and digital supply. The 3.8-V rail powers the entire system and also has excellent ripple performance of 0.4%. As measured, the 3.3-V and 1.1-V rails have a ripple performance of 0.1% and 0.7%, respectively. The 1.8-V rail is significant to the serializer, because it supplies the VDD and VDD\_PLL rails. The 1.8-V rail has great voltage ripple performance at 0.5%. The voltage ripple on all rails is low enough for video output to be successfully transmitted.

図 3-6. Output Voltage Ripple - 3.8 V

図 3-8. Output Voltage Ripple - 1.8 V

図 3-7. Output Voltage Ripple - 3.3 V

図 3-9. Output Voltage Ripple - 1.1 V

## 3.3.4 Power Supply Load Currents

The last measurements to take in regard to the power supplies on the camera module are the load currents for the system supply, and the load currents on the OX01F10 imager. These measurements verify total power consumption of the camera module as well as the load current for each individual rail on the OX01F10 imager. For the following test data, each rail is drawing the specific load current outlined for the serializer and imager. All load current measurements are taken while a video output stream is present.

表 3-1 displays the currents measured through each supply voltage in this reference design. The 9-V load current is the total input load for the camera module and measures at 85 mA. The total power consumption corresponds to an overall system efficiency of 67%, close to the 68% value derived in セクション 2.4.

| 表 3-1. Measured | Supply ( | Currents |

|-----------------|----------|----------|

|                 |          |          |

| VOLTAGE RAIL | MEASURED CURRENT |

|--------------|------------------|

| 9.0 V        | 85 mA            |

| 3.8 V        | 153 mA           |

| 3.3 V        | 31 mA            |

| 1.8 V        | 130 mA           |

| 1.1 V        | 151 mA           |

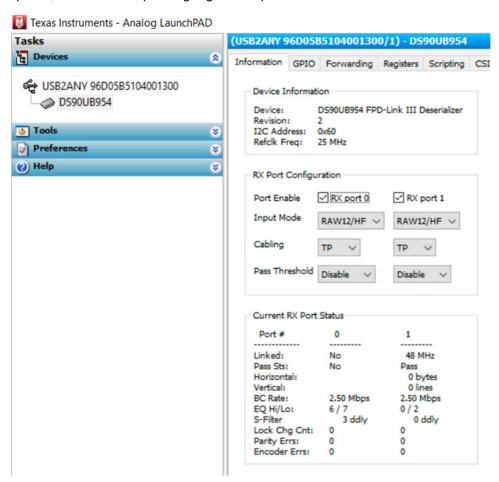

### 3.3.5 I<sup>2</sup>C Communications

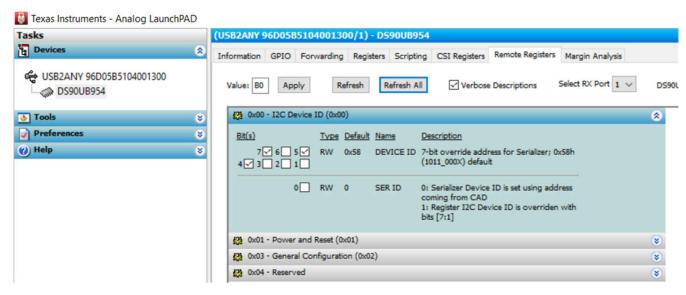

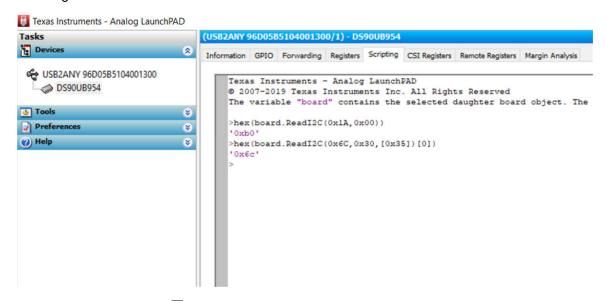

I2C communication between the DS90UB954-Q1 EVM and OX01F10 imager over the FPD-Link III back channel can be confirmed with the Analog LaunchPad GUI.  $\boxtimes$  3-10 and  $\boxtimes$  3-11 show the established link with the serializer on RX port 1, and the corresponding register map.

図 3-10. Analog LaunchPad™ Link Confirmation

図 3-11. Serializer Remote Registers

Read and writes to the imager, at slave alias address 0x6C (7-bit), are confirmed with the built-in Python scripting window of the Analog LaunchPad. Register 0x3035 reads data 0x6C, which is the expected default value for the register.

図 3-12. Back-Channel I2C Communication

# 4 Design and Documentation Support

## 4.1 Design Files

#### 4.1.1 Schematics

To download the schematics, see the design files at TIDA-050050.

# 4.1.2 Bill of Materials

To download the bill of materials (BOM), see the design files at TIDA-050050.

## 4.1.3 PCB Layout Recommendations

## 4.1.3.1 Layout Prints

To download the layer plots, see the design files at TIDA-050050.

## 4.1.3.2 PMIC Layout Recommendations

The PMIC portion of the layout requires careful consideration to minimize both PCB area and noise. As EMI is a critical concern in automotive systems, the TPS650330-Q1 device includes a spread spectrum feature to reduce conducted and radiated emissions, allowing more flexibility with placement and layout for space-constrained applications. However, it is still recommended to follow as many best practices as possible. This includes minimizing the area traveled by switching currents between buck regulator input capacitor, inductor, and output capacitor with tight component placement and minimal return path to the PMIC thermal pad.  $\boxtimes$  4-1 shows an example of this for buck 2.

For the LDO, separation of input and output capacitor ground planes will reduce noise coupling from the switching rails to the sensitive 3.3-V analog rail. To further reduce noise coupling, the dedicated AGND pin of the PMIC is connected to the ground plane on an internal layer with a via, rather than directly to the noisier thermal pad on the top layer.

図 4-1. PCB Layout With POC Routing

## 4.1.3.3 Serializer Layout Recommendations

Decoupling capacitors must be located very close to the supply pin on the serializer. Again, this requires consideration of the path of the supply current and the return current. Keeping the loop area of this connection small reduces the parasitic inductance associated with the connection of the capacitor. Due to space constraints, ideal placement is not always possible. For decoupling capacitors placed on the opposite layer of the serializer, minimize the return path to the serializer thermal pad. Place smaller value capacitors that provide higher frequency decoupling closest to the device.

For this application, a single-ended impedance of 50  $\Omega$  is required for the coax interconnect. Anti-pads are implemented in the ground plane under critical components such as the DOUT AC coupling capacitors to minimize impedance mismatch. Keep the coax connection to the serializer short.  $\boxtimes$  4-1 shows the routing of the high-speed serial line, highlighted by the yellow line. The total length of the yellow line is about  $\frac{1}{2}$  inch.

Lastly, minimize crosstalk between high-speed data lines by ensuring the high-speed data routing on adjacent layers do not overlap. If they must overlap due to space constraints, place a ground layer between the two

routing layers as a buffer. Keep high speed trace vias to a minimum. The vias must ideally be two or fewer to reduce stubs that cause reflections.

## 4.1.3.4 Imager Layout Recommendations

High-speed data routing must follow the same guidelines previously outlined for the serializer layout. Similarly, place the decoupling capacitors as close as possible to the supply pins, with smaller capacitors taking priority in terms of distance to the pin. Minimize the parasitic resistance and inductance to the ground plane with vias and wide traces. For some imagers, a separate analog ground (AGND) plane is recommended to reduce image noise. Connect imager AGND pins, AVDD decoupling capacitors, and the LDO output capacitor to this AGND plane, and connect the plane back to the main ground at a single point.

# 4.1.3.5 PCB Layer Stackup Recommendations

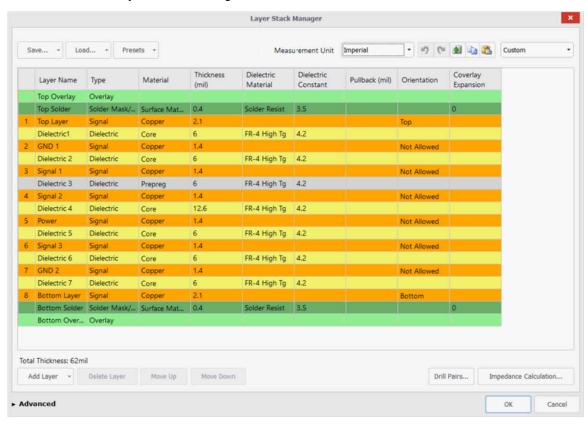

$\boxtimes$  4-2 shows the 8-layer stackup used for the PMIC and serializer board. Two signal layers are required due to the complex routing requirements introduced by the small size requirements of the PCB that must include I2C, logic IOs, clock, and control signals between the PMIC, serializer, and imager. The separation of the outer layers is selected to ensure a characteristic impedance of 50  $\Omega$ , ±10%

In this design, high current components are placed on both the top layer and the bottom layer, so Layer 2 and Layer 7 in the stackup are dedicated ground planes to minimize high current return paths. A separate AGND plane is also included on Layer 7 for the imager.

図 4-2. Layer Stackup

## 4.1.4 Altium Project

To download the Altium project files, see the design files at TIDA-050050.

### 4.1.5 Gerber Files

To download the Gerber files, see the design files at TIDA-050050.

## 5 Tools and Software

**Tools**

**Concise Description** Description

Software

**Concise Description** Description

# 6 Documentation Support

- 1. Texas Instruments, TPS650320-Q1 EVM user's guide

- Texas Instruments, DS90UB95x-Q1EVM Deserializer user's guide

- Texas Instruments, DS90UB933-Q1 FPD-Link III Serializer for 1-MP/60-fps Cameras 10/12 Bits,100 MHz data sheet

- 4. Texas Instruments, Sending Power Over Coax in DS90UB913A Designs application report

- 5. Texas Instruments, Camera PMIC Spin Selection Guide application report

# 7 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接 得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得るこ とができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するも のではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

## 8 Trademarks

TI E2E<sup>™</sup> and LaunchPad<sup>™</sup>, and are trademarks of Texas Instruments.

Murata® is a registered trademark of Murata Manufacturing Co., Ltd..

TDK® is a registered trademark of TDK Electronics AG.

OmniVision® is a registered trademark of Omnivision Technologies Inc..

Python® is a registered trademark of Python Software Foundation.

すべての商標は、それぞれの所有者に帰属します。

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022. Texas Instruments Incorporated