# Application Note

# Continuous Wave Doppler Signal Chain Designs for Ti's Ultrasound AFE

Zichen Liu and Hailey Chen

#### **ABSTRACT**

In Ultrasound scanners, there is only one set of transducers, which is used for transmit as well as receive function (one after the other, using T/R switch). This supports scanning of stationary objects inside body for example, tissues and bones. The blood is not stationary so continuous or simultaneous transmit and receive functions are must. For this, the same transducer is split in half and used as simultaneous transmit and receive. Continuous Wave (CW) Doppler is a mode of capturing the echo when transmit and receive functions are happening simultaneously. Based on Doppler effect, the velocity of the blood and other parameters can be calculated. The CW Doppler is a key function in mid-end to high-end ultrasound systems and it must handle high dynamic range along with strict phase noise performance. This application note highlights key challenges of CW Doppler path and proposes four solutions to achieve low-noise performance.

## **Table of Contents**

| 1 Introduction                  | 2     |

|---------------------------------|-------|

| 2 CWD Block Diagram and Designs | <br>2 |

|                                 |       |

|                                 |       |

|                                 |       |

| 2.4 Proposal 4                  | 7     |

| 3 Comparison of the Designs     | 8     |

|                                 |       |

|                                 |       |

## **Trademarks**

All trademarks are the property of their respective owners.

Introduction www.ti.com

## 1 Introduction

One of the most demanding clinical diagnostic tools employed in ultrasound systems is continuous-wave Doppler (CWD). Unfortunately, designing CWD system is not easy since the received CWD signal is a combination of strong signals from body tissue, commonly referred to as clutter and the much weaker Doppler signals from moving blood. The typical clutter signals on the input of a receive channel can be as large as 200mVpp, whereas the reflected Doppler signal is weak and has a small signal amplitude in uV to mV range. To receive CWD signals, a mixer is needed to demodulate CWD signals first and then demodulated CWD signals is summed from each received channel to enhance SNR. TI's AFE has integrated high performance mixer and summer in the chip. However, in actually design, there potential has 4 approximately 16 PCS AFE in a typical ultrasonic equipment. The designer has to summing the CWD signals external of AFE. So, designer has to design a summing circuit with low noise and high bandwidth. For simpler summing circuit, the full differential amplifier prefers to be used in here since the output CWD signals from AFE is a full differential signal. This is not straightforward for most designers. Quantization noise of ADC is another factor potential impact system performance since the weaker Doppler signals. With this said, this is challenged for a designer. This application note proposes four designs with different performance, size, and cost to meet customers miscellaneous requirements.

## 2 CWD Block Diagram and Designs

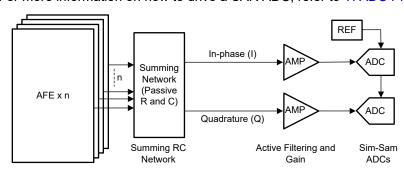

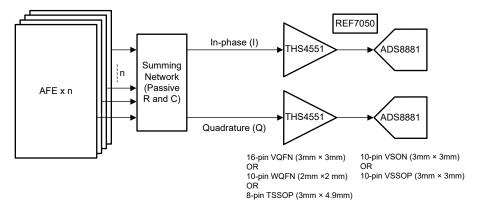

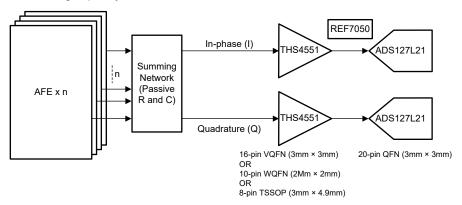

Figure 2-1 shows a typical CWD receive system. Four main components exist in the CWD receive signal chain. the four components include ultrasound receive AFEs, summing network, amplify and filtering and the sampling ADC. The summing network sums all the I and Q signals from the I and Q output channels respectively, then produces differential I and Q signals for analysis. The maximum signal frequency of I and Q signal can be in the range of 10kHz to 100kHz. The ADC used to digitize these signals can have sampling speed at least 10 times higher than the maximum input frequency. Besides, high-resolution of 16-bits or more is needed for precise measurement of blood speed. For better signal conditioning of input, a fully differential amplifier (FDA) is usually used to drive the ADC. High-speed and low-noise performance must be taken into consideration while selecting ADC driver amplifier. For more information on how to drive a SAR ADC, refer to TI ADC Precision Labs

Figure 2-1. CWD Block Diagram

Based on Figure 2-1, TI is currently providing four proposals.

## 2.1 Proposal 1

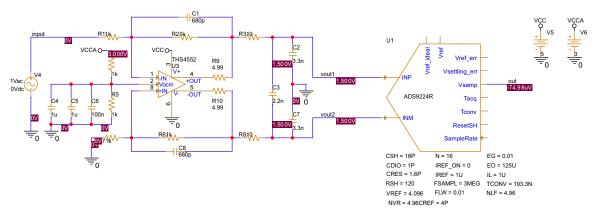

As shown in Figure 2-2, Proposal 1 adopts the THS4552 and ADS9224 as the CWD signal chain. The ADS9224 is TI's 16-bits ADC with internal reference and 3MSPS sample rate introduced in 2019. Because the CWD signal is divided into the In-phase signal and the Quadrature signal, this requires two amplifiers and two sampling ADCs, Regarding the ADS9224 and THS4552 both having dual channels, single ADS9224 and THS4552 can meet the CWD signal chain requirements, this proposal can be applicable for small size, cost-sensitive equipment such as hand-held or portable ultrasound with low dynamic range requirements, one benefits of this design is customer potential to implement an over-sampling to get better resolutions than 16-bits with low cost.

Figure 2-2. Proposal 1 ADS9224 and THS4552

Noise is one tough issue for electrical engineer. For CWD system, the situation is even worse since the reflect signals potential is very weak in a CWD system. Generally, the designer needs to evaluate the noise performance of circuit for CWD application. Figure 2-3 shows the circuit was simulated for evaluate noise performance of Proposal 1. In actual circuit design, there has several input signals with series resistor for add CWD signals from different AFEs. In the simulation, we use an equal resistor to replace these resistors. Figure 2-4 shows the frequency response and noise performance of Proposal 1 by simulation.

Figure 2-3. Proposal 1 Simulated Circuit

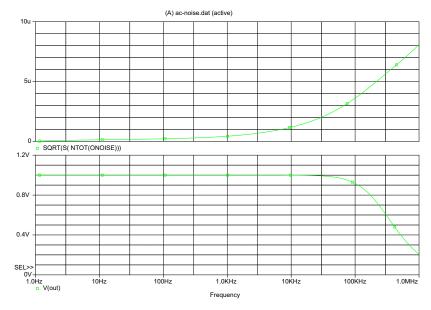

Proposal 1 noise and amplitude frequency characteristics.

Figure 2-4. Proposal 1 AC and Noise Performance

From the simulation result of Proposal 1, the total integrated noise within 1MHZ bandwidth is about 8.207uV.

## 2.2 Proposal 2

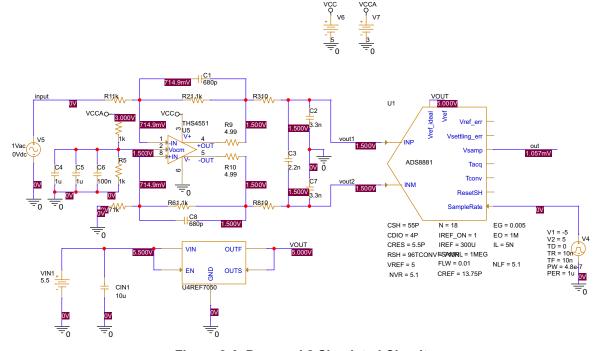

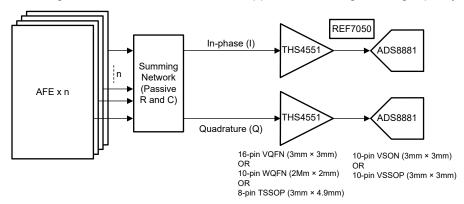

As shown in Figure 2-5, the Proposal 2 adopts the ADS8881 and THS4551 for the CWD signal chain, the ADS8881 with single-channel, 1-MSPS, 18-bits SAR ADC from TI in 2015, is now widely used in ultrasound CWD systems and is particularly designed for general ultrasound equipment. Because of the ADS8881 and THS4551 are both with single channel, so double ADS8881 and THS4551 are required to sample the CWD signals and since the ADS8881 does not have an internal reference. An additional reference source REF70 is used in this proposal, TI's ultra-low noise and ultra-low drift voltage reference source introduced in 2023.

Figure 2-5. Proposal 2 ADS8881 and THS4551

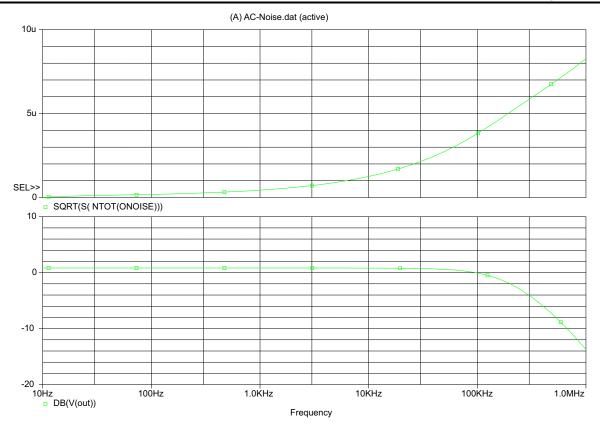

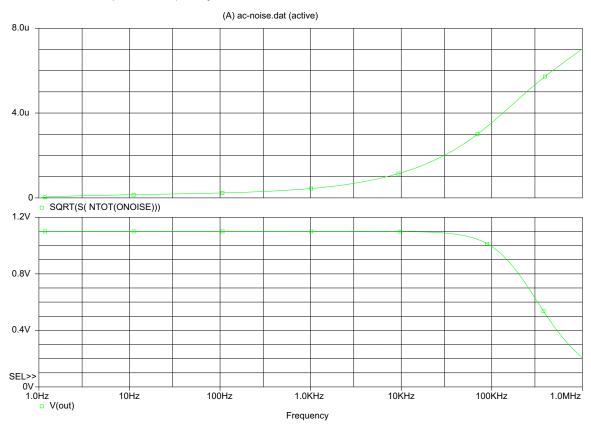

Figure 2-6 and Figure 2-7 show the circuit for simulation and simulation results. Simulation of the noise and amplitude frequency characteristics for Proposal 2.

Figure 2-6. Proposal 2 Simulated Circuit

Proposal 2 noise and amplitude frequency characteristics.

Figure 2-7. Proposal 2 AC and Noise Performance

As shown from the simulation results, the ADS8881 has an integral noise of 8.28uV in 1MHZ bandwidth, slightly exceeding the ADS9224, but due to the higher full-range input range, As a result, the overall SNR remains higher than the ADS9224R.

#### 2.3 Proposal 3

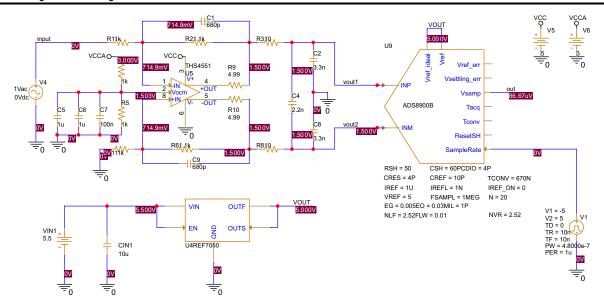

Shown in Figure 2-8, the ADS8900B used in Proposal 3 is a 20 bits SAR ADC with 1 MSPS in TI introduced in 2017, and since the ADS8900B does not have an internal reference, the REF70 is also required as an external reference. The proposal has the highest quality signal-to-noise ratio and dynamic range among the SAR ADC proposals. Designed for high-end ultrasound device CWD applications for higher image quality.

Figure 2-8. Proposal 3 ADS8900B and THS4551

Simulation of noise and amplitude frequency characteristics for Proposal 3.

Figure 2-9. Proposal 3 Simulated Circuit

## Proposal 3 noise and amplitude frequency characteristics

Figure 2-10. Proposal-3 AC and Noise Performance

As shown from the simulation results of the Proposal 3, the Proposal 3 has the lowest total integral noise, highest signal-to-noise ratio and dynamic range among all of the SAR ADC proposals.

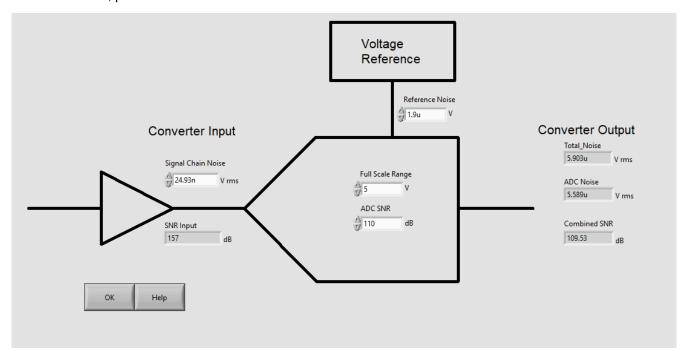

#### 2.4 Proposal 4

Figure 2-11 shows, the ADS127L21 used in Proposal 4 is a 24 bits Delta-Sigma ADC with 1.365 MSPS in TI introduced in 2023, and since ADS127L21 does not have an internal reference, ADS127L21 also uses the REF70 as an external reference. This proposal has the highest quality signal-to-noise ratio and dynamic range based on the highest sample bits and over-sample technology. Designed for high-end ultrasound device CWD applications for the best image quality.

Figure 2-11. Proposal 4 ADS127L21 and THS4551

#### 1. Proposal 4 Noise Calculation

As shown from Figure 2-12, because the simulation models of the ADS127L21 has not released in TI.com, So we cannot do the simulation in PSPICE or TINA, but we can use the Analog engineer calculator to complete this. For more details, please refer to TI.com.

Figure 2-12. Proposal 4 Noise Performance

## 3 Comparison of the Designs

Table 3-1 shows the comparison results between previous said four proposals. Customer can select any proposal previously mentioned for special applications.

**Table 3-1. Proposals Comparison**

| Table 6-1. I Toposais Companson |                                                                                            |                                                                                             |                                                                                         |                                                                                            |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Scheme                          | Proposal 1                                                                                 | Proposal 2                                                                                  | Proposal 3                                                                              | Proposal 4                                                                                 |  |  |

| ADC device                      | ADS9224R × 1                                                                               | ADS8881 × 2                                                                                 | ADS8900B × 2                                                                            | ADS127L21×2                                                                                |  |  |

| ADC Resolution and Speed        | 16-Bits<br>3-MSPS                                                                          | 18-Bits<br>1-MSPS                                                                           | 20-Bits<br>1-MSPS                                                                       | 24-Bits<br>1.365-MSPS                                                                      |  |  |

| ADC supply                      | AVDD = 5V typical<br>(Range: 4.5V to 5.5V)<br>DVDD = 3.3V typical<br>(Range: 1.65V to 5.5V | AVDD = 3V typical<br>(Range: 2.7V to 3.6V)<br>DVDD = 1.8V typical<br>(Range: 1.65V to 3.6V) | AVDD = 5V typical<br>(Range: 3V to 5.5V)<br>DVDD = 3V typical<br>(Range: 1.65V to 5.5V) | AVDD = 5V typical<br>(Range: 2.85V to 5.5V)<br>DVDD = 3V typical<br>(Range: 1.65V to 5.5V) |  |  |

| REF Range                       | 4.096V                                                                                     | 2.5V to 5V                                                                                  | 2.5V to AVDD-0.3V                                                                       | AVDD                                                                                       |  |  |

| REF device                      | Internal                                                                                   | REF7050                                                                                     | REF7050                                                                                 | REF7050                                                                                    |  |  |

| Front-end op-amp                | THS4552                                                                                    | THS4551 × 2                                                                                 | THS4551 × 2                                                                             | THS4551 × 2                                                                                |  |  |

| Front-end op-amp supply         | 2.7V to 5.4V                                                                               | 2.7V to 5.4V                                                                                | 2.7V to 5.4V                                                                            | 2.7V to 5.4V                                                                               |  |  |

| ADC Size & Package              | 32-pin VQFN (5mmX5mm)                                                                      | 10-pin VSON<br>(3mmX3mm) OR<br>10-pin VSSOP<br>(3mmX3mm)                                    | 24-pin VQFN (4mmX4mm)                                                                   | 20-pin QFN (3mmX3mm)                                                                       |  |  |

| No. of active components        | 2                                                                                          | 5                                                                                           | 5                                                                                       | 5                                                                                          |  |  |

| SNR (from data sheet)           | 94dB                                                                                       | 100dB                                                                                       | 104.5dB                                                                                 | 110dB                                                                                      |  |  |

| Noise(uV)                       | 8.207                                                                                      | 8.286                                                                                       | 7.030                                                                                   | 5.903                                                                                      |  |  |

www.ti.com Summary

## 4 Summary

Based on the previous simulation results and proposals comparison, each of the four proposals has advantages. Proposal 1 is applicable to hand-held and portable ultrasound machines. Proposal 2 can be applicable to the general ultrasound machine. Proposal 3 and Proposal 4 aims to the high-end ultrasound machine because of each high SNR and dynamic range. Engineers can decide which design to use based on the specific use case.

## **5 References**

- Texas Instruments, High-Resolution, High-SNR True Raw Data Conversion Reference Design for Ultrasound CW Doppler, design guide.

- Texas Instruments, Continuous Wave (CW) Signal Conditioning in Ultrasound Systems Using ADS92x4R, application note.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated