# SN54SC4T125-SEP Single-Event Latch-Up (SEL) Radiation Report

#### **ABSTRACT**

The purpose of this study is to characterize the effects of heavy-ion irradiation on the single-event latch-up (SEL) performance of the SN54SC4T125-SEP, a radiation-tolerant, quadruple buffer translator gate with 3-state output CMOS logic level shifter. Heavy-ions with an LET<sub>EFF</sub> of 43 MeV-cm<sup>2</sup> / mg were used to irradiate three production devices with a fluence of 1 ×  $10^7$  ions / cm<sup>2</sup>. The results demonstrate that the SN54SC4T125-SEP is SEL-free up to LET<sub>EFF</sub> = 43 MeV-cm<sup>2</sup> / mg as  $125^{\circ}$ C.

The SN54SC4T125-SEP Single-Event Latch-Up (SEL) radiation report covers the SEL performance of all seven devices listed below. The SN54SC4T125-SEP device covers all functional blocks and active die area of the other six devices, which is why the device was selected for single-event effect testing for this group of logic gate devices.

- SN54SC4T125-SEP

- SN54SC3T97-SEP

- SN54SC3T98-SEP

- SN54SC4T00-SEP

- SN54SC4T02-SEP

- SN54SC4T32-SEP

- SN54SC4T86-SEP

#### **Table of Contents**

| 1 Overview                                                                           | 3              |

|--------------------------------------------------------------------------------------|----------------|

| 2 Single-Event Effects (SEE)                                                         | 4              |

| 3 Test Device and Test Board Information                                             | <mark>5</mark> |

| 4 Irradiation Facility and Setup                                                     | <mark>7</mark> |

| 5 Results                                                                            |                |

| 5.1 SEL Results                                                                      | 8              |

| 5.2 Event Rate Calculations                                                          | 10             |

| 6 Summary                                                                            | 11             |

| 7 References                                                                         | 12             |

|                                                                                      |                |

| List of Figures                                                                      |                |

| Figure 2-1. Functional Block Diagram of the SN54SC4T125-SEP                          | 4              |

| Figure 3-1. SN54SC4T125-SEP Pinout Diagram                                           |                |

| Figure 3-2. Photo of SN54SC4T125-SEP Package Decapped                                | <mark>5</mark> |

| Figure 3-3. SN54SC4T125-SEP Evaluation Board (Top View)                              | 5              |

| Figure 3-4. SN54SC4T125-SEP SEL Bias Diagram                                         | 6              |

| Figure 3-5. SN54SC4T125-SEP Thermal Image for SEL                                    | 6              |

| Figure 4-1. SN54SC4T125-SEP Evaluation Board at the MSU FRIB Facility                |                |

| Figure 5-1. Current versus Time for Run Number 1 of the SN54SC4T125-SEP at T = 125°C |                |

| Figure 5-2. Current versus Time for Run Number 4 of the SN54SC4T125-SEP at T = 125°C | 9              |

| Figure 5-3. Current versus Time for Run 7 of the SN54SC4T125-SEP at T = 125°C        | 9              |

| 1                                                                                    |                |

| List of Tables                                                                       |                |

| Table 1-1. Overview Information <sup>1</sup>                                         |                |

| Table 5-1. Summary of SN54SC4T125-SEP Test Conditions and Results                    | 8              |

## **Trademarks**

All trademarks are the property of their respective owners.

www.ti.com Overview

#### 1 Overview

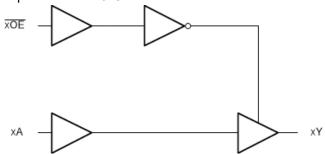

SN54SC4T125-SEP contains four independent buffers with 3-state outputs and extended voltage operation to allow for level translation. Each buffer performs the Boolean function Y = A in positive logic. The outputs can be put into a Hi-Z state by applying a High on the  $\overline{OE}$  pin. The output level is referenced to the supply voltage (VCC) and supports 1.8-V, 2.5-V, 3.3-V, and 5-V CMOS levels.

Table 1-1. Overview Information<sup>1</sup>

| Description               | Device Information                                                                                                   |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| TI Part Number            | SN54SC4T125-SEP                                                                                                      |  |  |

| MLS Number                | SN54SC4T125MPWTSEP                                                                                                   |  |  |

| Device Function           | Radiation Tolerant, Single Power Supply Quadruple Buffer Translate Gate With 3-State Output CMOS Logic Level Shifter |  |  |

| Technology                | LBC9                                                                                                                 |  |  |

| Exposure Facility         | Facility for Rare Isotope Beams (FRIB) at Michigan State Universi  – FRIB Single Event Effects (FSEE) Facility       |  |  |

| Heavy Ion Fluence per Run | 1×10 <sup>7</sup> ions / cm <sup>2</sup>                                                                             |  |  |

| Irradiation Temperature   | 125°C (for SEL testing)                                                                                              |  |  |

<sup>(1)</sup> TI may provide technical, applications or design advice, quality characterization, and reliability data or service, providing these items shall not expand or otherwise affect Tl's warranties as set forth in the Texas Instruments Incorporated Standard Terms and Conditions of Sale for Semiconductor Products and no obligation or liability shall arise from Semiconductor Products and no obligation or liability shall arise from Tl's provision of such items.

Single-Event Effects (SEE) www.ti.com

## 2 Single-Event Effects (SEE)

The primary single-event effect (SEE) event of interest in the SN54SC4T125-SEP is the destructive single-event latch-up. From a risk or impact perspective, the occurrence of an SEL is potentially the most destructive SEE event and the biggest concern for space applications. In mixed technologies such as the Linear BiCMOS (LBC9) process used for SN54SC4T125-SEP, the CMOS circuitry introduces a potential SEL susceptibility. SEL can occur if excess current injection caused by the passage of an energetic ion is high enough to trigger the formation of a parasitic cross-coupled PNP and NPN bipolar structure (formed between the p-substrate and n-well and n+ and p+ contacts). The parasitic bipolar structure initiated by a single-event creates a high-conductance path (inducing a steady-state current that is typically orders-of-magnitude higher than the normal operating current) between power and ground that persists (is latched) until power is removed or until the device is destroyed by the high-current state. The process modifications applied for SEL-mitigation were sufficient, as the SN54SC4T125-SEP exhibited no SEL with heavy-ions up to an LET<sub>EFF</sub> of 43 MeV-cm<sup>2</sup> / mg at a fluence of 1 × 10<sup>7</sup> ions / cm<sup>2</sup> and a chip temperature of 125°C.

Figure 2-1. Functional Block Diagram of the SN54SC4T125-SEP

## 3 Test Device and Test Board Information

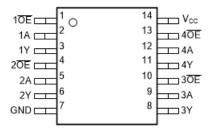

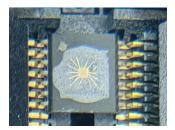

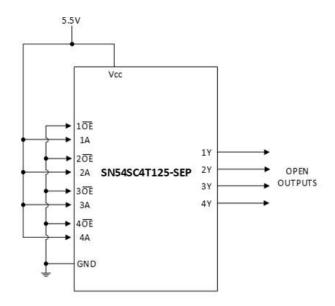

The SN54SC4T125-SEP is a packaged 14-pin, TSSOP plastic package shown in Figure 3-1 . Figure 3-2 shows the device with the package cap decapped to reveal the die for heavy ion testing. Figure 3-3 shows the evaluation board used for radiation testing. Figure 3-4 shows the bias diagram used for Single-Event Latch-up (SEL) testing.

Figure 3-1. SN54SC4T125-SEP Pinout Diagram

Figure 3-2. Photo of SN54SC4T125-SEP Package Decapped

Figure 3-3. SN54SC4T125-SEP Evaluation Board (Top View)

Figure 3-4. SN54SC4T125-SEP SEL Bias Diagram

Figure 3-5. SN54SC4T125-SEP Thermal Image for SEL

## 4 Irradiation Facility and Setup

The heavy ion species used for the SEE studies on this product were provide and delivered by the Facility for Rare Isotope Beams (FRIB) at Michigan State University (FRIB Single Event Effects (FSEE) Facility's linear accelerator.) The FSEE Facility has a dedicated beamline built on the FRIB linac infrastructure with a user experimental station at the end of the FSEE beamline. Ion beams are delivered with high uniformity over a 1-inch diameter exposure area using a thin vacuum window. For this study, ion flux of  $10^5$  ions / s-cm² was used to provide heavy ion fluence of  $1 \times 10^7$  ions / cm² using  $^{129}$ Xe ion at a linac energy of 25 MeV /  $\mu$ . Ion beam non-uniformity for all tests was 6.5%.

Figure 4-1 shows one of the three SN54SC4T125-SEP test board used for experiments at the MSU FSEE facility. The in-air gap between the device and the ion beam port window was maintained at 70 mm for all runs.

Figure 4-1. SN54SC4T125-SEP Evaluation Board at the MSU FRIB Facility

Results Www.ti.com

#### 5 Results

#### 5.1 SEL Results

During SEL characterization, the device was heated using forced hot air, maintaining IC temperature at 125°C. A FLIR (FLIR ONE Pro LT) thermal camera was used to validate die temperature to make sure that the device was accurately heated (see Figure 3-5). The species used for SEL testing was a Xenon ( $^{129}$ Xe) ion at a linac energy of 25 MeV /  $\mu$  with an angle-of-incidence of 0° for an LET<sub>EFF</sub> of 43 MeV-cm² / mg. A fluence of approximately 1 ×  $^{107}$  ions/cm² were used for the runs.

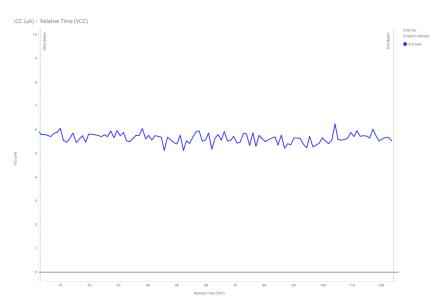

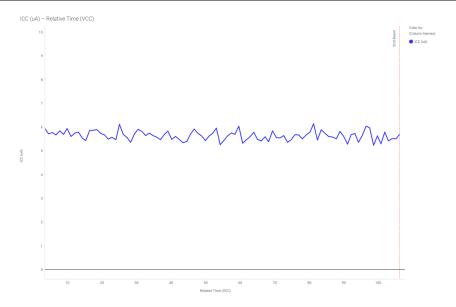

The three devices were powered up and exposed to the heavy-ions using the maximum recommended supply voltage of 5.5-V using a National Instruments PXI Chassis PXIe-1085. The run duration to achieve this fluence was approximately 2 minutes. As listed in Table 5-1, no SEL events were observed during the nine runs, indicating that the SN54SC4T125-SEP is SEL-free. Figure 5-1, Figure 5-2, and Figure 5-3 show the plot of current versus time for run numbers one, four, and seven, respectively.

Table 5-1. Summary of SN54SC4T125-SEP Test Conditions and Results

| Run<br>Number | Unit<br>Number | Distance<br>(mm) | Temperature (°C) | lon | Angle | FLUX<br>(ions × cm² /<br>mg) | Fluence<br>(number of<br>ions) | LET <sub>EFF</sub><br>(MeV × cm <sup>2</sup> /<br>mg) | Did a SEL<br>event<br>occur? |

|---------------|----------------|------------------|------------------|-----|-------|------------------------------|--------------------------------|-------------------------------------------------------|------------------------------|

| 1             | 1              | 70               | 123              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 2             | 1              | 70               | 123              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 3             | 1              | 70               | 123              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 4             | 2              | 70               | 123              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 5             | 2              | 70               | 123              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 6             | 2              | 70               | 123              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 7             | 3              | 70               | 122              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 8             | 3              | 70               | 122              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

| 9             | 3              | 70               | 122              | Xe  | 0°    | 1.00E+05                     | 1.00E+07                       | 43                                                    | No                           |

Figure 5-1. Current versus Time for Run Number 1 of the SN54SC4T125-SEP at T = 125°C

ww.ti.com Results

Figure 5-2. Current versus Time for Run Number 4 of the SN54SC4T125-SEP at T = 125°C

Figure 5-3. Current versus Time for Run 7 of the SN54SC4T125-SEP at T = 125°C

No SEL events were observed, indicating that the SN54SC4T125-SEP is SEL-immune at LET<sub>EFF</sub> = 43 MeV-cm<sup>2</sup> / mg and T =  $125^{\circ}$ C. Using the MFTF method shown in *Single-Event Effects (SEE) Confidence Interval Calculations*, the upper-bound cross-section (using a 95% confidence level) is calculated as:

$$\sigma_{\rm SEL} \le 1.23 \times 10^{-7} \ {\rm cm^2} \ / \ {\rm device} \ {\rm for} \ {\rm LET}_{\rm EFF} = 43 \ {\rm MeV-cm^2} \ / \ {\rm mg} \ {\rm and} \ {\rm T} = 125 {\rm ^{\circ}C} \ (1)$$

Results INSTRUMENTS

www.ti.com

#### **5.2 Event Rate Calculations**

Event rates were calculated for LEO (ISS) and GEO environments by combining CREME96 orbital integral flux estimations and simplified SEE cross-sections according to methods described in *Heavy Ion Orbital Environment Single-Event Effects Estimations*. A minimum shielding configuration of 100 mils (2.54 mm) of aluminum and *worst-week* solar activity is assumed. (This is similar to a 99% upper bound for the environment.) Note that this number is for reference since no events were observed.

Table 5-2. SEL Event Rate Calculations for Worst-Week LEO and GEO Orbits

| Orbit Type | Onset LET <sub>EFF</sub><br>(MeV-cm <sup>2</sup> / mg) | CREME96<br>Integral FLUX ( /<br>day / cm²) | σSAT (cm²)              | Event Rate (/<br>day)    | Event Rate (FIT)        | MTBF (Years)           |

|------------|--------------------------------------------------------|--------------------------------------------|-------------------------|--------------------------|-------------------------|------------------------|

| LEO (ISS)  | 43                                                     | 6.40 × 10 <sup>-4</sup>                    | 1.23 × 10 <sup>-7</sup> | 7.87 × 10 <sup>-11</sup> | 3.28 × 10 <sup>-3</sup> | 3.48 × 10 <sup>7</sup> |

| GEO        | 43                                                     | 2.17 × 10 <sup>-3</sup>                    | 1.25 ^ 10               | 2.67 × 10 <sup>-10</sup> | 1.11 × 10 <sup>-2</sup> | 1.03 × 10 <sup>7</sup> |

www.ti.com Summary

## 6 Summary

The purpose of this study was to characterize the effects of heavy-ion irradiation on the single-event latch-up (SEL) performance of the SN54SC4T125-SEP, a radiation-tolerant, quadruple buffer translator gate with 3-state output CMOS logic level shifter. Heavy-ions with an LET<sub>EFF</sub> of 43 MeV-cm²/ mg were used for the SEE characterization. The SEE results demonstrated that the SN54SC4T125-SEP is SEL-free up to LET<sub>EFF</sub> = 43 MeV·cm² / mg and across the full electrical specifications. CREME96-based worst-week event-rate calculations for LEO (ISS) and GEO orbits for the DSEE are shown for reference.

References Www.ti.com

## 7 References

- 1. M. Shoga and D. Binder, "Theory of Single Event Latchup in Complementary Metal-Oxide Semiconductor Integrated Circuits", *IEEE Trans. Nucl. Sci., Vol.* 33(6), Dec. 1986, pp. 1714-1717.

- 2. G. Bruguier and J. M. Palau, "Single particle-induced latchup", *IEEE Trans. Nucl. Sci., Vol. 43(2)*, Mar. 1996, pp. 522-532.

- 3. Texas A&M University, Texas A&M University Cyclotron Institute Radiation Effects Facility, webpage.

- 4. James F. Ziegler, Stopping and Range of lons in Matter, webpage.

- 5. D. Kececioglu, "Reliability and Life Testing Handbook", Vol. 1, PTR Prentice Hall, New Jersey,1993, pp. 186-193.

- 6. Vanderbilt University, ISDE CRÈME-MC, webpage.

- 7. A. J. Tylka, J. H. Adams, P. R. Boberg, et al., "CREME96: A Revision of the Cosmic Ray Effects on Micro-Electronics Code", *IEEE Trans. on Nucl. Sci., Vol. 44(6)*, Dec. 1997, pp. 2150-2160.

- 8. A. J. Tylka, W. F. Dietrich, and P. R. Boberg, "Probability distributions of high-energy solar-heavy-ion fluxes from IMP-8: 1973-1996", *IEEE Trans. on Nucl. Sci.*, Vol. 44(6), Dec. 1997, pp. 2140-2149.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated