Hello, and welcome to the lecture for the TI Precision Lab discussing input offset voltage, or  $V_{OS}$ . In this lecture we'll discuss op amp  $V_{OS}$  specifications,  $V_{OS}$  drift over temperature, input bias current (or  $I_B$ ), and input bias current drift over temperature. We'll also show the range of  $V_{OS}$  and  $I_B$  across many different Texas Instruments op amps.

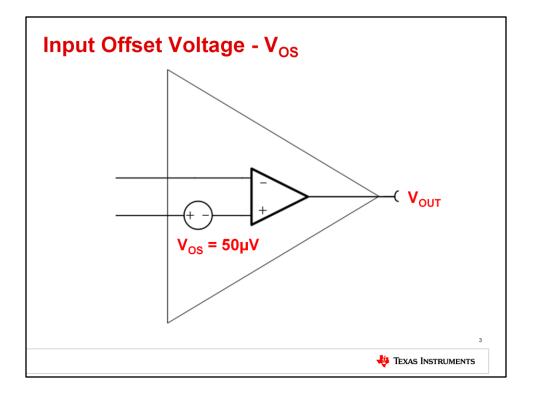

Let's start by defining offset voltage. Offset voltage is the differential input voltage that would have to be applied to force the op amp's output to zero volts. Typical offset voltages range from mV down to  $\mu$ V, depending on the op amp model. Offset can be modeled as an internal dc source connected to the input of the op amp. Changing power supply voltage and common mode voltage will affect input offset voltage.

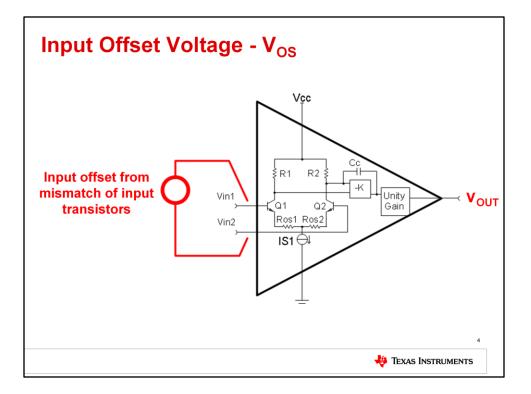

Looking at the inside of an op amp, we can see that the mismatch of transistors  $Q_1$  and  $Q_2$  in the differential input pair is what causes the offset voltage. In some cases, internal resistors  $R_{OS1}$  and  $R_{OS2}$  are laser trimmed in order to compensate for this mismatch and obtain very low offset voltage. In other cases, an internal digital correction circuit is used to minimize offset voltage and offset drift.

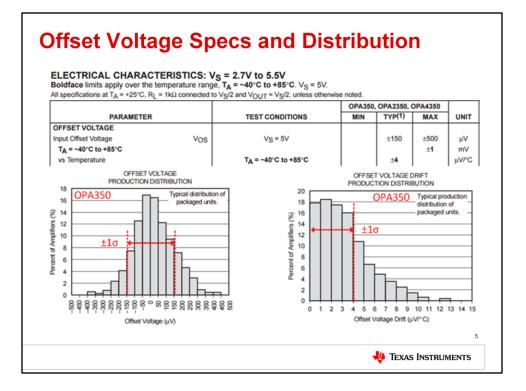

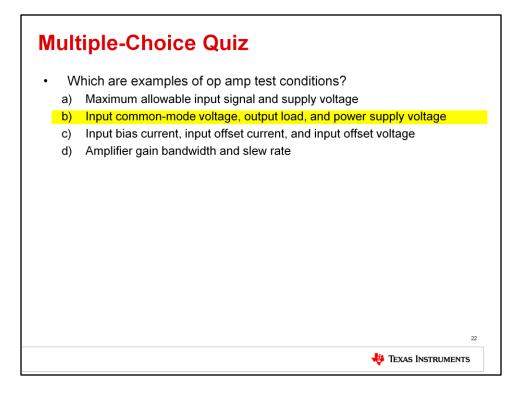

This slide introduces op amp specifications. The top of the specification table is the test conditions for all the parameters in the data sheet. In this example, the temperature is 25 °C, the load resistance is  $1 k \Omega$ , the load is connected to mid supply, and the common mode voltage is set to mid supply. These conditions are true unless otherwise specified. If you look at the offset voltage specs, it lists some additional conditions. The supply voltage is 5V.

The value listed in the typical specification will cover  $\pm$  one standard deviation, or  $\pm$  sigma, on a Gaussian distribution. This means that 68% of the device population will be less then the typical value. So, in this example, 68% of the devices would have less then  $\pm 150~\mu V$  of  $V_{os}$ . The maximum is a tested value, and so you will never find a device with greater than the maximum  $V_{os}$  of  $\pm 500~\mu V$ .

We also have a V<sub>os</sub> drift specification that is measured in  $\mu$ V/°C, describing how V<sub>os</sub> changes with temperature. In this case the typical drift, which represents +/- 1 standard deviation, is given as 4  $\mu$ V/°C. For this device, no maximum drift is given. However, the production distribution graph from the data sheet gives the designer an understanding of the drift distribution. Given one standard deviation is +/- 4uV/C, the six sigma value is approximately +/- 12uV/C. This means that about 99.7% of all devices will drift less than or equal to +/-12uV/C. Put another way, approximately 3 out of 1000 units will drift more than +/-12uV/C.

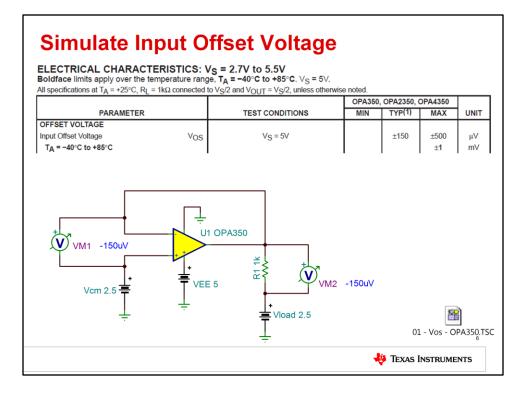

Most op amp SPICE models include the effects of offset voltage. Several external conditions, such as power supply voltage and common mode voltage, affect the offset voltage on a real world device. These effects are also included in the simulation model.

In order for the simulation result to match the offset specifications in the data sheet table, the same test conditions must to be applied to the amplifier. In this example, the power supply is set to 5 V, the common mode voltage is set to mid supply, or 2.5 V, and the load is connected to mid supply in order to match the data sheet conditions. The typical offset specification is 150  $\mu$ V, and the simulated offset is also 150  $\mu$ V. The goal of our models is to target typical op amp performance.

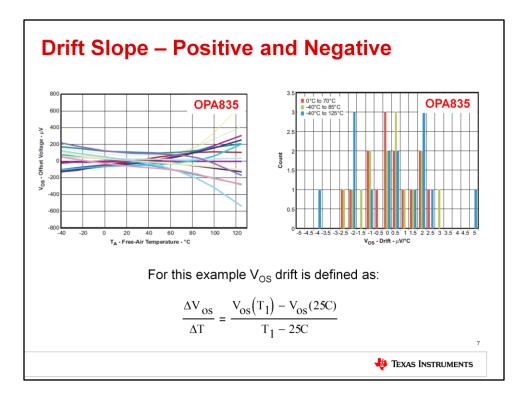

The slope on offset voltage drift can be either positive or negative. This formula shows one possible definition for offset drift. This formula will produce a positive or negative drift depending on the slope of the curve. Some other definitions use the absolute value, so you will not have a negative offset.

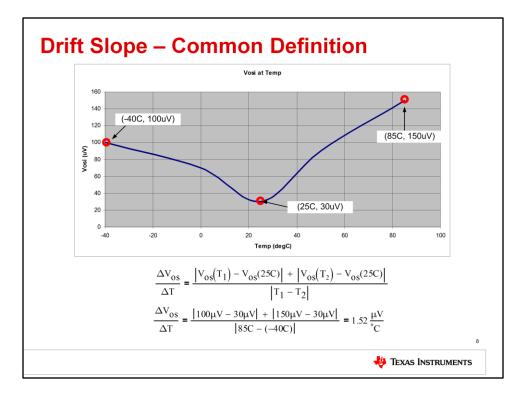

This is the more common definition for drift, which is separated into different two regions, although more than two regions could be used if desired.

The idea with this definition is that you get a more realistic view of what the expected error would be than if you only considered the end points over the entire region. In this example, you can see that the slope of the two separate regions is much more severe than the drift of the entire range. Note that the absolute value is used in the formula, so this formula will never give a negative result.

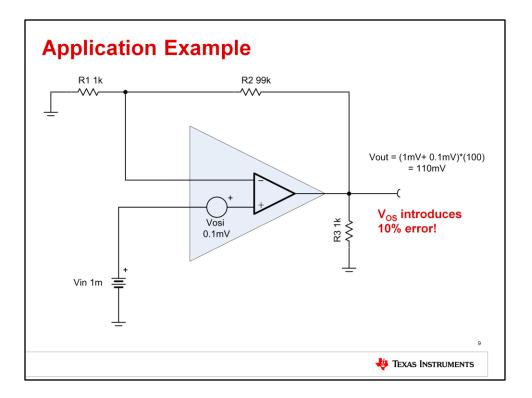

In this application example we will see how to calculate the output voltage error from the offset voltage.

Consider offset voltage as a dc voltage source in series with the non-inverting input of the op amp. We have a 0.1mV or 100uV offset in this case. The signal source is a very small input of 1mV, so the offset will generate a fairly significant error. The gain for this part is configured as 100 V/V, which can be calculated as R2/R1 + 1.

The total output voltage is the series combination of the offset and the input signal (1mV + 0.1mV), multiplied by the gain (100), which gives us 110 mV. The offset accounts for about 10% error.

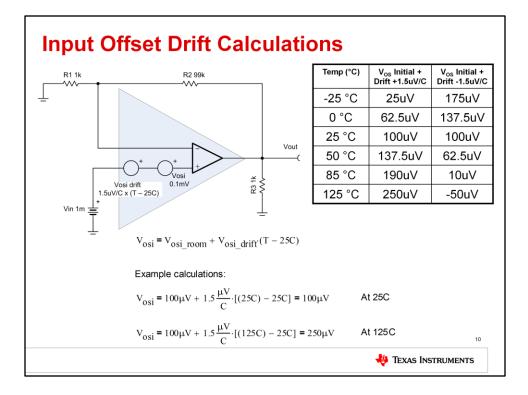

Offset drift calculations can be done in a similar manner. Notice that we have two sources: one for the initial offset and one for the offset drift. The offset drift source will be zero at 25C. As the temperature deviates from 25C, the temperature difference will be multiplied by the offset drift to generate the additional offset voltage.

For example, at 25C we have 100uV of offset, which is just the room temperature offset and no drift term. At 125C we have a total of 250uV; that is, 100uV from the initial offset, and 150uV from the drift term.

The table on the right illustrates how the offset changes over temperature. Keep in mind that the slope of the offset drift can be either positive or negative, so both cases are shown.

Drift is especially important in calibrated systems. In calibrated systems, room temperature offset is frequently measured and corrected for in software. Temperature drift, however, is often difficult and expensive to calibrate out, so devices with minimal drift are preferable.

| Op Amp | V <sub>os</sub> (max)<br>(high grade) | V <sub>os</sub> Drift (max)<br>(high grade) | Technology                     |

|--------|---------------------------------------|---------------------------------------------|--------------------------------|

| OPA333 | 10 µV                                 | 0.05 µV/°C                                  | Zero Drift CMOS                |

| OPA277 | 20 µV                                 | 0.15 µV/°C                                  | Precision Bipolar              |

| OPA188 | 25 µV                                 | 0.085 µV/°C                                 | Auto-Zero CMOS                 |

| OPA192 | 25 µV                                 | 0.5 µV/°C                                   | CMOS                           |

| OPA211 | 50 µV                                 | 1.5 µV/°C                                   | Precision Bipolar              |

| OPA827 | 150 µV                                | 1.5 µV/°C (typ.)                            | JFET input, Bipolar, Precision |

| OPA350 | 500 μV                                | 4 μV/°C (typ.)                              | CMOS                           |

| OPA835 | 1.85 mV                               | 13.5 µV/°C                                  | High Speed Bipolar             |

| LM741  | 3.00 mV                               | 15 µV/°C                                    | Bipolar commodity (lower cost) |

This chart shows a range of offset voltages, from uV to mV, for different types of TI amplifiers.

The first amplifier in the list, the OPA333, includes a zero drift topology which uses an internal digital calibration circuit to minimize offset and offset drift. Some precision bipolar amplifiers use laser trimming to minimize offset.

Often you must trade off bandwidth or other characteristics for low offset. For example, the OPA835 is optimized for speed, not for offset. Also, commodity, or low cost amplifiers are usually not optimized for low offset or offset drift.

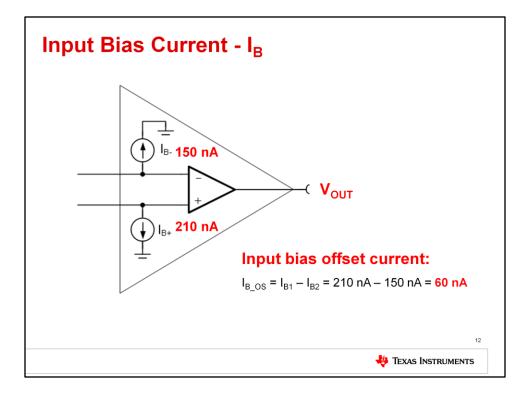

Let's now move on to input bias current, or I<sub>B</sub>, and input bias current drift.

Input bias current is the current flowing into the inputs of an op amp. These currents can be modeled as a current source connected to each input, as shown in this figure. Ideally, the two input bias currents would be equal to each other and would cancel. In reality, though, they are not equal, and the difference of these currents is defined as input offset current. If the input offset current is low, it's possible to match the impedances connected to each input and cancel the offset developed from the input bias currents.

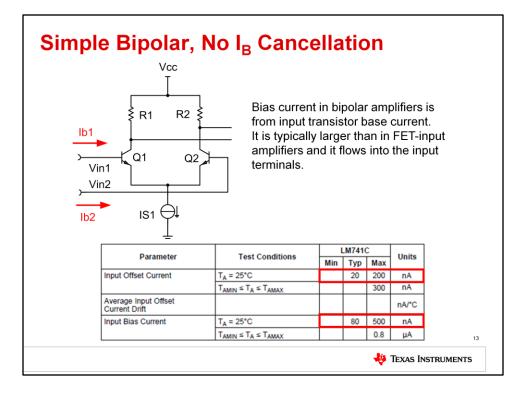

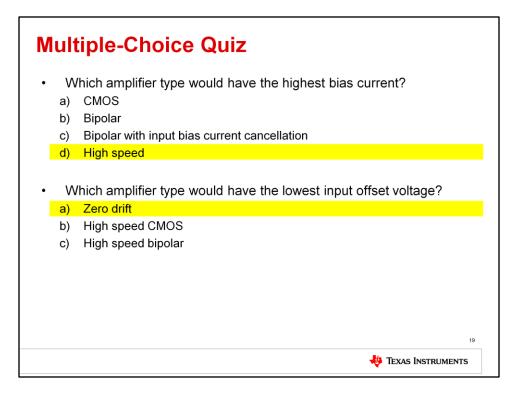

In a bipolar amplifier, input bias current is the current flowing into the base of each transistor in the input pair. Generally, the bias current for bipolar amplifiers is larger than the bias current for MOSFET and JFET amplifiers. Typical numbers are in the nA range. You can see in the case of the LM741C, the input offset current is about 200nA max, and the input bias current is about 500nA max.

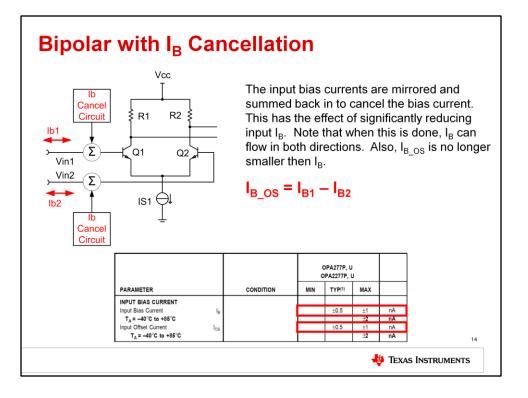

Some precision bipolar op amps use a method called bias current cancellation in order to minimize bias current. This is done inside the op amp, so no external components are required. The amplifier simply behaves like a bipolar amplifier with very low bias current.

Bias current cancellation is done by measuring the input bias current and summing in and equal, but opposite currents which cancel the bias current. This effectively takes an amplifier with hundreds of nA of bias current down to single nA of bias current.

You can see from the specification table in this example that the input bias current of the OPA277 is  $\pm$ 1nA maximum. In the previous example the bias current had to flow into the base of the transistor so the bias current could have only one polarity. In this case, however, the bias current can have either polarity, since the bias current cancelation circuit is not perfect and it's not known whether the polarity of the residual current will be positive or negative.

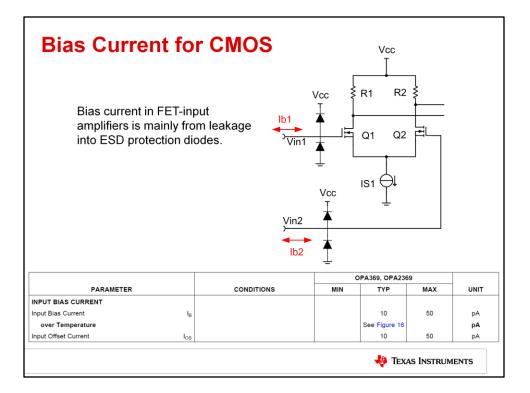

In the case of MOSFET or JFET op amps, the input bias current is primarily due to the leakage of the input ESD protection diodes. The gate of the input MOSFET transistors has extremely low leakage, so it doesn't contribute significant bias current. You can see in this example that the OPA369 has 50pA max of input bias current.

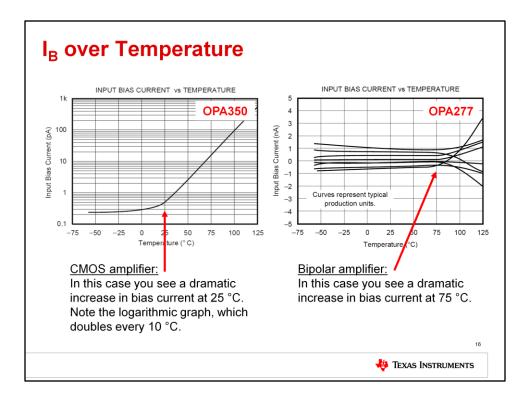

One thing to remember with low bias current amplifiers is the effect of  $I_B$  over temperature. In MOSFET amplifiers, the bias current can double every 10°C. You can see in the example on the left with the OPA350 that the input bias current increases significantly at temperatures above 25°C. If you only considered the room temperature value of  $I_B$  and then operated the amplifier at elevated temperature, you would have significant errors. Notice that the vertical axis of the plot uses a logarithmic scale.

With the bipolar amplifier, the initial input bias current at room temperature is often large enough such that the relative change in input bias current over temperature is minimized. You can see in the example on the right with the OPA277 that the input bias current starts to increase at temperatures above 75°C, but note that the vertical axis uses a linear scale.

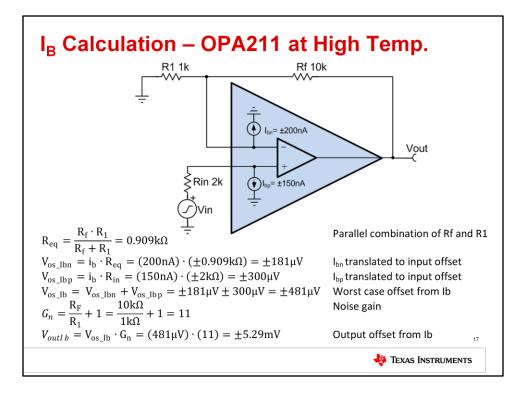

This bias current calculation is very similar to what was done for offset voltage. First, we model the bias currents as two current sources connected to the op amp inputs. Note that an offset error is generated when bias current from the inverting input interacts with the feedback network and also when the bias current from the non-inverting input interacts with the source impedance. The error from the inverting input can be reflected back to the non-inverting input when the bias current is multiplied by equivalent parallel combination of Rf and R1. Reflecting errors back to the non-inverting input referred error by the non-inverting gain. Note that the non-inverting gain is also called the noise gain. In this case the total error from Ib reflected to the input is  $\pm 482\mu$ V. This is multiplied by the noise gain of 11 to get an output error of  $\pm 5.29$ mV.

Please keep in mind that this was an error calculation using high temperature  $I_B$  values. If this calculation was done at room temperature, the error would have been significantly smaller.

| Op Amp | l <sub>B</sub> (max)<br>(high grade) | l <sub>B</sub> at max<br>temp. | Technology                     |

|--------|--------------------------------------|--------------------------------|--------------------------------|

| OPA129 | 100 fA                               | 20 pA (typ.)                   | Difet – Ultra Low Bias Current |

| OPA627 | 5 pA                                 | 1nA                            | Difet – Precision High Speed   |

| OPA350 | 10 pA                                | 500 pA (typ.)                  | CMOS                           |

| OPA827 | 50 pA                                | 50 nA max                      | JFET input, Bipolar, Precision |

| OPA333 | 70 pA                                | 150 pA (typ)                   | Zero Drift CMOS                |

| OPA277 | 1 nA                                 | 2 nA (max)                     | Precision Bipolar              |

| OPA211 | 125 nA                               | 200 nA                         | Precision Bipolar              |

| OPA835 | 400 nA                               | 530 nA                         | High Speed Bipolar             |

| LM741  | 80 nA                                | 0.2 µA (max)                   | Bipolar commodity (lower cost) |

This table gives a range of input bias currents for different TI op amps.

Values can range from fA for specialized CMOS amplifiers, all the way up to hundreds of nA for high speed and commodity op amps.

Note that bipolar op amps will always have higher input bias currents then CMOS amplifiers. Also, bipolar amplifiers with bias current cancellation circuitry, such as the OPA277, will have lower input bias current then bipolar op amps with out cancelation, such as the OPA211.

| Multiple-Choice Quiz                                                                                                                                                                                                                                       |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>Texas Instruments SPICE models target the specification:</li> <li>a) Maximum</li> <li>b) Typical</li> <li>c) High grade</li> <li>d) Low grade</li> </ul>                                                                                          | S. |

| <ul> <li>A typical offset voltage of 10µV indicates</li> <li>a) The average offset voltage is 10µV</li> <li>b) 100% of the devices will have an offset voltage less than 10µV</li> <li>c) 50% of the devices will have an offset less than 10µV</li> </ul> |    |

| d) $\pm 1$ standard deviation of the tested device distribution is equal to $\pm 10 \mu V$                                                                                                                                                                 |    |

| 👋 Texas Instruments                                                                                                                                                                                                                                        |    |

| Multiple-Choice Quiz                                                                                    |  |

|---------------------------------------------------------------------------------------------------------|--|

| <ul> <li>A maximum offset of 100µV indicates</li> </ul>                                                 |  |

| a) 90% of the devices have less than $100\mu V$ offset                                                  |  |

| <ul> <li>b) The device was tested with a 100µV limit and only passing units were<br/>shipped</li> </ul> |  |

| c) Applying more than 100µV will damage the unit                                                        |  |

| d) Offset can range from 0μV to 100μV                                                                   |  |

| <ul> <li>Bias current is modeled as</li> <li>a) A current source in series with each input</li> </ul>   |  |

| b) A current source connected to each input with respect to ground                                      |  |

| c) A resistance between the amplifier inputs                                                            |  |

| 21                                                                                                      |  |

| 👋 Texas Instruments                                                                                     |  |

Hello, and welcome to the lecture for the TI Precision Lab discussing op amp input and output limitations. In this lecture we'll discuss op amp common-mode input voltage, input and output voltage swing limitations, and show how to determine the source of circuit errors caused by these limitations.

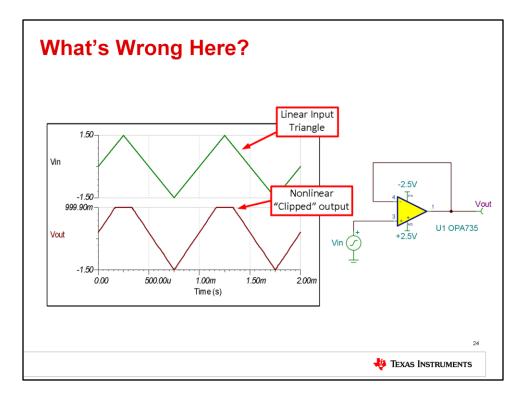

Lets start by considering this simple non-inverting buffer circuit. An triangle-wave input signal of +/- 1.5V is applied to the non-inverting input, and one might expect the output to look exactly the same. For some reason, the op amp output does not increase past +1V. This type of nonlinearity is called "clipping."

What is causing this clipping behavior? We'll answer this question later in the lecture, but first let's define some terms that are necessary to properly understand this issue.

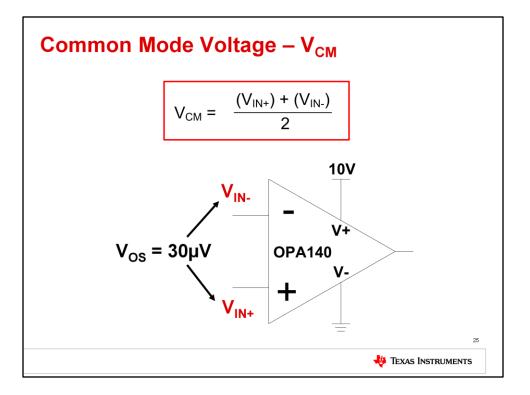

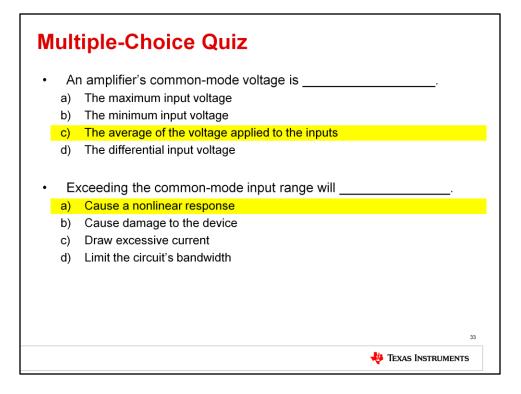

Common mode voltage is defined as the average voltage which is applied to the two inputs of an amplifier. In the case of an op amp, the two inputs are at the practically same potential, with only a small offset between them. So, effectively you can see the common mode voltage on either input.

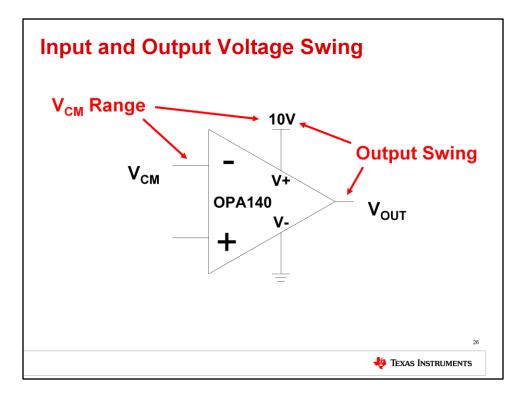

Common mode input voltage range is also known as input voltage swing. This term describes the range of input common mode voltages that can be used for normal linear operation of the amplifier. The common mode input voltage range is always defined relative to the positive supply and the negative supply. When you exceed the common mode input range, the output becomes nonlinear.

Output voltage swing is the range of output voltages that allow for linear operation of output signals. Output swing is also defined relative to the power supplies. The output signal becomes distorted and non-linear if you exceed the op amp's output swing specifications.

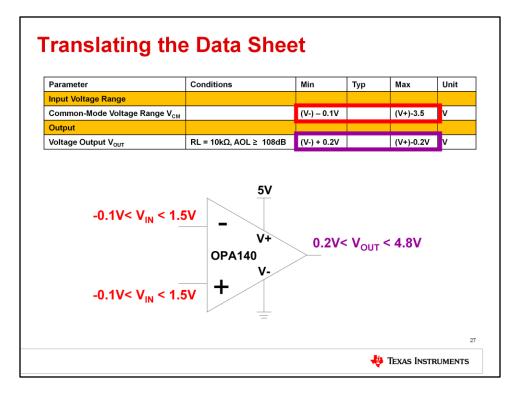

Let's look at how common mode voltage and input and output voltage swing are typically defined on a data sheet.

The common mode voltage range is defined here with the minimum and maximum limits given relative to the power supplies. The negative supply, V-, is zero volts in this case, so zero volts minus 0.1V gives us -0.1V for the minimum common mode limitation. The positive supply, V+, is 5V, so 5V minus 3.5V gives us 1.5V for the maximum common mode limitation. Therefore, applying an input common mode voltage below -0.1V or above 1.5V will result in nonlinear output.

The output swing is given here, and it's the same type of definition which is relative to the supply voltages. The minimum output voltage is V- + 0.2V, or 0.2V in this case, and the maximum output voltage is V+ - 0.2V, or 4.8V. Driving the output below 0.2V or above 4.8V will cause the output to become nonlinear.

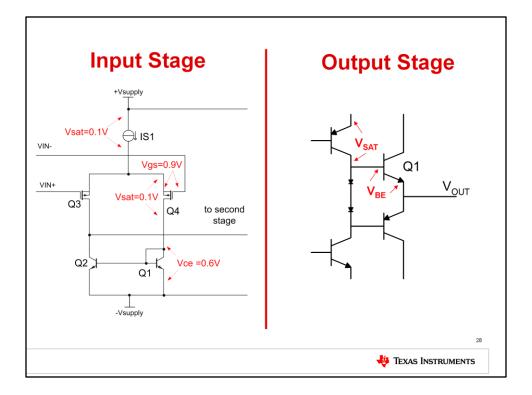

Let's discuss what elements inside the amplifier actually cause the input and output limitations.

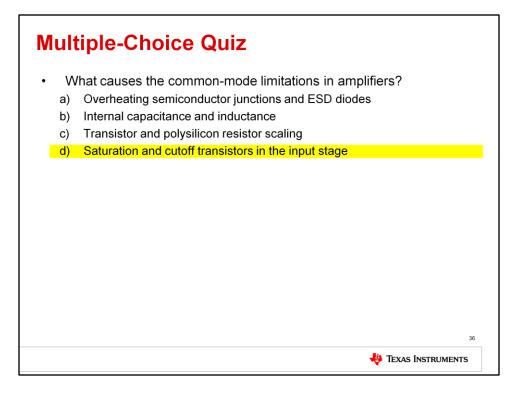

On the left you can see a typical CMOS input stage. As the common mode input signal approaches either the positive or negative supply, the input transistors will either saturate or cutoff. Saturation and cutoff are both nonlinear modes of operation, so the amplifier cannot linearly amplify the input signal. This is what causes the common mode input voltage limitation. Please keep in mind that some CMOS amplifiers have common mode limitations which are very near or even beyond the power supply rails.

The output stage voltage swing limitation caused by the saturation and diode drops on internal transistors. CMOS amplifiers tend to have better output voltage swing limitations, because CMOS transistors can have lower saturation voltages.

Amplifiers which can accept common mode input voltage ranges up to the power supply rails, and can swing the output voltage near the supply rails, are referred to as rail-to-rail amplifiers.

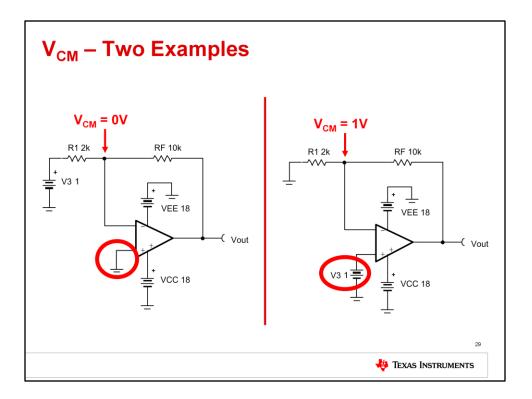

Here are two example circuits which have very different common mode considerations.

The op amp in the circuit on the left is in an inverting configuration, and notice that the non-inverting input is connected to GND, or 0V. Because of the basic properties of op amps, the inverting input will also be at approximately 0V. Therefore, the common mode input voltage of this circuit is 0V, and stays at a constant 0V regardless of the input signal. This is a good topology to use to avoid common mode limitations.

The op amp in the circuit on the right is in a non-inverting configuration, and the input signal is connected to the non-inverting input. The input signal and the common mode signal will track each other – in other words, when the input signal changes, the common mode signal will also change. Care must be taken in this configuration to avoid exceeding the common-mode voltage limitations of the amplifier.

Let's now consider a real-world circuit example.

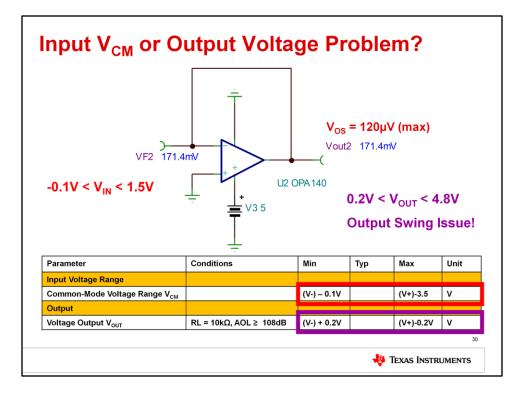

We have an op amp in a basic buffer configuration. One might expect to see 0V at the output, or a small offset depending on the  $V_{OS}$  specification of the device. However, after running a DC simulation we see that the output is almost 200mV! The maximum  $V_{OS}$  is only 120µV, so what's the problem?

First let's look at the input common mode range. Using the same technique as before, we can compute the common mode range to be from -0.1V to 1.5V. The input is connected to GND, or 0V, which is between the common mode limits of -0.1V and 1.5V, so there is no common mode input voltage violation.

Now let's look at the output voltage swing range. Again, we can compute the output range to be from 0.2V to 4.8V. Based on the input signal, the amplifier wants to drive the output to 0V, but this is below the minimum output of 0.2V! Therefore the output voltage range is being violated, which causes the actual output to clip nearly the 0.2V limit, at 171mV.

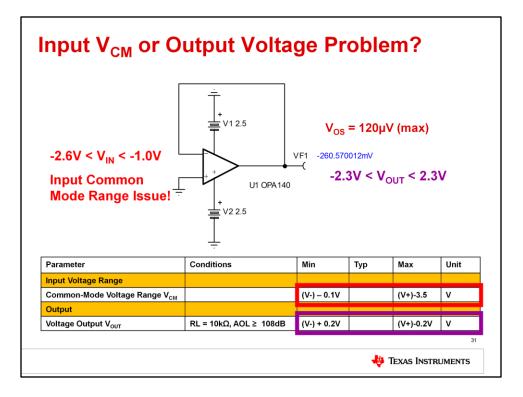

Lets look at another example. Note that this circuit has a different power supply arrangement, where the supplies are +/-2.5V.

Let's first consider the output voltage range. Using the data sheet specifications and the given power supply voltages, the output range is calculated to be from -2.3V to +2.3V. The amplifier wants to drive the output to zero 0V, and zero is inside the output range, so this circuit does not have an output voltage swing violation.

What about the input? The applied input common mode voltage is zero volts as in the previous circuit, but the input common mode voltage range is now from -2.6V to - 1V. OV is above that range, so we have a violation of the input common mode range. That is why we see hundreds of millivolts at the output, rather than microvolts.

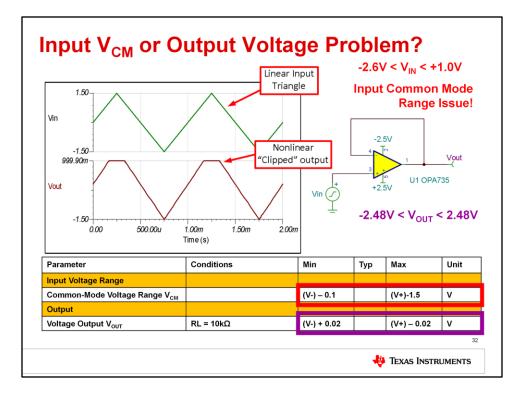

Finally, let's return to our original problem of output voltage clipping past 1V on the OPA735.

Let's first consider the output voltage range. Using the data sheet specifications and the given power supply voltages, the output range is calculated to be from -2.48V to +2.48V. The amplifier wants to drive the output from -1.5V to +1.5V, which is within the normal output range, so this circuit does not have an output voltage swing violation.

What about the input? Again, using the data sheet specifications, the allowed common-mode voltage range is calculated to be from -2.6V to +1V. Because this op amp is in a non-inverting buffer configuration, the VCM tracks the input, which is from -1.5V to +1.5V. Since the maximum VCM is +1V, we are exceeding the maximum by applying a triangle wave up to +1.5V. This violates the input common mode range and saturates the input stage transistors, so the output clips at 1V.

| . | nput and output swing limitations are                                                                   |

|---|---------------------------------------------------------------------------------------------------------|

| а | Given relative to the power supply voltage                                                              |

| b | Guidelines for preventing damage to the devices                                                         |

| C | Calculated using Ohm's Law                                                                              |

| d | Are only valid for DC signals                                                                           |

|   | An inverting op amp configuration has a constant common-mode<br>/oltage regardless of the input signal. |

|   | voltage regardless of the input signal.                                                                 |

| , | voltage regardless of the input signal.<br>True                                                         |

| a | voltage regardless of the input signal.<br>True                                                         |

| a | voltage regardless of the input signal.<br>True                                                         |

| a | voltage regardless of the input signal.<br>True                                                         |

| a | voltage regardless of the input signal.<br>True                                                         |

| Multiple-Choice Quiz                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>A non-inverting op amp configuration has a constant common-mode<br/>voltage regardless of the input signal.</li> <li>a) True</li> </ul> |

| b) False                                                                                                                                         |

| <ul> <li>A rail-to-rail input amplifier allows common-mode signals</li> </ul>                                                                    |

| a) Near ground                                                                                                                                   |

| b) Near the positive power supply                                                                                                                |

| c) That cover the full range from positive to negative supply                                                                                    |

| d) To be applied without damaging the device                                                                                                     |

| 35                                                                                                                                               |

| 🔱 Texas Instruments                                                                                                                              |

Hello, and welcome to the lecture for the TI Precision Lab discussing bandwidth. In this lecture we'll discuss an op amp's gain bandwidth product, the op amp's dominant pole and its impact on bandwidth, and the difference between inverting and non-inverting op amp configurations. Finally, we'll compare the bandwidth versus quiescent current of several TI amplifiers.

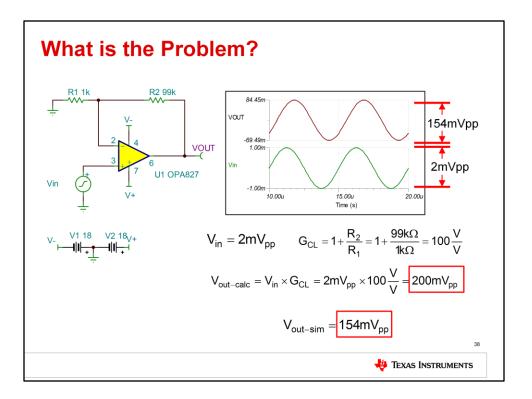

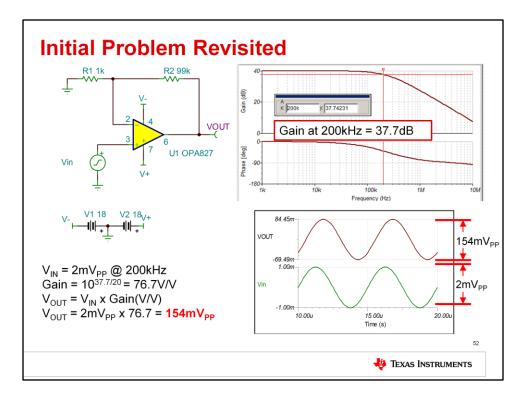

In this transient simulation, the OPA827 is set up in a non-inverting configuration with a closed loop gain of 100V/V. The input signal, Vin, is 2mVpp. The product of the input signal and closed loop gain is 200mVpp.

When simulated, however, the output voltage is only 154mVpp. Why?

In order to answer this question, we need to fully understand the concept of bandwidth. First, let's review a few topics.

When working with electronics we often need to express quantities such as op amp gain, signal-to-noise ratio, common-mode-rejection ratio, and power supply rejection ratio whose values have very large spans.

Therefore it is important to have a mechanism upon which we can represent a large range of values while using small numbers. This mechanism is called the 'decibel', or 'dB' for short. Note that decibels have no units.

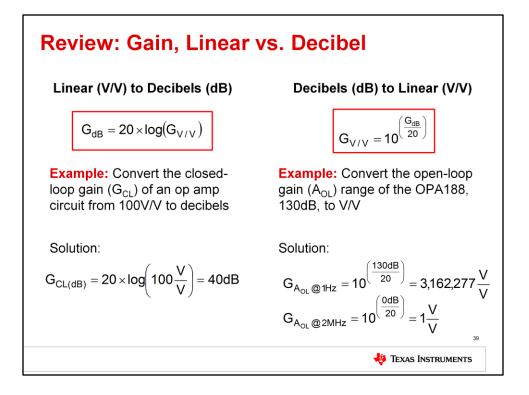

This slide shows how to convert linear gain values to dB and vice versa.

This equation shows how to convert from a linear gain in volts per volt to decibels. For example, let's convert the closed loop gain of an op amp circuit from 100V/V to decibels.

Substituting 100V/V for the linear gain in the given equation yields 40dB.

Similarly, given a gain in decibels we can convert it to a linear representation using this equation.

While the previous example may not seem like a significant improvement in representing large numbers, let's look at the open loop gain, or Aol, of the OPA188. At 1Hz, the open loop gain is 130dB, which equates to a linear gain of 3,162,277V/V.

At 2MHz the open loop gain is 0dB, which equates to a linear gain of 1V/V.

Ultimately we find it's much easier to represent such a large range of values using decibels instead of volts per volt.

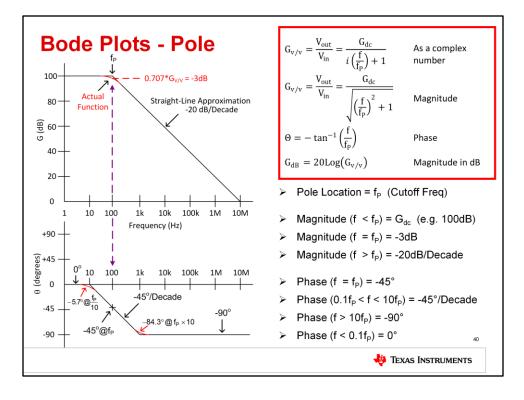

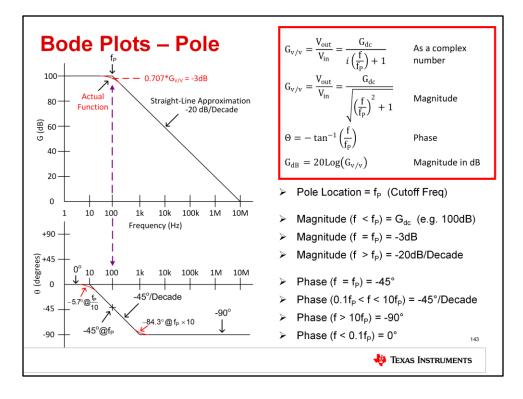

This slide illustrates the equations for a pole and its associated response. Later we will provide a real world circuit example for a pole. Looking at the equations, you can see that the first equation represents a pole as a complex number. Complex numbers have a real and imaginary part. For practical circuits the complex function is converted to a magnitude and phase. The second equation shows the magnitude and the third equation shows the phase. As discussed earlier 20\*log base 10 of the linear gain yields the gain in decibels.

The graphs show the magnitude in dB as well as the phase in degrees. This type of plot is called a Bode plot. Notice that both the horizontal axis and vertical axis are logarithmic. Let's look at some key points on the bode plot. First, the pole frequency as denoted by  $f_P$ . For frequencies below  $f_P$  the gain is constant and is denoted  $G_{DC}$ . In other words, the gain at dc or zero frequency would be  $G_{DC}$ . In this example  $G_{DC} = 100$ dB. Also notice that the gain at  $f_P$  is attenuated by 3db, or is 0.707 times the dc gain. Finally, for frequencies greater than  $f_P$ , the magnitude plot rolls off at a rate of -20dB/decade.

Now let's consider the graph of phase shift vs. frequency. The phase shift at the pole frequency is -45 degrees. Phase begins to change one decade before the pole and stops changing one decade after the pole. In this region the slope is -45 degrees per decade. Considering frequencies that are lower

than one decade below the pole, the phase shift is 0 degrees. For frequencies greater than one decade beyond the pole the phase shift is -90 degrees.

Notice that bode plots and phase plots are drawn using straight line approximations. In reality the function will deviate from this approximation. For example, if you consider the points exactly one decade below and above the pole on the phase curve. The straight line approximation shows the value at these points to be 0 degrees and -90 degrees respectively. However, the actual function deviates slightly from the straight line approximation. In practice, simulation software can be used to obtain the actual values.

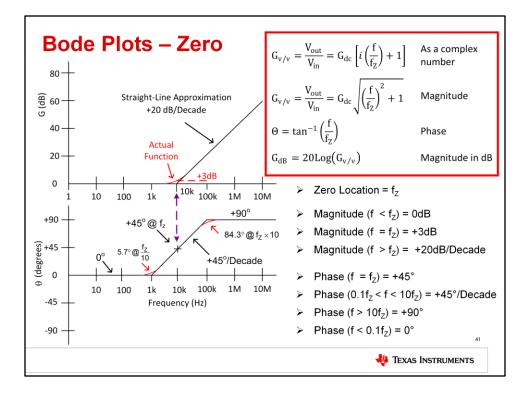

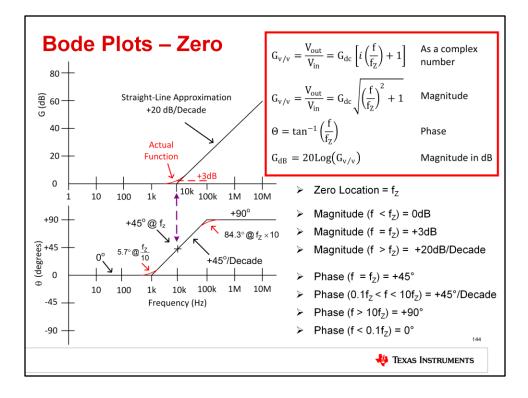

This slide illustrates the equations for a zero and its associated response. Looking at the equations, you can see that the first equation represents a zero as a complex number. Complex numbers have a real and imaginary part. For practical circuits the complex function is converted to a magnitude and phase. The second equation shows the magnitude and the third equation shows the phase. Taking 20 Log10 of the magnitude function gives the magnitude in dB.

The equations were used to generate the bode plot and phase plot. Let's look at some key points on the bode plot. First, the zero frequency is denoted  $f_z$ . For frequencies below  $f_z$  the gain is constant and is denoted  $G_{DC}$ . In this example  $G_{DC} = 0$ dB. Also notice that the gain at  $f_z$  is at **+3db**, or is 1.414 times the dc gain. Finally, for frequencies greater than  $f_z$ , the magnitude plot increases at a rate of +20dB/decade.

Now let's consider the graph of phase shift vs. frequency. The phase shift at the zero frequency is +45 degrees. Phase begins to change one decade before the zero and stops changing one decade after the zero. In this region the slope is +45 degrees per decade. Considering frequencies that are lower than one decade below the zero, the phase shift is 0 degrees. For frequencies greater than one decade beyond the zero the phase shift is +90 degrees.

Up to this point we have looked at the mathematics behind frequency

response. Now we will look at connecting the mathematics to electrical circuits.

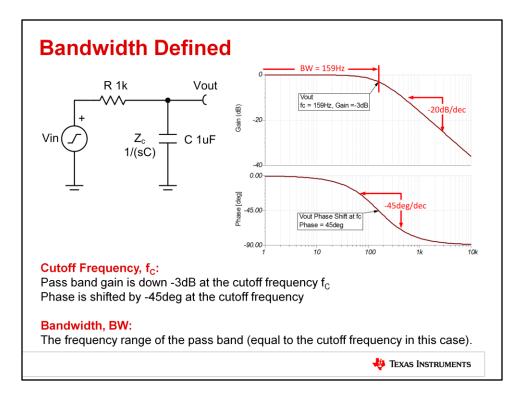

This figure shows the bode plot and the phase shift plot for a simple RC circuit. Recall that at dc or low frequencies a capacitor acts like an open. In this case the entire input signal is seen across the capacitor, so the gain is 1V/V or 0dB. Notice that the magnitude of the gain at the pole frequency is -3dB. Also notice that the phase at the pole frequency is -45 degrees. Furthermore, the phase shift begins about one decade before the pole and ends about one decade after the pole. Furthermore, the phase shift at very low frequencies is near zero degrees and at high frequencies the shift is nearly 90 degrees. Finally, notice that the gain decreases at a rate of -20dB/decade for frequencies above the pole frequency.

This circuit is a common building block and is called a low pass filter. The objective of this circuit is to pass low frequency signals and stop high frequency signals. For this reason, the pole frequency is often called the cutoff frequency, and denoted by fc. The idea is that all signals with frequency greater then the cutoff frequency are "cut off" or eliminated. In fact the high frequency signals are only attenuated and not fully eliminated. Another term associated with low pass filters is "bandwidth". Bandwidth is simply the *width* of the pass-band, and in this case is synonymous with the cutoff frequency. In later videos we will discuss different types of filters. For some filters, such as a band pass filter, the bandwidth definition *will* include both a lower and upper cutoff frequency.

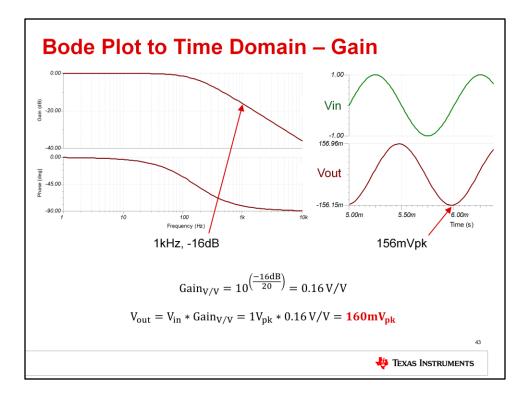

The bode gives information on the gain as well as the phase shift for a circuit. In this example we're going to calculate the peak output voltage of a 1Vp sinusoid at 1kHz. Given the amplitude and frequency of the input signal we can use the bode plot **magnitude (Gain (dB))** to determine the output signal amplitude. First, find the gain at 1kHz. In this example the gain is -16dB. Convert the gain from dB to a linear representation and multiply the input signal by the linear gain. In this example -16dB translates to 0.16V/V. Since the input is 1Vpk the output is 160mVpk. Notice that the time domain simulation peak output is very close to the expected value from the bode plot.

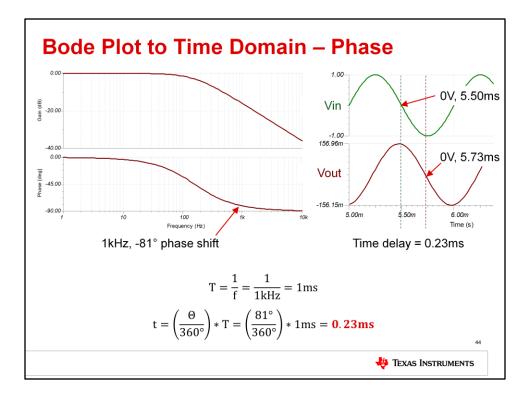

Here we will continue the example considering the phase shift in the time domain. Notice on the **bode phase (Phase (deg))** that the phase shift is -81degrees at 1kHz. On the time domain plot, you can see that the output signal is shifted to the right in time. This is called a phase shift or time delay. The calculation at the bottom of the page illustrates how you can convert the phase shift in degrees to expected time delay in seconds.

In this case, the phase shift is 81 degrees and the period of the 1kHz input is 1ms. The delay in seconds is calculated by dividing the phase shift by 360 degrees and multiplying by the period. As with the previous example, the calculated results match very well with simulation, and we see a time shift of 0.23ms.

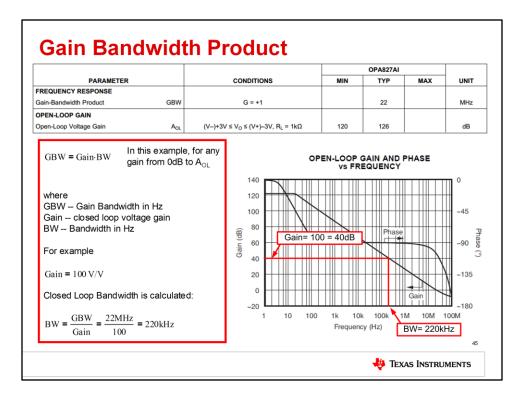

A simple approach to determining bandwidth is to use the gain-bandwidth product specification from an op amp data sheet.

The gain bandwidth product is literally the product of the linear gain and the bandwidth. Therefore, you can solve for one of the variables given the other two.

For example, let's calculate the bandwidth of a circuit that uses the OPA827 in a gain of 100V/V.

From the data sheet we see that the gain bandwidth product is 22MHz.

Solving the gain bandwidth equation for bandwidth tells us that the bandwidth is the gain bandwidth product divided by the linear gain. Dividing the OPA827 gain bandwidth product of 22MHz by the circuit gain of 100V/V yields a bandwidth of 220kHz.

This calculation is verified by looking at the OPA827 open loop gain curve from the data sheet. If we draw a horizontal line at the closed loop gain of 100V/V, or 40dB, until it intersects Aol we find the corresponding bandwidth is approximately 200kHz. Notice that solved graphically you may incorrectly interpret the bandwidth to be 200kHz, though by calculation we found it to be 220kHz.

It should be noted that the calculation approach to solving for bandwidth is only valid if the Aol curve decreases at a rate of **-20dB/decade**. While this is true for most op amps, there are some that have a limited range where the gain bandwidth product is specified. Also, consider that the data sheet gives only the typical value for both the gain bandwidth product and the Aol curves. Generally, you can expect a variation of as much as ±30% from this value at room temperature and an additional error of ±30% over the specified temperature range. So, it is always advisable to include margin in your design when considering amplifier bandwidth.

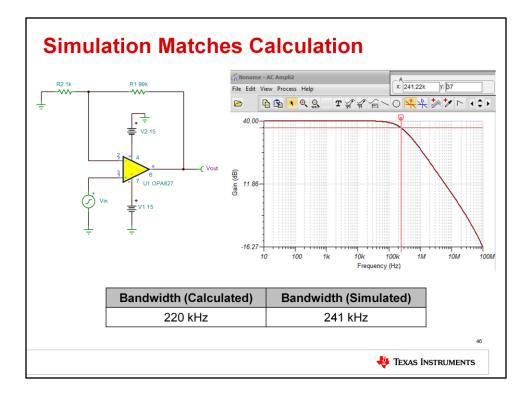

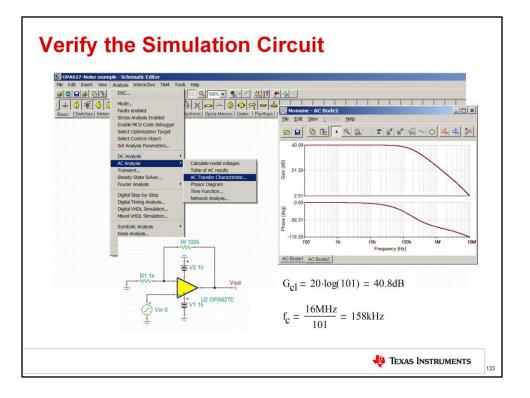

Let's now verify our bandwidth calculation with simulation. For the results to match, we must use the OPA827 in a non-inverting gain of 100V/V, or 40dB, like we did in the calculation on the last slide. If we run an AC transfer characteristic in TINA-TI, we see that the -3dB bandwidth, which occurs at 37dB since our DC signal gain is 40dB, is 241kHz. This matches well with our calculated bandwidth of 220kHz.

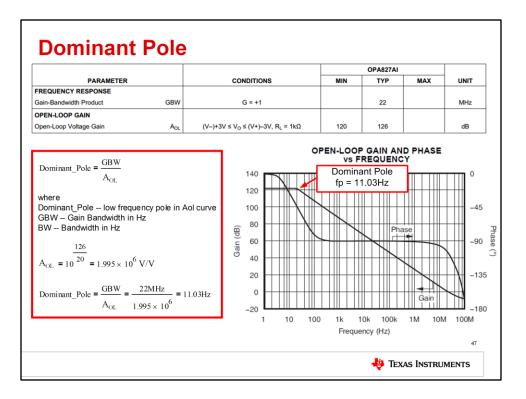

The dominant pole is the point on the Aol graph where Aol begins to roll off with frequency. This parameter is important when developing macromodels. The frequency of the pole can be estimated from the Aol curve, but a more accurate approach is to calculate it using this equation, where GBW is the gain bandwidth product and Avol is the open loop gain of the device.

Using the OPA827 as an example, we find the device has a gain bandwidth product of 22MHz and open loop gain of 126 decibels. We can convert 126dB to its linear representation using this equation.

Substituting 22MHz and 1.995 times 10 to the 6<sup>th</sup> for gain bandwidth and open loop gain, respectively, yields a dominate pole frequency of 11.03Hz. This calculation is consistent with the graph from the data sheet.

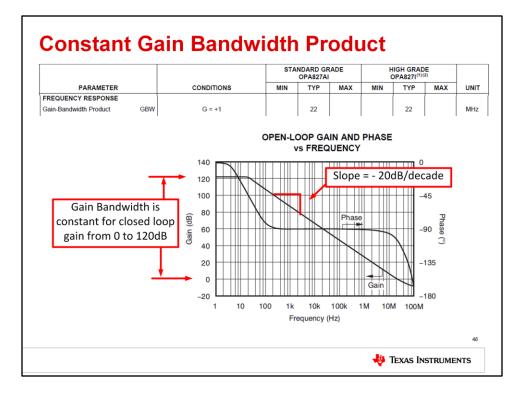

In this slide we further examine the OPA827 open loop gain curve. We see that the dc open loop gain is 120dB and remains constant until we reach the dominant pole. At frequencies greater than the dominant pole, the open loop gain decreases at a rate of -20dB per decade. Notice that for the OPA827 the slope of Aol is constant until we cross unity gain. Therefore the gain bandwidth product is constant for closed loop gains from 0 to 120 decibels.

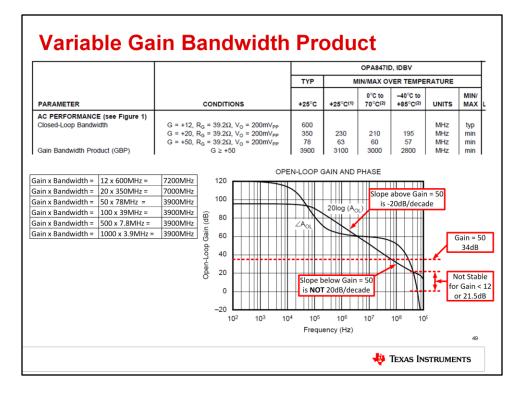

While it is common to have open loop gain curves decrease at a constant rate of 20dB per decade, it is not always the case. For example, let's take a look at the high-speed OPA847.

This slide shows the Aol curve for the OPA847, whose gain bandwidth product is defined for only a portion of the Aol curve. In this case it's defined only for closed loop gains greater than 50V/V.

Looking at the open loop gain curve, we see that for gains greater than 50V/V, or 34dB, the slope of the Aol curve is -20dB/decade. Therefore the gain bandwidth product is equal to 3900MHz for all closed loop gains greater than 50V/V.

However, as the gain decreases below 50V/V, the slope of Aol changes. Therefore, there is no gain bandwidth product specified. Instead, the closed loop bandwidth for particular gains is specified. Also notice that for gains less than 12V/V the phase margin indicates that the device is not stable. The table illustrates how the product of the gain and bandwidth is not constant for gains less than 50V/V, but is constant for gains of 50 or greater.

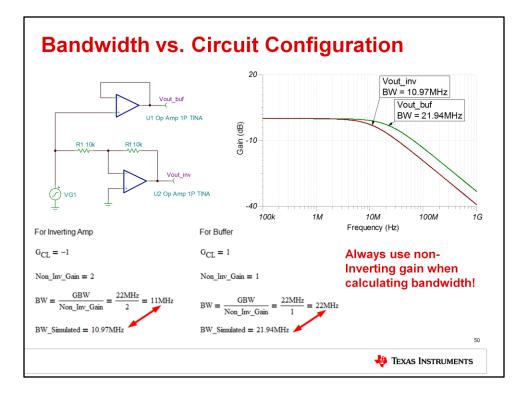

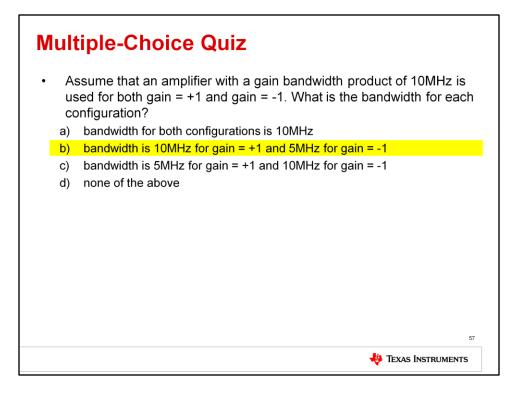

Earlier we calculated closed loop bandwidth for a non-inverting configuration using the gain bandwidth product. You might be surprised to learn that the bandwidth calculation for the *inverting* configuration is calculated using the *non-inverting gain*. Note that the non-inverting gain is typically referred to as noise gain.

This example shows the same amplifier connected in both an inverting and noninverting configuration. The inverting configuration has a gain of -1 and the noninverting configuration has a gain of +1. Let's start by calculating the bandwidth for the non-inverting configuration. The bandwidth for the non-inverting amplifier U1 is calculated by taking the gain bandwidth product and dividing by the non-inverting gain. So, for this example, the bandwidth is 22MHz divided by 1 which is equal to 22MHz.

On the other hand, the bandwidth of the inverting amplifier, U2, is calculated using the *non-inverting gain*. The gain with respect to the non-inverting input is calculated as Rf/R1 +1, which is 2 in this example. So, the bandwidth of the inverting amplifier is 22MHz divided by 2 which is 11MHz. A common mistake is to consider the gain seen by the signal source rather than the noise gain for bandwidth calculations involving inverting amplifiers.

This example is simulated to prove that the hand calculations are correct. Notice that the simulation and hand calculation results are very close to each other. This

simulation uses a simple single pole amplifier model to illustrate the relationship between bandwidth and circuit configuration.

| Op Amp | Typical GBW      | Typical I <sub>Q</sub> |

|--------|------------------|------------------------|

| OPA369 | 12kHz            | 0.8µA                  |

| OPA333 | 350kHz           | 17µA                   |

| OPA277 | 1MHz             | 790µA                  |

| OPA129 | 1MHz             | 1.2mA                  |

| OPA827 | 22MHz            | 4.8mA                  |

| OPA350 | 38MHz            | 5.2mA                  |

| OPA211 | 45MHz (Gain=1)   | 3.6mA                  |

| OPA835 | 51MHz (Gain=1)   | 250µA                  |

| OPA847 | 600MHz (Gain=12) | 18.1mA                 |

Finally, let's look at a number of op amps that depict a range of gain bandwidth products and their corresponding quiescent current, Iq.

In the slide we list Gain Bandwidth Products for different amplifiers that range from 12kHz to 600MHz. The OPA369, for example, is a very low bandwidth amplifier. This device is designed specifically to have very a low quiescent current of 0.8uA and is called a micro-power device. It is more common for amplifiers have bandwidth in the range of 1MHz like the OPA277. Some amplifiers like the OPA350 and OPA211 have wider bandwidth to facilitate driving A/D converters and for other wide bandwidth applications. For very high speed applications amplifiers like the OPA835 and OPA847 can be used. In general, the wider bandwidth op amps require more quiescent current. However, there are some exceptions , as displayed by the OPA835.

Let's return to our original problem, now that we understand the fundamentals of bandwidth. We have a non-inverting amplifier circuit with a closed-loop gain of 100V/V, or 40dB. The input is a 2mVpp sine wave at a frequency of 200kHz.

When we run an AC simulation of the circuit, we can see that at 200kHz, the closedloop gain has dropped to only 37.7dB. If we convert 37.7dB to linear gain of 76.7V/V and multiply by our input signal amplitude of 2mVpp, we get an expected output of 154mVpp. This matches perfectly with our transient simulation on the bottom-right!

| Multiple-Choice Quiz                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Different model amplifiers have different gain bandwidth products<br/>(GBW). Surveying many different models, you will see GBW vary<br/>from</li> </ul>                                                                                                        |

| a) 10Hz to 1kHz                                                                                                                                                                                                                                                         |

| b) 100Hz to 1MHz                                                                                                                                                                                                                                                        |

| c) 1MHz to 500MHz                                                                                                                                                                                                                                                       |

| d) 10kHz to 500MHz                                                                                                                                                                                                                                                      |

| <ul> <li>Amplifiers with wide bandwidth generally have</li> <li>a) lower l<sub>Q</sub> than amplifiers with narrow bandwidth</li> <li>b) higher l<sub>Q</sub> than amplifiers with narrow bandwidth</li> <li>c) low slew rate</li> <li>d) stability problems</li> </ul> |

| 55                                                                                                                                                                                                                                                                      |

| 🔱 Texas Instruments                                                                                                                                                                                                                                                     |

Hello, and welcome to the lecture for the TI Precision Lab discussing slew rate. In this lecture we'll go over the theory behind slew rate and compare the slew rate and current consumption of different TI amplifiers.

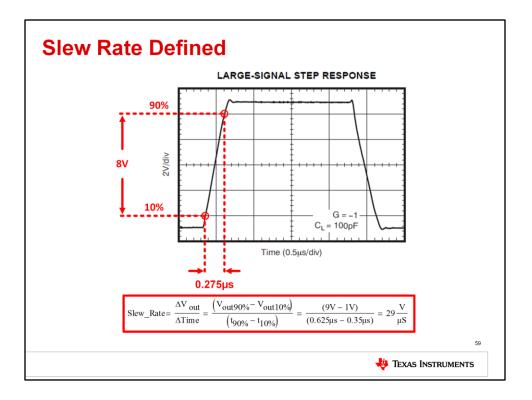

Slew rate is defined as the maximum rate of change of an op amp's output voltage and is given units of volts per microsecond. Slew rate is measured by applying a large signal step, such as 1V, to the input of the op amp, and measuring the rate of change from 10% to 90% of the output signal's amplitude.

The data sheet large-signal step response is an indication of the amplifiers slew rate. In this example, we calculate the slew rate to be about 29V/us. Again, the slew rate definition only considers the rate of change of the signal from 10% to 90%, which in this case is 1V to 9V.

Slew rate is a different specification than small-signal bandwidth, which considers differential input signals of  $\pm 100$  mV or less.

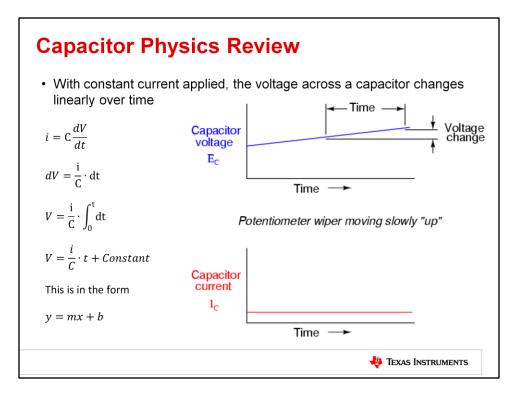

Before we get into an in-depth slew rate discussion, let's first review some basics.

The equation that defines how a capacitor works states that the current flow through a capacitor is equal to the capacitance times the derivative of voltage with respect to time. This behavior can also be interpreted to mean that if you have a constant current, then the voltage across the capacitor will rise linearly over time.

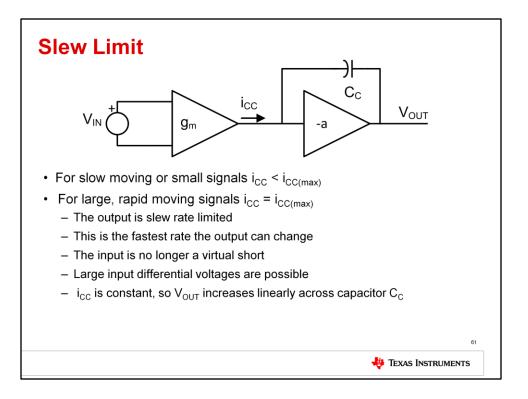

This is important with respect to slew rate of an amplifier. An amplifier has an internal  $g_M$ , or transconductance, stage which takes the input differential voltage and converts it to an output current,  $I_{CC}$ .  $I_{CC}$  flows into the next stage where it is used to charge  $C_c$ , which is called the Miller capacitance. If  $I_{CC}$  is a constant, then the voltage across  $C_c$  will rise linearly with time, just like we discussed on the previous slide.

For slow-moving signals,  $I_{CC}$  is less than some maximum value  $I_{CC_MAX}$ . This means that  $I_{CC}$  is able to change according to the differential input voltage without being limited. But for rapidly moving, large signals,  $I_{CC}$  reaches its maximum and becomes limited to some constant value. In this case the input to the amplifier will no longer be a virtual short, and therefore a differential voltage will develop across the input pins. Since  $I_{CC}$  is constant,  $V_{OUT}$  across the Miller capacitor  $C_C$  increases linearly over time. This is when the output of the amplifier is considered to be slew rate-limited, which is fastest that the output voltage can change.

| Op amp | Slew Rate (typ) | l <sub>Q</sub> (typ) |

|--------|-----------------|----------------------|

| OPA369 | 0.005 V/µs      | 0.862 µA             |

| OPA333 | 0.16 V/µs       | 17 µA                |

| OPA277 | 0.8 V/µs        | 790 µA               |

| OPA129 | 2.5 V/µs        | 1.2 mA               |

| OPA350 | 22 V/µs         | 5.2 mA               |

| OPA211 | 27 V/µs         | 3.6 mA               |

| OPA827 | 28 V/µs         | 4.8 mA               |

| OPA835 | 110 V/µs        | 250 µA               |

| OPA847 | 850 V/µs        | 18.1 mA              |

Here we compare the typical slew rate and quiescent current, or IQ, for different amplifiers.

On one end of the spectrum, we have the OPA369 which is a very low  $I_Q$  and low slew rate device. For 0.8µA of current we can achieve around 5mV/µs of slew. Compare that to the OPA847, which consumes 18.1mA of  $I_Q$  but can slew at 850V/µs. This shows us that amplifiers with higher slew rate, and therefore higher bandwidth, tend to have higher current consumption.

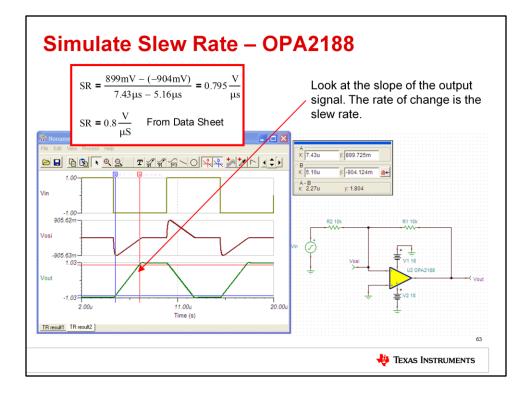

We can easily simulate slew rate using TINA-TI. Simply apply a step function to the input of the amplifier, which in this case is a  $\pm 1V$  square wave. You can see that when this input step is applied, the input offset voltage changes from 0V - which indicates a virtual short - to some other voltage, around 900mV in this case. Most importantly, the output voltage becomes slew rate-limited, shown as a constant ramp in voltage over time until finally reaching its true value. You can observe the input offset voltage moving linearly back to 0V as well.

Calculating the slew rate from this plot gives a result of  $0.795V/\mu s$ . The data sheet for this device, the OPA2188, lists the slew rate as  $0.8V/\mu s$ , indicating that the model accurately simulates the slew rate of the amplifier.

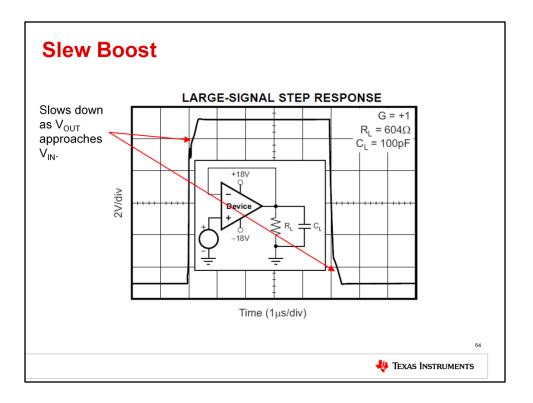

Some amplifiers include a "slew boost" circuit which allows for faster slew rates. An example of an amplifier with slew boost is shown in this large-signal step response plot. What happens is that the device has two different slew rates – an initial rate which is very fast, and a second, slower rate as the output settles to its final value. You may ask yourself, "why doesn't the amplifier just have one slew rate which is always fast?" The reason is that with one, extremely fast slew rate, the output would have a large overshoot. When that overshoot occurred, the amplifier would try to compensate for this and the negative slew would kick in, resulting in a large negative overshoot. This behavior would continue, resulting in oscillation.

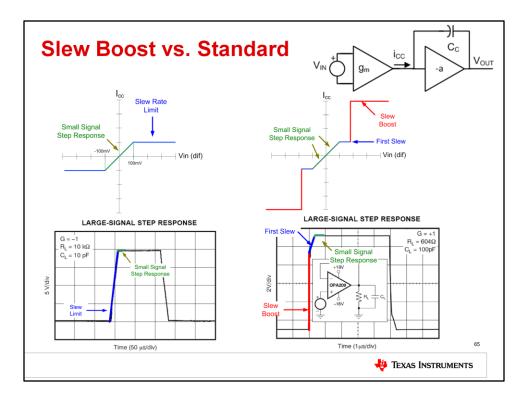

- So how does this slew boost look compared to a standard amplifier? On the left hand side is the response of a standard amplifier. The green region shows the small-signal response (or differential input voltage greater than ±100mV), where the amplifier can linearly change the current flowing into the Miller capacitance. The blue region shows the large-signal response (or differential input voltage greater than ±100mV), where the amplifier reaches its slew rate limit and the current flow into the Miller capacitance is held constant..

- We have a similar situation for an amplifier with slew boost. There is still a smallsignal response shown by the green region, but once the differential input voltage exceeds a certain value we reach the slew rate limit, indicated by the blue region, and eventually the slew boost, indicated by the red region. Therefore, when a large step function is applied to the input of the amplifier, the device will initially see a large differential input voltage and will be in Slew boost mode, allowing a large output current into the Miller capacitance and therefore a quickly-ramping output voltage. As the differential input voltage decreases the amplifier will move to its standard slew rate, and finally to its small-signal response once the input voltage becomes small enough. At this point the output will settle and the inputs of the amplifier will once again be a virtual short.

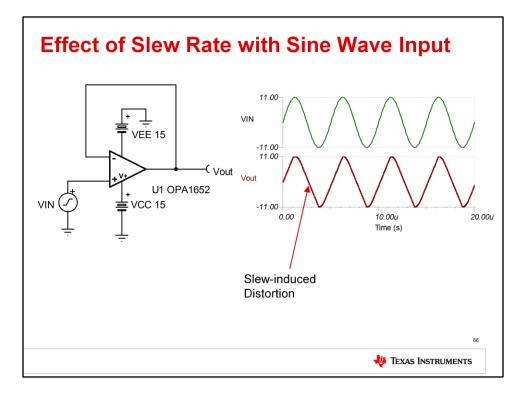

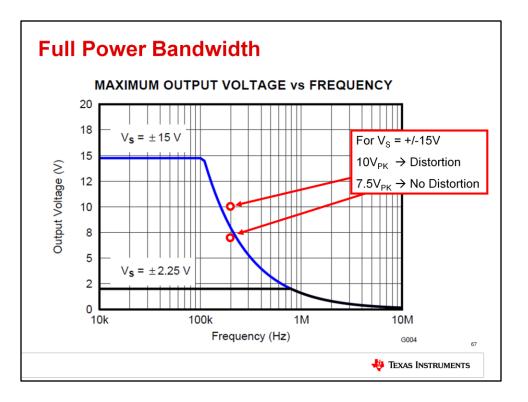

The slew rate of an op amp also impacts sinusoidal signals. If the op amp attempts to swing its output voltage past a certain frequency and amplitude which exceed the slew rate, the output will become distorted and will start to look more like a triangle wave. This limitation is called the full power bandwidth of the op amp.

The graph above shows the maximum output sinusoidal waveform that can be generated without slew-induced distortion. This example considers a 200kHz signal at both 7.5Vpk and 10Vpk. At 7.5Vpk, the output signal is under the curve and therefore will not be distorted by slew rate limitations. At 10Vpk, the output signal is above the curve and will be distorted by slew rate limits.

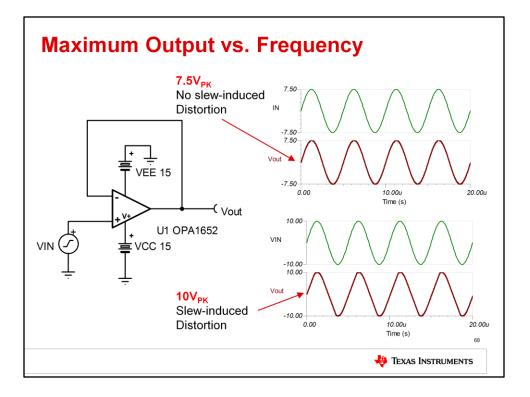

Let's simulate the conditions of the previous slide. With 7.5Vpk output, the response is sinusoidal with minimal distortion. However, with 10Vpk output, in a condition outside the full power bandwidth curve, the device is slew-rate limited and the output distorts.

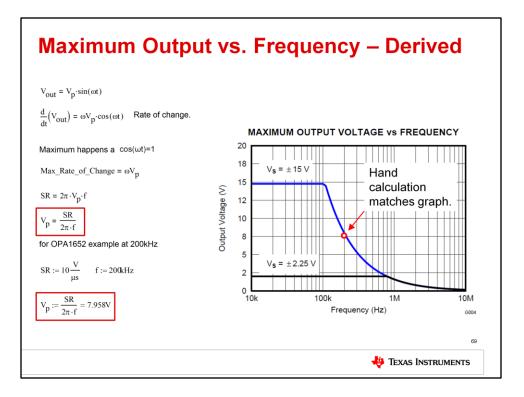

This slide illustrates that the maximum output vs. frequency curve can be derived with calculus. You can go through the math on your own, but the key point is that the final equation, Vpk = SR / (2 PI f) can be used if this curve is not available. The example shown in red confirms that the equation yields the same result as the curve.

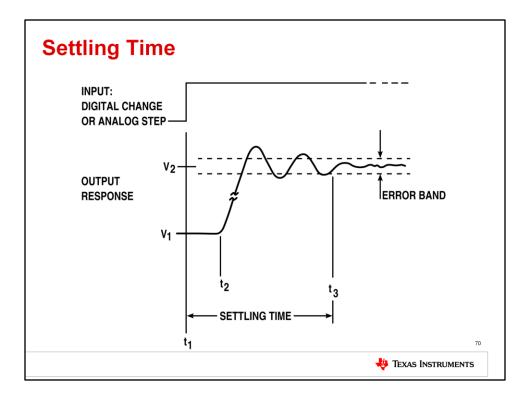

Let's now move on to discuss settling time.

Settling time is the time required for the amplifier's output to reach and stay within a certain error band after a large-signal step is applied to the input. The error band can either be specified in terms of percentage or number of LSBs (for an ADC with a specified number of bits).

Because the input is a large-signal step, the amplifier is in slew rate limit. The tighter the error band is (i.e. smaller error percentage), the longer the settling time will be. Capacitance, closed loop gain, and loading will also effect settling time.

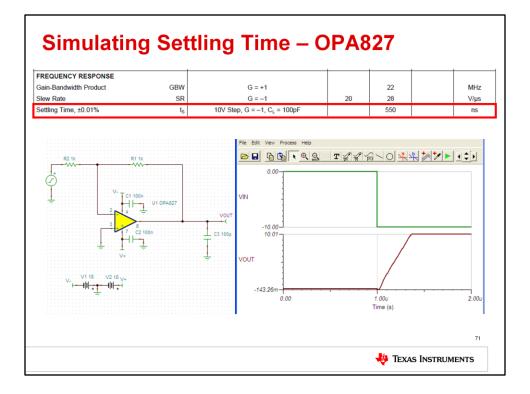

We can very easily simulate the settling time of an op-amp using TINA-TI's transient analysis function. In order to do this, it is important to closely follow the data sheet test conditions, such as the step size, gain configuration, and load capacitance.

In this case we are testing the OPA827 in a gain of -1, with a 10V step input and 100pF of load capacitance.

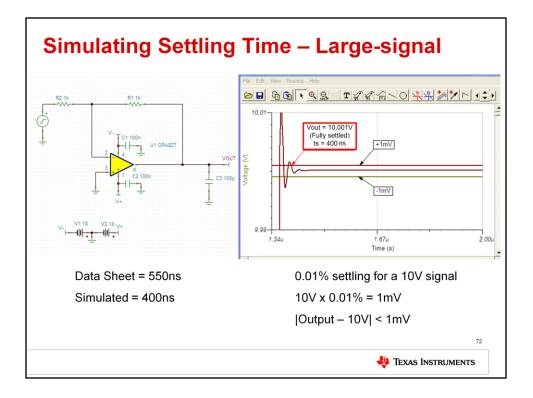

The settling behavior, with some overshoot and damped oscillations, can really be seen once we zoom in on the plot. In this example, the output settles after an over shoot and one cycle of ringing, for a total settling time of 400ns. This is acceptably close to the typical data sheet value of 550ns.

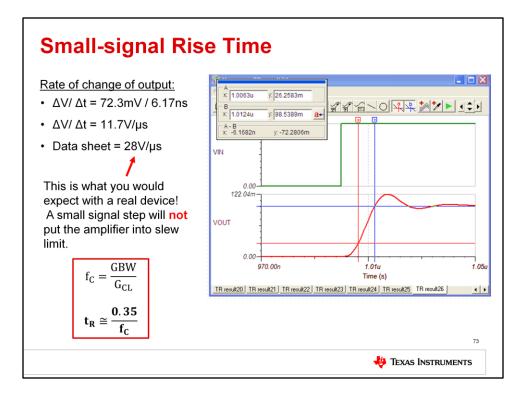

Here we observe the **small-signal** rise time of the same circuit, for purposes of comparison to the large-signal slew rate. Again, let's zoom in on the rising edge of the small signal step response. Measuring delta V over delta T from 10% to 90% of the output swing, me get a rise time of  $11.7V/\mu s$ . Compare this to the data sheet slew rate value of  $28V/\mu s$  – they're quite different!

Where does the difference in this behavior come from? Well, as you may remember from earlier, a large-signal step input puts an op-amp in slew limit and therefore forces it outside of its normal linear operation. A small-signal step input, on the other hand, allows the op-amp to operate in its linear region and therefore the rise time is based on the op-amp's bandwidth.

The equation to calculate 10% to 90% rise time is given here. It is derived from the properties of a single-pole system.

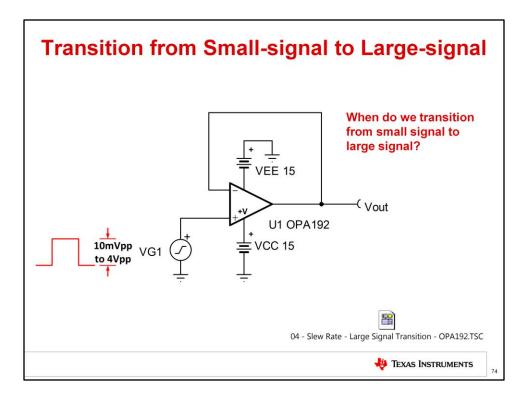

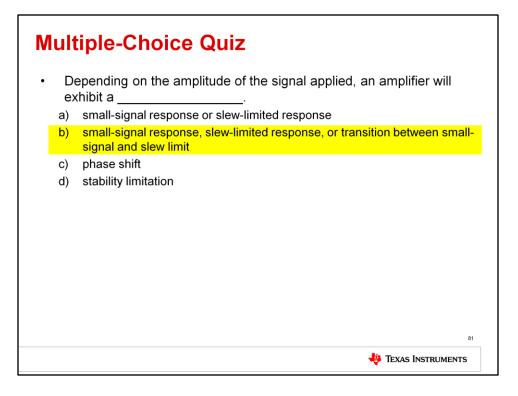

An amplifier's small-signal or large-signal behavior, like most things in the real world, isn't fully black and white. The way in which a circuit operates is not always fully large-signal or small-signal. In fact, there's a gradual transition between these two operating conditions.

Here we have a simple op amp circuit configured as a non-inverting buffer. We'll apply a range of input steps, from 10mVpp to 4Vpp, and observe the output. A transient simulation done in TINA-TI will allow us to observe whether the circuit shows small-signal or large-signal behavior.

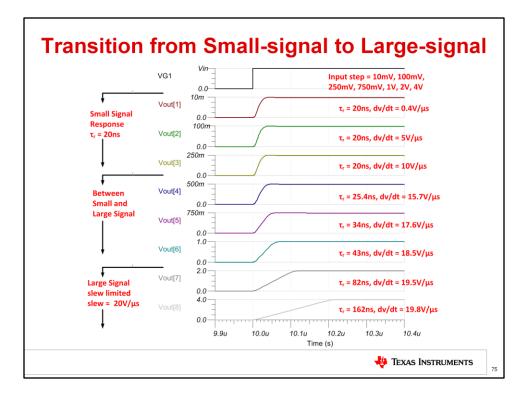

This figure illustrates the output of the non-inverting buffer circuit from the previous slide, versus different input step sizes.

Notice that the output rise time is a constant 20ns for input steps of 10mV to 250mV. Because the rise time is constant, we know that the response is small-signal. The device in this example, the OPA192, has a slew rate of 20V/us. You can see that the rate of change for the small step response is lower than the slew rate. Also, notice that the output signal increases exponentially for the small signal response, as opposed to the linear increase for amplifiers that are slew rate-limited.

For input steps between 500mV and 1V, the amplifier is transitioning between smallsignal and large-signal response. In this region the rise time is no longer constant; however, the amplifier is not yet at the full slew rate of 20V/us.

For input steps greater than 1V, the amplifier is slew rate-limited. You can see that the rate of change of the output signal is at the slew rate limit of about 20V/us. Also, notice that the output signal increases linearly in response to the input step.

In this example, input signals less than 250mV caused a small signal response and signals greater than 1V caused a large signal response. However, this transition depends on the amplifier's design and technology. CMOS amplifiers tend to reach slew limit for signals greater than 100mV, and bipolar amplifiers can slew limit at even lower input voltages. Note that the industry standard for small signal response is a 100mV step, but in practice the actual limit may be lower.

Because of the way the output signal is scaled in this figure, it is possible to be tricked into thinking that the slew rate limited signal at the bottom of the figure is moving more slowly then the small signal response at the top of the figure. This is not the case, and the next slide will provide further clarification.

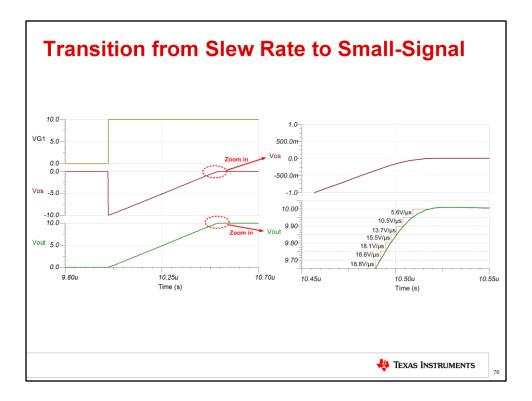

Let's take a closer look at the output of the non-inverting buffer circuit with a 10V step applied to the input.

In this case, the device is in slew-rate limit of 20V/us. However, when the signal approaches the final value of 10V, the op amp will transition to a small signal response. Zooming in on the last 300mV of the signal swing, you can see that the rate of change of the output decreases from approximately the slew rate, 20V/us, to a lower rate of change such as approximately 5V/us. Also, you can see that the shape of the output changes from the linear rise associated with slew rate limit, to the exponential behavior associated with small signal response.

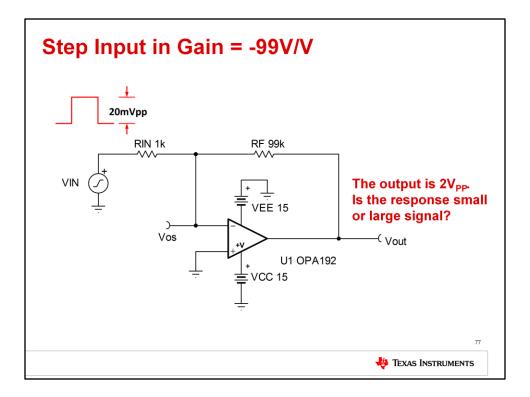

Most of the examples discussed thus far have been basic buffer circuits, also called unity-gain followers. Now let's look at amplifiers with different closed loop gains in order to see the effect that closed loop gain has on output response.

Here we show an inverting amplifier circuit in a gain of -99V/V. The input is a small signal step of 20mVpp. Based on the gain, the output should be approximately 2Vpp. Does the output respond as a small signal or as a large signal?

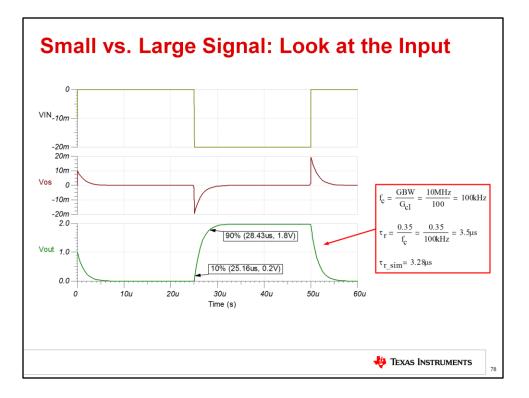

This is the simulated output response of the circuit from the previous slide. Notice that the output signals rise and fall in an exponential way, which indicates a small-signal response. Also, if we use the small signal rise time formula from before, we can see that the calculated rise time of 3.5us is very close to the simulated rise time of 3.28us. Thus, the amplifier responds to the 20mV input step as a small signal, and we can conclude that the amplitude of the *input* signal determines the behavior of the op amp. The output signal amplitude does not determine whether the response is small or large signal.

| ult            | tiple-Choice Quiz                                                                                                                      |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                | /hen a constant current is applied to a capacitor, the voltage on the apacitor will                                                    |

| a)             | increase exponentially                                                                                                                 |

| b)             | increase linearly                                                                                                                      |

| C)             | remain constant                                                                                                                        |

| d)             | oscillate                                                                                                                              |

| Sl<br>a)<br>b) | ew rate is defined as<br>the maximum rate of change of an input signal<br>the maximum frequency that can be applied before attenuation |

| C)             | the maximum rate of change of the output voltage                                                                                       |

| d)             | the rate of current consumption of the amplifier                                                                                       |

|                | 79<br>View Texas Instruments                                                                                                           |

|                | W<br>ca<br>a)<br>b)<br>c)<br>d)<br>SI<br>a)<br>b)                                                                                      |

| Multiple-Choice Quiz                                                                                                      |        |  |

|---------------------------------------------------------------------------------------------------------------------------|--------|--|

| Settling time is the                                                                                                      |        |  |

| a) Rise time from 10% to 90% of the output voltage                                                                        |        |  |

| <ul> <li>b) Time starting from when the input step is applied until the output is w<br/>a specified error band</li> </ul> | vithin |  |

| c) time from the overshoot peak to the final dampened oscillation                                                         |        |  |

| <ul> <li>Is settling time longer for a 0.1% or 0.01% error band?</li> </ul>                                               |        |  |

| a) 0.1%                                                                                                                   |        |  |

| b) 0.01%                                                                                                                  |        |  |

|                                                                                                                           |        |  |

|                                                                                                                           |        |  |

|                                                                                                                           |        |  |

|                                                                                                                           |        |  |

|                                                                                                                           |        |  |

|                                                                                                                           | 80     |  |

| 👋 Texas Instrum                                                                                                           | IENTS  |  |

Hello, and welcome to the lecture for the TI Precision Labs discussing intrinsic op amp noise, part 1. In this lecture we'll show how to predict op amp noise with calculation and simulation, as well how to accurately measure noise.

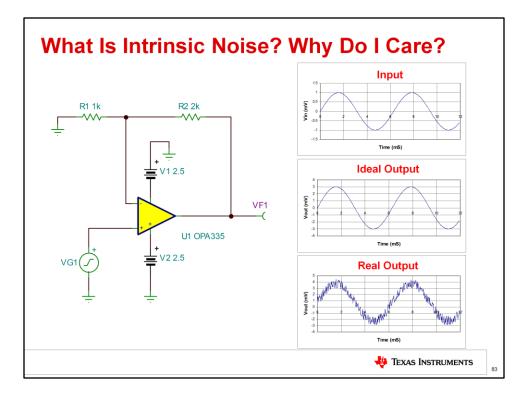

Noise can be defined as an unwanted signal that combines with a desired signal to result in an error. In audio, for example, noise can be noticed as a hiss or popping sound. In a sensor system, noise can be an error in the measured sensor output, such as pressure or temperature.

Noise can be categorized into two basic groups: extrinsic and intrinsic. Extrinsic noise is noise produced from some external circuit or natural phenomena. For example, 60Hz power line noise and interference from mobile phones are common examples of extrinsic noise. Cosmic radiation is another example of a natural phenomenon that causes extrinsic noise. Intrinsic noise is caused by components within a circuit. Resistors and semiconductor devices generate noise, for example.

Intrinsic noise is very predictable, where as extrinsic noise is typically difficult to predict. In this noise lecture, we will focus on intrinsic noise. As we mentioned before, our discussion will focus on how to calculate, simulate, and measure noise. We will also discuss techniques for reducing noise.

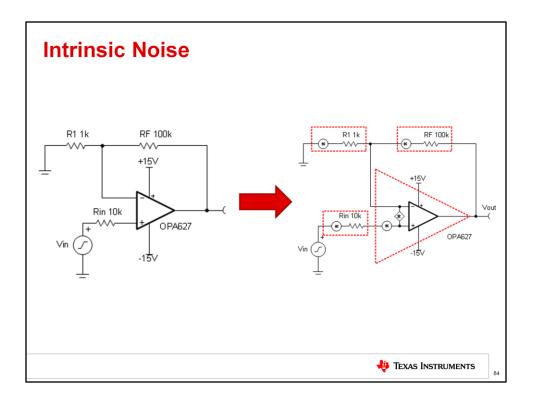

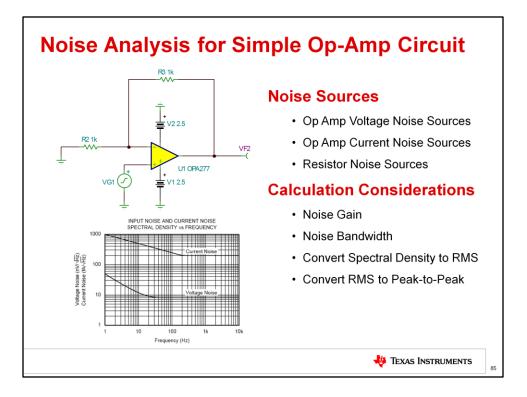

This slide illustrates how an amplifier circuit can be translated into a noise equivalent circuit.

Each resistor has a noise voltage source associated with it. The noise voltage source is denoted by a circle with an asterisk inside. The amplifier also has a noise voltage source and a noise current source. The noise current source is denoted by a diamond with an asterisk inside. The magnitude of the noise sources inside the amplifier is given in the amplifiers data sheet. The magnitude of the noise associated with the resistor is dependent on the resistance value and can be calculated.

We will soon learn how to combine the effects of all the noise sources to determine the total output noise. But first, lets look at some general categories of noise.

The noise analysis will involve looking at op amp noise voltage sources, op amp noise current sources, and resistor noise sources. The gain and bandwidth limitations of the op-amp will also effect the total noise calculation.

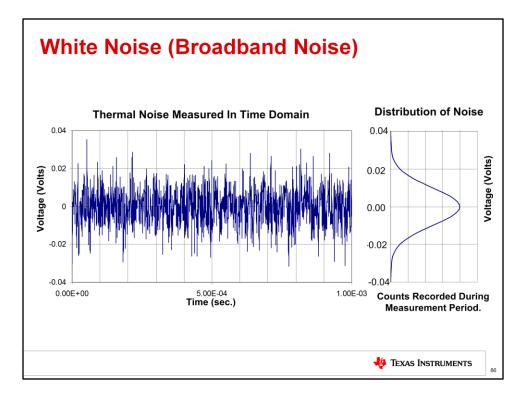

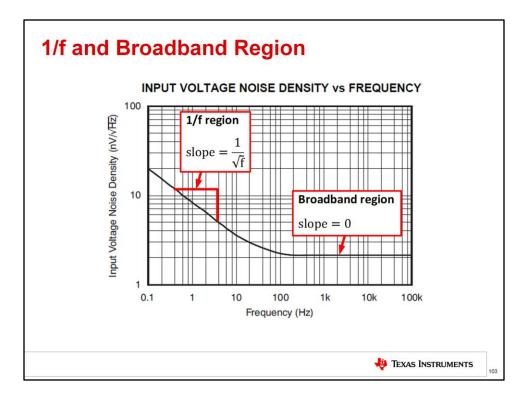

This slide shows the time domain waveform for white noise, also known as broadband noise. The time domain waveform is what you would see if you measured noise with an oscilloscope. Notice that the horizontal axis is 1ms, full scale. Taking the reciprocal of the full-scale time gives a frequency of 1kHz. In general, broadband noise is considered to be in the middle to high frequency range; that is, frequencies greater than 1kHz. In the next slide we'll consider lower frequency noise sources.

Also notice the statistical distribution to the right hand side of the slide. The distribution is Gaussian, with a mean value of OV and the skirts of the distribution at approximately ±40mV. The distribution indicates that the probability of measuring noise near OV is high, where as the probability of measuring noise near the skirts of the distribution is relatively low. Later we will see how the distribution can be used to estimate the peak-to-peak value of the noise signal.

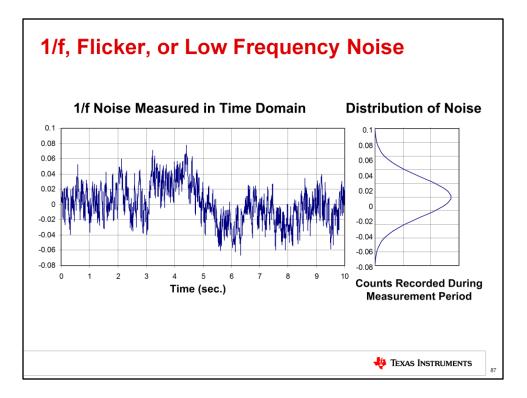

Flicker noise, also known as 1/f or low frequency noise, is another category of noise. This slide shows the time domain waveform, as well as the statistical distribution for 1/f noise. The time domain waveform is what you would see if you measured noise with an oscilloscope. Notice that the horizontal axis is 10s full scale. Taking the reciprocal of the full scale time gives a frequency of 0.1Hz. In general, 1/f noise is considered to be in the low frequency range; that is, frequencies less than 1kHz.

As we have already seen, the various categories of noise have many synonyms. For example, broadband noise is also called white noise, Johnson noise, thermal noise, and resistor noise. It can become very confusing to engineers that are new to this subject when literature and presentations switch between these different terms.

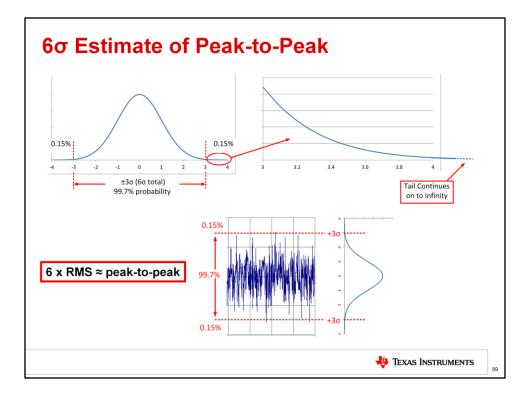

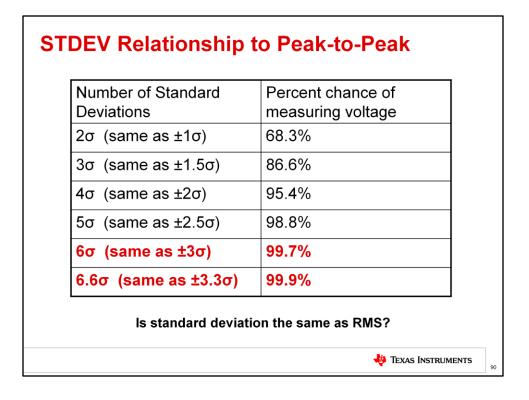

Multiplying the rms noise by 6, or even 6.6, is a common estimate for peak-to-peak noise. Remember that noise has a Gaussian distribution. The Gaussian distribution tells us that there is a 99.7% probability that any reading in time is within the limits of +/- 3 standard deviation or 6 standard deviations total. This means that there is a finite probability of 0.3% that a noise reading will be outside of this limit. Sometimes 6.6 standard deviations is used, because the probability of noise being inside of the limits is increased to 99.9%. It is important to realize that the tails of the Gaussian distribution extend infinitely, so there is no number of standard deviations that will produce a 100% probability that all noise is inside of the bounds. Thus, 6 or 6.6. are used as good estimates. One final thing to keep in mind is that RMS and standard deviation are equivalent for noise signals with no mean value. This is generally true for the intrinsic noise that we are considering.

The table shown here relates the number of standard deviations to the probability that a measurement is bounded by this range. For example, there is a 68% chance that any instantaneous noise measurement will be in the range of  $2\sigma$ , or  $\pm 1$  standard deviation.  $6\sigma$  and  $6.6\sigma$  are common ways of estimating the peak-to-peak noise. In the case of  $6\sigma$ , for example, there is a 99.7% chance that any instantaneous measurement will occur within that range. Thus, the chance that a noise reading is outside this limit at any instant in time is only 0.3%. The 0.3% probability is considered to be negligible, so  $6\sigma$  is often used as an approximation for peak-to-peak noise.

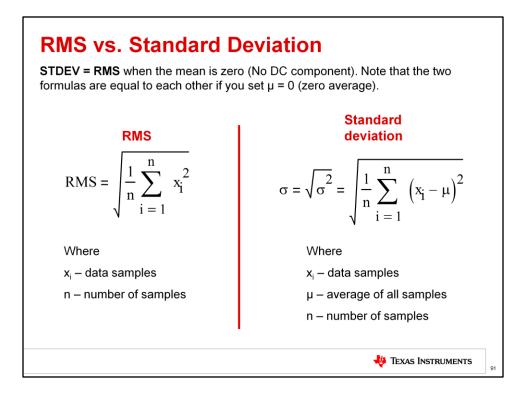

If you are familiar with noise analysis, you may have heard the terms standard deviation and RMS used interchangeably. This leads one to wonder, is RMS equivalent to standard deviation?

## So, the question is does RMS = standard deviation?

The answer is both yes and no! If the signal has no DC offset, the answer is yes. This is the case for most noise signals. Notice that the equation for RMS and standard deviation are the same, except that the standard deviation equation subtracts out the average, or dc offset.

In the case where a signal has a DC offset, RMS will not be equal to the standard deviation. Fortunately, op-amp and resistor noise do not have a DC offset, so we can consider RMS to be equivalent to the standard deviation in these cases. Some extrinsic noise, such as digital switching noise, may not be symmetrical and thus will have a DC offset. It is important to note, however, that some instruments or simulation tools will report RMS noise including the offset term (AC + DC) and others will report RMS without the offset term (AC only).

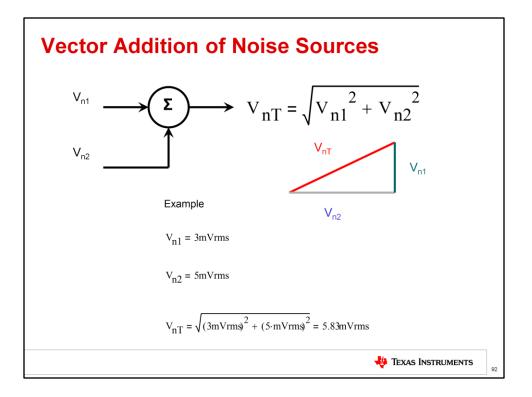

An important concept in nose analysis is adding noise values. Noise cannot be added algebraically, for example, 3+5=8. Noise must be added as a vector as shown here, where we take the square root of 3mVrms squared plus 5mVrms squared for a result of 5.83mVrms. It is important to note that this relationship applies only to uncorrelated ,random noise. If the noise source is correlated, a different formula applies.

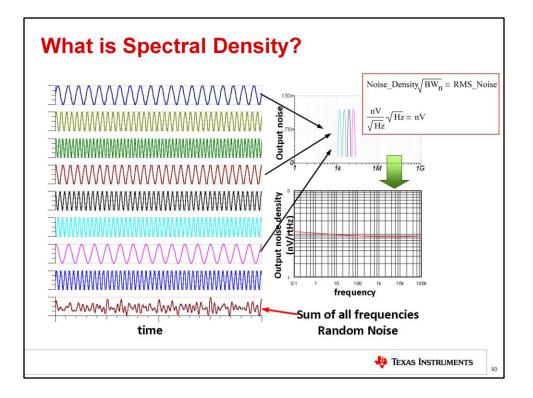

Do you remember that white light is the combination of all colors? Well, white noise is the combination of all frequencies. This figure shows that when you add several signals of different frequencies together in the time domain, the result is a random looking signal. In the frequency domain, each one of these signals looks like an impulse. Combining an infinite number of these signals across all frequencies creates what is called a noise spectral density curve.

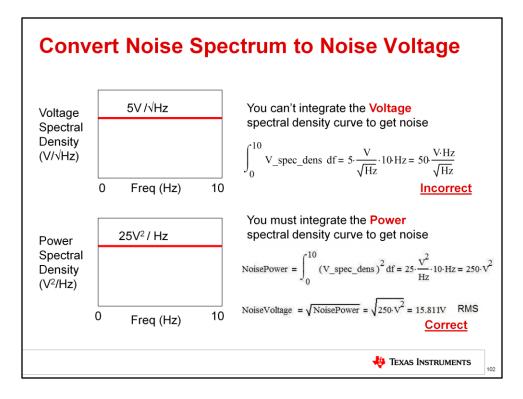

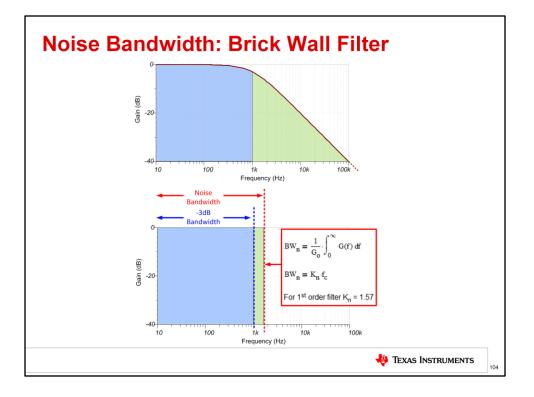

Voltage Noise Spectral Density is often a confusing parameter to engineers who are not familiar with noise analysis. Spectral density has units of nV per square root Hertz. Multiplying spectral density by the square root of the noise bandwidth gives the RMS noise as shown in the equation on the top right. Looking at the units in the equation, you can see how the square root Hertz cancels out.

The spectral density curve is the main amplifier specification used to describe an amplifier's noise characteristics. In this lecture we will use the spectral density curve extensively in noise calculations.

At this point we have introduced many of the fundamentals needed to understand noise.

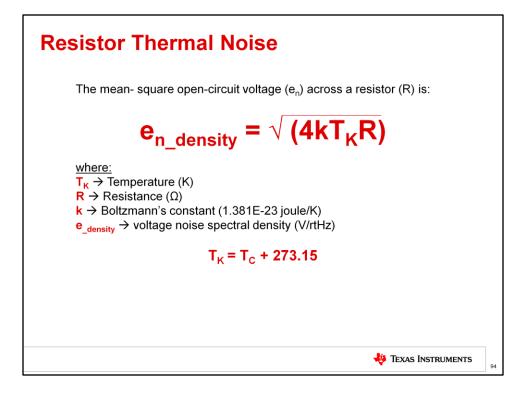

This slide shows how to calculate the noise produced by a resistor. This noise is generated by the random motion of charges within the resistor.

The equation shown above gives the total RMS noise generated by a resistor. Notice that the equation requires the temperature in Kelvin, the resistance, the bandwidth, and Boltzmann's constant. Dividing both sides of the equation by the square root of the bandwidth yields the voltage spectral density equation.

Remember that amplifiers' noise specifications are usually given in terms of spectral density. Determining the noise spectral density for a resistor is useful, because it allows for easy comparison of the noise generated by resistors and the noise generated by amplifiers.

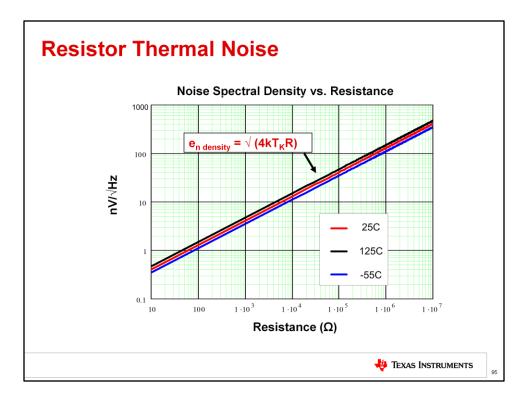

This plot was generated using the equation given in the last slide. Note that the equation was divided by the square root of bandwidth to give a spectral density, which is useful because it provides a quick way of comparing resistor noise to op-amp noise. Remember, most op-amps specify noise in nV/V(Hz).

A very low noise amplifier may have intrinsic noise of 1nV/V(Hz) noise. Comparing to this plot, 1nV/V(Hz) corresponds to a resistor value of approximately 70 ohms. Thus, for this example, op-amp you should try to use resistors of 70 ohms or less. For best performance, it's recommended for the amplifier in a circuit to generate more noise than the resistors. Low noise amplifiers can be expensive, and you would not want to pay extra for an expensive low noise amplifier and have resistor noise dominate the circuit's noise performance.

Neglecting resistor noise is a very common oversight of engineers who are new to noise analysis. For this reason, it is useful to have this chart available for quick reference.

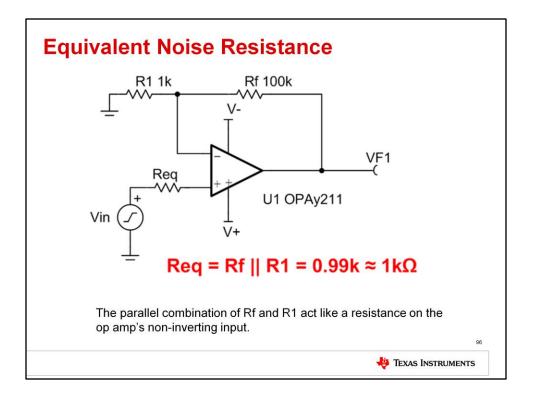

For noise calculations, it is often necessary to calculate Req, the equivalent resistance seen by the input. The most common method for calculating Req is given here. The parallel combination of Rf and R1 act like a resistance on the op amp's non-inverting input, so Req in this example has a value of approximately 1k.

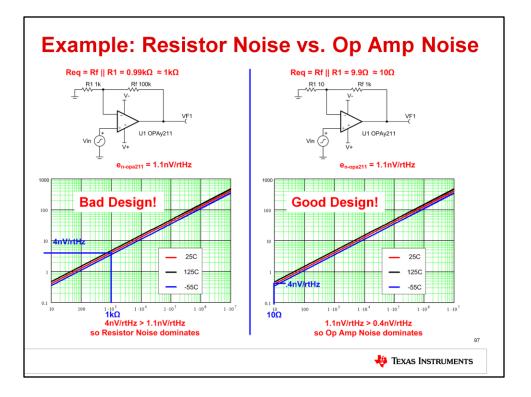

Let's compare resistor/thermal noise to op amp noise in two different circuits.

On the left, resistances of 1k and 100k are used. Req is roughly 1k, which according to the graph has a noise density of about  $4nV/\sqrt{Hz}$ . This is greater than the noise density of the OPA211, so the circuit is dominated by resistor noise.

On the right, the same circuit but with resistances of 10 ohms and 1k are used. Req is now roughly 10 ohms, which has a noise density of about 0.4 nV/ $\sqrt{Hz}$ . This is much less than the noise density of the OPA211, so the op amp noise dominates. This situation is most desirable for low-noise performance.

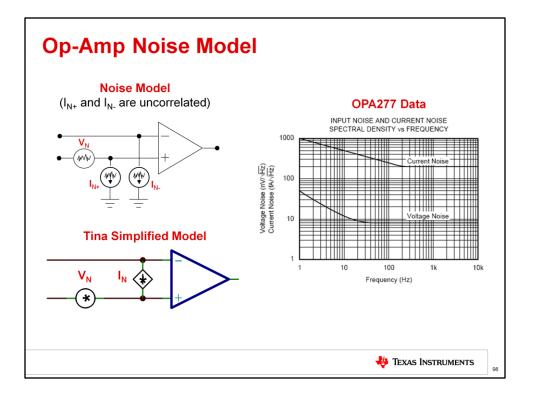

This slide show the typical op-amp noise model. In some cases, it is important to have two separate current noise sources, as shown in the upper left. In other cases, the simplified model with a single noise source between the inputs is adequate. The noise sources represent the spectral density curves. In the following lecture discussing noise, we will learn how to use the op amp noise model to predict the total peak-to-peak output noise for different amplifier configurations.

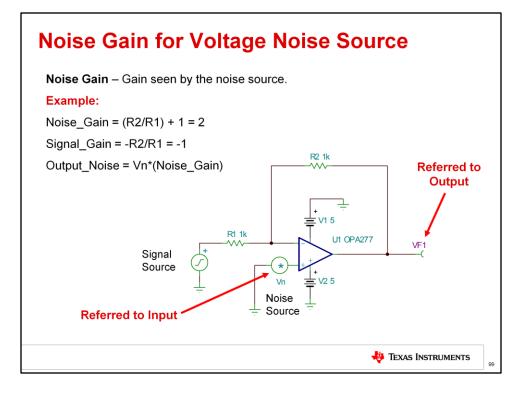

A key concept that we must understand before doing a noise analysis is **noise gain**. Noise gain is the gain seen by the noise voltage source, which is always on the noninverting input of the amplifier. It can be different from the signal gain. The example above shows a circuit with a noise gain of 2 and a signal gain of -1. In other words, the circuit is an inverting amplifier with respect to the signal source, but a noninverting amplifier to the noise voltage source.

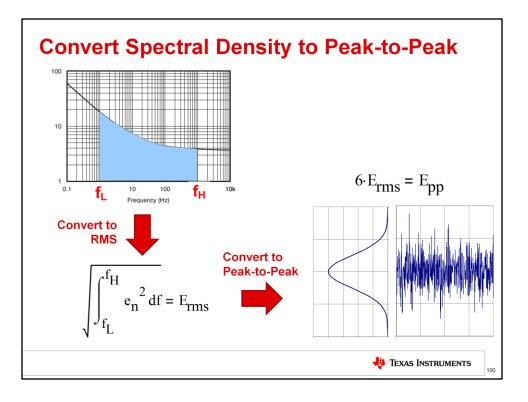

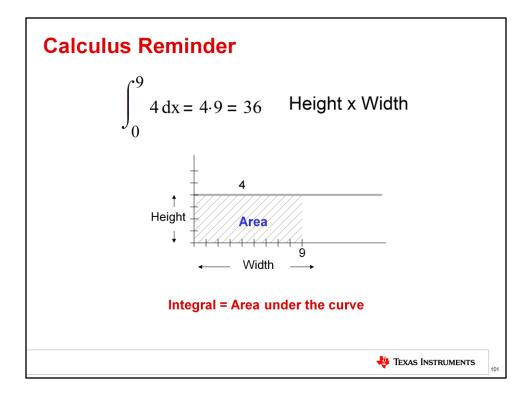

This slide summarizes the general procedure for converting voltage spectral density to RMS noise voltage, and for converting RMS to peak-to-peak voltage. To convert voltage spectral density to RMS, you must square the voltage spectral density, integrate across the desired bandwidth, and take the square root of the result. This is effectively integrating the power spectral density and taking the square root to convert back to voltage or current. Remember that  $P = V^2 / R$  and  $P = I^2 x R$ . We will discuss this in more detail soon.

Once the RMS noise voltage is calculated, it can be converted to peak-to-peak by multiplying by 6. The factor of 6 is a statistical estimate, representing  $\pm 3$  standard deviations or  $6\sigma$ , and there is a 0.3% chance that noise will exceed the peak-to-peak estimate at any instant in time.