# Application Brief **Optimizing Industrial Robot CPU Boards with Logic and Voltage Translation**

TEXAS INSTRUMENTS

Owen Westfall

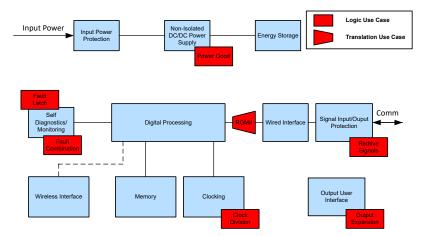

### **Functional Block Diagram**

For the purpose of this report, a simplified robot CPU board block diagram is used to illustrate the logic and translation use cases, see Figure 1. Each red block has an associated use-case document. Links are provided in Table 1 and Table 2. For a more complete block diagram, see the *Robot CPU Board Products and Reference Design* pages.

Figure 1. Simplified Block Diagram for Robot CPU Boards

### Logic and Translation Use Cases

Each use case is linked to a separate short document that provides additional details including a block diagram, design tips, and part recommendations. The nearest block and use-case identifiers are listed to match up exactly to the use cases shown in the provided Simplified Block Diagram for Robot CPU Boards.

| Nearest Block                   | Use-Case Identifier | Use Case                                           |

|---------------------------------|---------------------|----------------------------------------------------|

| Self-Diagnostics/Monitoring     | Fault Latch         | Catch a Digital Pulse<br>Multiple Fault Monitoring |

|                                 | Fault Combination   | Use Fewer Inputs to Monitor Error Signals          |

| Clocking                        | Clock Division      | Dividing a Clock                                   |

| Non Isolated DC/DC Power Supply | Power Good          | Combine Power Good Signals                         |

| Signal Input/Output Protection  | Redrive Signals     | Redrive Digital Signals                            |

| Output User Interface           | Output Expansion    | Drive Indicator LEDs                               |

## Table 1. Logic Use Cases

1

| Table 2. Translation Use Cases |                     |                              |  |  |

|--------------------------------|---------------------|------------------------------|--|--|

| Nearest Block                  | Use-Case Identifier | Use Case                     |  |  |

| Wired Interface                | RGMII               | Translate Voltages for RGMII |  |  |

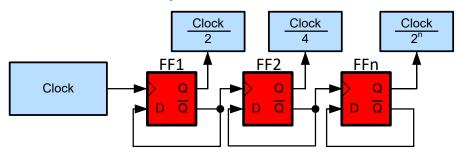

#### **Dividing a Clock**

It is common to see clocks be used in industrial robot CPU boards however not all devices are able to use the clock at its fastest. For devices to be able to operate, the user can divide the clock by using D-type flip-flops(DFF). Using DFFs to divide your clock frequency will result in values of  $\frac{clock}{2^n}$  where n is the number of

DFFs connected in series. This is shown in Figure 2.

Figure 2. Example of Dividing a Clock

#### **Design Considerations**

- · Effect can be accomplished using a counter

- Latched devices start in an unknown state [FAQ] What is the default output of a latched device? (Flip-Flop, latch, register)

- Depending on propagation delays the clock will not only be delayed but also behind by a few nanoseconds.

- [FAQ] How do I Calculate Power Consumption for my CMOS Logic Device?

- Need additional assistance? Ask our engineers a question on the TI E2E™ Logic Support Forum

#### Table 3. Recommended Parts

| Part Number     | Automotive<br>Qualified | Operating Voltage<br>Range | Features                                                                                                  |

|-----------------|-------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------|

| SN74AUP1G74     |                         | 0.8 V to 3.6 V             | AUP family logic devices are extremely low power, and fast; $I_{CC}$ < 0.9 $\mu\text{A};t_{pd}$ 5 - 10 ns |

|                 |                         |                            | Clear and preset                                                                                          |

| SN74AUP1G80     |                         | 0.8 V to 3.6 V             | AUP family logic devices are extremely low power, and fast; $I_{CC}$ < 0.9 $\mu\text{A};t_{pd}$ 5 - 10 ns |

|                 |                         |                            | Only inverted Q output                                                                                    |

| SN74AUC1G74     |                         | 0.8 V to 2.7 V             | Extremely high speed at 1.8 V; t <sub>pd</sub> < 2.4 ns                                                   |

| SN74LVC1G374    |                         |                            | High drive strength 32 mA                                                                                 |

| SN74LVC1G374-Q1 | 1                       |                            | 3-State outputs<br>Over-voltage inputs                                                                    |

| SN74LVC1G74     |                         | 1.65 V to 5.5 V            | High drive strength 32 mA                                                                                 |

| SN74LVC2G74-Q1  | 1                       |                            | Push-Pull outputs<br>Over voltage tolerant inputs                                                         |

| SN74HCS393      |                         | 2 V to 6 V                 | Counter<br>Up to 8 divisions                                                                              |

For more devices, browse through the *online parametric tool* where you can sort by desired voltage, channel numbers, and other features.

Optimizing Industrial Robot CPU Boards with Logic and Voltage Translation

2

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated